Beruflich Dokumente

Kultur Dokumente

Wash MC Prog

Hochgeladen von

navnath_chikhaleOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Wash MC Prog

Hochgeladen von

navnath_chikhaleCopyright:

Verfügbare Formate

Lab Assignment:3 Front end VLSI Design A]washing Machine Controller Using VHDL ---------------------------------------------------------------------------------- Company:Ikonic Edge Techno

Solutions -- Engineer: Navnath Chikhale --- Create Date: 20:19:53 08/02/2012 -- Design Name: -- Module Name: wash_mc - Behavioral -- Project Name: -- Target Devices: -- Tool versions: -- Description: --- Dependencies: --- Revision: -- Revision 0.01 - File Created -- Additional Comments: ---------------------------------------------------------------------------------library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; ---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity wash_mc is Port ( clk,rst,start: in STD_LOGIC; s_load,m_load,lg_load : in STD_LOGIC; cold,norm,hot : in STD_LOGIC; cw_v,hw_v,dr_v,htr,fan : out STD_LOGIC; mot : out STD_LOGIC_VECTOR (2 downto 0); --blower,heater : out STD_LOGIC; gentle,normal,heavy,no_heat,low_heat,normal_heat,high_heat: in STD_L OGIC; d_nht,d_lht,d_hht : in STD_LOGIC); end wash_mc; architecture Behavioral of wash_mc is type typ_decl is (s0,load,temp,wait_20,w_cycle,d_cycle,motor,heater); signal state:typ_decl; signal signal signal signal count_20:integer range 0 to 5000000; s_load_sig:std_logic; m_load_sig:std_logic; lg_load_sig:std_logic;

signal gentle_sig:std_logic; signal normal_sig:std_logic; signal heavy_sig:std_logic; signal no_heat_sig:std_logic; signal low_heat_sig:std_logic;

signal normal_heat_sig:std_logic; signal high_heat_sig:std_logic; begin process(clk,rst) begin if(rst='1')then state<=s0; elsif(clk'event and clk='1')then case state is when s0=>if(start='1')then state<=load; else state<=s0; end if; when load=> if s_load='1' then s_load_sig<='1'; state<=temp; elsif(m_load='1')then m_load_sig<='1'; state<=temp; elsif(lg_load='1')then lg_load_sig<='1'; state<=temp; else state<=load; end if; when temp=> if(cold='1')then cw_v<='1'; ----fill with cold water for 20 sec time. state<=wait_20; elsif(norm='1')then cw_v<='1';hw_v<='1';--fi ll with half cold and half hot water. state<=wait_20; elsif(hot='1')then hw_v<='1';--fill with ho t water. state<=wait_20; else state<=temp; end if; when wait_20=> if(count_20=5 and s_load _sig='1')then --fill for small load for 5 sec only. cw_v<='0';hw_v<='0'; count_20<=0; state<=w_cycle; elsif(count_20=10 and m_ load_sig='1')then --fill for medium load for 10 sec only cw_v<='0';hw_v<='0'; count_20<=0; state<=w_cycle; elsif(count_20=20 and lg _load_sig='1')then --fill for larg load for 20 sec only cw_v<='0';hw_v<='0'; count_20<=0; state<=w_cycle;

else count_20<=count_20+1; state<=wait_20; end if; when w_cycle=> if(gentle='1')then gentle_sig<='1'; state<=d_cycle; elsif(normal='1')then normal_sig<='1'; state<=d_cycle; elsif(heavy='1')then heavy_sig<='1'; state<=d_cycle; else state<=w_cycle; end if; when d_cycle=> if(no_heat='1')then no_heat_sig<='1'; state<=motor; elsif(low_heat='1')then low_heat_sig<='1'; state<=motor; elsif(normal_heat='1')th en normal_heat_sig<='1'; state<=motor; elsif(high_heat='1')then high_heat_sig<='1'; state<=motor; else state<=d_cycle; end if; when motor=> if(gentle_sig='1')then mot<="001"; state<=heater; elsif(normal_sig='1')the n mot<="011"; state<=heater; elsif(heavy_sig='1')then mot<="101"; state<=heater; end if; when heater=> if(no_heat_sig='1')then htr<='0'; fan<='1'; state<=s0; elsif(low_heat='1')then htr<='1'; fan<='1'; state<=s0; elsif(normal_heat='1')th en htr<='1'; fan<='1';

state<=s0; elsif(high_heat='1')then htr<='1'; fan<='1'; state<=s0; else state<=d_cycle; end if; end case; end if; end process; end Behavioral;

Das könnte Ihnen auch gefallen

- Modulo N CounterDokument24 SeitenModulo N CounterShankar RaoNoch keine Bewertungen

- DemoDokument2 SeitenDemoPhúc PhạmNoch keine Bewertungen

- Journal 0144Dokument20 SeitenJournal 0144Nacer KhoulaleneNoch keine Bewertungen

- New Microsoft Word DocumentDokument6 SeitenNew Microsoft Word DocumentShubham NigamNoch keine Bewertungen

- RefreshDokument5 SeitenRefreshKrishna GhantaNoch keine Bewertungen

- Contador Con Reset y CargaDokument2 SeitenContador Con Reset y CargasisissmashxdNoch keine Bewertungen

- Barrel Shifter CodeDokument2 SeitenBarrel Shifter CodeHarshal AmbatkarNoch keine Bewertungen

- Basic Elevator Design in VHDLDokument46 SeitenBasic Elevator Design in VHDLDenisa BrinzanNoch keine Bewertungen

- Physical Design InterviewDokument8 SeitenPhysical Design InterviewSharathNoch keine Bewertungen

- ChronoDokument4 SeitenChronomanelNoch keine Bewertungen

- PARCIALDokument9 SeitenPARCIALJaqueline MuñozNoch keine Bewertungen

- GCP Essentials ChallangeDokument2 SeitenGCP Essentials ChallangepramodbnNoch keine Bewertungen

- Xilinx ManualDokument74 SeitenXilinx Manualsukumar_bagNoch keine Bewertungen

- TutorialDokument14 SeitenTutorialAlcaraz Garcia Carlos EmmanuelNoch keine Bewertungen

- LEARNINGS - Google DriveDokument200 SeitenLEARNINGS - Google DriveG dileep KumarNoch keine Bewertungen

- Forcetv IptvDokument11 SeitenForcetv IptvdededunguNoch keine Bewertungen

- Lab6 - Achmad Mauludin H. - 165060301111002Dokument3 SeitenLab6 - Achmad Mauludin H. - 165060301111002Mauudin BRgNoch keine Bewertungen

- Contador Ascendente y Desendente en PararleloDokument2 SeitenContador Ascendente y Desendente en PararlelosisissmashxdNoch keine Bewertungen

- SNIPED Sessions and ORADokument8 SeitenSNIPED Sessions and ORARajab TambweNoch keine Bewertungen

- SimulacionDokument2 SeitenSimulacionRafaelNoch keine Bewertungen

- Rmougashmastershort 140207171440 Phpapp02Dokument111 SeitenRmougashmastershort 140207171440 Phpapp02Thota Mahesh DbaNoch keine Bewertungen

- InstallLog 20-Jan-2013 0119Dokument120 SeitenInstallLog 20-Jan-2013 0119bigbang747Noch keine Bewertungen

- Hive Case Study Assignment UpgradDokument45 SeitenHive Case Study Assignment Upgradaparna71% (14)

- СампдимемстаDokument6 SeitenСампдимемстаDime. STNoch keine Bewertungen

- SW1 Show TechDokument86 SeitenSW1 Show TechramitNoch keine Bewertungen

- General AdministrationDokument14 SeitenGeneral Administrationmaruthi631Noch keine Bewertungen

- Dataguardinaction Demo OutputDokument17 SeitenDataguardinaction Demo OutputCatalin EnacheNoch keine Bewertungen

- A3 CA Fri Ankit Aman SudershanDokument16 SeitenA3 CA Fri Ankit Aman SudershansrnankitNoch keine Bewertungen

- EBS DB 11.1.0.7 Upgrade To 12c 12.1.0.2Dokument20 SeitenEBS DB 11.1.0.7 Upgrade To 12c 12.1.0.2Abdallah AttiaNoch keine Bewertungen

- 01 DDL P131 F13107 STA LogDokument3 Seiten01 DDL P131 F13107 STA LogRaja RangasamyNoch keine Bewertungen

- Bach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineDokument11 SeitenBach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineMờ LanhNoch keine Bewertungen

- Server LogDokument3 SeitenServer Logismailismail192020Noch keine Bewertungen

- Lab 5 - A VHDL Reaction TimerDokument10 SeitenLab 5 - A VHDL Reaction TimerMayank AgarwalNoch keine Bewertungen

- ADT7420 Codigo LibroDokument4 SeitenADT7420 Codigo LibroAPRENDE LO QUE APRENDONoch keine Bewertungen

- I P C 7.1.1 Instal at Ion StepsDokument4 SeitenI P C 7.1.1 Instal at Ion StepsyprajuNoch keine Bewertungen

- 1 2 HamadahDokument239 Seiten1 2 HamadahHamada SaiedNoch keine Bewertungen

- 01 DDL P131 F13106 STA LogDokument3 Seiten01 DDL P131 F13106 STA LogRaja RangasamyNoch keine Bewertungen

- Lab 6 Firna FrilanisaDokument22 SeitenLab 6 Firna FrilanisaFirna FrilanisaNoch keine Bewertungen

- Lab 4 LogicaDokument16 SeitenLab 4 LogicaCamila CamperosNoch keine Bewertungen

- Server LogDokument151 SeitenServer LogantonantonNoch keine Bewertungen

- AP Lab 9Dokument19 SeitenAP Lab 9Latest TechiansNoch keine Bewertungen

- Computer-Aided VLSI System DesignDokument13 SeitenComputer-Aided VLSI System Design黃于瑄Noch keine Bewertungen

- Elm VHDLDokument8 SeitenElm VHDLnickNoch keine Bewertungen

- EBS UPGRADE From 11i To 12.2.5Dokument9 SeitenEBS UPGRADE From 11i To 12.2.5KingNoch keine Bewertungen

- Server LogDokument4 SeitenServer LogBogdanNoch keine Bewertungen

- 8to1 Mux Using 4to1 MuxDokument5 Seiten8to1 Mux Using 4to1 MuxYashaswiNoch keine Bewertungen

- CTV Old IptvDokument7 SeitenCTV Old IptvBagas Adi WigunaNoch keine Bewertungen

- I2c - Master CodeDokument4 SeitenI2c - Master CodeLikourgos LeisosNoch keine Bewertungen

- 03 DDL P131 F13107 ODS LogDokument4 Seiten03 DDL P131 F13107 ODS LogRaja RangasamyNoch keine Bewertungen

- Premiere Elements LogDokument911 SeitenPremiere Elements LogRyer SchellingNoch keine Bewertungen

- Debug Trace FileDokument7 SeitenDebug Trace FileStéphane AlexandreNoch keine Bewertungen

- Replace Duw: 1. Create A RBS Backup From EMAS in The Old DUWDokument5 SeitenReplace Duw: 1. Create A RBS Backup From EMAS in The Old DUWDonson junedi TampubolonNoch keine Bewertungen

- DUW ReplacementDokument5 SeitenDUW ReplacementAhmed Zehara100% (3)

- Some Tutorials in Computer Networking HackingVon EverandSome Tutorials in Computer Networking HackingNoch keine Bewertungen

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosVon EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosBewertung: 5 von 5 Sternen5/5 (1)

- Windows Server 2012 Hyper-V Installation and Configuration GuideVon EverandWindows Server 2012 Hyper-V Installation and Configuration GuideNoch keine Bewertungen

- Deploying and Managing a Cloud Infrastructure: Real-World Skills for the CompTIA Cloud+ Certification and Beyond: Exam CV0-001Von EverandDeploying and Managing a Cloud Infrastructure: Real-World Skills for the CompTIA Cloud+ Certification and Beyond: Exam CV0-001Noch keine Bewertungen

- Antennas: Constantine A. BalanisDokument45 SeitenAntennas: Constantine A. BalanisAzeem BhattiNoch keine Bewertungen

- FORTRAN Based ApproachDokument22 SeitenFORTRAN Based ApproachGS EKTANoch keine Bewertungen

- Electronic Symbol - WikipediaDokument11 SeitenElectronic Symbol - WikipediaLevy Faria GiembinskyNoch keine Bewertungen

- Hach-Sigma 900 Composite Sampler Users ManualDokument52 SeitenHach-Sigma 900 Composite Sampler Users ManualaquachemNoch keine Bewertungen

- JOB SHEET Drafting PCBDokument3 SeitenJOB SHEET Drafting PCBZeen DeeNoch keine Bewertungen

- Pricelist PLTS On Grid PerkotaanDokument2 SeitenPricelist PLTS On Grid PerkotaanNugrohoAriePutrantoNoch keine Bewertungen

- Instrukcja Obslugi MODECOM Volcano Amirani ARGBDokument2 SeitenInstrukcja Obslugi MODECOM Volcano Amirani ARGBKarol KotekNoch keine Bewertungen

- Pratt & Whitney Ft4 Three Shaft Gas Turbine Generator Drive Application Control PackageDokument3 SeitenPratt & Whitney Ft4 Three Shaft Gas Turbine Generator Drive Application Control PackageJose Medina AnguloNoch keine Bewertungen

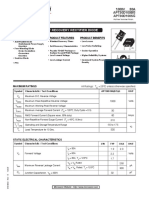

- Ultrafast Soft Recovery Rectifier Diode: Product Benefits Product Features Product ApplicationsDokument4 SeitenUltrafast Soft Recovery Rectifier Diode: Product Benefits Product Features Product ApplicationsEDER RIBEIRONoch keine Bewertungen

- Cold Room Evaporator UnitDokument2 SeitenCold Room Evaporator UnitAlex AndersNoch keine Bewertungen

- High Speed Centrifuge, 1248R - Service ManualDokument40 SeitenHigh Speed Centrifuge, 1248R - Service ManualTalhaNoch keine Bewertungen

- Power FusesDokument16 SeitenPower FusesrazvansasuNoch keine Bewertungen

- 873P Ultrasonic Sensors With Dual Discrete/Single Analog OutputsDokument4 Seiten873P Ultrasonic Sensors With Dual Discrete/Single Analog Outputsmanduca matthewNoch keine Bewertungen

- Service Manual: Portable Minidisc PlayerDokument26 SeitenService Manual: Portable Minidisc PlayerAnonymous Lfgk6vygNoch keine Bewertungen

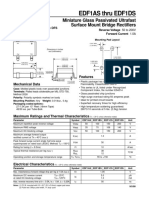

- EDF1AS Thru EDF1DS: Miniature Glass Passivated Ultrafast Surface Mount Bridge RectifiersDokument2 SeitenEDF1AS Thru EDF1DS: Miniature Glass Passivated Ultrafast Surface Mount Bridge RectifiersCarlosNoch keine Bewertungen

- Notes Switchgear and Protection Unit 2Dokument32 SeitenNotes Switchgear and Protection Unit 2Pratik SinghNoch keine Bewertungen

- RB800Dokument12 SeitenRB800Carlos GrandiNoch keine Bewertungen

- PSEN Ma1 4p-50 Operat Manual 22126-EN-06Dokument21 SeitenPSEN Ma1 4p-50 Operat Manual 22126-EN-06Doganay KalguNoch keine Bewertungen

- ReleaseNotes IndraDrive MPB20VRS ENDokument224 SeitenReleaseNotes IndraDrive MPB20VRS ENLinh Pham0% (1)

- En 54 Standard Family PartsDokument2 SeitenEn 54 Standard Family PartsionutenacheNoch keine Bewertungen

- Transas AIS T-201 Operational ManualDokument70 SeitenTransas AIS T-201 Operational ManualBhavin DoshiNoch keine Bewertungen

- Atasheet en 201508 T58I-E-02 Rev3 2Dokument17 SeitenAtasheet en 201508 T58I-E-02 Rev3 2deri mardiNoch keine Bewertungen

- 28 GHZ Millimeter Wave Cellular Communication Measurements For Reflection and Penetration Loss in and Around Buildings in New York CityDokument5 Seiten28 GHZ Millimeter Wave Cellular Communication Measurements For Reflection and Penetration Loss in and Around Buildings in New York CityJunyi LiNoch keine Bewertungen

- By: Mr.L.Kumaraswamy M.E. (Iisc), Associate Professor, Mce, HassanDokument6 SeitenBy: Mr.L.Kumaraswamy M.E. (Iisc), Associate Professor, Mce, Hassansarala20021990Noch keine Bewertungen

- DM7416 Hex Inverting Buffers With High Voltage Open-Collector OutputsDokument3 SeitenDM7416 Hex Inverting Buffers With High Voltage Open-Collector OutputsnooorNoch keine Bewertungen

- Thyssenkrupp Electrical Steel GMBHDokument32 SeitenThyssenkrupp Electrical Steel GMBHRichard SyNoch keine Bewertungen

- EcoEnergy Catalogue 081110Dokument68 SeitenEcoEnergy Catalogue 081110Hummingbird HgcNoch keine Bewertungen

- TCC Number 165-6Dokument1 SeiteTCC Number 165-6Alvaro Solis VegaNoch keine Bewertungen

- Unisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysDokument5 SeitenUnisonic Technologies Co., LTD: Eight High Voltage, High Current Darlington ArraysTojo BasheerNoch keine Bewertungen

- Raspberry Pi Alamode CNC Controller - 13 Steps (With Pictures)Dokument27 SeitenRaspberry Pi Alamode CNC Controller - 13 Steps (With Pictures)orangota100% (1)