Beruflich Dokumente

Kultur Dokumente

De2 - 115 User Manual

Hochgeladen von

Kenan Emre ÜstündağOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

De2 - 115 User Manual

Hochgeladen von

Kenan Emre ÜstündağCopyright:

Verfügbare Formate

5

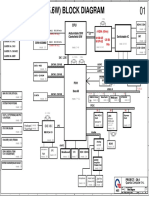

ALTERA Cyclone IV Development & Education Board (DE2-115)

D D

SCHEMATIC

01 TOP 02 MEMORY 03 DISPLAY 04 IN/OUT 05 ETHERNET 06 VIDEO 07 AUDIO 08 USB DEVICE 09 FPGA 10 POWER

CONTENT

Cover Page, Placement,TOP SDRAM , SRAM , FLASH , SD CARD LCD , LED , 7SEGMENT CLOCK, IrDA, PS2 , RS232 , BUTTON , SWITCH , HSMC, EEPROM 88E1111 ADV7123, ADV7180 WM8731 ISP1362 Cyclone IV EP4CE115 BANK1..BANK8 , POWER , CONFIG POWER 1.2V, 1.8V, 2.5V, 3.3V, 5V

PAGE

01 ~ 03 04 ~ 06 07 ~ 08 09 ~ 14 15 ~ 16 17 ~ 18 19 20 21 ~ 25 26 ~ 27

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number COVER PAGE Friday, September 24, 2010 Sheet

1

Rev B 1 of 27

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number PLACEMENT Friday, September 24, 2010 Sheet

1

Rev B 2 of 27

05 ETHERNET 10 EP4CE115 02 MEMORY DRAM_ADDR[12..0] DRAM_DQM[3..0] DRAM_BA0 DRAM_BA1 DRAM_CAS_N DRAM_RAS_N DRAM_CKE DRAM_WE_N DRAM_CS_N DRAM_CLK

D

PAGE 15-16 ENET0_RX_DATA[3..0] ENET0_RX_DV ENET0_RX_ER ENET0_RX_CRS ENET0_RX_COL ENET0_RX_CLK ENET0_TX_CLK ENET0_INT_N ENET0_MDIO ENET0_LINK100 ENET1_RX_DATA[3..0] ENET1_RX_DV ENET1_RX_ER ENET1_RX_CRS ENET1_RX_COL ENET1_RX_CLK ENET1_TX_CLK ENET1_INT_N ENET1_MDIO ENET1_LINK100 ENETCLK_25 ENET0_RX_DATA[3..0] ENET0_RX_DV ENET0_RX_ER ENET0_RX_CRS ENET0_RX_COL ENET0_RX_CLK ENET0_TX_CLK ENET0_INT_N ENET0_MDIO ENET0_LINK100 ENET1_RX_DATA[3..0] ENET1_RX_DV ENET1_RX_ER ENET1_RX_CRS ENET1_RX_COL ENET1_RX_CLK ENET1_TX_CLK ENET1_INT_N ENET1_MDIO ENET1_LINK100 ENETCLK_25

PAGE 21-25 ENET0_LINK100 ENET0_RX_DATA[3..0] ENET0_RX_ER ENET0_RX_COL ENET0_RX_CRS ENET0_RX_DV ENET0_RX_CLK ENET0_TX_DATA[3..0] ENET0_TX_CLK ENET0_GTX_CLK ENET0_TX_EN ENET0_TX_ER ENET0_INT_N ENET0_RST_N ENET0_MDC ENET0_MDIO ENET1_RX_DATA[3..0] ENET1_RX_ER ENET1_RX_COL ENET1_RX_CRS ENET1_RX_DV ENET1_RX_CLK ENET1_TX_DATA[3..0] ENET1_TX_CLK ENET1_GTX_CLK ENET1_TX_EN ENET1_TX_ER ENET1_INT_N ENET1_RST_N ENET1_MDC ENET1_MDIO ENET1_LINK100 ENETCLK_25 I2C_SCLK I2C_SDAT TD_DATA[7..0] TD_VS TD_HS TD_CLK27 TD_RESET_N VGA_R[7..0] VGA_G[7..0] VGA_B[7..0] VGA_BLANK_N VGA_SYNC_N VGA_VS VGA_HS VGA_CLK OTG_DATA[15..0] OTG_INT1 OTG_INT0 OTG_DREQ1 OTG_DREQ0 OTG_FSPEED OTG_LSPEED OTG_DACK_N1 OTG_DACK_N0 OTG_ADDR1 OTG_ADDR0 OTG_RD_N OTG_WR_N OTG_CS_N OTG_RST_N AUD_XCK AUD_BCLK AUD_ADCDAT AUD_ADCLRCK AUD_DACDAT AUD_DACLRCK TMS TCK TDI TDO ENET0_LINK100 ENET0_RX_DATA[3..0] ENET0_RX_ER ENET0_RX_COL ENET0_RX_CRS ENET0_RX_DV ENET0_RX_CLK ENET0_TX_DATA[3..0] ENET0_TX_CLK ENET0_GTX_CLK ENET0_TX_EN ENET0_TX_ER ENET0_INT_N ENET0_RST_N ENET0_MDC ENET0_MDIO ENET1_RX_DATA[3..0] ENET1_RX_ER ENET1_RX_COL ENET1_RX_CRS ENET1_RX_DV ENET1_RX_CLK ENET1_TX_DATA[3..0] ENET1_TX_CLK ENET1_GTX_CLK ENET1_TX_EN ENET1_TX_ER ENET1_INT_N ENET1_RST_N ENET1_MDC ENET1_MDIO ENET1_LINK100 ENETCLK_25 I2C_SCLK I2C_SDAT TD_DATA[7..0] TD_VS TD_HS TD_CLK27 TD_RESET_N VGA_R[7..0] VGA_G[7..0] VGA_B[7..0] VGA_BLANK_N VGA_SYNC_N VGA_VS VGA_HS VGA_CLK OTG_DATA[15..0] OTG_INT1 OTG_INT0 OTG_DREQ1 OTG_DREQ0 OTG_FSPEED OTG_LSPEED OTG_DACK_N1 OTG_DACK_N0 OTG_ADDR1 OTG_ADDR0 OTG_RD_N OTG_WR_N OTG_CS_N OTG_RST_N AUD_XCK AUD_BCLK AUD_ADCDAT AUD_ADCLRCK AUD_DACDAT AUD_DACLRCK JTAG_TMS JTAG_TCK JTAG_TDI FPGA_TDO

PAGE 4-6 DRAM_DQ[31..0] DRAM_DQ[31..0] DRAM_DQ[31..0] DRAM_ADDR[12..0] DRAM_DQM[3..0] DRAM_CAS_N DRAM_RAS_N DRAM_BA0 DRAM_BA1 DRAM_CKE DRAM_WE_N DRAM_CS_N DRAM_CLK SRAM_DQ[15..0] SRAM_ADDR[19..0] SRAM_CE_N SRAM_OE_N SRAM_WE_N SRAM_UB_N SRAM_LB_N FL_DQ[7..0] FL_ADDR[22..0] FL_RST_N FL_WE_N FL_CE_N FL_WP_N FL_OE_N FL_RY SD_DAT[3..0] SD_CLK SD_WP_N SD_CMD LCD_ON LCD_EN LCD_RW LCD_RS LCD_BLON LCD_DATA[7..0] HEX0[6..0] HEX1[6..0] HEX2[6..0] HEX3[6..0] HEX4[6..0] HEX5[6..0] HEX6[6..0] HEX7[6..0] LEDG[8..0] LEDR[17..0] CLOCK_50 CLOCK2_50 CLOCK3_50 SMA_CLKIN SMA_CLKOUT DRAM_DQ[31..0] DRAM_ADDR[12..0] DRAM_DQM[3..0] DRAM_CAS_N DRAM_RAS_N DRAM_BA0 DRAM_BA1 DRAM_CKE DRAM_WE_N DRAM_CS_N DRAM_CLK SRAM_DQ[15..0] SRAM_ADDR[19..0] SRAM_CE_N SRAM_OE_N SRAM_WE_N SRAM_UB_N SRAM_LB_N FL_DQ[7..0] FL_ADDR[22..0] FL_RST_N FL_WE_N FL_CE_N FL_WP_N FL_OE_N FL_RY SD_DAT[3..0] SD_CLK SD_WP_N SD_CMD LCD_ON LCD_EN LCD_RW LCD_RS LCD_BLON LCD_DATA[7..0] HEX0[6..0] HEX1[6..0] HEX2[6..0] HEX3[6..0] HEX4[6..0] HEX5[6..0] HEX6[6..0] HEX7[6..0] LEDG[8..0] LEDR[17..0] CLOCK_50 CLOCK2_50 CLOCK3_50 SMA_CLKIN SMA_CLKOUT SW[17..0] KEY[3..0] IRDA_RXD UART_TXD UART_RXD UART_RTS UART_CTS PS2_CLK PS2_DAT PS2_CLK2 PS2_DAT2 GPIO[35..0] HSMC_D[3..0] HSMC_CLKIN_P1 HSMC_CLKIN_N1 HSMC_CLKIN_P2 HSMC_CLKIN_N2 HSMC_CLKOUT_P1 HSMC_CLKOUT_N1 HSMC_CLKOUT_P2 HSMC_CLKOUT_N2 HSMC_CLKIN0 HSMC_CLKOUT0 HSMC_TX_D_P[16..0] HSMC_TX_D_N[16..0] HSMC_RX_D_P[16..0] HSMC_RX_D_N[16..0] EX_IO[6..0]

DRAM_ADDR[12..0] DRAM_DQM[3..0] DRAM_BA0 DRAM_BA1 DRAM_CAS_N DRAM_RAS_N DRAM_CKE DRAM_WE_N DRAM_CS_N DRAM_CLK SRAM_ADDR[19..0] SRAM_UB_N SRAM_LB_N SRAM_WE_N SRAM_OE_N SRAM_CE_N

ENET0_TX_DATA[3..0] ENET0_GTX_CLK ENET0_TX_EN ENET0_TX_ER ENET0_RST_N ENET0_MDC

ENET0_TX_DATA[3..0] ENET0_GTX_CLK ENET0_TX_EN ENET0_TX_ER ENET0_RST_N ENET0_MDC

SRAM_ADDR[19..0] SRAM_UB_N SRAM_LB_N SRAM_WE_N SRAM_OE_N SRAM_CE_N

SRAM_DQ[15..0]

SRAM_DQ[15..0]

ENET1_TX_DATA[3..0] ENET1_MDC ENET1_GTX_CLK ENET1_TX_EN ENET1_TX_ER ENET1_RST_N

ENET1_TX_DATA[3..0] ENET1_MDC ENET1_GTX_CLK ENET1_TX_EN ENET1_TX_ER ENET1_RST_N

FL_ADDR[22..0] FL_WP_N FL_CE_N FL_OE_N FL_WE_N FL_RST_N

FL_ADDR[22..0] FL_WP_N FL_CE_N FL_OE_N FL_WE_N FL_RST_N

FL_DQ[7..0] FL_RY

FL_DQ[7..0]

06 VIDEO

PAGE 17-18

FL_RY

SD_CLK

SD_CLK

SD_CMD SD_DAT[3..0] SD_WP_N

SD_CMD SD_DAT[3..0] SD_WP_N

VGA_R[7..0] VGA_G[7..0] VGA_B[7..0] VGA_SYNC_N VGA_CLK VGA_VS VGA_HS VGA_BLANK_N TD_RESET_N

VGA_R[7..0] VGA_G[7..0] VGA_B[7..0] VGA_SYNC_N VGA_CLK VGA_VS VGA_HS VGA_BLANK_N TD_RESET_n TD_DATA[7..0] TD_VS TD_HS TD_CLK27 TD_DATA[7..0] TD_VS TD_HS TD_CLK27

03 DISPLAY LCD_ON LCD_BLON LCD_EN LCD_RS LCD_RW LEDR[17..0] LEDG[8..0] HEX0[6..0] HEX1[6..0] HEX2[6..0] HEX3[6..0] HEX4[6..0] HEX5[6..0] HEX6[6..0] HEX7[6..0] LCD_ON LCD_BLON LCD_EN LCD_RS LCD_RW LEDR[17..0] LEDG[8..0] HEX0[6..0] HEX1[6..0] HEX2[6..0] HEX3[6..0] HEX4[6..0] HEX5[6..0] HEX6[6..0] HEX7[6..0]

PAGE 7-8 LCD_DATA[7..0] LCD_DATA[7..0]

I2C_SCLK I2C_SDAT

I2C_SCLK I2C_SDAT

C

07 AUDIO AUD_DACDAT AUD_XCK I2C_SDAT I2C_SCLK

PAGE 19 AUD_ADCDAT AUD_BCLK AUD_DACLRCK AUD_ADCLRCK

AUD_DACDAT AUD_XCK I2C_SDAT I2C_SCLK

AUD_ADCDAT AUD_BCLK AUD_DACLRCK AUD_ADCLRCK

04 IN/OUT

PAGE 9 - 14 SW[17..0] GPIO[35..0] SW[17..0] KEY[3..0] GPIO[35..0] KEY[3..0] SW[17..0] IRDA_RXD KEY[3..0] UART_TXD UART_RXD UART_RTS UART_CTS PS2_CLK PS2_DAT PS2_CLK2 PS2_DAT2 GPIO[35..0] HSMC_D[3..0] HSMC_CLKIN_P1 HSMC_CLKIN_N1 HSMC_CLKIN_P2 HSMC_CLKIN_N2 HSMC_CLKOUT_P1 HSMC_CLKOUT_N1 HSMC_CLKOUT_P2 HSMC_CLKOUT_N2 HSMC_CLKIN0 HSMC_CLKOUT0 HSMC_TX_D_P[16..0] HSMC_TX_D_N[16..0] HSMC_RX_D_P[16..0] HSMC_RX_D_N[16..0] EX_IO[6..0]

08 USB DEVICE OTG_ADDR1 OTG_ADDR0 OTG_CS_N OTG_WR_N OTG_RD_N OTG_DACK_N1 OTG_DACK_N0 OTG_RST_N USB_12MHz OTG_ADDR1 OTG_ADDR0 OTG_CS_N OTG_WR_N OTG_RD_N OTG_DACK_N1 OTG_DACK_N0 OTG_RST_N USB_12MHz

PAGE 20 OTG_DATA[15..0] OTG_FSPEED OTG_LSPEED OTG_INT1 OTG_INT0 OTG_DREQ1 OTG_DREQ0 OTG_DATA[15..0] OTG_FSPEED OTG_LSPEED OTG_INT1 OTG_INT0 OTG_DREQ1 OTG_DREQ0

SMA_CLKOUT

SMA_CLKOUT

CLOCK_50 CLOCK2_50 CLOCK3_50 SMA_CLKIN

CLOCK_50 CLOCK2_50 CLOCK3_50 SMA_CLKIN

11 POWER

PAGE 26 -27

PS2_CLK2 PS2_DAT2 PS2_CLK PS2_DAT UART_TXD UART_CTS

B

PS2_CLK2 PS2_DAT2 PS2_CLK PS2_DAT UART_RXD UART_RTS IRDA_RXD EEP_I2C_SDAT EX_IO[6..0]

UART_TXD UART_CTS

UART_RXD UART_RTS IRDA_RXD

NSTATUS CONF_DONE NCONFIG NCE

NSTATUS CONF_DONE NCONFIG NCE

EEP_I2C_SCLK

EEP_I2C_SCLK

EEP_I2C_SDAT EX_IO[6..0]

DCLK DATA0 NCSO ASDO EEP_I2C_SCLK EEP_I2C_SDAT

DCLK DATA0 NCSO ASDO EEP_I2C_SCLK EEP_I2C_SDAT

FPGA_TDO JTAG_TMS JTAG_TCK HSMC_CLKOUT_P1 HSMC_CLKOUT_N1 HSMC_CLKOUT_P2 HSMC_CLKOUT_N2

HSMC_TDI HSMC_TMS HSMC_TCK HSMC_CLKOUT_P1 HSMC_CLKOUT_N1 HSMC_CLKOUT_P2 HSMC_CLKOUT_N2

JTAG_TDO HSMC_SDA HSMC_SCL HSMC_CLKOUT0 HSMC_TX_D_P[16..0] HSMC_TX_D_N[16..0] HSMC_RX_D_P[16..0] HSMC_RX_D_N[16..0] HSMC_CLKIN_P1 HSMC_CLKIN_N1 HSMC_CLKIN_P2 HSMC_CLKIN_N2 HSMC_CLKIN0 HSMC_D[3..0]

JTAG_TDO I2C_SDAT I2C_SCLK HSMC_CLKOUT0 HSMC_TX_D_P[16..0] HSMC_TX_D_N[16..0] HSMC_RX_D_P[16..0] HSMC_RX_D_N[16..0] HSMC_CLKIN_P1 HSMC_CLKIN_N1 HSMC_CLKIN_P2 HSMC_CLKIN_N2 HSMC_CLKIN0 HSMC_D[3..0]

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size C Date:

5 4 3 2

Document Number TOP Friday, September 24, 2010

1

Rev B Sheet 3 of 27

DRAM_DQ[31..0] DRAM_ADDR[12..0] DRAM_DQM[3..0] DR_VCC3P3 DR_VCC3P3

1 14 27

3 9 43 49

1 14 27

U15

D

U13

3 9 43 49

VDD VDD VDD

VDDQ VDDQ VDDQ VDDQ

VDD VDD VDD

DRAM_ADDR0 DRAM_ADDR1 DRAM_ADDR2 DRAM_ADDR3 DRAM_ADDR4 DRAM_ADDR5 DRAM_ADDR6 DRAM_ADDR7 DRAM_ADDR8 DRAM_ADDR9 DRAM_ADDR10 DRAM_ADDR11 DRAM_ADDR12 DRAM_CLK DRAM_CKE DRAM_DQM0 DRAM_DQM1 DRAM_WE_N DRAM_CAS_N DRAM_RAS_N DRAM_CS_N DRAM_BA0 DRAM_BA1

23 24 25 26 29 30 31 32 33 34 22 35 36 38 37 15 39 16 17 18 19 20 21

A0 D0 A1 D1 A2 D2 A3 D3 A4 D4 A5 D5 A6 D6 A7 D7 A8 D8 A9 D9 A10 D10 A11 SDRAM 32Mx16 D11 A12 D12 CLK D13 CKE D14 LDQM D15 UDQM nWE nCAS nRAS nCS BA0 BA1 VSS VSS VSS

2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53

DRAM_DQ0 DRAM_DQ1 DRAM_DQ2 DRAM_DQ3 DRAM_DQ4 DRAM_DQ5 DRAM_DQ6 DRAM_DQ7 DRAM_DQ8 DRAM_DQ9 DRAM_DQ10 DRAM_DQ11 DRAM_DQ12 DRAM_DQ13 DRAM_DQ14 DRAM_DQ15

DRAM_ADDR0 DRAM_ADDR1 DRAM_ADDR2 DRAM_ADDR3 DRAM_ADDR4 DRAM_ADDR5 DRAM_ADDR6 DRAM_ADDR7 DRAM_ADDR8 DRAM_ADDR9 DRAM_ADDR10 DRAM_ADDR11 DRAM_ADDR12 DRAM_CLK DRAM_CKE DRAM_DQM2 DRAM_DQM3 DRAM_WE_n DRAM_CAS_n DRAM_RAS_n DRAM_CS_n DRAM_BA0 DRAM_BA1

23 24 25 26 29 30 31 32 33 34 22 35 36 38 37 15 39 16 17 18 19 20 21

VDDQ VDDQ VDDQ VDDQ

A0 D0 A1 D1 A2 D2 A3 D3 A4 D4 A5 D5 A6 D6 A7 D7 A8 D8 A9 D9 A10 D10 A11 SDRAM 32Mx16 D11 A12 D12 CLK D13 CKE D14 LDQM D15 UDQM nWE nCAS nRAS nCS BA0 BA1 VSS VSS VSS

2 4 5 7 8 10 11 13 42 44 45 47 48 50 51 53

DRAM_DQ16 DRAM_DQ17 DRAM_DQ18 DRAM_DQ19 DRAM_DQ20 DRAM_DQ21 DRAM_DQ22 DRAM_DQ23 DRAM_DQ24 DRAM_DQ25 DRAM_DQ26 DRAM_DQ27 DRAM_DQ28 DRAM_DQ29 DRAM_DQ30 DRAM_DQ31

VSSQ VSSQ VSSQ VSSQ

VSSQ VSSQ VSSQ VSSQ

DR_VCC3P3 R223 R224 4.7K DRAM_WE_N 4.7K DRAM_CAS_N 4.7K DRAM_RAS_N 4.7K DRAM_CS_N 4.7K DRAM_CKE

B

28 41 54

6 12 46 52

28 41 54

6 12 46 52

SDRAM0

VCC3P3 R235 DR_VCC3P3 0 C82 10u C85 10u C280 0.1u C286 0.1u C282 0.1u C281 0.1u C283 0.1u C287 0.1u C284 0.1u C262 0.1u C258 0.1u C259 0.1u C273 0.1u DR_VCC3P3 DR_VCC3P3

SDRAM1

R225 R226 R234

C272 0.1u

C260 0.1u

C261 0.1u

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size A Date:

5 4 3

Document Number SDRAM Friday, September 24, 2010

2

Rev B Sheet 4

1

of

27

SR_VCC3P3

SRAM_DQ[15..0] SRAM_ADDR[19..0]

12

U17

VDD

SRAM_ADDR19 SRAM_ADDR18 SRAM_ADDR17 SRAM_ADDR16 SRAM_ADDR15 SRAM_ADDR14 SRAM_ADDR13 SRAM_ADDR12 SRAM_ADDR11 SRAM_ADDR10 SRAM_ADDR9 SRAM_ADDR8 SRAM_ADDR7 SRAM_ADDR6 SRAM_ADDR5 SRAM_ADDR4 SRAM_ADDR3 SRAM_ADDR2 SRAM_ADDR1 SRAM_ADDR0 SRAM_CE_N SRAM_OE_N SRAM_WE_N SRAM_UB_N SRAM_LB_N

20 21 22 23 24 25 26 27 28 29 30 45 46 47 48 1 2 3 4 5 7 44 18 43 42

VDD

36

A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 CE_n OE_n WE_n UB_n LB_n

SRAM 1Mx16

I/O15 I/O14 I/O13 I/O12 I/O11 I/O10 I/O9 I/O8 I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 I/O0

41 40 39 38 35 34 33 32 17 16 15 14 11 10 9 8

SRAM_DQ15 SRAM_DQ14 SRAM_DQ13 SRAM_DQ12 SRAM_DQ11 SRAM_DQ10 SRAM_DQ9 SRAM_DQ8 SRAM_DQ7 SRAM_DQ6 SRAM_DQ5 SRAM_DQ4 SRAM_DQ3 SRAM_DQ2 SRAM_DQ1 SRAM_DQ0

NC1 NC2 NC3

6 19 31

SR_VCC3P3 SRAM_CE_N R240 4.7K

GND 13

37

GND

VCC3P3 R78

SR_VCC3P3 SR_VCC3P3 0 C86 10u C289 0.1u C290 0.1u

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size A Date:

5 4 3

Document Number SRAM Friday, September 24, 2010

2

Rev B Sheet 5

1

of

27

SD_DAT[3..0] FL_DQ[7..0] FL_ADDR[22..0] U26 SD_DAT2 SD_DAT3 SD_CMD F_VCC3P3 SD_CLK SD_DAT0 SD_DAT1 SD_WP_N

C

F_VCC3P3 SD_DAT3 SD_DAT2 SD_DAT1 SD_DAT0 SD_CMD R236 SD_WP_N R237 10K C274 10u C285 0.1u 10K

U18 FL_ADDR1 FL_ADDR2 FL_ADDR3 FL_ADDR4 FL_ADDR5 FL_ADDR6 FL_ADDR7 FL_ADDR8 FL_ADDR9 FL_ADDR10 FL_ADDR11 FL_ADDR12 FL_ADDR13 FL_ADDR14 FL_ADDR15 FL_ADDR16 FL_ADDR17 FL_ADDR18 FL_ADDR19 FL_ADDR20 FL_ADDR21 FL_ADDR22

F_VCC3P3

9 1 2 3 4 5 6 7 8 11

DAT2 DAT3 CMD VSS VCC CLK VSS DAT0 DAT1 WP VSS

SD Card Socket

8 7 6 5

10K

1 2 3 4

RN24

31 26 25 24 23 22 21 20 10 9 8 7 6 5 4 3 54 19 18 11 12 15 2 1 56 55 13 14 16 17 32 34 53

A0 VIO A1 VCC A2 A3 DQ0 A4 DQ1 A5 DQ2 A6 DQ3 A7 DQ4 A8 DQ5 A9 DQ6 A10 DQ7 A11 DQ8 A12 DQ9 A13 DQ10 A14 DQ11 A15 DQ12 A16 DQ13 A17 DQ14 A18 DQ15/A-1 A19 A20 A21 FLASH 8Mx8 A22 A23 A24 A25 WE# RESET# WP#ACC RY/BY# CE# OE# BYTE# RFU0 RFU1 RFU2 VSS VSS

29 43 35 37 39 41 44 46 48 50 36 38 40 42 45 47 49 51

FL_DQ0 FL_DQ1 FL_DQ2 FL_DQ3 FL_DQ4 FL_DQ5 FL_DQ6 FL_DQ7

FL_ADDR0

VCC3P3 R79

F_VCC3P3 0 C87 10u

F_VCC3P3

FL_WE_N FL_RST_N FL_WP_N FL_RY FL_CE_N FL_OE_N

27 28 30 33 52

C288 0.1u

C291 0.1u

F_VCC3P3 R238 R239 4.7K 4.7K FL_RY FL_CE_N

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size A Date:

5 4 3

Document Number Flash & SD Friday, September 24, 2010

2

Rev B Sheet 6

1

of

27

LEDR[17..0] LEDG[8..0]

LEDR0 D71 DNI LCD_DATA0 1 3 2 VCC3P3 C263 D70 DNI LCD_DATA1 1 3 2 VCC5 VCC43 LCD_ON D69 DNI LCD_DATA2 1 3 2 VCC43 Q7 DNI R204 1K D68 DNI LCD_DATA3 1 3 2 LCD_BLON D67 DNI LCD_DATA4 1 3 2 U11 D66 DNI LCD_DATA5 1 3 2 LEDR10 LEDR11 LEDR12 LEDR13 4 3 2 1 RN34 5 6 7 8 120 LEDR13 D64 DNI LCD_DATA7 1 3 2 LEDR14 LEDR15 LEDR16 LEDR17 4 3 2 1 RN36 5 6 7 8 120 LEDR17 LEDR15 LEDR16 LEDR14 LCD-2x16 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 R227 DNI DNI Q9 DNI LCD_DATA[7..0] R214 LCD_BL LCD_DATA7 LCD_DATA6 LCD_DATA5 LCD_DATA4 LCD_DATA3 LCD_DATA2 LCD_DATA1 LCD_DATA0 LCD_EN LCD_RW LCD_RS LCD_CONT LCD_VCC R205 47 LEDR8 LEDR9 LEDG8 4 3 2 1 RN32 5 6 7 8 120 LEDR8 LEDR9 LEDG8 R212 680 R213 680 LEDR4 Q5 8050 VCC43 LEDR4 LEDR5 LEDR6 LEDR7 4 3 2 1 RN31 5 6 7 8 120 LEDR7 LEDR5 LEDR6 1u Q8 8050 Q6 8550 LEDR0 LEDR1 LEDR2 LEDR3 4 3 2 1 RN28 5 6 7 8 120 LEDR3 LEDR1 LEDR2

LEDR LEDR LEDR LEDR

LEDR LEDG0 LEDR LEDR LEDR LEDG0 LEDG1 LEDG2 LEDG3 4 3 2 1 RN25 5 6 7 8 120 LEDG3 LEDR LEDG4 LEDR LEDG LEDG4 LEDG5 LEDG6 LEDG7 4 3 2 1 RN27 5 6 7 8 120 LEDG7 LEDG LEDG5 LEDG6 LEDG LEDG LEDG LEDG LEDG1 LEDG2 LEDG LEDG

C

LEDG

GND BL D7 D6 D5 D4 D3 D2 D1 D0 EN RW RS CONT VCC GND

LEDR10 LEDR11 LEDR12

LEDR LEDR LEDR

B

2 X 16 DIGIT LCD

D65 DNI LCD_DATA6

B

1 3 2

LEDR

LEDR LEDR LEDR LEDR

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number LCD & LED Friday, September 24, 2010 Sheet

1

Rev B 7 of 27

HEX0[6..0]

D

HEX1[6..0] HEX2[6..0] HEX3[6..0] HEX4[6..0] HEX5[6..0] HEX6[6..0] HEX7[6..0]

HEX70 HEX71 HEX72 HEX73

RN3 1 2 3 4 RN2 1 2 3 4

680 8 7 6 5 680 8 7 6 5

HEX7 A7 B7 C7 D7 E7 F7 G7 10 9 8 5 4 2 3 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

HEX30 HEX31 HEX32 HEX33

RN10 1 2 3 4 RN9 1 2 3 4

680 8 7 6 5 680 8 7 6 5

HEX3 A3 10 9 B3 8 C3 5 D3 4 E3 2 F3 3 G3 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

HEX74 HEX75 HEX76 HEX60

7Segment Display

HEX34 HEX35 HEX36 HEX20

7Segment Display

HEX61 HEX62 HEX63 HEX64

RN5 1 2 3 4 RN4 1 2 3 4

680 8 7 6 5 680 8 7 6 5

HEX6 A6 B6 C6 D6 E6 F6 G6 10 9 8 5 4 2 3 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

HEX21 HEX22 HEX23 HEX24

RN12 1 2 3 4 RN11 1 2 3 4

680 8 7 6 5 680 8 7 6 5

HEX2 A2 10 9 B2 8 C2 5 D2 4 E2 2 F2 3 G2 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

HEX65 HEX66 HEX50 HEX51

7Segment Display

HEX25 HEX26 HEX10 HEX11

7Segment Display

HEX5 HEX52 HEX53 HEX54 HEX55 RN6 1 2 3 4 RN8 1 2 3 4 680 8 7 6 5 680 8 7 6 5 A5 B5 C5 D5 E5 F5 G5 10 9 8 5 4 2 3 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

HEX12 HEX13 HEX14 HEX15

RN13 1 2 3 4 RN15 1 2 3 4

680 8 7 6 5 680 8 7 6 5

HEX1 A1 10 9 B1 8 C1 5 D1 4 E1 2 F1 3 G1 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

HEX56 HEX40 HEX41 HEX42

B

7Segment Display

HEX16 HEX00 HEX01 HEX02

7Segment Display

HEX43 HEX44 HEX45 HEX46

RN7 1 2 3 4

680 8 7 6 5

HEX4 A4 B4 C4 D4 E4 F4 G4 10 9 8 5 4 2 3 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

HEX03 HEX04 HEX05 HEX06

RN14 1 2 3 4

680 8 7 6 5

HEX0 A0 10 9 B0 8 C0 5 D0 4 E0 2 F0 3 G0 7

a b c d e f g dp

VCC2P5

CA1 CA2

1 6

7Segment Display

7Segment Display

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number LCD & LED Friday, September 24, 2010 Sheet

1

Rev B 8 of 27

J16 SMA_CLKIN

D

GPIO_VCCIO U20 SMA_CLKOUT GPIO_VCCIO EXT CLOCK R81 DNI VCC3P3 C88 0.1u GPIO_VCCIO C89 0.1u 1 3 5

A

VCC3P3 6 4 2 R80 DNI J15 PLL_CLKOUT

VCCA VCCB B

DIR

GND

SN74AVC1T45

VCC3P3 C84 VCC3P3 0.1u

GPIO_VCCIO C83 0.1u

VCC3P3 4 8 11 16 U16 3 5 7 10 12 14 15

C275 1 0.1u 2

C

Y4 EN GND 50MHZ VCC OUT 4 3 1

VDD

CLOCK_50 CLOCK2_50

VCC3P3 1 3 5

U14

A

GPIO_VCCIO 6 4 2

VCCA VCCB B

CLOCK3_50

C

VCC3P3

DIR

GND

SN74AVC1T45

GND

VCC3P3 VCC3P3

U21

R83 10K OUT VCC GND CHASSIS 1 2 3 47u 4 R82 C90 IRDA_RXD 47

C278 0.1u

2 6 9 13 C276 0.1u C277 0.1u

PI49FCT3803

C279 0.1u

IRM

IRM

VCC3P3

IRM_V538_TR1

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number CLOCK & IrDA Friday, September 24, 2010 Sheet

1

Rev B 9 of 27

RXD1 R18

D

LEDR UART_RXD J6 LEDG UART_TXD U1 UART_RXD UART_RTS UART_TXD UART_CTS C25 C26 1u 1u

330 TXD1 330

VCC3P3 R19

12 9 11 10 1 3 4 5 2 6

C27 1u

R1OUT R2OUT T1IN T2IN

R1IN R2IN T1OUT T2OUT

13 8 14 7

RXD RTS TXD CTS

5 9 4 8 3 7 2 6 1 10 11

RS232

VCC3P3

C+ ZT3232LEEY C1C2+ VCC C2GND V+ V-

16 15

VCC3P3

C12

0.1u

C13

C

C14 1u

0.1u

VCC5

VCC5

VCC5

VCC5

R24 2K PS2_DAT PS2_CLK PS2_DAT2 PS2_CLK2 R21 R20 R22 R23 120 120 120 120

R25 2K

R27 2K

R26 2K KBDAT MSDAT J7

TOP

VCC5 D5 BAT54S C15

KBCLK MSCLK

1 2 3 5 6 8

8 5 2 1

6 3

B

D4 BAT54S

D6 BAT54S

D7 BAT54S

C28 VCC3P3 VCC3P3 VCC3P3 VCC3P3 0.1u

0.1u

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

9 10 11

PS2

Title

DE2-115 Main Board

Size A Date:

5 4 3

Document Number PS2 & RS232 Friday, September 24, 2010

2

Rev B Sheet 10

1

of

27

HSMC_VCCIO RN26 1 2 3 4 100K 8 7 6 5 VCC3P3

U19 GND OE

D

D75 10 19 11 12 13 14 15 16 17 18 RN16 8 7 6 5 10K 1 2 3 4 KEY0 KEY1 KEY2 KEY3 1 3 2 BAT54S D76 1 3 2 BAT54S D77 1 3 2 BAT54S D78 1 3 2 BAT54S KEY3 KEY2 KEY1

D

KEY0

KEYIN0 KEYIN1 KEYIN2 KEYIN3 KEY0 4 1 TACT SW 3 2 4 1 TACT SW KEY1 3 2 4 1 TACT SW KEY2 3 2 4 1 TACT SW VCC3P3 KEYIN0 KEYIN1 KEYIN2 KEYIN3 BUTTON0 4 1 DNI 3 2 4 1 DNI BUTTON1 3 2 4 1 DNI BUTTON2 3 2 4 1 DNI BUTTON3 3 2 KEY3 3 2 C295 1u C294 1u C293 1u C292 1u

9 8 7 6 5 4 3 2 1 20

A8 A7 A6 A5 A4 A3 A2 A1 DIR VCC 74HC245

B8 B7 B6 B5 B4 B3 B2 B1

SW0 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW1 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW2 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW3 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW RN29 8 7 6 5 120 1 2 3 4 SW3 SW2 SW1 SW0

SW4 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW5 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW6 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW7 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW RN30 8 7 6 5 120 1 2 3 4 SW7 SW6 SW5 SW4

SW8 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW9 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW10 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW11 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW RN33 8 7 6 5 120 1 2 3 4 SW11 SW10 SW9 SW8

SW12 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW13 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW14 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW

SW15 4 GND 1HSMC_VCCIO 2 3 GND 5 GND SLIDE SW RN35 8 7 6 5 120 1 2 3 4 SW15 SW14 SW13 SW12

SW16 4 1 2 3 5 SLIDE SW

A

SW17 GND HSMC_VCCIO R241 GND GND 120 SW16 4 1 2 3 5 SLIDE SW

A

GND HSMC_VCCIO R242 GND GND 120 SW17

KEY[3..0] SW[17..0]

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number BUTTON & SWITCH Friday, September 24, 2010 Sheet

1

Rev B 11 of 27

GPIO_VCCIO

D

GPIO_VCCIO D48 1 3IO_D0 3IO_D1 2

GPIO_VCCIO D25 1 3IO_D2 2

GPIO_VCCIO D49 1 3IO_D3 2

GPIO_VCCIO D26 1 3IO_D4 2

GPIO_VCCIO D47 1 3IO_D5 2

GPIO_VCCIO D27 1 3IO_D6 2

GPIO_VCCIO D50 1 3IO_D7 2

GPIO_VCCIO

D

D24 1 2 BAT54S

D52 1 3IO_D8 2 BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

BAT54S

D55 1 3IO_D9 2 BAT54S 2 1

D28 1 3IO_D10 2 BAT54S

D51 1 3IO_D11 2 BAT54S

D29 1 3IO_D12 2 BAT54S

D53 1 3IO_D13 2 BAT54S

D30 1 3IO_D14 2 BAT54S

D56 1 3IO_D15 2 BAT54S

D31 1 3IO_D16 2 BAT54S

D58 3IO_D17 BAT54S

D32 1

C

D54 1 3IO_D18 3IO_D19 2 2 BAT54S 1

D33 1 3IO_D20 2 BAT54S

D57 1 3IO_D21 2 BAT54S

D34 1 3IO_D22 2 BAT54S

D59 1 3IO_D23 2 BAT54S

D35 1 3IO_D24 2 BAT54S

D62 1 3IO_D25 2 BAT54S

D36 3IO_D26 BAT54S

C

2 BAT54S

D60 1 3IO_D27 2 BAT54S 2 1

D37 1 3IO_D28 2 BAT54S

D61 1 3IO_D29 2 BAT54S

D38 1 3IO_D30 2 BAT54S

D63 1 3IO_D31 2 BAT54S

D39 1 3IO_D32 2 BAT54S

D74 1 3IO_D33 2 BAT54S

D73 1 3IO_D34 2 BAT54S

D72 3IO_D35 BAT54S

GPIO[35..0] GPIO JP5 GPIO0 R197 47 IO_D0 R195 DNI GPIO1 GPIO3 GPIO5 GPIO7 GPIO8 GPIO11 GPIO9 GPIO13 RN21 16 15 14 13 12 11 10 9 47 1 2 3 4 5 6 7 8 IO_D1 IO_D3 IO_D5 IO_D7 IO_D8 IO_D11 IO_D9 IO_D13 GPIO2 GPIO4 R198 47 R199 47 IO_D2 IO_D4 R196 DNI GPIO6 GPIO10 R200 47 R208 47 IO_D6 IO_D10 R206 DNI GPIO17 GPIO21 GPIO23 GPIO27 GPIO25 GPIO29 GPIO31 GPIO35

A

GPIO22

R221 47

IO_D22 R218 DNI IO_D0 IO_D2 IO_D4 IO_D6 IO_D8 VCC5 IO_D10 IO_D12 IO_D14 IO_D16 IO_D18 IO_D20 IO_D22 IO_D24 IO_D26 IO_D28 IO_D30 IO_D32 IO_D34 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 IO_D1 IO_D3 IO_D5 IO_D7 IO_D9 IO_D11 IO_D13 IO_D15 IO_D17 IO_D19 IO_D21 IO_D23 IO_D25 IO_D27 IO_D29 IO_D31 IO_D33 IO_D35

GPIO24 GPIO26

R222 47 R230 47

IO_D24 IO_D26 R228 DNI

GPIO28 GPIO30

R231 47 R232 47

IO_D28 IO_D30 R229 DNI Close to FPGA VCC3P3

RN23 16 15 14 13 12 11 10 9

47 1 2 3 4 5 6 7 8

IO_D17 IO_D21 IO_D23 IO_D27 IO_D25 IO_D29 IO_D31 IO_D35

GPIO12 GPIO14

R209 47 R210 47

IO_D12 IO_D14 R207 DNI

GPIO32

R233 47

IO_D32

BOX Header 2X20M GPIO15 GPIO19 R182 47 R183 47 R216 47 R215 47 IO_D15 IO_D19 IO_D34 Title IO_D33 Size B Date:

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

GPIO16 GPIO18

R211 47 R219 47

IO_D16

A

IO_D18 R217 DNI GPIO34 GPIO33

GPIO20

R220 47

IO_D20

DE2-115 Main Board

Document Number GPIO Friday, September 24, 2010 Sheet

1

Rev B 12 of 27

HSMC_TX_D_P[16..0] HSMC_TX_D_N[16..0] HSMC_RX_D_P[16..0] HSMC_RX_D_N[16..0] HSMC_D[3..0] EX_IO[6..0] JP8 VCC3P3

D D

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 HSMC_SDA E_HSMC_TCK E_HSMC_TDO HSMC_CLKOUT0 33 35 37 39

1 3 161 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 164

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40

2 4 6 8 10 12 14 16 18 20 22 24 26 28 VCC2P5 30 32 34 36 38 40 HSMC_SCL E_HSMC_TMS E_HSMC_TDI E_HSMC_CLKIN0 E_HSMC_TMS E_HSMC_TCK E_HSMC_TDI E_HSMC_TDO R147 10K VCC2P5 1 2 3 4 5 8 U22

VCCA VCCB

R181 2.2K VCC3P3 GPIO_VCCIO U25 HSMC_CLKIN0 1 3 5

VCCA VCCB A DIR B GND

R171 2.2K

R170 2.2K

R169 2.2K

R168 2.2K

R159 2.2K

JP4 14 12 10 8 6 4 2 13 11 9 7 5 3 1 EX_IO0 EX_IO1 EX_IO2 EX_IO3 R160 33 EX_IO5 EX_IO6

HSMC_VCCIO 6 4 2

GPIO_VCCIO C184

HSMC_VCCIO C183 0.1u

EX_IO4

E_HSMC_CLKIN0 0.1u

162

SN74AVC1T45

HEADER 7X2

R158 2.2K

163

VCC3P3 14 13 12 11 10 7 HSMC_TMS HSMC_TCK HSMC_TDI HSMC_TDO

OE

GND

VCC2P5 161 162 163 164 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99 169 170 171 172 HSMC_TX_D_p8 HSMC_TX_D_n8 HSMC_TX_D_p9 HSMC_TX_D_n9 HSMC_TX_D_p10 HSMC_TX_D_n10 HSMC_TX_D_p11 HSMC_TX_D_n11 HSMC_TX_D_p12 HSMC_TX_D_n12 HSMC_TX_D_p13 HSMC_TX_D_n13 HSMC_TX_D_p14 HSMC_TX_D_n14 HSMC_TX_D_p15 HSMC_TX_D_n15 HSMC_TX_D_p16 HSMC_TX_D_n16 HSMC_CLKOUT_P2 HSMC_CLKOUT_N2 101 103 105 107 109 111 113 115 117 119 121 123 125 127 129 131 133 135 137 139 141 143 145 147 149 151 153 155 157 159 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99 169 170 171 172 101 103 105 107 109 111 113 115 117 119 121 123 125 127 129 131 133 135 137 139 141 143 145 147 149 151 153 155 157 159 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80 82 84 86 88 90 92 94 96 98 100 165 166 167 168 102 104 106 108 110 112 114 116 118 120 122 124 126 128 130 132 134 136 138 140 142 144 146 148 150 152 154 156 158 160 161 162 163 164 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80 82 84 86 88 90 92 94 96 98 100 165 166 167 168 102 104 106 108 110 112 114 116 118 120 122 124 126 128 130 132 134 136 138 140 142 144 146 148 150 152 154 156 158 160 HSMC_RX_D_p8 HSMC_RX_D_n8 HSMC_RX_D_p9 HSMC_RX_D_n9 HSMC_RX_D_p10 HSMC_RX_D_n10 HSMC_RX_D_p11 HSMC_RX_D_n11 HSMC_RX_D_p12 HSMC_RX_D_n12 HSMC_RX_D_p13 HSMC_RX_D_n13 HSMC_RX_D_p14 HSMC_RX_D_n14 HSMC_RX_D_p15 HSMC_RX_D_n15 HSMC_RX_D_p16 HSMC_RX_D_n16 HSMC_CLKIN_P2 HSMC_CLKIN_N2 HSMC_PSNT_n VCC3P3 HSMC_D1 HSMC_D3 HSMC_RX_D_P0 HSMC_RX_D_N0 HSMC_RX_D_P1 HSMC_RX_D_N1 HSMC_RX_D_P2 HSMC_RX_D_N2 HSMC_RX_D_P3 HSMC_RX_D_N3 JP3 HSMC_RX_D_P4 HSMC_RX_D_N4 HSMC_RX_D_P5 HSMC_RX_D_N5 HSMC_RX_D_P6 HSMC_RX_D_N6 HSMC_RX_D_P7 HSMC_RX_D_N7 HSMC_CLKIN_P1 HSMC_CLKIN_N1 1 2 3 HEADER 3 VCC12 C172 0.1u

15

TXS0104ERGYR VCC3P3 C171 0.1u

C

VCC3P3

C

HSMC_D0 HSMC_D2 HSMC_TX_D_P0 HSMC_TX_D_N0 HSMC_TX_D_P1 HSMC_TX_D_N1 HSMC_TX_D_P2 HSMC_TX_D_N2 HSMC_TX_D_P3 HSMC_TX_D_N3 HSMC_TX_D_P4 HSMC_TX_D_N4 HSMC_TX_D_P5 HSMC_TX_D_N5 HSMC_TX_D_P6 HSMC_TX_D_N6 HSMC_TX_D_P7 HSMC_TX_D_N7 HSMC_CLKOUT_P1 HSMC_CLKOUT_N1

VCC12

VCC3P3

165

C241 22u

C180 10u

C179 0.1u

C182 10u

C181 0.1u

166

HSMC_TDI JTAG_TDO HSMC_TDO

167

Short pin1 and pin2: JTAG chain not including HSMC Short pin2 and pin3: JTAG chain including HSMC

168

170

169

171

R77 120 D40 LEDG HSMC_PSNT_n

172

HSMC

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size C Date:

5 4 3 2

Document Number HSMC Friday, September 24, 2010

1

Rev B Sheet 13 of 27

VCC3P3 VCC3P3

R165 R163 R161 DNI DNI DNI

VCC3P3 U24

1 2 3 4

A0 A1 A2 VSS

VCC WP SCL SDA

8 7 6 5

R150 2K

R149 2K EEP_I2C_SCLK EEP_I2C_SDAT

VCC3P3 C173 0.1u

C

R166 R164 24LC32A 1K 1K R162 1K I2C ADDRESS W/R = 0xA0/0xA1

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size A Date:

5 4 3

Document Number EEPROM Friday, September 24, 2010

2

Rev B Sheet 14

1

of

27

ENET_VCC2P5 VCC2P5 R32

D

26 48

52 66 72

0 0 A0_VCC2P5 32 36 35 40 45 78 ENET0_VCC1P2 1 6 10 15 57 62 67 71 85 29 31 33 34 39 41 42 43 24 25 23 37 38 ENET0_RST_N 27 28 30 56 22 55 54 47 49 46 44 50 53

U8

5 21 88 96

ENET_VCC2P5

ENET_VCC2P5 L12

A0_VCC2P5 BEAD

ENET0_TX_DATA[3..0] ENET0_RX_DATA[3..0]

VDDOH VDDOH VDDOH

VDDOX VDDOX

R33

VDDO VDDO VDDO VDDO

VCC2P5 U23 1 VCCA 2 ENET_25MHZ ENET0_LED_LINK100 3 4 ENET1_LED_LINK100 5 8 R148 10K VCC2P5 OE

VCC3P3

VCCB

GND

14 13 12 11 10 7

ENETCLK_25 ENET0_LINK100 ENET1_LINK100

D

AVDD AVDD AVDD AVDD AVDD AVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD MDI0_p MDI0_n MDI1_p MDI1_n MDI2_p MDI2_n MDI3_p MDI3_n MDIO MDC INT_n HSDAC_p HSDAC_n COMA RESET_n RSET SEL_FREQ 125CLK XTAL1 XTAL2 TRST_n TCK TMS TDI TDO VSSC

2.5V

GTX_CLK TX_CLK TX_EN TX_ER TXD0 TXD1 TXD2 TXD3 TXD4 TXD5 TXD6 TXD7 RXCLK RX_DV RX_ER RXD0 RXD1 RXD2 RXD3 RXD4 RXD5 RXD6 RXD7 CRS COL S_CLK_p S_CLK_n S_IN_p S_IN_n S_OUT_p S_OUT_n CONFIG0 CONFIG1 CONFIG2 CONFIG3 CONFIG4 CONFIG5 CONFIG6 LED_TX LED_RX LED_DUPLEX LED_LINK1000 LED_LINK100 LED_LINK10

8 4 9 7 11 12 14 16 17 18 19 20 2 94 3 95 92 93 91 90 89 87 86 84 83 79 80 82 81 77 75 65 64 63 61 60 59 58 68 69 70 73 74 76

ENET0_GTX_CLK ENET0_TX_CLK ENET0_TX_EN ENET0_TX_ER ENET0_TX_DATA0 ENET0_TX_DATA1 ENET0_TX_DATA2 ENET0_TX_DATA3

VCC2P5 C174 0.1u

15

TXS0104ERGYR VCC3P3 C176 0.1u

VCC1P2 L15

ENET0_VCC1P2 BEAD

R35 22 ENET0_RX_DV ENET0_RX_ER ENET0_RX_DATA0 ENET0_RX_DATA1 ENET0_RX_DATA2 ENET0_RX_DATA3 ENET0_RX_CLK

ENET_VCC2P5 J4 Jack-RJ45-8P10C-B 9 VCC 1 MX(0)+ MX(0)+ 2 MX(0) MX(0) 3 MX(1)+ MX(1)+ 6 MX(1) MX(1) 4 MX(2)+ MX(2)+ 5 MX(2) MX(2) 7 MX(3)+ MX(3)+ 8 MX(3) MX(3) 10 GND

CMR CHOKES

MDI INTERFACE

ENET0_MDI_p0 ENET0_MDI_n0 ENET0_MDI_p1 ENET0_MDI_n1 ENET0_MDI_p2 ENET0_MDI_n2 ENET0_MDI_p3 ENET0_MDI_n3 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 ENET0_MDIO ENET0_MDC ENET0_INT_N

GMII/MII/TBI

JP1 1 2 3 ENET0_LED_DUPLEX ENET0_CONFIG4 ENET_VCC2P5 R37 DNI

C

SHIELED

MGMT

12

11

ENET0_RX_CRS ENET0_RX_COL

HEADER 3

TEST

R9

R8

R7

R6

R5

R4

R3

R2

Short pin1 and pin2: RGMII mode Short pin2 and pin3: MII mode

SGMII

ENET_VCC2P5

C7 10n

C6 10n

C5 10n

C4 10n

ENET_VCC2P5 LEDG ENET_VCC2P5 ENET0_CONFIG4 D12 NET0_TX LEDG D13 NET0_RX LEDG ENET0_LED_TX ENET0_LED_RX ENET0_LED_DUPLEX ENET0_LED_LINK1000 ENET0_LED_LINK100 ENET0_LED_LINK10 D14 NET0_DUP LEDG D15 NET0_1K LEDG D16 NET0_100 LEDG D17 NET0_10 RN20 8 7 6 5 120 1 2 3 4

B

ENET0_RSET

R142 R141

120 120

C138 1 0.1u 2

B

Y2 EN GND 25MHZ VCC OUT 4 3 ENET_25MHZ ENET_VCC2P5 RN18 1 2 3 4 R121 R122

ENET_25MHZ ENET0_TRST_N

4.99K ENET0_RSET 4.7K ENET0_TRST_N

PHYADR[4:0]=10000b

ENET_VCC2P5 A0_VCC2P5 ENET0_VCC1P2

C17 10u

A

C19 0.1u

C40 0.1u

C18 0.1u

C37 0.1u

C34 0.1u

C142 C139 10u 0.1u

C140 0.1u

C141 0.1u

C168 10u

C38 0.1u

C39 0.1u

C20 0.1u

C35 0.1u

C36 0.1u

A

97

88E1111

VSS

4.7K 8 7 6 5

ENET0_RST_N ENET0_MDC ENET0_MDIO ENET0_INT_N

JTAG

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number Ethernet 0 Friday, September 24, 2010 Sheet

1

Rev B 15 of 27

ENET_VCC2P5 ENET_VCC2P5 L11 A1_VCC2P5 BEAD A1_VCC2P5

D

ENET1_TX_DATA[3..0] 26 48 52 66 72 5 21 88 96 U9 ENET1_RX_DATA[3..0]

VDDOH VDDOH VDDOH

VDDOX VDDOX

32 36 35 40 45 78 VCC1P2 L14 ENET1_VCC1P2 BEAD ENET1_VCC1P2 1 6 10 15 57 62 67 71 85 29 31 33 34 39 41 42 43 24 25 23 37 38 ENET1_RST_N C11 10n C10 10n C9 10n C8 10n ENET1_RSET 27 28 30 56 22 55 54 47 49 46 44 50 53

VDDO VDDO VDDO VDDO

AVDD AVDD AVDD AVDD AVDD AVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD MDI0_p MDI0_n MDI1_p MDI1_n MDI2_p MDI2_n MDI3_p MDI3_n MDIO MDC INT_n HSDAC_p HSDAC_n COMA RESET_n RSET SEL_FREQ 125CLK XTAL1 XTAL2 TRST_n TCK TMS TDI TDO VSSC

2.5V

GTX_CLK TX_CLK TX_EN TX_ER TXD0 TXD1 TXD2 TXD3 TXD4 TXD5 TXD6 TXD7 RXCLK RX_DV RX_ER RXD0 RXD1 RXD2 RXD3 RXD4 RXD5 RXD6 RXD7 CRS COL S_CLK_p S_CLK_n S_IN_p S_IN_n S_OUT_p S_OUT_n CONFIG0 CONFIG1 CONFIG2 CONFIG3 CONFIG4 CONFIG5 CONFIG6 LED_TX LED_RX LED_DUPLEX LED_LINK1000 LED_LINK100 LED_LINK10

8 4 9 7 11 12 14 16 17 18 19 20 2 94 3 95 92 93 91 90 89 87 86 84 83 79 80 82 81 77 75 65 64 63 61 60 59 58 68 69 70 73 74 76

ENET1_GTX_CLK ENET1_TX_CLK ENET1_TX_EN ENET1_TX_ER ENET1_TX_DATA0 ENET1_TX_DATA1 ENET1_TX_DATA2 ENET1_TX_DATA3

R36 22 ENET1_RX_DV ENET1_RX_ER ENET1_RX_DATA0 ENET1_RX_DATA1 ENET1_RX_DATA2 ENET1_RX_DATA3 JP2 1 2 3 HEADER 3 ENET1_RX_CRS ENET1_RX_COL ENET1_LED_DUPLEX R38 ENET1_CONFIG4 ENET_VCC2P5 DNI ENET1_RX_CLK

ENET_VCC2P5 J5 Jack-RJ45-8P10C-B 9 VCC 1 MX(0)+ MX(0)+ 2 MX(0) MX(0) 3 MX(1)+ MX(1)+ 6 MX(1) MX(1) 4 MX(2)+ MX(2)+ 5 MX(2) MX(2) 7 MX(3)+ MX(3)+ 8 MX(3) MX(3) 10 GND

CMR CHOKES

MDI INTERFACE

ENET1_MDI_p0 ENET1_MDI_n0 ENET1_MDI_p1 ENET1_MDI_n1 ENET1_MDI_p2 ENET1_MDI_n2 ENET1_MDI_p3 ENET1_MDI_n3 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 ENET1_MDIO ENET1_MDC ENET1_INT_N

GMII/MII/TBI

SHIELED

MGMT

Short pin1 and pin2: RGMII mode Short pin2 and pin3: MII mode

12

11

TEST

R17

R16

R15

R14

R13

R12

R10

R11

SGMII

ENET_VCC2P5 LEDG ENET_VCC2P5 ENET1_CONFIG4 D18 NET1_TX LEDG D19 NET1_RX LEDG ENET1_LED_TX ENET1_LED_RX ENET1_LED_DUPLEX ENET1_LED_LINK1000 ENET1_LED_LINK100 ENET1_LED_LINK10 ENET1_LED_LINK100 D20 NET1_DUP LEDG D21 NET1_1K LEDG D22 NET1_100 LEDG D23 NET1_10 RN19 8 7 6 5 120 1 2 3 4 R139 120 R140 120

ENET_25MHZ ENET_25MHZ ENET_VCC2P5 RN17 1 2 3 4 ENET1_TRST_N

4.7K 8 7 6 5

ENET1_RST_N ENET1_MDC ENET1_MDIO ENET1_INT_N

JTAG

R119 R120

4.99K ENET1_RSET ENET1_TRST_N 4.7K

PHYADR[4:0]=10001b

ENET_VCC2P5 A1_VCC2P5 ENET1_VCC1P2

C21 10u

A

C47 0.1u

C22 0.1u

C41 0.1u

C23 0.1u

C44 0.1u

C137 10u

C136 0.1u

C135 0.1u

C134 0.1u

C167 10u

C24 0.1u

C45 0.1u

C46 0.1u

C42 0.1u

C43 0.1u

A

97

88E1111

VSS

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number Ethernet 1 Friday, September 24, 2010 Sheet

1

Rev B 16 of 27

VGA_R7 VGA_R6 VGA_R5 VGA_R4 VGA_R3 VGA_R2 VGA_R1 VGA_R0

VGA_VCC3P3

D

R101 R100 RSET

4.7K 560 C109 0.1u C108 0.1u

VGA_G0 VGA_G1 VGA_G2 VGA_G3 VGA_G4 VGA_G5 VGA_G6 VGA_G7 VGA_BLANK_N VGA_SYNC_N

1 2 3 4 5 6 7 8 9 10 11 12

R9 R8 R7 R6 R5 R4 R3 R2 R1 R0 PSAVE RSET

VGA_R[7..0] VGA_G[7..0] VGA_B[7..0]

U7

48 47 46 45 44 43 42 41 40 39 38 37

VAA B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 CLOCK

G0 G1 G2 G3 G4 G5 G6 G7 G8 G9 BLANK SYNC

ADV7123

VREF COMP IOR IOR IOG IOG VAA VAA IOB IOB GND GND

36 35 34 33 32 31 30 29 28 27 26 25

J13 VGA_R VGA_G VGA_B VGA_VCC3P3 R99 75 R98 75 R97 75

VGA_HS VGA_VS

R96 R95

47 47

13 14 15 16 17 18 19 20 21 22 23 24

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

6 1 11

10 5 15

VGA

16

C105 0.1u

VGA_B0 VGA_B1 VGA_B2 VGA_B3 VGA_B4 VGA_B5 VGA_B6 VGA_B7 VGA_CLK

17

VGA_VCC3P3

VCC3P3 R123

VGA_VCC3P3 0 C143 10u

VGA_VCC3P3

C107 0.1u

C106 0.1u

C144 0.1u

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size A Date:

5 4 3

Document Number ADV7123 VGA Friday, September 24, 2010

2

Rev B Sheet 17

1

of

27

V_VCC3P3 VGND 2 1

V_VCC3P3 V_VCC1P8 D41 BAT54S AV_VCC1P8 PV_VCC1P8 C113 0.1u 14 36 U6 C118 0.1u VGND TD_RESET_N 23 29 30 31 26 C116 C115 0.1u 0.1u 25 13 12 32 V_VCC3P3 18 34 33 27 20 1 4 C112 10n ELPF P0 P1 P2 P3 P4 P5 P6 P7 VS/FIELD HS SFL INTRQ LLC TEST_0 19 17 16 10 9 8 7 6 5 37 39 2 38 11 22 C147 10u C148 10u L8 BEAD VGND RN1 1 2 3 4 5 6 7 8 R126 R127 47 16 15 14 13 12 11 10 9 120 120 TD_DATA0 TD_DATA1 TD_DATA2 TD_DATA3 TD_DATA4 TD_DATA5 TD_DATA6 TD_DATA7 TD_VS TD_HS VCC3P3 TD_CLK27 R124 0 R125 0

C

TD_DATA[7..0]

D

R102 1.74K V_VCC3P3

DVDD DVDD

J12 RCA JACK

R104 R103 VGND

36 39

AIN1 AIN2 AIN3 RESET VREFN VREFP XTAL XTAL1 ALSB

DVDDIO DVDDIO

AVDD PVDD

C145 1 0.1u 2

Y1 EN GND VCC OUT 4 3 28MHz

C149 0.1u

ADV7180

28.63636MHZ

28MHz

V_VCC3P3

VCC1P8

V_VCC1P8

PWRDWN SCLK SDATA DGND DGND DGND DGND EXPOSED AGND AGND AGND VGND

I2C_SCLK I2C_SDAT

I2C ADDRESS W/R = 0x40/0x41

3 15 35 40 41 21 24 28

PV_VCC1P8 L6 C111 10u VGND

B

V_VCC1P8 BEAD C146 0.1u L7 C150 0.1u

AV_VCC1P8 BEAD C114 0.1u VGND

B

C110 0.1u VGND

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number ADV7180 DECODER Friday, September 24, 2010 Sheet

1

Rev B 18 of 27

J2

LINE IN

C91

1u C92 1u R84 4.7K

R85 R86 R87 4.7K

4.7K 4.7K

NCL R NCR L GND

VCC3P3 VCC3P3

R129 2K I2C_SDAT I2C_SCLK

R128 AGND 2K AGND R90 330 C94 1u AGND J1 MIC IN

I2C ADDRESS = 0x34 (write only) U5

C

28 27 26 25 24 23 22

NCL R NCR L GND

5 2 4 1 3

PHONE JACK B

5 2 4 1 3

PHONE JACK P

C

A_VCC3P3

AGND

1 2 3 4 5 6 7

SCLK SDIN CSB MODE LLINEIN RLINEIN MICIN

EXPOSED DACDAT DACLRCK ADCDAT ADCLRCK HPVDD LHPOUT RHPOUT

NCL R NCR L GND 5 2 4 1 3

PHONE JACK G

XTI/MCLK XTO DCVDD DGND DBVDD CLKOUT BCLK

WM8731

MBIAS VMID AGND AVDD ROUT LOUT HPGND

21 20 19 18 17 16 15

R88 C120 10u AGND A_VCC3P3 AGND

680 C93 1n AGND R89 AGND 47K J3 AGND LINE OUT

AUD_XCK AUD_BCLK AUD_DACDAT AUD_DACLRCK AUD_ADCDAT AUD_ADCLRCK

29 8 9 10 11 12 13 14

AGND

C2

100u C3 100u R106 47K R105 47K AGND

A_VCC3P3

VCC3P3 L13

A_VCC3P3 BEAD C151 AGND L9 BEAD C119 0.1u

A_VCC3P3 AGND C153 0.1u C117 0.1u C152 0.1u Title

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

AGND

10u AGND

AGND Size A Date:

5 4 3

DE2-115 Main Board

Document Number WM8731 Audio Friday, September 24, 2010

2

Rev B Sheet 19

1

of

27

H_VCC5 U_VCC3P3 2 1

D

H_VCC5 2 1

D

OTG_DATA[15..0] U4 58 52 40 26 14 4 U_VCC5

D43 BAT54S 3 3 L5 33 34 56 41 36 46 47 42 35 49 50 48 45 55 54 53 39 60 59 23 38 3 43 44 OTG_FSPEED OTG_LSPEED R93 R94 1.5K 1.5K O_VCC5 L10 BEAD C101 47p R108 R107 4.7K 4.7K U_VCC3P3 U_VCC5 C97 47p R109 R110 22 22 R91 R112 R111 22 22 15K R92 15K BEAD H_VCC5

D44 BAT54S J11 1 2 3 4 C98 USB A-TYPE 6 C99 0.1u 5 47p

OTG_ADDR1 OTG_ADDR0 OTG_DATA15 OTG_DATA14 OTG_DATA13 OTG_DATA12 OTG_DATA11 OTG_DATA10 OTG_DATA9 OTG_DATA8 OTG_DATA7 OTG_DATA6 OTG_DATA5 OTG_DATA4 OTG_DATA3 OTG_DATA2 OTG_DATA1 OTG_DATA0 R131 4.7K OTG_CS_N OTG_WR_N OTG_RD_N OTG_INT1 OTG_INT0 OTG_RST_N OTG_DREQ1 OTG_DACK_N1 OTG_DREQ0 OTG_DACK_N0

62 61 18 17 16 15 13 12 11 10 8 7 6 5 3 2 64 63 21 22 20 31 30 32 25 29 24 28

A1 A0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 CS WR RD INT2 INT1 RESET DREQ2 DACK2 DREQ1 DACK1

H_SUSPEND/H_SUSWKUP H_SUSPEND/D_SUSWKUP VDD_5V H_OC2 H_PSW2 H_DM2 H_DP2 H_OC1 H_PSW1 OTG_DM1 OTG_DP1 ISP1362 ID OTGMODE VBUS CP_CAP2 CP_CAP1 GL TEST2 TEST1 TEST0 CLKOUT X1 X2 DGND DGND DGND DGND DGND DGND AGND

VCC VCC VCC VCC VCC VCC

C155 0.1u LEDG R117 R133 R132 R130 330 D2 10K 10K 100K U_VCC3P3 O_VCC5 2 1 O_VCC5 2 1

U_VCC3P3

GOOD

U_VCC3P3

D46 BAT54S 3

D45 BAT54S J10 3 2 1 4 C100 47p C102 0.1u

DD+

VBUS GND

57 37 27 19 9 1

51

USB B-TYPE 6 5

USB_12MHz

B B

VCC5 R134

U_VCC5 0 C158 10u C122 0.1u

VCC3P3 R138

U_VCC3P3 0 C164 10u C121 10n C154 10n

U_VCC3P3

H_VCC5

O_VCC5

C162 10n

C163 10n

C156 10n

C157 10n

C96 0.1u

C95 100u

C133 0.1u

C132 10u

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number ISP1362 Friday, September 24, 2010 Sheet

1

Rev B 20 of 27

SRAM_ADDR[19..0] DRAM_DQ[31..0]

D

OTG_DATA[15..0] DRAM_ADDR[12..0] LCD_DATA[7..0] DRAM_DQM[3..0] U12B U12A AUD_ADCLRCK AUD_ADCDAT AUD_DACDAT PS2_CLK PS2_CLK2 AUD_DACLRCK OTG_DATA14 PS2_DAT2 OTG_DATA15 OTG_DATA12 OTG_DATA9 OTG_DATA8 AUD_XCK AUD_BCLK OTG_DATA13 OTG_DATA4 OTG_DATA5 OTG_DATA11 OTG_DATA10 LCD_DATA5 LCD_DATA4 OTG_DATA1 OTG_DATA3 LCD_EN LCD_DATA0 DRAM_DQ21 LCD_DATA6 OTG_DATA0 OTG_DATA2 OTG_DATA6 LCD_DATA3 DRAM_DQM2 DRAM_DQ17 DRAM_DQ23 LCD_BLON DRAM_DQ20 DRAM_DQ19 DRAM_DQ16 DRAM_DQ22 LCD_DATA2 LCD_DATA1 LCD_RS LCD_RW DRAM_DQ18 DRAM_ADDR3 C2 D2 D1 G6 G5 E3 F3 F5 G4 G3 H4 H3 E1 F2 F1 J4 J3 G2 G1 K2 K1 K4 K3 L4 L3 M4 M3 J6 J5 J7 K7 K8 L8 L7 L6 N4 N3 M8 M7 L2 L1 M2 M1 P2 P1 DIFFIO_L1n/DQ2L DIFFIO_L2p/DQ2L DIFFIO_L2n/DQ2L DIFFIO_L3p/DQ2L/nRESET DIFFIO_L3n/DQ2L DIFFIO_L4p/DQS2L/CQ3L,CDPCLK0 DIFFIO_L4n/DQ2L DIFFIO_L5p/DQ2L DIFFIO_L6p/DQ2L DIFFIO_L6n DIFFIO_L7p DIFFIO_L7n DIFFIO_L8n DIFFIO_L9p/DM2L DIFFIO_L9n/DQ0L DIFFIO_L10p DIFFIO_L10n/DQ0L DIFFIO_L11p/DQ0L DIFFIO_L11n DIFFIO_L12p/DQS0L/CQ1L,DPCLK0 DIFFIO_L12n/DQOL DIFFIO_L13p DIFFIO_L13n DIFFIO_L14p DIFFIO_L14n DIFFIO_L15p DIFFIO_L15n DIFFIO_L16p DIFFIO_L16n DIFFIO_L17p DIFFIO_L17n DIFFIO_L18p DIFFIO_L18n DIFFIO_L19p DIFFIO_L19n DIFFIO_L20p DIFFIO_L20n DIFFIO_L21p DIFFIO_L21n DIFFIO_L22p DIFFIO_L22n/DQ0L DIFFIO_L23p DIFFIO_L23n/DQ0L DIFFIO_L24p DIFFIO_L24n/DQ0L EP4CE115F29 IO_0 IO_1 IO_2 VREFB1N0 VREFB1N1 VREFB1N2 DRAM_DQ27 DRAM_DQ26 DRAM_DQ25 DRAM_ADDR0 DRAM_DQ7 DRAM_DQ30 DRAM_DQ28 DRAM_BA1 DRAM_CS_N DRAM_DQ29 DRAM_DQM0 DRAM_DQ31 DRAM_DQ2 DRAM_DQ4 DRAM_DQ5 DRAM_DQ6 DRAM_DQ12 DRAM_DQ10 DRAM_DQ1 DRAM_DQ3 DRAM_RAS_N DRAM_DQ24 DRAM_DQ9 DRAM_DQ8 DRAM_DQ15 DRAM_DQ13 SRAM_ADDR13 SRAM_ADDR11 SRAM_DQ9 SRAM_DQ8 SRAM_ADDR14 DRAM_DQ11 SRAM_DQ10 SRAM_DQ11 DRAM_WE_N DRAM_ADDR4 DRAM_ADDR1 DRAM_CAS_N DRAM_DQM1 DRAM_DQ0 DRAM_ADDR9 DRAM_ADDR8 DRAM_ADDR5 DRAM_ADDR12 DRAM_CKE DRAM_ADDR11 SRAM_DQ12 SRAM_ADDR10 SRAM_ADDR7 SRAM_UB_N SRAM_ADDR4 SRAM_ADDR6 R2 R1 R7 R6 U3 U4 R3 R4 T4 T3 U2 U1 V4 V3 V2 V1 AB2 AB1 W2 W1 U6 U5 Y4 Y3 AC2 AC1 AC3 AD3 AD2 AD1 AA4 AA3 AE2 AE1 V6 V5 V8 V7 W4 W3 Y6 Y5 W8 Y7 AA6 AA5 AE3 AF2 AC5 AC4 AB6 AB5 DIFFIO_L25p/DQ0L DIFFIO_L25n DIFFIO_L26p DIFFIO_L26n DIFFIO_L27p/DM0L DIFFIO_L27n DIFFIO_L28p/DQ1L DIFFIO_L28n/DQ1L DIFFIO_L29p/DQ1L DIFFIO_L29n DIFFIO_L30p DIFFIO_L30n/DQ1L DIFFIO_L31p/DQ1L DIFFIO_L31n DIFFIO_L32p/DQ1L DIFFIO_L32n/DQ1L DIFFIO_L33p/DQS1L/CQ1L#,DPCLK1 DIFFIO_L33n DIFFIO_L34p/DQ1L DIFFIO_L34n/DM1L/BWS#1L DIFFIO_L35p/DQ3L DIFFIO_L35n DIFFIO_L36p/DQ3L DIFFIO_L36n DIFFIO_L37p/DQ3L DIFFIO_L37n/DQ3L DIFFIO_L38p/DQ3L DIFFIO_L38n DIFFIO_L39p/DQ3L DIFFIO_L39n DIFFIO_L40p/DQ3L DIFFIO_L40n SRAM_DQ[15..0]

H6 H5 N8 H7 L5 M5

OTG_DATA7 PS2_DAT DRAM_DQM3 OTG_ADDR0 LCD_ON LCD_DATA7

BANK2

IO_0/DQ1L IO_1/DQ3L IO_2 IO_3

R5 AB3 W7 AA7

DRAM_ADDR10 DRAM_DQ14 DRAM_ADDR6 DRAM_ADDR7

BANK1

RUP1 RDN1 VREFB2N0 VREFB2N1 VREFB2N2

U7 U8 T7 T8 AB4

DRAM_BA0 DRAM_ADDR2 SRAM_ADDR9 SRAM_ADDR19 SRAM_ADDR12

DIFFCLK_0n/CLK1

J1

OTG_DREQ0

DIFFIO_L41p/DQ3L DIFFIO_L41n DIFFIO_L42p DIFFIO_L42n DIFFIO_L43P DIFFIO_L43n DIFFIO_L44p DIFFIO_L44n DIFFIO_L45p DIFFIO_L45n DIFFIO_L46p DIFFIO_L46n DIFFIO_L47p DIFFIO_L47n DIFFIO_L48p/DQS3L/CQ3L#,CDPCLK1 DIFFIO_L48n/DM3L/BWS#3L DIFFIO_L49p DIFFIO_L49n DIFFIO_L50p DIFFIO_L50n EP4CE115F29

DIFFCLK_1p/CLK2 DIFFCLK_1n/CLK3

Y2 Y1

CLOCK_50 FL_RY

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number EP4CE115 BANK 1 and BANK 2 Friday, September 24, 2010 Sheet

1

Rev B 21 of 27

HEX7[6..0] HEX6[6..0] HEX5[6..0]

D

HEX4[6..0] GPIO[35..0] HEX3[6..0] FL_DQ[7..0] SRAM_ADDR[19..0] SRAM_DQ[15..0] FL_ADDR[22..0] SD_DAT[3..0] U12C SRAM_OE_N SRAM_ADDR5 SRAM_LB_N SRAM_DQ1 SRAM_DQ13 SRAM_DQ15 SRAM_DQ0 SRAM_DQ14 SRAM_DQ2 SRAM_DQ3 FL_ADDR13 SRAM_ADDR3 SRAM_DQ5 SRAM_DQ6 SRAM_ADDR17 SRAM_ADDR18 FL_CE_N FL_ADDR1 SRAM_ADDR0 FL_ADDR14 FL_ADDR16 FL_ADDR12 FL_OE_N FL_DQ0 SRAM_ADDR2 SRAM_DQ7 SRAM_WE_N SRAM_CE_N FL_ADDR20 FL_DQ1 FL_DQ2 FL_DQ3 AD5 AE6 AD4 AF4 AE4 AG3 AH3 AF3 AG4 AH4 AD8 AC7 AG6 AH6 AB9 AB8 AG7 AH7 AB7 AC8 AA8 AA10 AG8 AH8 AE7 AF7 AE8 AF8 AE10 AF10 AG10 AH10 U12D DIFFIO_B1p DIFFIO_B1n/DM1B DIFFIO_B2p DIFFIO_B2n/DQ1B DIFFIO_B3p DIFFIO_B3n/DQ1B DIFFIO_B4p/DQ1B DIFFIO_B4n DIFFIO_B5p DIFFIO_B5n/DQ1B DIFFIO_B6p/DQ1B DIFFIO_B6n DIFFIO_B7p/DQ1B DIFFIO_B7n/DQ1B DIFFIO_B8p/DM3B/BWS#3B DIFFIO_B8n DIFFIO_B25p DIFFIO_B25n DIFFIO_B26p DIFFIO_B26n DIFFIO_B27p DIFFIO_B27n DIFFIO_B28p/DQ5B DIFFIO_B28n DIFFIO_B29p DIFFIO_B29n DIFFIO_B30p DIFFIO_B30n Y12 AA12 Y13 AA13 AA14 AB14 AG12 AH12 AC14 AD14 Y14 Y15 FL_ADDR4 FL_ADDR6 FL_ADDR2 FL_ADDR5 HEX76 SD_DAT2 FL_ADDR0 FL_ADDR17 SD_DAT3 SD_CMD FL_ADDR3 IRDA_RXD GPIO1 GPIO8 GPIO9 GPIO13 HEX72 HEX73 GPIO7 GPIO11 HEX62 HEX61 HEX71 HEX74 HEX75 HEX56 HEX54 HEX53 HEX66 HEX70 HEX42 HEX43 HEX46 HEX55 GPIO26 GPIO28 GPIO31 GPIO34 HEX44 HEX45 GPIO14 GPIO16 GPIO30 GPIO32 GPIO15 GPIO19 GPIO25 GPIO29 GPIO22 GPIO24 GPIO10 GPIO12 GPIO3 GPIO5 GPIO18 GPIO20 HEX40 HEX52 GPIO23 GPIO27 AC15 AD15 AE15 AF15 AG17 AH17 AE16 AF16 AA16 AB16 AE17 AF17 AG18 AH18 AG19 AH19 AC17 AD17 AG21 AH21 AE18 AF18 AG22 AH22 AG23 AH23 AE19 AF19 AF24 AF25 AE20 AF20 AE21 AF21 AE25 AF26 AG25 AH25 AC19 AD19 Y17 Y16 AE22 AF22 AB19 AB18 AD25 AE24 DIFFIO_B31p/DM4B DIFFIO_B31n DIFFIO_B32p DIFFIO_B32n/DQ4B DIFFIO_B33p/DQ4B DIFFIO_B33n/DQ4B DIFFIO_B34p DIFFIO_B34n/DQ4B DIFFIO_B35p DIFFIO_B35n/DQ4B DIFFIO_B36p/DQ4B DIFFIO_B36n/DQS4B/CQ5B,DPCLK4 DIFFIO_B37p/DQ4B DIFFIO_B37n/DQ4B DIFFIO_B38p DIFFIO_B38n/DM2B DIFFIO_B39p DIFFIO_B39n/DQ2B DIFFIO_B40p/DQ2B DIFFIO_B40n/DQ2B DIFFIO_B41p/DQS2B/CQ3B,DPCLK5 DIFFIO_B41n DIFFIO_B42p/DQ2B DIFFIO_B42n/DQ2B DIFFIO_B43p DIFFIO_B43n/DQ2B DIFFIO_B44p/DQ2B DIFFIO_B44n DIFFIO_B45p/DQ2B DIFFIO_B45n/DM0B DIFFIO_B46p DIFFIO_B46n/DQ0B DIFFIO_B55p DIFFIO_B55n DIFFIO_B56p DIFFIO_B56n DIFFIO_B57p DIFFIO_B57n DIFFIO_B58p DIFFIO_B58n DIFFIO_B59p/DQ0B DIFFIO_B59n AC21 AD21 Y19 AA19 AB22 AB21 AC22 AD22 AG26 AH26 GPIO4 GPIO6 HEX36 HEX41 GPIO0 GPIO2 GPIO17 GPIO21 GPIO35 GPIO33

IO_0/DQS1B/CQ1B#,CDPCLK2 DIFFIO_B9p/DQ3B IO_1/DQ1B DIFFIO_B9n/DQ3B IO_2/DQ3B DIFFIO_B10p IO_3/DQ3B DIFFIO_B10n/DQ3B IO_4/DQ5B DIFFIO_B11p IO_5 DIFFIO_B11n/DQ3B DIFFIO_B12p/DQ3B DIFFIO_B12n/DQ3B VREFB3N0 DIFFIO_B13p VREFB3N1 DIFFIO_B13n/DQ3B VREFB3N2 DIFFIO_B14p DIFFIO_B14n/DM5B/BWS#5B DIFFIO_B15p/DQS3B/CQ3B#,DPCLK2 DIFFIO_B15n/DQ5B PLL1_CLKOUTp DIFFIO_B16p/DQ5B PLL1_CLKOUTn DIFFIO_B16n

BANK3

AD7 AF6 AD10 AF9 AE9 AD12 AB13 AB11 Y10

SRAM_ADDR1 SRAM_DQ4 FL_ADDR21 FL_ADDR11 FL_ADDR10 FL_ADDR19 FL_ADDR7 SRAM_ADDR15 FL_ADDR15

IO_0 IO_1/DQ0B IO_2 IO_3 RUP2 RDN2

AB15 AD18 AD24 AA21 AA17 AB17

HEX64 HEX50 HEX34 HEX33 HEX60 HEX63

BANK4

VREFB4N0 VREFB4N1 VREFB4N2

AB20 AC18 AA15

HEX32 HEX51 HEX65

AE5 AF5

DRAM_CLK SRAM_ADDR8

FL_WP_N AE12 AF12 FL_DQ7 AE11 FL_RST_N AF11 FL_DQ4 AB10 FL_ADDR9 AC10 FL_WE_N AG11 FL_DQ5 AH11 FL_DQ6 AE13 SD_CLK AF13 SD_DAT1 AC12 FL_ADDR18 AB12 FL_ADDR8 AE14 SD_DAT0 AF14 SD_WP_N SRAM_ADDR16 AC11 AD11 FL_ADDR22

DIFFIO_B17p/DQ5B DIFFIO_B17n DIFFIO_B18p/DQ5B DIFFIO_B18n/DQS5B/CQ5B#,DPCLK3 DIFFIO_B19p DIFFIO_B19n DIFFIO_B20p/DQ5B DIFFIO_B20n/DQ5B DIFFIO_B21p/DQ5B DIFFIO_B21n DIFFIO_B22p DIFFIO_B22n DIFFIO_B23p DIFFIO_B23n DIFFIO_B24p DIFFIO_B24n EP4CE115F29

PLL4_CLKOUTp PLL4_CLKOUTn

AE23 AF23

SMA_CLKOUT HEX35

DIFFCLK6p/CLK15 DIFFCLK6n/CLK14

AG14 AH14

CLOCK2_50 SMA_CLKIN

DIFFIO_B47p/DQ0B DIFFIO_B47n DIFFIO_B48p/DQ0B DIFFIO_B48n/DQS0B/CQ1B,CDPCLK3 DIFFIO_B49p DIFFIO_B49n/DQ0B DIFFIO_B50p DIFFIO_B50n DIFFIO_B51p DIFFIO_B51n DIFFIO_B52p DIFFIO_B52n/DQ0B DIFFIO_B53p DIFFIO_B53n DIFFIO_B54p DIFFIO_B54n/DQ0B

DIFFCLK_7p/CLK13 DIFFCLK_7n/CLK12

AG15 AH15

CLOCK3_50 HSMC_CLKIN0

EP4CE115F29

The LVDS pair can be exchanged eash other, don't exchange single-ended pins with LVDS pins during PCB layout

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number EP4CE115 BANK 3 and BANK 4 Friday, September 24, 2010 Sheet

1

Rev B 22 of 27

The LVDS pair can be exchanged eash other, don't exchange single-ended pins with LVDS pins during PCB layout SW[17..0] HEX3[6..0] KEY[3..0]

HSMC_TX_D_P[16..0] HEX2[6..0] HSMC_TX_D_N[16..0] HEX1[6..0] HSMC_RX_D_P[16..0] HEX0[6..0] HSMC_RX_D_N[16..0] HSMC_D[3..0]

U12E HSMC_RX_D_P14 HSMC_RX_D_N14 HSMC_RX_D_P15 HSMC_RX_D_N15 HSMC_TX_D_P13 HSMC_TX_D_N13 HSMC_RX_D_P8 HSMC_RX_D_N8 HSMC_RX_D_P16 HSMC_RX_D_N16 HSMC_RX_D_P9 HSMC_RX_D_N9 HEX13 HEX11 HSMC_TX_D_P14 HSMC_TX_D_N14 HSMC_RX_D_P10 HSMC_RX_D_N10 HSMC_TX_D_P16 HSMC_TX_D_N16 HEX30 HEX12 HSMC_CLKOUT_P2 HSMC_CLKOUT_N2 HSMC_TX_D_P12 HSMC_TX_D_N12 HSMC_TX_D_P15 HSMC_TX_D_N15 HEX26 HEX25 HEX14 HEX23 HEX22 HEX24 SW4 SW0 HEX20 HEX21 SW9 SW7 SW2 SW1 SW17 SW16 SW3 HSMC_CLKOUT0 HSMC_D2 HSMC_D1 P21 R21 R22 R23 R27 R28 R25 R26 T21 T22 T25 T26 W22 Y22 U27 U28 U25 U26 U22 V22 V21 W21 V23 V24 V25 V26 V27 V28 W28 W27 W25 W26 Y25 Y26 AB27 AB28 AA25 AA26 AB25 AB26 AC27 AC28 Y23 Y24 AD27 AD28 AE27 AE28 DIFFIO_R25p DIFFIO_R49p DIFFIO_R25n DIFFIO_R49n/DQ3R DIFFIO_R26p DIFFIO_R50p DIFFIO_R26n DIFFIO_R50n/DQS3R/CQ3R#,CDPCLK4 DIFFIO_R27p DIFFIO_R51p DIFFIO_R27n/DM0R DIFFIO_R51n DIFFIO_R28p DIFFIO_R28n/DQ1R DIFFIO_R29p/DEV_CLRn DIFFIO_R29n/DEV_OE DIFFIO_R30p/DQS1R/CQ1R#,DPCLK6 DIFFIO_R30n IO_0 DIFFIO_R31p IO_1 DIFFIO_R31n IO_2 DIFFIO_R32p IO_3/DM3R/BWS#3R DIFFIO_R32n/DQ1R DIFFIO_R33p DIFFIO_R33n DIFFIO_R34p DIFFIO_R34n DIFFIO_R35p DIFFIO_R35n DIFFIO_R36p DIFFIO_R36n DIFFIO_R37p/DQ1R DIFFIO_R37n DIFFIO_R38p DIFFIO_R38n/DQ1R DIFFIO_R39p/DQ1R DIFFIO_R39n/DQ1R DIFFIO_R40p DIFFIO_R40n/DQ1R DIFFIO_R41p DIFFIO_R41n/DQ1R DIFFIO_R42p/DQ1R DIFFIO_R42n/DM1R/BWS#1R DIFFIO_R43p DIFFIO_R43n/DQ3R DIFFIO_R44p DIFFIO_R44n/DQ3R DIFFIO_R45p/DQ3R DIFFIO_R45n/DQ3R DIFFIO_R46p DIFFIO_R46n/DQ3R DIFFIO_R47p/DQ3R DIFFIO_R47n/DQ3R DIFFIO_R48p DIFFIO_R48n/DQ3R EP4CE115F29 RUP3 RDN3 AC26 AD26 AE26 AF27 AC24 AC25 SW5 SW6 HSMC_D0 HSMC_D3 SW10 SW8 HSMC_CLKOUT_P1 HSMC_CLKOUT_N1 HSMC_RX_D_P0 HSMC_RX_D_N0 HSMC_RX_D_P3 HSMC_RX_D_N3 HSMC_TX_D_P7 HSMC_TX_D_N7 HSMC_TX_D_P6 HSMC_TX_D_N6 HSMC_TX_D_P8 HSMC_TX_D_N8 HSMC_RX_D_P11 HSMC_RX_D_N11 HSMC_RX_D_P1 HSMC_RX_D_N1 HSMC_TX_D_P0 HSMC_TX_D_N0 HSMC_RX_D_P2 HSMC_RX_D_N2 HSMC_RX_D_P4 HSMC_RX_D_N4 HSMC_TX_D_P1 HSMC_TX_D_N1 HSMC_TX_D_P2 HSMC_TX_D_N2 HSMC_RX_D_P5 HSMC_RX_D_N5 HSMC_TX_D_P3 HSMC_TX_D_N3 HSMC_TX_D_P10 HSMC_TX_D_N10 HSMC_TX_D_P4 HSMC_TX_D_N4 HSMC_RX_D_P6 HSMC_RX_D_N6 HSMC_TX_D_P11 HSMC_TX_D_N11 HSMC_RX_D_P7 HSMC_RX_D_N7 HSMC_TX_D_P5 HSMC_TX_D_N5 HSMC_RX_D_P12 HSMC_RX_D_N12 HSMC_TX_D_P9 HSMC_TX_D_N9 HSMC_RX_D_P13 HSMC_RX_D_N13 G23 G24 F24 F25 G25 G26 H23 H24 K21 K22 J23 J24 L21 L22 D26 C27 D27 D28 F26 E26 H25 H26 E27 E28 F27 F28 K25 K26 G27 G28 J25 J26 K27 K28 L23 L24 L27 L28 M25 M26 M27 M28 N25 N26 P27 P28 P25 P26

U12F DIFFIO_R1p DIFFIO_R1n DIFFIO_R2p DIFFIO_R2n DIFFIO_R3p DIFFIO_R3n DIFFIO_R4p DIFFIO_R4n DIFFIO_R5p DIFFIO_R5n DIFFIO_R6p DIFFIO_R6n DIFFIO_R7p DIFFIO_R7n DIFFIO_R8p DIFFIO_R8n/DQS2R/CQ3R,CDPCLK5/PADD20 DIFFIO_R9p/DQ2R/PADD21 DIFFIO_R9n/PADD22 DIFFIO_R10p/DQ2R DIFFIO_R10n DIFFIO_R11p DIFFIO_R11n DIFFIO_R12p/DQ2R DIFFIO_R12n/DQ2R/PADD23 DIFFIO_R13p DIFFIO_R13n/DQ2R/nAVD DIFFIO_R14p DIFFIO_R14n/DQ2R DIFFIO_R15p/DQ2R/nOE DIFFIO_R15n/DQ2R/nWE DIFFIO_R16p DIFFIO_R16n

R24 U21 AA23 AB24 AA22 AB23

KEY3 HEX31 SW14 SW11 SW15 SW12

IO_0 IO_1 IO_2/DM2R IO_3 IO_4

H22 L25 L26 M24 M23

HEX06 HEX04 HEX03 HEX10 KEY0

BANK5

VREFB5N0 VREFB5N1 VREFB5N2

U24 U23 AA24

HEX16 HEX15 SW13

VREFB6N0 VREFB6N1 VREFB6N2

J22 M21 N21

HEX05 KEY1 KEY2

BANK6

DIFFCLK_3p/CLK6 DIFFCLK_3n/CLK7

Y27 Y28

HSMC_CLKIN_P2 HSMC_CLKIN_N2

DIFFIO_R17p/DQ0R DIFFIO_R17n/DQ0R DIFFIO_R18p DIFFIO_R18n/DQ0R DIFFIO_R19p/DQ0R DIFFIO_R19n/DQ0R DIFFIO_R20p DIFFIO_R20n/DQ0R DIFFIO_R21p/DQ0R DIFFIO_R21n/DQ0R DIFFIO_R22p DIFFIO_R22n/DQS0R/CQ1R,DPCLK7 DIFFIO_R23p/CLKUSR DIFFIO_R23n/nCEO DIFFIO_R24p/CRC_ERROR DIFFIO_R24n/INIT_DONE EP4CE115F29

DIFFCLK_2p/CLK4 DIFFCLK_2n/CLK5

J27 J28

HSMC_CLKIN_P1 HSMC_CLKIN_N1

Close to FPGA HSMC_RX_D_p0 HSMC_RX_D_p1 HSMC_RX_D_p2 HSMC_RX_D_p3

A

R55 R57 R56 R60 R58 R61 R59 R66 R65

DNI DNI DNI DNI DNI DNI DNI DNI DNI

HSMC_RX_D_n0 HSMC_RX_D_n1 HSMC_RX_D_n2 HSMC_RX_D_n3 HSMC_RX_D_n4 HSMC_RX_D_n5 HSMC_RX_D_n6 HSMC_RX_D_n7 HSMC_RX_D_n8

4

HSMC_RX_D_p9 HSMC_RX_D_p10 HSMC_RX_D_p11 HSMC_RX_D_p12 HSMC_RX_D_p13 HSMC_RX_D_p14 HSMC_RX_D_p15 HSMC_RX_D_p16

R69 R70 R67 R71 R72 R73 R74 R76

DNI DNI DNI DNI DNI DNI DNI DNI

HSMC_RX_D_n9 HSMC_RX_D_n10 HSMC_RX_D_n11 HSMC_RX_D_n12

HSMC_CLKIN_P1 HSMC_CLKIN_P2

R64 R75

DNI HSMC_CLKIN_N1 DNI HSMC_CLKIN_N2

HSMC_RX_D_p4 HSMC_RX_D_p5 HSMC_RX_D_p6 HSMC_RX_D_p7 HSMC_RX_D_p8

5

HSMC_RX_D_n13 HSMC_RX_D_n14 HSMC_RX_D_n15 HSMC_RX_D_n16 Size B Date:

3 2

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Document Number EP4CE115 BANK 5 and BANK 6 Friday, September 24, 2010 Sheet

1

Rev B 23 of 27

VGA_R[7..0] ENET0_RX_DATA[3..0] HEX0[6..0] ENET0_TX_DATA[3..0] ENET1_TX_DATA[3..0] VGA_B[7..0]

D

TD_DATA[7..0]

ENET1_RX_DATA[3..0] VGA_G[7..0] EX_IO[6..0]

D

LEDG[8..0]

LEDR[17..0]

U12G ENET0_RX_CRS ENET0_RX_DATA3 ENET0_RX_COL LEDR14 LEDR10 LEDR17 ENET0_TX_CLK ENET0_GTX_CLK ENET0_RX_DATA1 ENET0_RX_DATA0 LEDR11 LEDR12 HEX02 LEDG8 LEDR13 LEDR16 HEX00 LEDR0 LEDG6 LEDG4 LEDR6 LEDR7 LEDG7 LEDG5 ENET0_TX_ER ENET0_TX_EN ENET0_TX_DATA3 ENET0_TX_DATA2 ENET0_RX_DATA2 ENET0_RX_DV ENET0_TX_DATA1 ENET0_RST_N LEDG2 LEDG3 ENET1_RX_CRS ENET0_MDC ENET0_RX_ER ENET0_TX_DATA0 LEDR4 LEDR5 ENET0_MDIO ENET0_INT_N ENET1_RX_COL ENET1_RX_DV ENET1_RX_DATA3 ENET1_TX_CLK ENET1_INT_N ENET1_RX_ER D15 C15 E15 F15 J15 H15 B17 A17 D16 C16 H16 J16 E17 F17 H17 G16 G18 G19 G22 H21 J19 H19 G21 G20 B18 A18 B19 A19 D17 C17 D19 C19 E25 E24 D20 C20 D18 C18 F18 E18 B21 A21 B22 A22 D21 C22 D24 C24 DIFFIO_T32p/DQ5T/PADD14 DIFFIO_T32n/PADD13 DIFFIO_T33p/DM4T DIFFIO_T33n DIFFIO_T34p DIFFIO_T34n DIFFIO_T35p/DQS4T/CQ5T,DPCLK9/PADD12 DIFFIO_T35n/PADD11 DIFFIO_T36p/PADD10 DIFFIO_T36n/DQ4T/PADD9 DIFFIO_T37p DIFFIO_T37n DIFFIO_T38p/DQ4T DIFFIO_T38n DIFFIO_T39p DIFFIO_T39n DIFFIO_T40p DIFFIO_T40n DIFFIO_T41p DIFFIO_T41n DIFFIO_T42p DIFFIO_T42n DIFFIO_T43p DIFFIO_T43n DIFFIO_T44p/DQ4T/PADD8 DIFFIO_T44n/PADD7 DIFFIO_T45p/DQ4T/PADD6 DIFFIO_T45n/DQ4T/PADD5 DIFFIO_T46p/DQS2T/CQ3T,DPCLK8/PADD4 DIFFIO_T46n/DQ4T/PADD3 DIFFIO_T47p DIFFIO_T47n/DQ4T DIFFIO_T48p DIFFIO_T48n DIFFIO_T49p/DQ4T DIFFIO_T49n/DM2T DIFFIO_T50p/PADD2 DIFFIO_T50n/PADD1 DIFFIO_T51p DIFFIO_T51n/DQ2T DIFFIO_T52p/DQ2T DIFFIO_T52n/DQ2T DIFFIO_T53p/PADD0 DIFFIO_T53n/DQ2T DIFFIO_T54p/DQ2T DIFFIO_T54n/DQ2T DIFFIO_T55p DIFFIO_T55n/DQ2T EP4CE115F29 DIFFIO_T56p/DM0T DIFFIO_T56n/DQ0T DIFFIO_T57p/DQ0T DIFFIO_T57n DIFFIO_T58p/DQ0T DIFFIO_T58n DIFFIO_T59p/DQS0T/CQ1T,CDPCLK6 DIFFIO_T59n/DQ0T DIFFIO_T60p/DQ0T DIFFIO_T60n/DQ0T DIFFIO_T61p/DQ0T DIFFIO_T61n B23 A23 C25 D25 F21 E21 A25 A26 E22 D22 B26 C26 ENET1_RX_DATA0 ENET1_RX_DATA2 ENET1_TX_DATA0 ENET1_MDIO LEDR3 LEDG0 ENET1_TX_ER ENET1_TX_DATA1 LEDG1 ENET1_RST_N ENET1_TX_DATA2 ENET1_TX_DATA3 TD_HS TD_VS OTG_DACK_N1 OTG_DACK_N0 OTG_CS_N OTG_RD_N OTG_DREQ1 OTG_WR_N TD_DATA7 TD_RESET_N VGA_R6 VGA_G0 VGA_G2 TD_DATA0 TD_DATA5 TD_DATA6 TD_DATA4 TD_DATA3 TD_DATA2 VGA_G4 VGA_G5 I2C_SDAT EX_IO0 VGA_R7 VGA_R4 VGA_G6 EX_IO6 VGA_G7 VGA_B6 VGA_B2 VGA_G3 VGA_G1 OTG_LSPEED OTG_INT0 I2C_SCLK TD_DATA1 VGA_BLANK_N VGA_R1 VGA_R3 VGA_R0 VGA_R2 VGA_SYNC_N EX_IO2 VGA_HS VGA_B0 VGA_B1 VGA_R5 UART_RTS E5 E4 D4 C4 A3 B3 B4 A4 F7 G7 H8 G8 F8 E8 D6 E7 D7 C7 D8 C8 B8 A8 J10 H10 G10 F10 D9 C9 D11 C11 H12 G11 B6 A6 B7 A7 F11 E11 F12 E12 D10 C10 H13 G13 B10 A10 J12 J13

U12H DIFFIO_T1p DIFFIO_T1n DIFFIO_T2p/DM1T DIFFIO_T2n/DQ1T DIFFIO_T3p/DQ1T DIFFIO_T3n DIFFIO_T4p/DQS1T/CQ1T#,CDPCLK7/DATA12 DIFFIO_T4n/DQ1T DIFFIO_T5p DIFFIO_T5n DIFFIO_T6p DIFFIO_T6n DIFFIO_T7p DIFFIO_T7n DIFFIO_T8p/DQ1T DIFFIO_T8n DIFFIO_T9p/DATA11 DIFFIO_T9n/DQ1T/DATA10 DIFFIO_T10p/DQ1T DIFFIO_T10n/DQ1T DIFFIO_T11p DIFFIO_T11n/DM3T/BWS#3T/DATA9 DIFFIO_T12p DIFFIO_T12n DIFFIO_T13p DIFFIO_T13n DIFFIO_T14p/DATA8 DIFFIO_T14n/DQ3T DIFFIO_T15p DIFFIO_T15n/DQ3T/DATA7 DIFFIO_T16p DIFFIO_T16n DIFFIO_T25p/DQ5T/DATA3 DIFFIO_T25n/DQ5T/DATA2 DIFFIO_T26p/DQ5T DIFFIO_T26n DIFFIO_T27n/DQ5T DIFFIO_T28p DIFFIO_T28n DIFFIO_T29p/DQS5T/CQ5T#,DPCLK10/PADD17 DIFFIO_T29n/DQ5T/PADD16 DIFFIO_T30p/PADD15 DIFFIO_T30n/DQ5T DIFFIO_T31p/DQ5T DIFFIO_T31n/DQ5T B11 A11 E14 F14 A12 J14 H14 D12 C12 D14 C14 D13 C13 VGA_B3 VGA_B4 EEP_I2C_SDAT EX_IO4 VGA_CLK EX_IO1 EX_IO3 VGA_B7 VGA_B5 EEP_I2C_SCLK ENET0_LINK100 ENET1_LINK100 VGA_VS

BANK7

IO_0 IO_1/DQ2T IO_2/DQ0T

J17 C21 B25

LEDR8 ENET1_RX_DATA1 ENET1_TX_EN

IO_0 IO_1/DQ1T IO_2

C3 C6 E10

OTG_ADDR1 OTG_FSPEED EX_IO5

RUP4 RDN4

F19 E19

LEDR1 LEDR2

BANK8

VREFB8N0 VREFB8N1 VREFB8N2

G14 G12 G9

UART_CTS UART_RXD UART_TXD

VREFB7N0 VREFB7N1 VREFB7N2 PLL2_CLKOUTp PLL2_CLKOUTn

F22 G17 G15 D23 C23

HEX01 LEDR9 LEDR15 ENET1_MDC ENET1_GTX_CLK

DIFFCLK_5p/CLK9 DIFFCLK_5n/CLK8

B15 A15

ENET1_RX_CLK ENET0_RX_CLK

DIFFIO_T17p/DQ3T/DATA6 DIFFIO_T17n DIFFIO_T18p/DQ3T/DATA5 DIFFIO_T18n/DQ3T DIFFIO_T19p DIFFIO_T19n/DQ3T DIFFIO_T20p/DATA13 DIFFIO_T20n/DQS3T/CQ3T#,DPCLK11/DATA14 DIFFIO_T21p/DQ3T DIFFIO_T21n/DQ3T DIFFIO_T22p/DQ3T/DATA15 DIFFIO_T22n/PADD19 DIFFIO_T23p/DM5T/BWS#5T/DATA4 DIFFIO_T23n/PADD18 DIFFIO_T24p DIFFIO_T24n EP4CE115F29

PLL3_CLKOUTp PLL3_CLKOUTn

D5 C5

OTG_INT1 OTG_RST_N

DIFFCLK_4p/CLK11 DIFFCLK_4n/CLK10

B14 A14

TD_CLK27 ENETCLK_25

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number EP4CE115 BANK 7 and BANK 8 Friday, September 24, 2010 Sheet

1

Rev B 24 of 27

VCCIO3P3

D

VCCIO3P3

VCCIO3P3

GPIO_VCCIO

HSMC_VCCIO

HSMC_VCCIO

VCCIO2P5

VCCIO3P3

D

AA28 AG28 T24 T28 W24

AA11 AD6 AD9 AD13 AH2 AH5 AH9 AH13

AA18 AD16 AD20 AD23 AH16 AH20 AH24 AH27

AA1 AG1 T1 T5 W5

B28 H28 K24 N24 N28

A16 A20 A24 A27 E16 E20 E23 H18 VCCIO7 VCCIO7 VCCIO7 VCCIO7 VCCIO7 VCCIO7 VCCIO7 VCCIO7

VCCINT K9 K11 K13 K15 K17 K19 L10 L12 L14 L16 L18 L20 M9 M11 M13 M15 M17 M19 N10 N12 N14 N16 N18 N20 P9 P11 P13 P15 P17 P19 R10 R12 R14 R16 R18 R20 T9 T11 T13 T15 T17 T19 U10 U12 U14 U16 U18 U20 V9 V11 V13 V15 V17 V19 W10 W12 W14 W16 W18 W20 VCCD_PLL Y9 J20 J9 Y20 Y8 J21 J8 Y21

U12I VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT

VCCIO1 VCCIO1 VCCIO1 VCCIO1 VCCIO1

VCCIO2 VCCIO2 VCCIO2 VCCIO2 VCCIO2

VCCIO3 VCCIO3 VCCIO3 VCCIO3 VCCIO3 VCCIO3 VCCIO3 VCCIO3

VCCIO4 VCCIO4 VCCIO4 VCCIO4 VCCIO4 VCCIO4 VCCIO4 VCCIO4

VCCIO5 VCCIO5 VCCIO5 VCCIO5 VCCIO5

VCCIO6 VCCIO6 VCCIO6 VCCIO6 VCCIO6

VCCIO8 VCCIO8 VCCIO8 VCCIO8 VCCIO8 VCCIO8 VCCIO8 VCCIO8

A2 A5 A9 A13 E6 E9 E13 H11

B1 H1 K5 N1 N5

VCCIO3P3 Bnak1 GNDA4 GNDA3 GNDA2 GNDA1 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND AA20 H9 H20 AA9 B12 D3 J2 Y18 Y11 W23 W6 T27 T23 T6 T2 N27 N23 N6 N2 K23 K6 J18 J11 H27 H2 F23 F20 F16 F13 F9 F6 C28 C1 B27 B24 B20 B16 B13 B9 B5 B2 AG27 AG24 AG20 AG16 AG13 AG9 AG5 AG2 AF28 AF1 AC23 AC20 AC16 AC13 AC9 AC6 AA27 AA2

VCCIO3P3 Bnak2

VCCIO3P3 Bnak3

GPIO_VCCIO Bnak4

C199 0.1u

C237 0.1u

C239 0.1u

C200 0.1u

C240 0.1u

C238 0.1u

C257 0.1u

C256 0.1u

C271 0.1u

C270 0.1u

C269 0.1u

C268 0.1u

C267 0.1u

C264 0.1u

C265 0.1u

C266 0.1u

HSMC_VCCIO

Bnak5

HSMC_VCCIO

Bnak6

VCCIO2P5 Bnak7

VCCIO3P3 Bnak8

C207 0.1u

C205 0.1u

C243 0.1u

C242 0.1u

C192 0.1u

C193 0.1u

C206 0.1u

C204 0.1u

C195 0.1u

C185 0.1u

C186 0.1u

C187 0.1u

C197 0.1u

C190 0.1u

C188 0.1u

C189 0.1u

VCCD_PLL

VCCA

POWER & GROUND

C194 0.1u

C198 0.1u

C244 0.1u

C255 0.1u

C196 0.1u

C222 0.1u

C250 0.1u

C249

C

0.1u

VCCINT

VCCINT VCC2P5 R47 0 0 C59 10u VCCINT VCCINT VCCIO2P5

C225 10n

C228 10n

C218 10n

C217 10n

C220 10n

C221 10n

C227 10n

C224 10n

C209 22n

C211 22n

C208 22n

C212 22n

C234 22n

C233 22n

C214 22n

C231 22n

C215 22n

C230 R46 22n

C252 0.1u

C226 0.1u

C235 0.1u

C216 0.1u

C219 0.1u

C247 0.1u

C248 0.1u

C236 0.1u

C223 0.1u

C251 0.1u

C229 0.47u

C254 0.47u

C246 0.47u

C253 0.47u

C245 0.47u

C210 0.47u

C213 0.47u

C232 VCC3P3 0.47u R45 R44 0 0

VCCIO3P3

C57 100u

VCCD_PLL1 VCCD_PLL2 VCCD_PLL3 VCCD_PLL4 VCCA1 VCCA2 VCCA3 VCCA4 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND

VCCA

B

VCC2P5 L2

VCCA BEAD C58 10u

VCCINT L4

VCCD_PLL BEAD C81 10u VCC1P2 R68 R63 R62 VCCINT 0 0 0

B

K10 K12 K14 K16 K18 K20 L9 L11 L13 L15 L17 L19 M10 M12 M14 M16 M18 M20 N9 N11 N13 N15 N17 N19 P10 P12 P14 P16 P18 P20 R9 R11 R13 R15 R17 R19 T10 T12 T14 T16 T18 T20 U9 U11 U13 U15 U17 U19 V10 V12 V14 V16 V18 V20 W9 W11 W13 W15 W17 W19

EP4CE115F29 C79 100u C80 100u C70 100u C71 100u

U12J VCCA

DCLK DATA0 NCONFIG NCE TDI TCK TMS TDO VCCA

P3 N7 P4 R8 P7 P5 P8 P6

DCLK DATA0 nCONFIG nCE TDI TCK TMS TDO

CONTROL SIGNAL

ASDO nCSO nSTATUS CONF_DONE MSEL0 MSEL1 MSEL2 MSEL3

F4 E2 M6 P24 N22 P23 M22 P22

ASDO NCSO NSTATUS CONF_DONE

R175 0

R187 0

R185 DNI

R173 0

R174 R172 DNI EP4CE115F29 TCK R188 R189 1K TMS TDI DNI R184 DNI 0

R186 DNI

R202 10K

R203 10K

C201 DNI

TDO

R201

DNI

VCCA Title

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE2-115 Main Board

Size C Date:

5 4 3 2

Document Number EP4CE115 POWER and CONFIG Friday, September 24, 2010

1

Rev B Sheet 25 of 27

SW18 1 5 6 VCC12 4 2 J8

D

VCC12

DC_12V 1 2 3

D8 D10 D9 D11

SM340A SM340A SM340A

3 POWER SW 5 6 7 8 C50 C48 Q2 22u 0.1u 2 R39 34K 7 REG2 VIN HG 11 4 IRF7455PbF

D

SM340A

RON

VCC

1 C49 2.2u 12 C175

3 2 1

6 C51 15n 3

SS

BST

L1 0.47u EN SW 10 R157 5

C

3.3uH

1V2

VCC1P2

1.2V/5A

5 6 7 8 Q1

R244

C30 C170

SGND

ILIM

8 DNI DNI C31 DNI 1.2n 1.78K 4 IRF7455PbF

R145 10K C29 330u R146 10K C32 0.1u

C

PGND

EP

FB

SGND

LG LM3150MH

13 3 2 1

14

15

5 6 7 8 C60 22u C53 Q4 0.1u 2 R48 52.3K 7 REG3 VIN HG 11 4 IRF7455PbF

RON

VCC

1 C54 2.2u 12 C191

3 2 1

6 C61 15n VCC3P3 3

SS

BST

L3 0.47u EN SW 10 R180 5 R118 120 9 D1 SGND SGND ILIM 8 Q3 2.4K PGND EP FB LG LM3150MH 13 3 2 1 4 75K 5 6 7 8 R245

3.3uH

3V3

VCC3P3

3.3V/6A

C73 C202 3.3n C74 2.2u 390p

R190 22K C72 330u C203 0.1u

IRF7455PbF

POWER

LEDB

R191 4.87K

14

15

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number POWER 1.2V & 3.3V Friday, September 24, 2010 Sheet

1

Rev B 26 of 27

VCC12 REG1 1 C55 10u R41 11.8K R40 34K R167 68.1K 3 GND EP EN SS 5 C178 R42 1K 2 VIN RON VOUT FB 7

5V

VCC5

5V/3A ADJ/1A for Bank 4 I/O Voltage/1A

VCC3P3 GPIO_VCCIO REG6 4 VIN VOUT 3 JP6 R177 VEN GND 10K 1 ADJ 2 1 3 5 7 VCC3P3 R53 4.99K JP6: 1-2 : 1.5V 3-4 : 1.8V 5-6 : 2.5V 7-8 : 3.3V 2 4 6 8 R156 R155 R154 1K 2.2K 4.99K C66 10u C67 0.1u C77 10u GPIO_VCCIO

R43 5.23K

C177 C52 22n 100u 100u 0.1u C296 C56

4 8

LMZ12003 TZ-ADJ

10n

GPIO_VCCIO

VCC3P3 REG4

C

2V5 VCC2P5 4 VIN VOUT 3 R49 4.99K C62 10u C63

2.5V/1A

LP38692MP-ADJ

HEADER 2X4

C75 10u R179 VEN GND 10K 1 ADJ 2 VCC3P3 0.1u 4 C78 R50 4.99K 10u R176 VEN GND 10K 1 ADJ 2 REG7 VIN VOUT 3 JP7 1 3 5 7 VCC3P3 R54 4.99K VCC3P3 REG5 4

B

ADJ/1A for Bank 5 & 6 I/O Voltage/1A

HSMC_VCCIO

HSMC_VCCIO

LP38692MP-ADJ

2 4 6 8

R153 R152 R151

1K 2.2K 4.99K

C68 10u

C69 0.1u

HSMC_VCCIO

LP38692MP-ADJ

HEADER 2X4

1V8 VCC1P8 VIN VOUT 3 R51 2.2K C64 10u C65 0.1u

1.8V/1A

JP7: 1-2 : 1.5V 3-4 : 1.8V 5-6 : 2.5V 7-8 : 3.3V

B

C76 10u R178 VEN GND 10K 1 ADJ 2

LP38692MP-ADJ R52 4.99K MH5 MH6 MH8 MH2 MH1 MH7 MH4 MH3

FID5

FID6

FID2

FID1

FID4

FID3

FID9

FID8

FID7

FID10

GND1

GND2

GND3

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan. All rights reserved. No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE2-115 Main Board

Size B Date:

5 4 3 2

Document Number POWER 1.8V & 2.5V & 5V Friday, September 24, 2010 Sheet

1

Rev B 27 of 27

Das könnte Ihnen auch gefallen

- Baccara Solenoid Catalogue 2009Dokument230 SeitenBaccara Solenoid Catalogue 2009baccaragevaNoch keine Bewertungen

- Digital Servo Amplifier S701x2Dokument164 SeitenDigital Servo Amplifier S701x2Kiem Do Viet100% (1)

- Generic Base Elements GuideDokument81 SeitenGeneric Base Elements GuidengocanhvyNoch keine Bewertungen

- Tai Lieu XG5000Dokument48 SeitenTai Lieu XG5000NguyễnThanhSangNoch keine Bewertungen

- 840 USE 100 00 v80Dokument902 Seiten840 USE 100 00 v80nelsonacuaNoch keine Bewertungen

- EDMI User ManualDokument11 SeitenEDMI User ManualDai HaizhongNoch keine Bewertungen

- Bluetooth Module GuideDokument13 SeitenBluetooth Module GuideJaime Leonardo CruzNoch keine Bewertungen

- VisiLogic UtilitiesDokument210 SeitenVisiLogic UtilitiesJorge ManuelNoch keine Bewertungen

- CET Power - Agil Modular UPS - User Manual - v7.2Dokument61 SeitenCET Power - Agil Modular UPS - User Manual - v7.2Renzo Velarde100% (1)

- NE MotoHawk Resource Guide PDFDokument105 SeitenNE MotoHawk Resource Guide PDFMarkus SenojNoch keine Bewertungen

- Manual CS121 enDokument166 SeitenManual CS121 enABELNoch keine Bewertungen

- RLC 1st ManualDokument141 SeitenRLC 1st Manualjaved shaikh chaandNoch keine Bewertungen

- Supervisory Module SM3XDokument2 SeitenSupervisory Module SM3XMatias EspinosaNoch keine Bewertungen

- Datasheet SKHI 22A PDFDokument12 SeitenDatasheet SKHI 22A PDFGlauber GoncalvesNoch keine Bewertungen

- Guide to the Climate Control System in the BMW 5 Series (G30Dokument7 SeitenGuide to the Climate Control System in the BMW 5 Series (G30SalisburNoch keine Bewertungen

- Chart2D OlchocxDokument262 SeitenChart2D Olchocxmongool33Noch keine Bewertungen

- Maacpmicro1 Eng PDFDokument221 SeitenMaacpmicro1 Eng PDFSarah SalinasNoch keine Bewertungen

- Trans-Amf Syncro Eng Man v01Dokument125 SeitenTrans-Amf Syncro Eng Man v01juan pablo GodoyNoch keine Bewertungen

- DMN FST Manual Sp-Ec-Rot-Mt Reset Module en 20100713-MsDokument2 SeitenDMN FST Manual Sp-Ec-Rot-Mt Reset Module en 20100713-MsadrianpashnicNoch keine Bewertungen

- 48V LiFePO4 Battery: Long Cycle Life, High Power, Safe Lithium BatteryDokument2 Seiten48V LiFePO4 Battery: Long Cycle Life, High Power, Safe Lithium BatteryAbdul Saboor MarwatNoch keine Bewertungen

- Manual English Movicon11 Programmer GuideDokument662 SeitenManual English Movicon11 Programmer Guidetihamer_v100% (1)

- Hướng dẫn kết nối board plc FK3UDokument7 SeitenHướng dẫn kết nối board plc FK3UHiệp Trần100% (1)

- Carregador CCL Sentinel 150Dokument8 SeitenCarregador CCL Sentinel 150José Da Silva MataNoch keine Bewertungen

- Spax (Safi Pickup Amplifier Extended) : Technical InstructionDokument26 SeitenSpax (Safi Pickup Amplifier Extended) : Technical InstructionAli QaziNoch keine Bewertungen

- MTC Integrative Automation Background Monitoring Software Operating InstructionDokument99 SeitenMTC Integrative Automation Background Monitoring Software Operating InstructionmattroimocmocNoch keine Bewertungen

- Solar River Grid Connect ManualDokument36 SeitenSolar River Grid Connect Manualanomalous_space100% (1)

- Label Scale User Manual - RONGTA RLS1000 PDFDokument25 SeitenLabel Scale User Manual - RONGTA RLS1000 PDFSaci Bennacer100% (1)

- SMP Gateway SoftPLC Reference ManualDokument47 SeitenSMP Gateway SoftPLC Reference Manualswalker948100% (1)

- UL 1564 SUN Rev 8 25 2020 ED 8 25 2022Dokument3 SeitenUL 1564 SUN Rev 8 25 2020 ED 8 25 2022Joshua JonesNoch keine Bewertungen

- EDMI Genius Register Manual E7Dokument114 SeitenEDMI Genius Register Manual E7scozans0% (1)

- CyberCat & Cheetah Xi Battery Charging UpdateDokument1 SeiteCyberCat & Cheetah Xi Battery Charging UpdateNestor100% (1)

- Schneider Electric TSX3722101 DatasheetDokument5 SeitenSchneider Electric TSX3722101 DatasheetSadat AhmadNoch keine Bewertungen

- Sma STP 110-60 Core2Dokument84 SeitenSma STP 110-60 Core2Manuel UrdanetaNoch keine Bewertungen

- Osicoder - Rotary Encoders Catalogue 2006.01Dokument54 SeitenOsicoder - Rotary Encoders Catalogue 2006.01Sarah RichardNoch keine Bewertungen

- 8201-8204 Inverter v02-08 ENDokument72 Seiten8201-8204 Inverter v02-08 ENmarco mazzolaNoch keine Bewertungen

- Robot Programming in "C": Tak Auyeung, Ph.D. February 15, 2006Dokument160 SeitenRobot Programming in "C": Tak Auyeung, Ph.D. February 15, 2006MaYur D AeronNoch keine Bewertungen

- Automatic Fan Speed Control Circuit Using PIC16F877A MicrocontrollerDokument5 SeitenAutomatic Fan Speed Control Circuit Using PIC16F877A MicrocontrollerPramillaNoch keine Bewertungen

- 10 tm21-m tm126b 201309 dn-3zw214-bDokument60 Seiten10 tm21-m tm126b 201309 dn-3zw214-bkosmitoNoch keine Bewertungen

- Platinum Frame and System EditionAD - 20160504Dokument522 SeitenPlatinum Frame and System EditionAD - 20160504anyuser100% (1)

- TMEIC Manual PDFDokument2 SeitenTMEIC Manual PDFKhoi DangNoch keine Bewertungen

- Kepware Mitsubishi FXDokument20 SeitenKepware Mitsubishi FXlue-ookNoch keine Bewertungen

- Flexible Mode Bridgeless Boost PFC Rectifier Achieves High EfficiencyDokument3 SeitenFlexible Mode Bridgeless Boost PFC Rectifier Achieves High EfficiencyBrightworld ProjectsNoch keine Bewertungen

- VC PDFDokument114 SeitenVC PDFMisha KulibaevNoch keine Bewertungen

- CE Smart PLC USER ManualDokument99 SeitenCE Smart PLC USER Manualgerald rockNoch keine Bewertungen

- Master Drives T 400Dokument241 SeitenMaster Drives T 400aqccc120Noch keine Bewertungen

- (Manual) Estun ProNet PROFIBUS Communication EN v1.01 PDFDokument30 Seiten(Manual) Estun ProNet PROFIBUS Communication EN v1.01 PDFjns1606Noch keine Bewertungen

- PC Bulb Injection Stretch Blow Molding Machine Proposal 20150522Dokument8 SeitenPC Bulb Injection Stretch Blow Molding Machine Proposal 20150522kotharideepNoch keine Bewertungen

- Converter Manual 24062010 PDFDokument50 SeitenConverter Manual 24062010 PDFarusar2002Noch keine Bewertungen

- Operation Manual Invertronic Compact Inverter: Operating InstructionsDokument102 SeitenOperation Manual Invertronic Compact Inverter: Operating Instructionsenrique mendozaNoch keine Bewertungen

- Compact NSX PDFDokument228 SeitenCompact NSX PDFjaysonlkhNoch keine Bewertungen

- Falcoweb User Manual 250113Dokument67 SeitenFalcoweb User Manual 250113HendriJuniantoNoch keine Bewertungen