Beruflich Dokumente

Kultur Dokumente

Design Problem 1 ECE (Communication System II)

Hochgeladen von

seema jain0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

24 Ansichten1 Seiteknowledge

Originaltitel

11106_dp1

Copyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

DOC, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenknowledge

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als DOC, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

24 Ansichten1 SeiteDesign Problem 1 ECE (Communication System II)

Hochgeladen von

seema jainknowledge

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als DOC, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 1

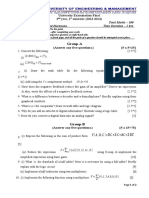

Design Problem 1 ECE ( Communication System II)

1) Design the block diagram of M-ARY FSK(M=8) using simulink. [5] 2) Compare the bit error rate of the M-ARY FSK (M=8) , BFSK and QFSK using graph. [5] 3) Compare the symbol rate of M-ary FSK (M=8) and BFSK using graph. [5] 4) Design the delta modulator block diagram using simulink and show the results. [5]

Note- Assume any signal or parameters by your own.

Das könnte Ihnen auch gefallen

- Ade Module 3 Question BankDokument1 SeiteAde Module 3 Question BankYugandhar ChejarlaNoch keine Bewertungen

- Project Titles Sem 2 1617Dokument15 SeitenProject Titles Sem 2 1617marwanNoch keine Bewertungen

- (Nov-11) (EUREE-504) : Unit-IiiDokument1 Seite(Nov-11) (EUREE-504) : Unit-IiiAnand KalNoch keine Bewertungen

- Department of Electronic and Computer Engineering: M552 Digital Modulation and CodingDokument4 SeitenDepartment of Electronic and Computer Engineering: M552 Digital Modulation and CodingRaj Karthik RajasekaranNoch keine Bewertungen

- Tutorial ComDokument4 SeitenTutorial ComMaga LakshmiNoch keine Bewertungen

- Ii Ece B I SemDokument52 SeitenIi Ece B I SemElectronics & communication engineering AstcNoch keine Bewertungen

- Switchinng Theory and Logic Design July 2022Dokument2 SeitenSwitchinng Theory and Logic Design July 2022drkhamuruddeenNoch keine Bewertungen

- Ec6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesDokument12 SeitenEc6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesSurendar PNoch keine Bewertungen

- School of Electronics Engineering ECE 2003 (Fall 20-21) / Assignment / D1 Slot / Dr.M.Geetha Priya Max Marks: 100 Si - No. Questions MarksDokument4 SeitenSchool of Electronics Engineering ECE 2003 (Fall 20-21) / Assignment / D1 Slot / Dr.M.Geetha Priya Max Marks: 100 Si - No. Questions MarksBarath KumarNoch keine Bewertungen

- ADE E (CS) 301 Term-FinalDokument2 SeitenADE E (CS) 301 Term-FinalGaitonde GaneshNoch keine Bewertungen

- Digital Logic Microprocessor AssignmentDokument4 SeitenDigital Logic Microprocessor AssignmentSourabh YadavNoch keine Bewertungen

- f215 Tut06 27-09Dokument10 Seitenf215 Tut06 27-09desaikaran1997_44873Noch keine Bewertungen

- 2EC6302-Digital Electronics QBDokument12 Seiten2EC6302-Digital Electronics QBSurendar PNoch keine Bewertungen

- Ec6302 Digital Electronics 123 PDFDokument6 SeitenEc6302 Digital Electronics 123 PDFAnkush MauryaNoch keine Bewertungen

- Ec6302 Digital Electronics 1234 PDFDokument6 SeitenEc6302 Digital Electronics 1234 PDFgunasekaran kNoch keine Bewertungen

- Digital ElectronicsDokument2 SeitenDigital ElectronicsVaso RanaNoch keine Bewertungen

- EC6302 Digital ElectronicsDokument13 SeitenEC6302 Digital ElectronicsDhanaa DhanagopalNoch keine Bewertungen

- For K 0,1, ..... ..,9Dokument2 SeitenFor K 0,1, ..... ..,9SayanMaitiNoch keine Bewertungen

- EC 6302 2-Marks and 16 Marks QuestionsDokument12 SeitenEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceNoch keine Bewertungen

- Ldco Insem BankDokument2 SeitenLdco Insem BankShivamNoch keine Bewertungen

- EC6302-Digital ElectronicsDokument14 SeitenEC6302-Digital Electronicsmagy1989Noch keine Bewertungen

- Structured Digital System Design Question PaperDokument1 SeiteStructured Digital System Design Question PaperSatish Bojjawar0% (1)

- Digital Electronics June July 2022Dokument8 SeitenDigital Electronics June July 2022RCEE-2020 ONLINE FDPNoch keine Bewertungen

- Digital Image Processing IT Question Paper Sets 2018Dokument1 SeiteDigital Image Processing IT Question Paper Sets 2018samarthNoch keine Bewertungen

- EC6302 Digital ElectronicsDokument12 SeitenEC6302 Digital ElectronicsJabeen BanuNoch keine Bewertungen

- B) All Sub-Parts of A Question Must Be Answered at One Place Only, Otherwise It Will Not Be Valued. C) Missing Data Can Be Assumed SuitablyDokument1 SeiteB) All Sub-Parts of A Question Must Be Answered at One Place Only, Otherwise It Will Not Be Valued. C) Missing Data Can Be Assumed SuitablyGayathri KalyankarNoch keine Bewertungen

- Department Semester Subject Code Subject Name: ECE 6 6EC2 Microprocessor and MicrocontrollerDokument3 SeitenDepartment Semester Subject Code Subject Name: ECE 6 6EC2 Microprocessor and Microcontrollerektagoyal273Noch keine Bewertungen

- ECE211 Digital ElectronicsDokument3 SeitenECE211 Digital Electronicstejaputta6Noch keine Bewertungen

- Advanced Virtual InstrumentationDokument1 SeiteAdvanced Virtual InstrumentationSangeetha VeeraNoch keine Bewertungen

- R5311303 Principles of CommunicationsDokument1 SeiteR5311303 Principles of CommunicationssivabharathamurthyNoch keine Bewertungen

- SWITCHINNG THEORY AND LOGIC DESIGN Jan 2023Dokument8 SeitenSWITCHINNG THEORY AND LOGIC DESIGN Jan 2023drkhamuruddeenNoch keine Bewertungen

- Switchinng Theory and Logic Design Feb 2022Dokument2 SeitenSwitchinng Theory and Logic Design Feb 2022panda pavanNoch keine Bewertungen

- Question Bank: Ec6302 Digital ElectronicsDokument14 SeitenQuestion Bank: Ec6302 Digital ElectronicsBarry SmithNoch keine Bewertungen

- Ec1312 DLCDokument5 SeitenEc1312 DLCDeepak RavichandranNoch keine Bewertungen

- Unit 1Dokument1 SeiteUnit 1Asokan ChinnasamyNoch keine Bewertungen

- DPSDDokument24 SeitenDPSDdigital1206Noch keine Bewertungen

- See AdddDokument2 SeitenSee Addd1ms21ec132Noch keine Bewertungen

- EE-361 Feedback Control Systems Introduction To Simulink and Data Acquisition Experiment # 2Dokument23 SeitenEE-361 Feedback Control Systems Introduction To Simulink and Data Acquisition Experiment # 2Shiza ShakeelNoch keine Bewertungen

- AssignmentDokument2 SeitenAssignmentjihadNoch keine Bewertungen

- Assignment 2: Communication TheoryDokument2 SeitenAssignment 2: Communication TheoryJahnavi RameshNoch keine Bewertungen

- Digital Logic Design and Microprocessor 2Dokument4 SeitenDigital Logic Design and Microprocessor 2Aditya VibhuteNoch keine Bewertungen

- B. Tech: Microprocessor and Its ApplicationsDokument1 SeiteB. Tech: Microprocessor and Its ApplicationsAnant VermaNoch keine Bewertungen

- Digital Logic CircuitsDokument20 SeitenDigital Logic CircuitsrameshsophidarlaNoch keine Bewertungen

- Question # 1 2 3 4 5 Total Total Marks 5 5 5 5 5 25 Obtained MarksDokument11 SeitenQuestion # 1 2 3 4 5 Total Total Marks 5 5 5 5 5 25 Obtained MarksFarah DurraniNoch keine Bewertungen

- Filter ImplementationDokument3 SeitenFilter Implementation김예린[학생](전자정보대학 생체의공학과)Noch keine Bewertungen

- Eda Paper of TestDokument2 SeitenEda Paper of TestSameer ShahNoch keine Bewertungen

- M.E. (VLSI & Embedded Systems) Analog & Digital Cmos Ic Design (2008 Course)Dokument4 SeitenM.E. (VLSI & Embedded Systems) Analog & Digital Cmos Ic Design (2008 Course)Manu SeaNoch keine Bewertungen

- Srinivasa Ramanujan Institute of TechnologyDokument2 SeitenSrinivasa Ramanujan Institute of TechnologyPandu RangareddyNoch keine Bewertungen

- Ece-Iii-Logic Design (10es33) - Assignment PDFDokument3 SeitenEce-Iii-Logic Design (10es33) - Assignment PDFmahesh24pkNoch keine Bewertungen

- Digital CommunicationDokument3 SeitenDigital CommunicationHa ShimNoch keine Bewertungen

- Module-1: Set No. 1Dokument2 SeitenModule-1: Set No. 1Omkar MutalikNoch keine Bewertungen

- Digital Communication System Part A (2 Marks) : UNIT-1Dokument3 SeitenDigital Communication System Part A (2 Marks) : UNIT-1parthidhanNoch keine Bewertungen

- Digital Logic CircuitsDokument15 SeitenDigital Logic CircuitsskblkoNoch keine Bewertungen

- AprMay 2012 (R10)Dokument38 SeitenAprMay 2012 (R10)Rajesh ViswanadhamNoch keine Bewertungen

- Q. P. Code: 08235Dokument8 SeitenQ. P. Code: 08235Mr AnonymousNoch keine Bewertungen

- Question Bank: B.Tech Iii Year - I Sem (R17) (2019-20)Dokument32 SeitenQuestion Bank: B.Tech Iii Year - I Sem (R17) (2019-20)Banoth PavanNoch keine Bewertungen

- BFSK PDFDokument5 SeitenBFSK PDFRiad Al JuboriNoch keine Bewertungen

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionVon EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNoch keine Bewertungen

- IPTV Delivery Networks: Next Generation Architectures for Live and Video-on-Demand ServicesVon EverandIPTV Delivery Networks: Next Generation Architectures for Live and Video-on-Demand ServicesSuliman Mohamed FatiNoch keine Bewertungen