Beruflich Dokumente

Kultur Dokumente

There Are Basically Two Types of Logic Gate

Hochgeladen von

S BhupendraCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

There Are Basically Two Types of Logic Gate

Hochgeladen von

S BhupendraCopyright:

Verfügbare Formate

There are basically two types of logic gate - a '1' gate and a '3' gate.

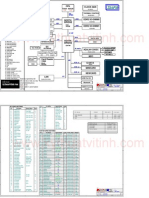

These differ only in the clock phases used to drive them. A gate can have any logic function; thus potentially each and every gate has a customized layout. An example 2-input NAND 1 gate and an inverter 3 gate, together with their clock phases (the example uses NMOS transistors), are shown below:

The 1 and 3 clocks need to be non-overlapping, as do the 2 and 4 clocks. Considering the 1 gate, during the 1 clock high time (also known as the precharge time) the output C precharges up to V(1)-Vth, where Vth represents the threshold of the precharge transistor. During the next quarter clock cycle (the sample time), when 1 is low and 2 is high, C either stays high (if A or B are low) or C gets discharged low (if A and B are high). The A and B inputs must be stable throughout this sample time. The output C becomes valid during this time and therefore a 1 gate output can't drive another 1 gate's inputs. Hence 1 gates have to feed 3 gates and they in turn have to feed 1 gates. One more thing is useful - 2 and 4 gates. A 2 gate precharges on 1 and samples on 3:

and a 4 gate precharges on 3 and samples on 1. Gate interconnection rules are: 1 gates can drive 2 gates and/or 3 gates; 2 gates can drive only 3 gates, 3 gates can drive 4 gates and/or 1 gates, 4 gates can drive only 1 gates:

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- 05 Logistic RegressionDokument4 Seiten05 Logistic RegressionS BhupendraNoch keine Bewertungen

- Car Loan Behavior and Customer RetentionDokument6 SeitenCar Loan Behavior and Customer RetentionS BhupendraNoch keine Bewertungen

- 04 Metrics in ClassificationDokument3 Seiten04 Metrics in ClassificationS BhupendraNoch keine Bewertungen

- 03 R Square and Adjusted R SquareDokument4 Seiten03 R Square and Adjusted R SquareS BhupendraNoch keine Bewertungen

- ## Multicollinearity CheckingDokument3 Seiten## Multicollinearity CheckingS BhupendraNoch keine Bewertungen

- 06 MultiClass ClassificationDokument16 Seiten06 MultiClass ClassificationS BhupendraNoch keine Bewertungen

- Bhupendra Linux 01-01-2020Dokument3 SeitenBhupendra Linux 01-01-2020S BhupendraNoch keine Bewertungen

- IsdnDokument18 SeitenIsdnIchbal ItachiNoch keine Bewertungen

- Centre For Personnel Talent Management (Ceptam) Defence Research & Development Organisation (Drdo) Ministry of Defence, Govt of IndiaDokument3 SeitenCentre For Personnel Talent Management (Ceptam) Defence Research & Development Organisation (Drdo) Ministry of Defence, Govt of IndiaS BhupendraNoch keine Bewertungen

- ACIO Iiexe 2013 Detailed AdvtDokument10 SeitenACIO Iiexe 2013 Detailed AdvtBhasker Nayak DharavathNoch keine Bewertungen

- Recording Request Form: North Videocon MP STV25 STV27 MCA OBD Hindi 3 FemaleDokument1 SeiteRecording Request Form: North Videocon MP STV25 STV27 MCA OBD Hindi 3 FemaleS BhupendraNoch keine Bewertungen

- Recording Request Form: North Videocon MP STV25 STV27 MCA OBD Hindi 3 FemaleDokument1 SeiteRecording Request Form: North Videocon MP STV25 STV27 MCA OBD Hindi 3 FemaleS BhupendraNoch keine Bewertungen

- Recording Request Form: North Videocon MPDokument1 SeiteRecording Request Form: North Videocon MPS BhupendraNoch keine Bewertungen

- Recording Request Form: North Videocon MPDokument1 SeiteRecording Request Form: North Videocon MPS BhupendraNoch keine Bewertungen

- Ccna PDFDokument3 SeitenCcna PDFcalhabardoNoch keine Bewertungen

- Bill GtesSalary SlipDokument2 SeitenBill GtesSalary SlipS BhupendraNoch keine Bewertungen

- My Mark SheetsDokument1 SeiteMy Mark SheetsS BhupendraNoch keine Bewertungen

- 2Dokument46 Seiten2S BhupendraNoch keine Bewertungen

- Inder Singh Rawat: - 39, Street No-06, Amrit Vihar, Burari Delhi-110084 Contact:9013961389 011-27611008Dokument1 SeiteInder Singh Rawat: - 39, Street No-06, Amrit Vihar, Burari Delhi-110084 Contact:9013961389 011-27611008S BhupendraNoch keine Bewertungen

- 02aug Sub Logs MPDokument11 Seiten02aug Sub Logs MPS BhupendraNoch keine Bewertungen

- A Poem by BsaDokument1 SeiteA Poem by BsaS BhupendraNoch keine Bewertungen

- JABBHIDokument1 SeiteJABBHIS BhupendraNoch keine Bewertungen

- AaaDokument3 SeitenAaaS BhupendraNoch keine Bewertungen

- Shiva RudrashtakamDokument2 SeitenShiva RudrashtakamS BhupendraNoch keine Bewertungen

- Noc OverviewDokument2 SeitenNoc OverviewS BhupendraNoch keine Bewertungen

- Recording Request Form: North Videocon MPDokument1 SeiteRecording Request Form: North Videocon MPS BhupendraNoch keine Bewertungen

- Recording Request Form: North Videocon MPDokument1 SeiteRecording Request Form: North Videocon MPS BhupendraNoch keine Bewertungen

- Railway Recruitment Board (RRB) NotificationDokument16 SeitenRailway Recruitment Board (RRB) NotificationFreshers Plane India100% (2)

- Borad Restart in Datacom WAVEDokument1 SeiteBorad Restart in Datacom WAVES BhupendraNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Ec8791 Erts QBDokument8 SeitenEc8791 Erts QBRajarajeswari KannanNoch keine Bewertungen

- Catalogo Colectora Carlson Mini2 ENGDokument2 SeitenCatalogo Colectora Carlson Mini2 ENGChristian Camilo Gómez BautistaNoch keine Bewertungen

- Parasplit: A Scalable Architecture On Fpga For Terabit Packet ClassificationDokument8 SeitenParasplit: A Scalable Architecture On Fpga For Terabit Packet ClassificationDevNoch keine Bewertungen

- Managing Alarms in SCADA Expert Vijeo Citect 7.5Dokument84 SeitenManaging Alarms in SCADA Expert Vijeo Citect 7.5phongNoch keine Bewertungen

- Siprotec 5 Configuration May 29, 2017 2:18 PM: Note On Function-Points ClassDokument6 SeitenSiprotec 5 Configuration May 29, 2017 2:18 PM: Note On Function-Points ClassOae FlorinNoch keine Bewertungen

- Scope Planning Management Summary NotesDokument14 SeitenScope Planning Management Summary NotesGeorge NjolomaNoch keine Bewertungen

- Siemens 6GK1500 0FC10 DatasheetDokument2 SeitenSiemens 6GK1500 0FC10 DatasheetJosé CarlosNoch keine Bewertungen

- BR 14 01 ENG Fusion4 MSC L BrochureDokument8 SeitenBR 14 01 ENG Fusion4 MSC L BrochureJavier Alejandro QuingaNoch keine Bewertungen

- Software Requirements SpecificationDokument16 SeitenSoftware Requirements SpecificationPheesayor 'Phyzzle' AdewunmiNoch keine Bewertungen

- Final Project Report On e Commerce Shopping WebsiteDokument80 SeitenFinal Project Report On e Commerce Shopping WebsiteOmkarNoch keine Bewertungen

- TR 3647Dokument4 SeitenTR 3647batungNoch keine Bewertungen

- Substation Automation SolutionsDokument6 SeitenSubstation Automation Solutions3319826Noch keine Bewertungen

- 2020 - Superfetch - The Famous Unknown SpyDokument14 Seiten2020 - Superfetch - The Famous Unknown Spyrohto1945Noch keine Bewertungen

- UG Syllabus DCSE Acad Year 2020-21 Onwards - For - UPLOADDokument173 SeitenUG Syllabus DCSE Acad Year 2020-21 Onwards - For - UPLOADkhushiNoch keine Bewertungen

- EN Spec TU-S9 (V1.1 1.2)Dokument2 SeitenEN Spec TU-S9 (V1.1 1.2)jusufjNoch keine Bewertungen

- Static Program Analysis: Anders Møller and Michael I. SchwartzbachDokument6 SeitenStatic Program Analysis: Anders Møller and Michael I. SchwartzbachDoob StrifeNoch keine Bewertungen

- 28Ghz 2-Way Wilkinson Power Divider: Description FeaturesDokument2 Seiten28Ghz 2-Way Wilkinson Power Divider: Description FeaturesMuhammad AkhtarNoch keine Bewertungen

- Ericsson W-Cdma Bbu/rru SystemDokument2 SeitenEricsson W-Cdma Bbu/rru SystemAbdeladhim Stich67% (3)

- OS Question PaperDokument2 SeitenOS Question PaperBrinda BMNoch keine Bewertungen

- CLASS XI Operators - and - ExpressionsDokument13 SeitenCLASS XI Operators - and - ExpressionsAmisha DalalNoch keine Bewertungen

- Modicon M241 - TM241C24RDokument12 SeitenModicon M241 - TM241C24Rfeinrae3Noch keine Bewertungen

- GRUB - ArchWikiDokument37 SeitenGRUB - ArchWikiAstin GengoNoch keine Bewertungen

- Communicate With S7-1200 Via EhernetDokument6 SeitenCommunicate With S7-1200 Via EhernetRegisNoch keine Bewertungen

- Brain Wave MachineDokument4 SeitenBrain Wave MachineJhony_Quintero_7874Noch keine Bewertungen

- Troubleshooting VXLAN BGP VPNDokument103 SeitenTroubleshooting VXLAN BGP VPNNguyễn Đức KiênNoch keine Bewertungen

- CoSc4181-Lab-5 (Lect-6-Laravel-Rest)Dokument24 SeitenCoSc4181-Lab-5 (Lect-6-Laravel-Rest)Abebaw AmareNoch keine Bewertungen

- Samsung Scx-6345 Scx-6345n Service Manual Repair GuideDokument309 SeitenSamsung Scx-6345 Scx-6345n Service Manual Repair GuideRay Boone50% (2)

- Chs Assignment 1Dokument7 SeitenChs Assignment 1Kiruba KaranNoch keine Bewertungen

- Asus Z84FMDokument66 SeitenAsus Z84FMNicu LiviuNoch keine Bewertungen

- Keyboard/Display Controller - Intel 8279Dokument16 SeitenKeyboard/Display Controller - Intel 8279Anamika singhNoch keine Bewertungen