Beruflich Dokumente

Kultur Dokumente

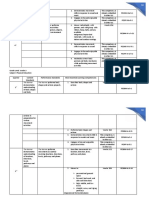

Ejercicio de Clase Maquina de Estados

Hochgeladen von

hector_vilcaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ejercicio de Clase Maquina de Estados

Hochgeladen von

hector_vilcaCopyright:

Verfügbare Formate

----------------------------------------------------------------------------------- Company: -- Engineer: --- Create Date: 17:05:08 05/07/2013 -- Design Name: -- Module Name: maq - Behavioral -- Project

Name: -- Target Devices: -- Tool versions: -- Description: --- Dependencies: --- Revision: -- Revision 0.01 - File Created -- Additional Comments: ----------------------------------------------------------------------------------library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.

--library UNISIM; --use UNISIM.VComponents.all;

entity maq is Port ( clk : in STD_LOGIC; rst : in STD_LOGIC; a : in STD_LOGIC; b : in STD_LOGIC; z : out STD_LOGIC); end maq;

architecture Behavioral of maq is type estados is (s0,s1); signal ep,es: estados; begin process(clk,rst) begin if(rst='1')then ep<=s0; elsif(rising_edge(clk))then ep<=es; end if; end process;

process(a,b,ep) begin

case ep is when s0 => if a='1' then es<=s1; else es<=s0; end if; when s1 => if b='1' then es<=s0; else es<=s1; end if; end case; end process;

process(ep) begin case ep is when s0 => z<='0'; when s1 => z<='1'; end case; end process;

end Behavioral;

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Conservation Assignment 02Dokument16 SeitenConservation Assignment 02RAJU VENKATANoch keine Bewertungen

- Jee MainsDokument32 SeitenJee Mainsjhaayushbhardwaj9632Noch keine Bewertungen

- Odisha State Museum-1Dokument26 SeitenOdisha State Museum-1ajitkpatnaikNoch keine Bewertungen

- Gracie Warhurst WarhurstDokument1 SeiteGracie Warhurst Warhurstapi-439916871Noch keine Bewertungen

- Komunikasi Sebagai Piranti Kebijakan Bi: Materi SESMABI Mei 2020Dokument26 SeitenKomunikasi Sebagai Piranti Kebijakan Bi: Materi SESMABI Mei 2020syahriniNoch keine Bewertungen

- EdisDokument227 SeitenEdisThong Chan100% (1)

- 1995 Biology Paper I Marking SchemeDokument13 Seiten1995 Biology Paper I Marking Schemetramysss100% (2)

- PE MELCs Grade 3Dokument4 SeitenPE MELCs Grade 3MARISSA BERNALDONoch keine Bewertungen

- Blockchains: Architecture, Design and Use CasesDokument26 SeitenBlockchains: Architecture, Design and Use Caseseira kNoch keine Bewertungen

- Upes School of Law Lac & Adr Association: PresentsDokument7 SeitenUpes School of Law Lac & Adr Association: PresentsSuvedhya ReddyNoch keine Bewertungen

- To Study Customer Relationship Management in Big BazaarDokument45 SeitenTo Study Customer Relationship Management in Big BazaarAbhi KengaleNoch keine Bewertungen

- Feed-Pump Hydraulic Performance and Design Improvement, Phase I: J2esearch Program DesignDokument201 SeitenFeed-Pump Hydraulic Performance and Design Improvement, Phase I: J2esearch Program DesignJonasNoch keine Bewertungen

- Module 1 Lesson 2Dokument31 SeitenModule 1 Lesson 2Angela Rose BanastasNoch keine Bewertungen

- 1916 South American Championship Squads - WikipediaDokument6 Seiten1916 South American Championship Squads - WikipediaCristian VillamayorNoch keine Bewertungen

- Battery Guide - 2021Dokument27 SeitenBattery Guide - 2021Mario LaurieNoch keine Bewertungen

- Building and Structural Construction N6 T1 2024 T2Dokument9 SeitenBuilding and Structural Construction N6 T1 2024 T2FranceNoch keine Bewertungen

- 5 Minute Pediatric ConsultDokument5 Seiten5 Minute Pediatric Consultajescool0% (4)

- Standard Test Methods For Rheological Properties of Non-Newtonian Materials by Rotational (Brookfield Type) ViscometerDokument8 SeitenStandard Test Methods For Rheological Properties of Non-Newtonian Materials by Rotational (Brookfield Type) ViscometerRodrigo LopezNoch keine Bewertungen

- Siemens Rapidlab 248, 348, 840, 845, 850, 855, 860, 865: Reagents & ControlsDokument2 SeitenSiemens Rapidlab 248, 348, 840, 845, 850, 855, 860, 865: Reagents & ControlsJuan Carlos CrespoNoch keine Bewertungen

- MME 52106 - Optimization in Matlab - NN ToolboxDokument14 SeitenMME 52106 - Optimization in Matlab - NN ToolboxAdarshNoch keine Bewertungen

- Basic Econometrics Questions and AnswersDokument3 SeitenBasic Econometrics Questions and AnswersRutendo TarabukuNoch keine Bewertungen

- Union Test Prep Nclex Study GuideDokument115 SeitenUnion Test Prep Nclex Study GuideBradburn Nursing100% (2)

- Business-Communication Solved MCQs (Set-3)Dokument8 SeitenBusiness-Communication Solved MCQs (Set-3)Pavan Sai Krishna KottiNoch keine Bewertungen

- T5 B11 Victor Manuel Lopez-Flores FDR - FBI 302s Re VA ID Cards For Hanjour and Almihdhar 195Dokument11 SeitenT5 B11 Victor Manuel Lopez-Flores FDR - FBI 302s Re VA ID Cards For Hanjour and Almihdhar 1959/11 Document Archive100% (2)

- EN 50122-1 January 2011 Corrientes RetornoDokument81 SeitenEN 50122-1 January 2011 Corrientes RetornoConrad Ziebold VanakenNoch keine Bewertungen

- The Mane Reason - UNDERSTANDING CONSUMER BEHAVIOUR TOWARDS NATURAL HAIR PRODUCTS IN GHANADokument68 SeitenThe Mane Reason - UNDERSTANDING CONSUMER BEHAVIOUR TOWARDS NATURAL HAIR PRODUCTS IN GHANAYehowadah OddoyeNoch keine Bewertungen

- 레벨 테스트Dokument2 Seiten레벨 테스트BNoch keine Bewertungen

- Acc116 Dec 2022 - Q - Test 1Dokument6 SeitenAcc116 Dec 2022 - Q - Test 12022825274100% (1)

- Morfologi Dan Citra Kota Kawasan Kauman, Kecamatan Juwana, Kabupaten Pati The Morphology and Image of Kauman Town, Juwana Sub District, Pati RegencyDokument16 SeitenMorfologi Dan Citra Kota Kawasan Kauman, Kecamatan Juwana, Kabupaten Pati The Morphology and Image of Kauman Town, Juwana Sub District, Pati RegencyRABIAH ARDIANTI TUM TOMAGOLANoch keine Bewertungen

- Ducted Split ACsDokument31 SeitenDucted Split ACsHammadZaman100% (1)