Beruflich Dokumente

Kultur Dokumente

AlarmaTemperaturaPr 5

Hochgeladen von

imperia76Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

AlarmaTemperaturaPr 5

Hochgeladen von

imperia76Copyright:

Verfügbare Formate

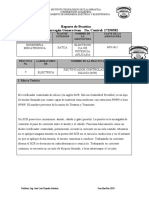

Problema 5 Un proceso qumico posee tres indicadores de la temperatura del punto P cuyas salidas T1, T2, y T3 adoptan dos

niveles de tensin bien diferenciados segn la temperatura sea menor, o mayor-igual a t1, t2, t3 respectivamente (t1< t2< t3). Se asigna el valor cero al nivel de tensin correspondiente a una temperatura inferior a t, y el valor uno al nivel correspondiente a una temperatura superior o igual a t. Se desea generar una seal que: Adopte un nivel de tensin alto (1 lgico) si la temperatura est comprendida entre t1 y t2 Adopte un nivel de tensin alto si la temperatura es superior o igual a t3 Adopte un nivel de tensin bajo en cualquier otro caso diferente a los descritos anteriormente. Disear esa funcin lgica usando: puertas NAND y NOR Respuesta:

Paso 2: Tabla de verdad minterm/Maxterm m0 / M0 m1 / M1 m2 / M2 m3 / M3 m4 / M4 m5 / M5 m6 / M6 m7 / M7 T3 0 0 0 0 1 1 1 1 T2 0 0 1 1 0 0 1 1 T1 0 1 0 1 0 1 0 1 S 0 1 X 0 X X X 1

F (T3 , T2 , T1 ) = (1,7) + d (2,4,5,6) para minterms (Primera forma cannica SoP) F (T3 , T2 , T1 ) = (0,3) D(2,4,5,6) para Maxterms (Segunda forma cannica PoS) Paso 3: Simplificacin del circuito

Figura 1: A partir de minterms

Figura 2: A partir de Maxterms

F (T3 , T2 , T1 ) = T3 + T2T1 funcin simplificada a partir de minterms

F (T3 , T2 , T1 ) = T1 [T3 + T2 ] funcin simplificada a partir de Maxterms

Tabla de verdad resultante

T3 0 0 0 0 1 1 1 1

T2 0 0 1 1 0 0 1 1

T1 0 1 0 1 0 1 0 1

S 0 1 X 0 X X X 1

S(minterms) 0 1 0 0 1 1 1 1

S(Maxterms) 0 1 0 0 0 1 0 1

Podemos observar que los trminos indiferentes o imposibles, se han convertido en 0 o 1 al realizar la simplificacin. Resolucin empleando slo puertas NAND o slo puertas NOR a) Slo puertas NAND, partimos de la forma sop de la funcin simplificada, negamos dos veces y aplicamos el teorema de De Morgan:

F (T3 , T2 , T1 ) = T3 + T2T1 = T3 + T2T1 = T3 T2T1

b) Slo puertas NOR, partimos de la forma pos de la funcin simplificada, negamos dos veces y aplicamos el teorema de De Morgan:

F (T3 , T2 , T1 ) = T1 [T3 + T2 ] = T1 [T3 + T2 ] = T1 + T3 + T2

Esquema del circuito

Figura 3: Esquema del circuito en el que se han fusionado varias respuestas. Realmente slo nos piden el circuito cuya salida es fnand y el circuito cuya salida es fnor. Adems, se emplean tres tipos de inversores: inversor normal (vlido para las funciones fsop y fpos), utilizando una puerta NAND (este es el que hay que emplear en el caso de implementar el circuito slo con puertas NAND y solamente este) y utilizando una puerta NOR (este es el que hay que emplear en el caso de implementar el circuito slo con puertas NOR y solamente este).

Cronograma del circuito

Figura 4: Cronograma del circuito con todas las posibles combinaciones de entrada. Se pueden apreciar los retardos.

Das könnte Ihnen auch gefallen

- Laboratorio - 2 - Logica DigitalDokument5 SeitenLaboratorio - 2 - Logica DigitalSanchez EliseoNoch keine Bewertungen

- Practicas 2Dokument2 SeitenPracticas 2xodriNoch keine Bewertungen

- LABORATORIO 3 Rectificadores Trifásicos Carga RLDokument10 SeitenLABORATORIO 3 Rectificadores Trifásicos Carga RLJ Av IerNoch keine Bewertungen

- Contador de 0-99 Con AlarmaDokument3 SeitenContador de 0-99 Con AlarmaMarvin GarcíaNoch keine Bewertungen

- Amplificador de Instrumentación - Práctica 1Dokument11 SeitenAmplificador de Instrumentación - Práctica 1imt.jlgc100% (1)

- Circuito Derivador e IntegradorDokument6 SeitenCircuito Derivador e IntegradorBryan Tiago FonsecaNoch keine Bewertungen

- Ejercicios Propuestos ElectronicaDokument1 SeiteEjercicios Propuestos ElectronicaJuan0% (1)

- Control de Llenado de Un Tanque IndustrialDokument9 SeitenControl de Llenado de Un Tanque IndustrialAlexis Núñez GonzálezNoch keine Bewertungen

- Reguladores e Interruptores Estáticos de AlternaDokument10 SeitenReguladores e Interruptores Estáticos de AlternaGiovanny Cifuentes100% (1)

- Ejercicios de amplificadores con transistores BJT y MOSFETDokument10 SeitenEjercicios de amplificadores con transistores BJT y MOSFETPablo V SalazarNoch keine Bewertungen

- Practica 4 Contador AsincronoDokument5 SeitenPractica 4 Contador AsincronoRulo PinedaNoch keine Bewertungen

- S05 - Sistemas Combinacionales IIDokument38 SeitenS05 - Sistemas Combinacionales IImicuantaNoch keine Bewertungen

- El Transistor Como InterruptorDokument4 SeitenEl Transistor Como InterruptorAlejandra Gallego GonzalezNoch keine Bewertungen

- Ejercicio de TermodinamicaDokument3 SeitenEjercicio de Termodinamicacrisalida suarezNoch keine Bewertungen

- Informe Practica Final FPGADokument15 SeitenInforme Practica Final FPGASilvi SilvidosNoch keine Bewertungen

- Practrica 4 Electronica de PotenciaDokument5 SeitenPractrica 4 Electronica de Potenciagenaro muozNoch keine Bewertungen

- MultivibradoresDokument39 SeitenMultivibradoresGabriel Alejandro Astete VargasNoch keine Bewertungen

- Lab Electronica 02 NDokument13 SeitenLab Electronica 02 NEdgar TelloNoch keine Bewertungen

- 9 Diseño de Sistemas Secuenciales TeamsDokument35 Seiten9 Diseño de Sistemas Secuenciales TeamsPaola de LeonNoch keine Bewertungen

- Potenciador y RadicacionDokument3 SeitenPotenciador y RadicacionRobertNoch keine Bewertungen

- Movimiento de RototraslacionDokument6 SeitenMovimiento de RototraslacionFranciscoNoch keine Bewertungen

- Experiencia 5-ACE PDFDokument14 SeitenExperiencia 5-ACE PDFLuis CuchoNoch keine Bewertungen

- Lab 3 - Amplificador SumadorDokument10 SeitenLab 3 - Amplificador SumadorSebastian AcerosNoch keine Bewertungen

- Oscilador HartleyDokument4 SeitenOscilador Hartleynelson trullo tafurNoch keine Bewertungen

- Amplificador OperacionalDokument9 SeitenAmplificador OperacionalJoHaN ESPOCITONoch keine Bewertungen

- Dispositivos de potenciaDokument11 SeitenDispositivos de potenciaFabiola OrtuñoNoch keine Bewertungen

- Buffer TriestadoDokument2 SeitenBuffer TriestadoAlicia MagañaNoch keine Bewertungen

- TRIAC: Comportamiento y funcionamiento del dispositivo de control de potenciaDokument7 SeitenTRIAC: Comportamiento y funcionamiento del dispositivo de control de potenciaLuis SanabriaNoch keine Bewertungen

- Solucionario RecortadoDokument52 SeitenSolucionario RecortadoBrenda GallegosNoch keine Bewertungen

- Informe Proyecto Final Instrumentaci N y Control Control PID para Un Sistema Ball and Beam 2 PDFDokument5 SeitenInforme Proyecto Final Instrumentaci N y Control Control PID para Un Sistema Ball and Beam 2 PDFMiguel Angel GomezNoch keine Bewertungen

- Informe N1 de Laboratorio Sistemas DigitalesDokument14 SeitenInforme N1 de Laboratorio Sistemas DigitalesWilmer Cubas SolanoNoch keine Bewertungen

- Practica 5 Multiplexor y DemultiplexorDokument8 SeitenPractica 5 Multiplexor y DemultiplexorNicolas Garcia Aranda De MartinezNoch keine Bewertungen

- Lógica CableadaDokument4 SeitenLógica CableadaRonald Barcia0% (1)

- Errores de Acondicionamiento de SeñalesDokument6 SeitenErrores de Acondicionamiento de SeñalesAlejandro GuarderasNoch keine Bewertungen

- Laboratorio 7 - Circuitos Aritméticos RestadoresDokument9 SeitenLaboratorio 7 - Circuitos Aritméticos RestadoresIan MelgarejoNoch keine Bewertungen

- Eol002u2 7790 Ep PDFDokument2 SeitenEol002u2 7790 Ep PDFjavier rolandoNoch keine Bewertungen

- Funcion de Transferencia, Diagramas de MansonDokument12 SeitenFuncion de Transferencia, Diagramas de MansonBryan PupialesNoch keine Bewertungen

- Lab2 Grupo5 4805Dokument25 SeitenLab2 Grupo5 4805Nayro PazmiñoNoch keine Bewertungen

- Principales diferencias TTL CMOSDokument8 SeitenPrincipales diferencias TTL CMOSWilson AcarapiNoch keine Bewertungen

- Practica 2 Caracteristicas DiodosDokument4 SeitenPractica 2 Caracteristicas DiodosCarlos JuradoNoch keine Bewertungen

- CTM Ejemplo - Modelación Del Experimento Barra y BolaDokument7 SeitenCTM Ejemplo - Modelación Del Experimento Barra y BolaWilson Barco MNoch keine Bewertungen

- Deber 4Dokument4 SeitenDeber 4Cristian IpialesNoch keine Bewertungen

- Circuito Primer Orden RCDokument9 SeitenCircuito Primer Orden RCDayiito Morales100% (1)

- EJERCICIOS SISTEMAS DIGITAL 2°parcialDokument7 SeitenEJERCICIOS SISTEMAS DIGITAL 2°parciallokilloNoch keine Bewertungen

- Clase 5 Circuitos CombinacionalesDokument27 SeitenClase 5 Circuitos CombinacionalesJohanna J. Pérez DucasaNoch keine Bewertungen

- Circuito con diodo y L: corrientes i(S1) y i(DmDokument2 SeitenCircuito con diodo y L: corrientes i(S1) y i(DmDiego A CruzNoch keine Bewertungen

- Controlador de voltaje AC trifásico de onda completa totalmente controladoDokument3 SeitenControlador de voltaje AC trifásico de onda completa totalmente controladoalejoNoch keine Bewertungen

- Reporte de laboratorio sobre compuertas lógicas y álgebra de Boole de la UNIDokument4 SeitenReporte de laboratorio sobre compuertas lógicas y álgebra de Boole de la UNIAder Hariel Treminio Montoya100% (1)

- Taller2 Control Secuencial PLC AVANZADO Ceres DoradaDokument2 SeitenTaller2 Control Secuencial PLC AVANZADO Ceres DoradaMARIA CAMILA ARIAS GIRALDONoch keine Bewertungen

- SCR: Rectificador controlado de silicioDokument4 SeitenSCR: Rectificador controlado de silicioDiego CastilloNoch keine Bewertungen

- Informe Laboratorio 8Dokument27 SeitenInforme Laboratorio 8Sebastian CespedesNoch keine Bewertungen

- Amplificadores InformeDokument10 SeitenAmplificadores InformeAlex OñaNoch keine Bewertungen

- Informe TermistorDokument14 SeitenInforme TermistorErick CordovaNoch keine Bewertungen

- Lab N°1 AMPLIFICADORES DE AUDIODokument8 SeitenLab N°1 AMPLIFICADORES DE AUDIOEDISON FELIPE LEÓN VEGANoch keine Bewertungen

- Termistor PicDokument2 SeitenTermistor PicCarlos Aranda100% (2)

- Rectificador de Onda CompletaDokument11 SeitenRectificador de Onda CompletaTu Lokito Ninito CristhianNoch keine Bewertungen

- Laboratorio#3Dokument5 SeitenLaboratorio#3Sergio100% (1)

- Circuitos neumáticos: válvulas y temporizadoresDokument3 SeitenCircuitos neumáticos: válvulas y temporizadoresKancoGonzalesCNoch keine Bewertungen

- Apuntes de Control Digital de La Unidad 1Dokument29 SeitenApuntes de Control Digital de La Unidad 1santiago pablo albertoNoch keine Bewertungen

- Representación de Sistemas en Variables de EstadoDokument10 SeitenRepresentación de Sistemas en Variables de EstadoJuan LivingstonNoch keine Bewertungen