Beruflich Dokumente

Kultur Dokumente

Dem LCD

Hochgeladen von

Vo Phong PhuOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Dem LCD

Hochgeladen von

Vo Phong PhuCopyright:

Verfügbare Formate

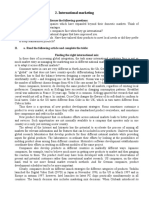

library IEEE; use IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.

ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity LCD23_00 is Port ( CK100 : in STD_LOGIC; RST : in STD_LOGIC; DB : out STD_LOGIC_VECTOR (7 downto 0); RS : out STD_LOGIC; RW : out STD_LOGIC; E : out STD_LOGIC; SETUP : in STD_LOGIC; START : in STD_LOGIC; STOP : in STD_LOGIC; EXI : in STD_LOGIC; BW : in STD_LOGIC_VECTOR (5 downto 0)); end LCD23_00; architecture Behavioral of LCD23_00 is TYPE STATE IS (POWER_UP_DELAY, FUNCTION_SET, DISPLAY_CONTROL, CLEAR_DISPLAY, RETURN_HOME, SET_DDRAM, STRING_DISPLAY); SIGNAL PR_STATE,NX_STATE : STATE:=POWER_UP_DELAY; SIGNAL THOIGIAN,THOIGIANX,J:INTEGER; TYPE MANG IS ARRAY(0 TO 9) OF STD_LOGIC_VECTOR(7 DOWNTO 0); CONSTANT MASCII: MANG:=(X"30",X"31",X"32",X"33",X"34",X"35",X"36",X"37",X"38",X" 39"); --TYPE MANG2 IS ARRAY(0 TO 5) OF STD_LOGIC_VECTOR(7 DOWNTO 0); --CONSTANT MACHU: MANG:=(X"53",X"45",X"54",X"20",X"55",X"50"); TYPE MANG1 IS ARRAY(0 TO 15) OF STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL MATIME: MANG1:=(X"20",X"20",X"20",X"20",X"20",X"20",X"20",X"20",X"20",X"2 0",X"20",X"20",X"20",X"20",X"20",X"20"); SIGNAL CHIA:STD_LOGIC_VECTOR(27 DOWNTO 0):=X"0000000"; SIGNAL CK1HZ:STD_LOGIC; SIGNAL CH1 : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL DV1 : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL CH2 : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL DV2 : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL DEM: INTEGER:=0; SIGNAL T: INTEGER; SIGNAL TT,TT1: STD_LOGIC; begin PROCESS(CK100,CHIA,CK1HZ) BEGIN IF FALLING_EDGE(CK100) THEN

IF CHIA=X"17D7840" THEN CHIA<=X"0000000"; CK1HZ <= NOT CK1HZ; ELSE CHIA<=CHIA+1; END IF; END IF; END PROCESS; --------------------------------------------------------------------------------------------------PROCESS VARIABLE SO: INTEGER; BEGIN SO:=0; IF EXI='1' THEN TT<='1'; ELSIF SETUP='1' THEN TT<='0';--TT1<='0'; ELSE IF TT='1' THEN TT<='1'; ELSIF TT='0' THEN TT<='0'; END IF; END IF; IF START='1' THEN TT1<='1'; ELSIF STOP='1' THEN TT1<='0'; ELSE IF TT1='1' THEN TT1<='1'; ELSIF TT1='0' THEN TT1<='0'; END IF; END IF; IF TT='1' THEN TT1<='0'; MATIME(1)<= MATIME(2)<= MATIME(3)<= MATIME(4)<= MATIME(5)<= MATIME(6)<= ELSE IF TT1='0' THEN FOR I IN 0 TO 5 LOOP IF BW(I)='1' THEN SO := SO+ 2**I; END IF; END LOOP; T<=SO; CH1<=MASCII(T/10); DV1<=MASCII(T-10*(T/10));

X"53"; X"45"; X"54"; X"20"; X"55"; X"50";

CH2<=X"30"; DV2<=X"30"; MATIME(1)<=CH1; MATIME(2)<=DV1; MATIME(3)<=X"3A"; MATIME(4)<=CH2; MATIME(5)<=DV2; MATIME(6)<=X"20"; --END IF; --END IF; ELSE IF RISING_EDGE(CK1HZ) THEN T<=T; DEM<=DE M+1; IF DEM=T THEN DEM<=0; END IF; END IF; CH1<=MASCII(T/10); DV1<=MASCII(T-10*(T/10)); CH2<=MASCII(DEM/10); DV2<=MASCII(DEM-10*(DEM/10)); MATIME(1)<=CH1; MATIME(2)<=DV1; MATIME(3)<=X"3A"; MATIME(4)<=CH2; MATIME(5)<=DV2; MATIME(6)<=X"20"; END IF; END IF; END PROCESS; PROCESS(RST,CK100) BEGIN IF RST='1' THEN THOIGIAN<=0; J<=0; PR_STATE<=POWER_UP_DELAY; ELSIF RISING_EDGE(CK100) THEN PR_STATE<=NX_STATE; IF THOIGIAN=THOIGIANX THEN THOIGIAN<=0; IF PR_STATE=STRING_DISPLAY THEN IF J=MATIME'HIGH THEN J<=0; ELSE J<=J+1; END IF; END IF; ELSE THOIGIAN<=THOIGIAN+1; END IF; END IF; END PROCESS; -----------------------------PROCESS(PR_STATE) BEGIN CASE PR_STATE IS WHEN POWER_UP_DELAY => THOIGIANX<=3200000; DB<=X"00"; RS<='0'; RW<='0'; IF THOIGIAN=THOIGIANX THEN NX_STATE<=FUNCTION_SET;

ELSE NX_STATE<=POWER_UP_DELAY; END IF; WHEN FUNCTION_SET => THOIGIANX<=4000; DB<=x"3C"; RS<='0'; RW<='0'; IF THOIGIAN =0 THEN E<='0'; ELSIF THOIGIAN=4 THEN E<='1'; ELSIF THOIGIAN=26 THEN E<='0'; END IF; IF THOIGIAN=THOIGIANX THEN NX_STATE <=DISPLAY_CONTROL; ELSE NX_STATE<=FUNCTION_SET; END IF; WHEN DISPLAY_CONTROL => THOIGIANX<=4000; DB<=X"0C"; RS<='0'; RW<='0'; IF THOIGIAN =0 THEN E<='0'; ELSIF THOIGIAN=4 THEN E<='1'; ELSIF THOIGIAN=26 THEN E<='0'; END IF; IF THOIGIAN=THOIGIANX THEN NX_STATE<=CLEAR_DISPLAY; ELSE NX_STATE<=DISPLAY_CONTROL; END IF; WHEN CLEAR_DISPLAY => THOIGIANX<=164000; DB<=X"01"; RS<='0'; RW<='0'; IF THOIGIAN =0 THEN E<='0'; ELSIF THOIGIAN=4 THEN E<='1'; ELSIF THOIGIAN=26 THEN E<='0'; END IF; IF THOIGIAN=THOIGIANX THEN NX_STATE<=RETURN_HOME; ELSE NX_STATE<=CLEAR_DISPLAY; END IF; WHEN RETURN_HOME => THOIGIANX<=164000; DB<=X"02"; RS<='0'; RW<='0'; IF THOIGIAN =0 THEN E<='0'; ELSIF THOIGIAN=4 THEN E<='1'; ELSIF THOIGIAN=26 THEN E<='0'; END IF; IF THOIGIAN=THOIGIANX THEN NX_STATE<=SET_DDRAM; ELSE NX_STATE<=RETURN_HOME; END IF; WHEN SET_DDRAM => THOIGIANX<=164000; DB<=X"80"; RS<='0'; RW<='0'; IF THOIGIAN =0 THEN E<='0'; ELSIF THOIGIAN=4 THEN E<='1'; ELSIF THOIGIAN=26 THEN E<='0'; END IF; IF THOIGIAN=THOIGIANX THEN NX_STATE<=STRING_DISPLAY; ELSE NX_STATE<=SET_DDRAM;

END IF; WHEN STRING_DISPLAY => THOIGIANX<=4000; DB<=MATIME(J); RS<='1'; RW<='0'; IF THOIGIAN =0 THEN E<='0'; ELSIF THOIGIAN=4 THEN E<='1'; ELSIF THOIGIAN=26 THEN E<='0'; END IF; IF THOIGIAN=THOIGIANX AND J=MATIME'HIGH THEN NX_STATE<=SET_DDRAM ; ELSE NX_STATE<=STRING_DISPLAY; END IF; WHEN OTHERS =>NULL; END CASE; END PROCESS; end Behavioral;

Das könnte Ihnen auch gefallen

- Main - Centrifuge Maintenance Log Template Eppendorf PDFDokument1 SeiteMain - Centrifuge Maintenance Log Template Eppendorf PDFVo Phong Phu100% (1)

- Reading Comprehension Reading Comprehension: Basic Types of Distractors For Part VIDokument10 SeitenReading Comprehension Reading Comprehension: Basic Types of Distractors For Part VIVo Phong PhuNoch keine Bewertungen

- Lit 2 Study Guide PDFDokument33 SeitenLit 2 Study Guide PDFVo Phong PhuNoch keine Bewertungen

- Wzhuang Rls WPCDokument15 SeitenWzhuang Rls WPCVo Phong PhuNoch keine Bewertungen

- Adaptive Equalization Techniques Using Recursive Least Square (RLS) AlgorithmDokument8 SeitenAdaptive Equalization Techniques Using Recursive Least Square (RLS) AlgorithmVo Phong PhuNoch keine Bewertungen

- PC357NJ0000F Series: Mini-Flat Package, General Purpose PhotocouplerDokument14 SeitenPC357NJ0000F Series: Mini-Flat Package, General Purpose PhotocouplerVo Phong PhuNoch keine Bewertungen

- Multisim 9 For EducatorsDokument110 SeitenMultisim 9 For EducatorsHeo Hư HỏngNoch keine Bewertungen

- Bài 3-TT DSPDokument44 SeitenBài 3-TT DSPVo Phong PhuNoch keine Bewertungen

- Bài 2-TT DSPDokument40 SeitenBài 2-TT DSPVo Phong PhuNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- International MarketingDokument3 SeitenInternational MarketingVarga CasianaNoch keine Bewertungen

- Java Programming - Module2021Dokument10 SeitenJava Programming - Module2021steven hernandezNoch keine Bewertungen

- Data Warehouse Massively Parallel Processing Design PatternsDokument28 SeitenData Warehouse Massively Parallel Processing Design PatternsMatthew LawlerNoch keine Bewertungen

- HiddenDokument2 SeitenHiddenBruno PaveiNoch keine Bewertungen

- Overview of TCAD Sentaurus SoftwareDokument6 SeitenOverview of TCAD Sentaurus Softwareshawan ChowdhuryNoch keine Bewertungen

- Support Device ListDokument60 SeitenSupport Device Listfox7878Noch keine Bewertungen

- Ross 2015 ProblemSet RevisedDokument8 SeitenRoss 2015 ProblemSet RevisedOdoggNoch keine Bewertungen

- CambalacheDokument21 SeitenCambalacheRODRINoch keine Bewertungen

- E-Recruitment: Avinash S. Kapse, Vishal S. Patil, Nikhil V. PatilDokument5 SeitenE-Recruitment: Avinash S. Kapse, Vishal S. Patil, Nikhil V. PatilRidish KumarNoch keine Bewertungen

- CV 2024030809232876Dokument2 SeitenCV 2024030809232876info4nirbhayNoch keine Bewertungen

- Perkins 2506-15Dokument144 SeitenPerkins 2506-15namvinh100% (2)

- 42 POWER8 Enterprise E870 From ExperienceDokument63 Seiten42 POWER8 Enterprise E870 From ExperienceAntonio A. Bonita100% (1)

- Instalación PLC Sr2a - B - 01a55Dokument2 SeitenInstalación PLC Sr2a - B - 01a55Jonathan Daniel Buendia FloresNoch keine Bewertungen

- Linux IntroductionDokument20 SeitenLinux IntroductionHave No IdeaNoch keine Bewertungen

- Consolidation Practice Top Notch 2 Units 789Dokument3 SeitenConsolidation Practice Top Notch 2 Units 789Carlos M BeltránNoch keine Bewertungen

- SING 18 19. Operators Manual For The Latest Functions ENGDokument32 SeitenSING 18 19. Operators Manual For The Latest Functions ENGremon nabilNoch keine Bewertungen

- LogDokument1.290 SeitenLogibnunabawi22Noch keine Bewertungen

- CV0-001 Examcollection Premium Exam 389qDokument70 SeitenCV0-001 Examcollection Premium Exam 389qRoman KlamkeNoch keine Bewertungen

- Lisp Programming LanguageDokument5 SeitenLisp Programming LanguageAnkit PathakNoch keine Bewertungen

- Static and Dynamic RAMDokument6 SeitenStatic and Dynamic RAMankitamaheshwariNoch keine Bewertungen

- Installation and User's Guide: IBM Spectrum Protect PlusDokument131 SeitenInstallation and User's Guide: IBM Spectrum Protect PlusanirudhaNoch keine Bewertungen

- Course Code Course Title L T P C 1152EC225 Wireless Adhoc and Sensor Networks 2 0 2 3Dokument4 SeitenCourse Code Course Title L T P C 1152EC225 Wireless Adhoc and Sensor Networks 2 0 2 3BALAKRISHNANNoch keine Bewertungen

- Tesla TV 50s635bus EngDokument2 SeitenTesla TV 50s635bus EngMirnesMujicNoch keine Bewertungen

- Zebradesigner Essentials Version 3 User Guide: Product Level: Essentials. Rev-2019-1 P1108968-EnDokument138 SeitenZebradesigner Essentials Version 3 User Guide: Product Level: Essentials. Rev-2019-1 P1108968-EngabrielolaveNoch keine Bewertungen

- Autumn: Ann LoganDokument8 SeitenAutumn: Ann LoganBlu Marie100% (2)

- VI Editor Cheat SheetDokument2 SeitenVI Editor Cheat SheetZoumana DiomandeNoch keine Bewertungen

- Ecosys FS-920Dokument126 SeitenEcosys FS-920Joel CaipiroNoch keine Bewertungen

- RELIABILITYrev2 Jan17 - Version 2Dokument18 SeitenRELIABILITYrev2 Jan17 - Version 2Ainan SyabilNoch keine Bewertungen

- Name: Vinayak Nagar Reg - No.: 21MCA0015 Subject: Database Technology Topic: Assignment-1Dokument77 SeitenName: Vinayak Nagar Reg - No.: 21MCA0015 Subject: Database Technology Topic: Assignment-1miu worldNoch keine Bewertungen

- Excel Assignment PDFDokument2 SeitenExcel Assignment PDFSomik JainNoch keine Bewertungen