Beruflich Dokumente

Kultur Dokumente

R7210504 Digital Logic Design

Hochgeladen von

sivabharathamurthyCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

R7210504 Digital Logic Design

Hochgeladen von

sivabharathamurthyCopyright:

Verfügbare Formate

R07

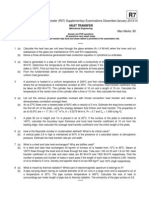

Code: R7210504 B.Tech II Year I Semester (R07) Supplementary Examinations December/January 2013/14 DIGITAL LOGIC DESIGN

(Common to CSE, IT & CSS)

Time: 3 hours Answer any FIVE questions All questions carry equal marks *****

1 (a) Solve for X: (i) (AE232)16 = (X)10 (ii) (5CA2)16 = (X)3 Differentiate hexadecimal codes and alpha numeric codes.

Max. Marks: 80

(b)

2 (a) (b)

Define canonical form, standard form, minterm, maxterm with an example. Derive Boolean expression for a 2 input Ex-OR gate realize with 2 input NAND gates without using complemented variables and draw the circuit.

3 (a) (b)

Explain how you convert sum of the products into product of sums. Give with example. Map the following function and simplify using K-Map: F = (A+B+C)(A+B+C)(A+B+C)(A+B+C)

Design a 2 bit comparator using gates. What is a decoder? Draw the circuit of 3-to-8 line decoder with the help of a truth table. Give different latches and Illustrate SR latch with example. Explain about HDL for sequential circuits. Write the HDL behavioral description of the 4- bit universal shift register. Draw the 4-bit binary ripple counter with D flip-flops. Explain PLA in detail. Design a random access memory having 8K bytes. Explain about the procedure for designing sequential circuits. Explain about the types of hazards in detail.

4 (a) (b) 5 (a) (b) 6 (a) (b) 7 (a) (b) 8 (a) (b)

*****

Das könnte Ihnen auch gefallen

- Complete PCB Design Using OrCAD Capture and PCB EditorVon EverandComplete PCB Design Using OrCAD Capture and PCB EditorBewertung: 5 von 5 Sternen5/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxVon EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxBewertung: 4 von 5 Sternen4/5 (2)

- R7220404 Switching Theory and Logic DesignDokument1 SeiteR7220404 Switching Theory and Logic DesignsivabharathamurthyNoch keine Bewertungen

- II B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic DesignDokument8 SeitenII B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic Design142545Noch keine Bewertungen

- 9A04401 Switching Theory and Logic DesignDokument4 Seiten9A04401 Switching Theory and Logic DesignsivabharathamurthyNoch keine Bewertungen

- R7210504 Digital Logic DesignDokument1 SeiteR7210504 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- Switching Theory and Logic DesignDokument8 SeitenSwitching Theory and Logic DesignVenkat ChadalavadaNoch keine Bewertungen

- R7310404 Digital IC ApplicationsDokument1 SeiteR7310404 Digital IC ApplicationssivabharathamurthyNoch keine Bewertungen

- FAQs - CS1202 Digital Principles and System DesignDokument13 SeitenFAQs - CS1202 Digital Principles and System DesignsridharanchandranNoch keine Bewertungen

- 21 - 2011 - Dec - R09 - STLDDokument8 Seiten21 - 2011 - Dec - R09 - STLDvasuvlsiNoch keine Bewertungen

- Code - No: 43216: Jawaharlal Nehru Technological University HyderabadDokument1 SeiteCode - No: 43216: Jawaharlal Nehru Technological University HyderabadKareem KhanNoch keine Bewertungen

- 9A04401 Switching Theory & Logic DesignDokument4 Seiten9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- 9A12301 Digital Logic Design and Computer OrganizationDokument4 Seiten9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- Digital Logic DesignDokument4 SeitenDigital Logic DesignShareef KhanNoch keine Bewertungen

- 9a04306-Digital Logic DesignDokument1 Seite9a04306-Digital Logic DesignSheikh Noor MohammadNoch keine Bewertungen

- Switching Theory and Logic DesignDokument6 SeitenSwitching Theory and Logic DesignVijay MNoch keine Bewertungen

- STLD 2009 RegularDokument4 SeitenSTLD 2009 RegularrangerNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- 9A04401 Switching Theory & Logic DesignDokument4 Seiten9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument2 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- ICT 9A04306 Digital Logic DesignDokument1 SeiteICT 9A04306 Digital Logic DesignMahaboob SubahanNoch keine Bewertungen

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDokument8 Seiten07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNoch keine Bewertungen

- 9A04401 Switching Theory & Logic DesignDokument1 Seite9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- AprMay 2012 (R10)Dokument38 SeitenAprMay 2012 (R10)Rajesh ViswanadhamNoch keine Bewertungen

- Digital Logic DesignDokument4 SeitenDigital Logic DesignrppvchNoch keine Bewertungen

- 21 - 2010 - Nov - R09 - STLDDokument8 Seiten21 - 2010 - Nov - R09 - STLDvasuvlsiNoch keine Bewertungen

- Switching Theory and Logic DesignDokument8 SeitenSwitching Theory and Logic DesignSubrahmanyam VjsNoch keine Bewertungen

- R5 210504 Digital Logic DesignDokument1 SeiteR5 210504 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- QBank DPSD cs2202Dokument6 SeitenQBank DPSD cs2202kunarajNoch keine Bewertungen

- 9A04306 Digital Logic Design3Dokument1 Seite9A04306 Digital Logic Design3Mahaboob SubahanNoch keine Bewertungen

- DPSDDokument16 SeitenDPSDDhilip PrabakaranNoch keine Bewertungen

- Midterm LDST 2012 BatchDokument2 SeitenMidterm LDST 2012 BatchyazdanieNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignMahaboob SubahanNoch keine Bewertungen

- Question Paper Code:: (10×2 20 Marks)Dokument2 SeitenQuestion Paper Code:: (10×2 20 Marks)kenny kannaNoch keine Bewertungen

- Switching Theory and Logic Design (CSE-203) (Makeup)Dokument2 SeitenSwitching Theory and Logic Design (CSE-203) (Makeup)Random ShitNoch keine Bewertungen

- Practice Problems - 1: Department of Electrical EngineeringDokument2 SeitenPractice Problems - 1: Department of Electrical EngineeringMalay Kumar MohantaNoch keine Bewertungen

- DIGITAL ELECTRONICS NovemberDecember-2020Dokument1 SeiteDIGITAL ELECTRONICS NovemberDecember-2020ethanNoch keine Bewertungen

- Digital Electronics Question BankDokument11 SeitenDigital Electronics Question BankS.Haribabu SNSNoch keine Bewertungen

- CS 2202 - Digital Principles and Systems Design PDFDokument3 SeitenCS 2202 - Digital Principles and Systems Design PDFvelkarthi92Noch keine Bewertungen

- BCA I I Digital SystemDokument4 SeitenBCA I I Digital SystemAmory Sabri AsmaroNoch keine Bewertungen

- Ia1 DPSDDokument2 SeitenIa1 DPSDRaja BenitaNoch keine Bewertungen

- 2019 Summer Question Paper (Msbte Study Resources)Dokument3 Seiten2019 Summer Question Paper (Msbte Study Resources)Ashutosh PatilNoch keine Bewertungen

- DPSD Nov 2011 - Reg 2008Dokument3 SeitenDPSD Nov 2011 - Reg 2008sububillaNoch keine Bewertungen

- Sample Question Paper Digital Techniques PDFDokument5 SeitenSample Question Paper Digital Techniques PDFAshutosh PatilNoch keine Bewertungen

- March-2022 (1) - 231101 - 193459Dokument1 SeiteMarch-2022 (1) - 231101 - 193459nanikarthikreddy2002Noch keine Bewertungen

- EC2203 Digital Electronics Question BankDokument16 SeitenEC2203 Digital Electronics Question BankSophiaKaviNoch keine Bewertungen

- Electronics-Fundamentals of Digital SystemDokument3 SeitenElectronics-Fundamentals of Digital Systemrohithlal2020Noch keine Bewertungen

- Jntuk 2 1 DLD Nov 2017 Q.PDokument5 SeitenJntuk 2 1 DLD Nov 2017 Q.PRoopa Krishna ChandraNoch keine Bewertungen

- Convert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0Dokument23 SeitenConvert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0khadarbasha.n nNoch keine Bewertungen

- De As1Dokument2 SeitenDe As1Dr-Tarun ParasharNoch keine Bewertungen

- 3 Hours / 70 Marks: Seat NoDokument23 Seiten3 Hours / 70 Marks: Seat NoHitesh BadgujarNoch keine Bewertungen

- 9A04306 Digital Logic Design2Dokument1 Seite9A04306 Digital Logic Design2Mahaboob SubahanNoch keine Bewertungen

- DPSD QBDokument11 SeitenDPSD QBHANISHA SAALIHNoch keine Bewertungen

- Digital Electronics QB 2015-RDokument8 SeitenDigital Electronics QB 2015-RKeerthe VaasanNoch keine Bewertungen

- Unit-1-2-3 Question Bank DEC 2131004Dokument2 SeitenUnit-1-2-3 Question Bank DEC 2131004Amit KumarNoch keine Bewertungen

- Logic Design June 2010 ESDokument2 SeitenLogic Design June 2010 ESPrasad C MNoch keine Bewertungen

- CS-64 Bachelor in Computer Applications Term-End Examination December, 2009 CS-64Dokument4 SeitenCS-64 Bachelor in Computer Applications Term-End Examination December, 2009 CS-64Prince AroraNoch keine Bewertungen

- Control Systems (CS) Notes As Per JntuaDokument203 SeitenControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- R7410506 Mobile ComputingDokument1 SeiteR7410506 Mobile ComputingsivabharathamurthyNoch keine Bewertungen

- 07A4EC01 Environmental StudiesDokument1 Seite07A4EC01 Environmental StudiessivabharathamurthyNoch keine Bewertungen

- SSC Telugu (FL) (AP)Dokument232 SeitenSSC Telugu (FL) (AP)sivabharathamurthyNoch keine Bewertungen

- SSC Social Textbook (AP)Dokument100 SeitenSSC Social Textbook (AP)sivabharathamurthyNoch keine Bewertungen

- R7410407 Operating SystemsDokument1 SeiteR7410407 Operating SystemssivabharathamurthyNoch keine Bewertungen

- R5410201 Neural Networks & Fuzzy LogicDokument1 SeiteR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyNoch keine Bewertungen

- R7311205 Distributed DatabasesDokument1 SeiteR7311205 Distributed DatabasessivabharathamurthyNoch keine Bewertungen

- 9A05707 Software Project ManagementDokument4 Seiten9A05707 Software Project ManagementsivabharathamurthyNoch keine Bewertungen

- 9A13701 Robotics and AutomationDokument4 Seiten9A13701 Robotics and AutomationsivabharathamurthyNoch keine Bewertungen

- R7311506 Operating SystemsDokument1 SeiteR7311506 Operating SystemssivabharathamurthyNoch keine Bewertungen

- Code: R7311306: (Electronics & Control Engineering)Dokument1 SeiteCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyNoch keine Bewertungen

- R7312301 Transport Phenomena in BioprocessesDokument1 SeiteR7312301 Transport Phenomena in BioprocessessivabharathamurthyNoch keine Bewertungen

- R7311006 Process Control InstrumentationDokument1 SeiteR7311006 Process Control InstrumentationsivabharathamurthyNoch keine Bewertungen

- R7310506 Design & Analysis of AlgorithmsDokument1 SeiteR7310506 Design & Analysis of AlgorithmssivabharathamurthyNoch keine Bewertungen

- 9A23501 Heat Transfer in BioprocessesDokument4 Seiten9A23501 Heat Transfer in BioprocessessivabharathamurthyNoch keine Bewertungen

- R7310306 Heat TransferDokument1 SeiteR7310306 Heat Transfersivabharathamurthy100% (1)

- R5310406 Digital CommunicationsDokument1 SeiteR5310406 Digital CommunicationssivabharathamurthyNoch keine Bewertungen

- R7310406 Digital CommunicationsDokument1 SeiteR7310406 Digital CommunicationssivabharathamurthyNoch keine Bewertungen

- R7310106 Engineering GeologyDokument1 SeiteR7310106 Engineering GeologysivabharathamurthyNoch keine Bewertungen

- R7310206 Linear Systems AnalysisDokument1 SeiteR7310206 Linear Systems AnalysissivabharathamurthyNoch keine Bewertungen

- R5310204 Power ElectronicsDokument1 SeiteR5310204 Power ElectronicssivabharathamurthyNoch keine Bewertungen

- 9A10505 Principles of CommunicationsDokument4 Seiten9A10505 Principles of CommunicationssivabharathamurthyNoch keine Bewertungen

- 9A21506 Mechanisms & Mechanical DesignDokument8 Seiten9A21506 Mechanisms & Mechanical DesignsivabharathamurthyNoch keine Bewertungen

- 9A15502 Digital System DesignDokument4 Seiten9A15502 Digital System Designsivabharathamurthy100% (1)

- 9A14503 Principles of Machine DesignDokument8 Seiten9A14503 Principles of Machine DesignsivabharathamurthyNoch keine Bewertungen

- 9A03505 Heat TransferDokument4 Seiten9A03505 Heat TransfersivabharathamurthyNoch keine Bewertungen

- 9A04504 Digital IC ApplicationsDokument4 Seiten9A04504 Digital IC ApplicationssivabharathamurthyNoch keine Bewertungen

- 9A05505 Operating SystemsDokument4 Seiten9A05505 Operating SystemssivabharathamurthyNoch keine Bewertungen

- 9A02505 Electrical Machines-IIIDokument4 Seiten9A02505 Electrical Machines-IIIsivabharathamurthyNoch keine Bewertungen