Beruflich Dokumente

Kultur Dokumente

Adv Cmos Part1-2

Hochgeladen von

Luis PiresOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Adv Cmos Part1-2

Hochgeladen von

Luis PiresCopyright:

Verfügbare Formate

Advanced CMOS Process Technology

MICROELECTRONIC ENGINEERING ROCHESTER INSTITUTE OF TECHNOLOGY

Advanced CMOS Process Technology Part 1 and 2 Dr. Lynn Fuller

Webpage: http://people.rit.edu/lffeee Microelectronic Engineering Rochester Institute of Technology 82 Lomb Memorial Drive Rochester, NY 14623-5604 Tel (585) 475-2035 Fax (585) 475-5041 Email: Lynn.Fuller@rit.edu Department webpage: http://www.microe.rit.edu

Rochester Institute of Technology Microelectronic Engineering

4-19 -2010 ADV_CMOS_Part1-2.ppt

Page 1

April 19, 2010 Dr. Lynn Fuller

Advanced CMOS Process Technology

OUTLINE Devices for 0.15 m CMOS High Performance Sub 0.1 m Channel nMOSFETs Sub - 1/4 m Dual-Gate CMOS Technology High-Performance 0.07 - m CMOS Enhanced Strain Effects in 25-nm Gate-Length Thin-Body nMOSFET

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 2

Advanced CMOS Process Technology

1995

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 3

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 4

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 5

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 6

Advanced CMOS Process Technology

In Preamorphization As Implant 50nm deep

Sb Preamorphization BF2 Implant 60nm deep

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 7

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 8

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 9

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 10

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 11

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 12

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 13

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 14

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 15

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 16

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 17

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

Silicon on Insulator

April 19, 2010 Dr. Lynn Fuller

Page 18

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 19

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 20

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 21

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 22

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 23

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 24

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 25

Advanced CMOS Process Technology

~75 mV/dec nMOS ~80 mV/dec pMOS

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 26

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 27

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 28

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 29

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 30

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 31

Advanced CMOS Process Technology

0.08 m MOSFETS

The T shaped gate structure helps reduce resistance of the gate connection

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 32

Advanced CMOS Process Technology

Rochester Institute of Technology Microelectronic Engineering

December 8, 1998

Page 33

April 19, 2010 Dr. Lynn Fuller

Advanced CMOS Process Technology

(Continued)

Rochester Institute of Technology Microelectronic Engineering April 19, 2010 Dr. Lynn Fuller

Page 34

Advanced CMOS Process Technology

0.06 m MOSFETS

Rochester Institute of Technology Microelectronic Engineering

IEDM 1999

Page 35

April 19, 2010 Dr. Lynn Fuller

Advanced CMOS Process Technology

0.05 m MOSFET Dopant Profile

IEEE Spectrum July 1999

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 36

Advanced CMOS Process Technology

ATOMIC SCALE TRANSISTORS

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 37

Advanced CMOS Process Technology

0.03 m Leff MOSFETS IMEC Meeting December 1999

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 38

Advanced CMOS Process Technology

0.03 m MOSFETS

Xox 4.0 nm gate oxide

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 39

Advanced CMOS Process Technology

0.03 m MOSFETS

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 40

Advanced CMOS Process Technology

0.025m

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 41

Advanced CMOS Process Technology

0.025m

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 42

Advanced CMOS Process Technology

0.025m

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 43

Advanced CMOS Process Technology

0.02 m MOSFET

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 44

Advanced CMOS Process Technology

0.02 m MOSFET

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 45

Advanced CMOS Process Technology

0.02 m MOSFET

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 46

Advanced CMOS Process Technology

0.006 m MOSFET

Channel is 4 nm thick on Buried Oxide. 8-19-2002

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 47

Advanced CMOS Process Technology

MULTILAYER METAL, W PLUGS, CMP

8 Layers Metal

Rochester Institute of Technology Microelectronic Engineering April 19, 2010 Dr. Lynn Fuller

Page 48

Advanced CMOS Process Technology

REFERENCES 1. IEEE Electron Device Letters 2. Electronics News 3. Silicon Processing for the VLSI Era Vol 2. - Process Integration. 4. The Science and Engineering of Microelectronic Fabrication, Stephen A. Campbell. 5. May 1999, IEEE Electron Device Letters, Fabrication and Characterization of Sub 0.25 m Copper Gate MOSFET with copper gate, page 254 6. July 1999 IEEE Transactions on Electron Devices, An 0.18 um CMOS for Mixed Digital and Analog Applications with Zero-Volt-Vth Epitaxial Channel MOSFETs, page 1378. 7. IEEE Journal of Solid-State Circuits, CMOS Technology - Year 2010 and Beyond, H. Iwai, Pg 357. 8. Solid State Technology, July 1999, Cobalt Silicide Processing in a Susceptor Based LP-RTP System, pg 125.

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 49

Advanced CMOS Process Technology

REFERENCES 9. Solid State Technology's WaferNEWS - www.wafernews.com 10. EE Times Newsletter [from_EETimes@newsletter.eetimes.com] 11. Internationa Technology Roadmap for Semiconductors (ITRS) http://www.itrs.net

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 50

Advanced CMOS Process Technology

HOMEWORK- ADVANCED CMOS PART 1&2 1. Briefly describe the following CMOS process enhancements, a) silicide, b) salicide, c) dual doped gate CMOS, d) side wall spacers, e) gate stack formation, f) multi layer metal. 2. What types of lithography technology was used to make the < 0.2 m transistors described in this set of notes? 3. What types of isolation technology was used to make the CMOS devices described in this set of notes? 4. What technology is used to reduce Boron penetration through the gate oxide for the devices described in this set of notes? 5. Sketch the crossection of the 0.07 m CMOS described in this set of notes. Make the sketch to scale in both the lateral direction and the direction into the wafer.

Rochester Institute of Technology Microelectronic Engineering

April 19, 2010 Dr. Lynn Fuller

Page 51

Das könnte Ihnen auch gefallen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

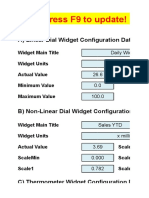

- Excel Dashboard WidgetsDokument47 SeitenExcel Dashboard WidgetskhincowNoch keine Bewertungen

- Admin Interview Questions and Answers - Robert HalfDokument2 SeitenAdmin Interview Questions and Answers - Robert HalfWaqqas AhmadNoch keine Bewertungen

- Testing concrete and brick strengthDokument2 SeitenTesting concrete and brick strengthlolenlennNoch keine Bewertungen

- Fire Pump ChecklistDokument11 SeitenFire Pump ChecklistLD Jr FrancisNoch keine Bewertungen

- Digital Logic and Microprocessor Design With Interfacing 2nd Edition Hwang Solutions ManualDokument27 SeitenDigital Logic and Microprocessor Design With Interfacing 2nd Edition Hwang Solutions Manualdacdonaldnxv1zq100% (27)

- Grade 6 Science PuzzleDokument4 SeitenGrade 6 Science Puzzlemargie riveraNoch keine Bewertungen

- MPTK Medium Pressure Pump Performance SpecsDokument2 SeitenMPTK Medium Pressure Pump Performance SpecssaronandyNoch keine Bewertungen

- POSSIBILITIES OF LOW VOLTAGE DC SYSTEMSDokument10 SeitenPOSSIBILITIES OF LOW VOLTAGE DC SYSTEMSTTaanNoch keine Bewertungen

- College Report of Optical Burst SwitchingDokument21 SeitenCollege Report of Optical Burst Switchingimcoolsha999Noch keine Bewertungen

- The Future of Smart Cities and RegionsDokument20 SeitenThe Future of Smart Cities and RegionsChristianNoch keine Bewertungen

- 1HD-T - 1 Land Cruiser Engine Service ManualDokument26 Seiten1HD-T - 1 Land Cruiser Engine Service ManualMichael Dzidowski86% (7)

- MyPower S3220&S3320-INSTALLATIONDokument83 SeitenMyPower S3220&S3320-INSTALLATIONJorge GonzalesNoch keine Bewertungen

- 7.qad-Dpr-11 ImteDokument4 Seiten7.qad-Dpr-11 ImteDhinakaranNoch keine Bewertungen

- HoltacDokument8 SeitenHoltacdargil66Noch keine Bewertungen

- D72140GC10 46777 UsDokument3 SeitenD72140GC10 46777 UsWilliam LeeNoch keine Bewertungen

- Damage To Stern Tube Bearing and SealsDokument4 SeitenDamage To Stern Tube Bearing and SealsJoão Henrique Volpini MattosNoch keine Bewertungen

- Panasonic WJ FS616Dokument62 SeitenPanasonic WJ FS616triliteNoch keine Bewertungen

- Protection Systems TransformerDokument14 SeitenProtection Systems Transformerrajabharath12Noch keine Bewertungen

- Indus Water Treaty & Emerging Water IssuesDokument24 SeitenIndus Water Treaty & Emerging Water Issuesu1umarNoch keine Bewertungen

- Strategic Information Systems Planning: Course OverviewDokument18 SeitenStrategic Information Systems Planning: Course OverviewEmmy W. RosyidiNoch keine Bewertungen

- G12gasa Group5 PR2Dokument7 SeitenG12gasa Group5 PR2Lizley CordovaNoch keine Bewertungen

- Engineering Data, Summary of Productivity 2022Dokument2 SeitenEngineering Data, Summary of Productivity 2022Listya AnggrainiNoch keine Bewertungen

- Astral Column Pipe PricelistDokument4 SeitenAstral Column Pipe PricelistVaishamNoch keine Bewertungen

- Unit4questions 100415042439 Phpapp01Dokument4 SeitenUnit4questions 100415042439 Phpapp01Mohamad HishamNoch keine Bewertungen

- Gpa 2145Dokument15 SeitenGpa 2145Sergio David Ruiz100% (1)

- Process Sizing CriteriaDokument91 SeitenProcess Sizing CriteriaMohammad BadakhshanNoch keine Bewertungen

- Designing The Marketing Channels 13Dokument13 SeitenDesigning The Marketing Channels 13Gajender SinghNoch keine Bewertungen

- Conveyor Chain GuideDokument59 SeitenConveyor Chain GuideajaykrishnaaNoch keine Bewertungen

- 38.11 Cum Total Qty of 4 Nos. Culvests 38.11x4 152.43 CumDokument14 Seiten38.11 Cum Total Qty of 4 Nos. Culvests 38.11x4 152.43 CumMandeep SinghNoch keine Bewertungen

- Timeline of Programming Languages PDFDokument11 SeitenTimeline of Programming Languages PDFMohd Khir ZainunNoch keine Bewertungen