Beruflich Dokumente

Kultur Dokumente

Carparking Verilog Code

Hochgeladen von

Thota Indra MohanOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Carparking Verilog Code

Hochgeladen von

Thota Indra MohanCopyright:

Verfügbare Formate

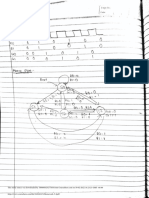

module Carpark (y_out,x_in, clock, reset); output y_out; input x_in,clock,reset; reg y_out; reg [1:0]state,next_state; parameter S0 !

"#00, S1 !"#01, S! !"#10, S$ !"#11;

al%ays & ( posedge clock, negedge reset) i' (reset 0) state ( S0;

else state ( next_state; al%ays & (state, x_in) case (state) S0: i' (x_in) next_state S1: i' (x_in) next_state S!: i' ()x_in) next_state S$: i' (x_in) next_state endcase al%ays & (state, x_in) case (state) S0: y_out 0; )x_in; S1; else next_state S$; else next_state S0; else next_state S!; else next_state S0; S0; S!; S0;

S1, S!, S$: y_out endcase endmodule **+est ,enc-

module +est_.;

** /nputs reg x_in;

reg clock; reg reset;

** 0utputs %ire y_out;

** /nstantiate t-e 1nit 1nder +est (11+) Carpark uut ( 2y_out(y_out), 2x_in(x_in), 2clock(clock), 2reset(reset) ); initial #egin clock 0; )clock;

'ore.er 34 clock end initial #egin x_in clock reset 3100; 0; 0; 0;

end initial 'ork reset 0; 1;

3! reset

356 reset 357 reset 310 x_in 3$0 x_in 380 x_in 340 x_in 34! x_in 348 x_in 360 x_in 350 x_in 360 x_in 370 x_in 3100 x_in 31!0 x_in 3190 x_in 3160 x_in :oin

0; 1; 1; 0; 1; 0; 1; 0; 1; 1; 0; 1; 0; 1; 0; 1;

endmodule

Das könnte Ihnen auch gefallen

- DSD Lab3 Fa20-Bce-029 PDFDokument5 SeitenDSD Lab3 Fa20-Bce-029 PDFabdullahNoch keine Bewertungen

- FSMDokument12 SeitenFSMRohit PanwarNoch keine Bewertungen

- A Finite State MachineDokument2 SeitenA Finite State Machinesantosh861986Noch keine Bewertungen

- FSM Design Verilog HDL PDFDokument7 SeitenFSM Design Verilog HDL PDFajayNoch keine Bewertungen

- Finite State MachineDokument14 SeitenFinite State MachineDeven MaliNoch keine Bewertungen

- VHDL ProjectDokument4 SeitenVHDL ProjectJayp MistryNoch keine Bewertungen

- New Text DocumentDokument8 SeitenNew Text DocumentMuneeb AhmadNoch keine Bewertungen

- Exp 11Dokument9 SeitenExp 11Nithi BNoch keine Bewertungen

- PDF Primary-Whatsapp-Media-Whatsapp-Documents-VlsilabquestDokument17 SeitenPDF Primary-Whatsapp-Media-Whatsapp-Documents-VlsilabquestSanju SraNoch keine Bewertungen

- Homework 5: Pro Reset CLK N OutyDokument6 SeitenHomework 5: Pro Reset CLK N OutyBan BanNoch keine Bewertungen

- Verilog Code - State MachinesDokument3 SeitenVerilog Code - State MachinesvasuvlsiNoch keine Bewertungen

- Practice Problems 4Dokument5 SeitenPractice Problems 4PBNoch keine Bewertungen

- Verilog Expt 3Dokument5 SeitenVerilog Expt 3Labiba ZahinNoch keine Bewertungen

- Homework 5 2 PDFDokument6 SeitenHomework 5 2 PDFAkshay BhardwajNoch keine Bewertungen

- 14 SequentialCircuitDesignDokument39 Seiten14 SequentialCircuitDesignSaurav GuptaNoch keine Bewertungen

- Code TempDokument11 SeitenCode TempHoàng Long Nguyễn BùiNoch keine Bewertungen

- 2) Verify The Behavior of Logic Gates Using Truth Tables (AND, OR, NOT, XOR, NAND, NOR, XNOR)Dokument9 Seiten2) Verify The Behavior of Logic Gates Using Truth Tables (AND, OR, NOT, XOR, NAND, NOR, XNOR)SyamPvpsitNoch keine Bewertungen

- Chapter #9: Finite State Machine OptimizationDokument51 SeitenChapter #9: Finite State Machine Optimizationఅనిల్ కుమార్ రాజగిరిNoch keine Bewertungen

- Impletar en VHDL La Siguiente Maquina de EstadosDokument10 SeitenImpletar en VHDL La Siguiente Maquina de EstadosGian SusanaNoch keine Bewertungen

- Chess Panel ProjectDokument31 SeitenChess Panel ProjectMahmoud El-tabeyNoch keine Bewertungen

- Lecture 4: Continuation of SystemverilogDokument17 SeitenLecture 4: Continuation of SystemverilogSivasubramanian ManickamNoch keine Bewertungen

- Moore Machine VHDL CodeDokument2 SeitenMoore Machine VHDL CodeKewl84Noch keine Bewertungen

- Unsigned Divider RTL ModelDokument10 SeitenUnsigned Divider RTL ModelgadhaNoch keine Bewertungen

- 07 FSM - VHDLDokument8 Seiten07 FSM - VHDLayahNoch keine Bewertungen

- Barrel ShifterDokument6 SeitenBarrel ShifterRomy SharmaNoch keine Bewertungen

- B.1 FSM (Finite State Machine) Sortir BendaDokument11 SeitenB.1 FSM (Finite State Machine) Sortir BendaMuhammad FaizNoch keine Bewertungen

- Exp4 VlsiDokument6 SeitenExp4 VlsiShyam SundarNoch keine Bewertungen

- Ejemplos VHDLDokument5 SeitenEjemplos VHDLLeón Emmanuel NNoch keine Bewertungen

- BT3 TuvietDokument2 SeitenBT3 TuvietChúc Văn KiênNoch keine Bewertungen

- Practical Exam - RonquilloDominicDokument9 SeitenPractical Exam - RonquilloDominicCYCLONE 1020Noch keine Bewertungen

- Chung FSM DesignDokument28 SeitenChung FSM DesignRiyasNoch keine Bewertungen

- 수정 전 코드Dokument2 Seiten수정 전 코드붕붕부릉부릉Noch keine Bewertungen

- Analysis of The Original System:: S G S S S S H S VDokument7 SeitenAnalysis of The Original System:: S G S S S S H S VFongyin HoNoch keine Bewertungen

- Electiva - CIRCUITOS SECUENCIALES EN VHDLDokument5 SeitenElectiva - CIRCUITOS SECUENCIALES EN VHDLfer gutiNoch keine Bewertungen

- Structure of A Typical Digital SystemDokument29 SeitenStructure of A Typical Digital SystemQasimNoch keine Bewertungen

- HHGFHGDokument3 SeitenHHGFHGSouhel TenbakjyNoch keine Bewertungen

- دورة تدريبية من سيمنز - الجزء الثانىDokument53 Seitenدورة تدريبية من سيمنز - الجزء الثانىHamid BouleghabNoch keine Bewertungen

- Exam1 (Example With Solutions)Dokument5 SeitenExam1 (Example With Solutions)Rüya Gïbî100% (1)

- Verilog Code For AluDokument7 SeitenVerilog Code For Aludivya gogineniNoch keine Bewertungen

- Verilog Code For AluDokument7 SeitenVerilog Code For Aludivya gogineniNoch keine Bewertungen

- Verilog Code For AluDokument7 SeitenVerilog Code For Alumeaow88100% (3)

- Sequence DetectorDokument9 SeitenSequence DetectorBHAVYANoch keine Bewertungen

- Experiment 8Dokument6 SeitenExperiment 8routbismay99Noch keine Bewertungen

- MAQUINA DE ESTADOS1 (Autoguardado)Dokument19 SeitenMAQUINA DE ESTADOS1 (Autoguardado)YealsatoNoch keine Bewertungen

- Alu ArithmeticDokument7 SeitenAlu ArithmeticTech-savvy GirishaNoch keine Bewertungen

- Lab 08: SR Flip Flop FundamentalsDokument6 SeitenLab 08: SR Flip Flop Fundamentalsjitu123456789Noch keine Bewertungen

- Digital System Design Example 1: GCD Calculator: Start Signal, Which Commences The Computation ProcessDokument31 SeitenDigital System Design Example 1: GCD Calculator: Start Signal, Which Commences The Computation ProcessEMJAYNoch keine Bewertungen

- TASK-5: Name: Nithin Raja Ss REG NO:19BML0009Dokument7 SeitenTASK-5: Name: Nithin Raja Ss REG NO:19BML0009Cathrine CruzNoch keine Bewertungen

- AGV Project Codes CompilationDokument15 SeitenAGV Project Codes CompilationJhasper ManagyoNoch keine Bewertungen

- Experiment 10:: AIM: WAP To Implement Shift Reduce ParserDokument5 SeitenExperiment 10:: AIM: WAP To Implement Shift Reduce Parserakshat sharmaNoch keine Bewertungen

- Ejemplo Ejercicios Arquitectura de ComputadoresDokument7 SeitenEjemplo Ejercicios Arquitectura de ComputadoresMericoNoch keine Bewertungen

- Divide by 3 FSMDokument14 SeitenDivide by 3 FSMGirish ChukkaNoch keine Bewertungen

- Piranti Terprogram - FSMDokument8 SeitenPiranti Terprogram - FSMnamirarizqi annisaNoch keine Bewertungen

- Hancel Pin Ver FullDokument4 SeitenHancel Pin Ver FullToàn ĐỗNoch keine Bewertungen

- Chuong Trinh Den Giao ThongDokument2 SeitenChuong Trinh Den Giao ThongHồng PhượngNoch keine Bewertungen

- Fundamentals of Logic Design 6th Edition Chapters 14-15Dokument32 SeitenFundamentals of Logic Design 6th Edition Chapters 14-15Huy HoangNoch keine Bewertungen

- DEMUXDokument9 SeitenDEMUXPooja DhakaneNoch keine Bewertungen

- Mac ProtocolDokument38 SeitenMac ProtocolThota Indra MohanNoch keine Bewertungen

- Memory Management: AbstractDokument20 SeitenMemory Management: AbstractThota Indra MohanNoch keine Bewertungen

- 20Dokument9 Seiten20Thota Indra MohanNoch keine Bewertungen

- 1 s2.0 S1389128614002874 MainDokument12 Seiten1 s2.0 S1389128614002874 MainThota Indra MohanNoch keine Bewertungen

- 1Dokument9 Seiten1Sai KrishnaNoch keine Bewertungen

- Input-Output Operations.: J.Tiberghien - Computer Systems - Printed: 29/09/2014Dokument10 SeitenInput-Output Operations.: J.Tiberghien - Computer Systems - Printed: 29/09/2014Thota Indra MohanNoch keine Bewertungen

- 5Dokument4 Seiten5Rahul RajNoch keine Bewertungen

- EnglishDokument4 SeitenEnglishMondeep PaulNoch keine Bewertungen

- Amplitude Shift Keying: Experiment - 7Dokument2 SeitenAmplitude Shift Keying: Experiment - 7Thota Indra MohanNoch keine Bewertungen

- B INDEXDokument1 SeiteB INDEXThota Indra MohanNoch keine Bewertungen

- DSP Third Fourth UnitDokument44 SeitenDSP Third Fourth UnitThota Indra MohanNoch keine Bewertungen

- E&t Paper IiDokument20 SeitenE&t Paper IiPriyanka KatariaNoch keine Bewertungen

- ADC and DACDokument16 SeitenADC and DACThota Indra MohanNoch keine Bewertungen

- ADC and DACDokument16 SeitenADC and DACThota Indra MohanNoch keine Bewertungen

- 1 - AMCAT Guidelines and ModulesDokument1 Seite1 - AMCAT Guidelines and ModulesThota Indra MohanNoch keine Bewertungen

- Phpapp01Dokument44 SeitenPhpapp01Tushar DudhadeNoch keine Bewertungen

- (WWW - Entrance-Exam - Net) - IES E&T PAPER IDokument28 Seiten(WWW - Entrance-Exam - Net) - IES E&T PAPER IkrsekarNoch keine Bewertungen

- Poc Complete NotesDokument307 SeitenPoc Complete NotesThota Indra MohanNoch keine Bewertungen

- Concept: Central Vendor Data Migration ApproachDokument4 SeitenConcept: Central Vendor Data Migration Approachnileshgupta11112756Noch keine Bewertungen

- MCS 206 DalalTechnologies AftnucDokument29 SeitenMCS 206 DalalTechnologies AftnucRajnish KaurNoch keine Bewertungen

- Quiz App Javascript Report Css Mini Project-1Dokument32 SeitenQuiz App Javascript Report Css Mini Project-1Kamini SalunkheNoch keine Bewertungen

- Sample Question Paper Computer Science (Code: 083)Dokument7 SeitenSample Question Paper Computer Science (Code: 083)Mutual Fund JunctionNoch keine Bewertungen

- Course Outline CSC 588 Data Warehousing and Data Mining1Dokument5 SeitenCourse Outline CSC 588 Data Warehousing and Data Mining1Madawi AlOtaibiNoch keine Bewertungen

- Universityof Hertfordshire School of Physics, Engineering and Computer ScienceDokument4 SeitenUniversityof Hertfordshire School of Physics, Engineering and Computer ScienceMuhammad AsadNoch keine Bewertungen

- First Analysis of Site After SWAPDokument23 SeitenFirst Analysis of Site After SWAPRaviNoch keine Bewertungen

- BD-JB: Blu-Ray Disc Java Sandbox Escape: by Andy NguyenDokument51 SeitenBD-JB: Blu-Ray Disc Java Sandbox Escape: by Andy NguyenJean HarveyNoch keine Bewertungen

- Opencv2refman PDFDokument899 SeitenOpencv2refman PDFrosasilbusNoch keine Bewertungen

- Example Script StellariumDokument2 SeitenExample Script Stellariumsudhakarcscbe5179Noch keine Bewertungen

- Get Backlinks For Free - Easy Backlink Builder GuideDokument4 SeitenGet Backlinks For Free - Easy Backlink Builder GuidejurarajanNoch keine Bewertungen

- RTA-TRACE Getting Started GuideDokument27 SeitenRTA-TRACE Getting Started GuideRafael StriederNoch keine Bewertungen

- Teh Chin ChainDokument14 SeitenTeh Chin ChainNoelia RevolloNoch keine Bewertungen

- Java Lab ManualDokument104 SeitenJava Lab Manualrajangam04Noch keine Bewertungen

- How To Install Solr StandaloneDokument7 SeitenHow To Install Solr Standaloneheddoun00Noch keine Bewertungen

- SQLDokument26 SeitenSQLSonal JadhavNoch keine Bewertungen

- x86 DisassemblyDokument81 Seitenx86 DisassemblyTommy KrinkleNoch keine Bewertungen

- JAVA Networking Classes and InterfacesDokument5 SeitenJAVA Networking Classes and InterfacesArchana R gopinathNoch keine Bewertungen

- Bentley Structural Enterprise Work SuiteDokument2 SeitenBentley Structural Enterprise Work SuiteKim Kenneth AsiaNoch keine Bewertungen

- How To Disable Visual Studio Debugger - Stack OverflowDokument4 SeitenHow To Disable Visual Studio Debugger - Stack Overflowguruh anindraNoch keine Bewertungen

- Kibes - : Multiplex System For Buses and Special VehiclesDokument7 SeitenKibes - : Multiplex System For Buses and Special Vehiclesruman214Noch keine Bewertungen

- MN 123b 6100 099 VPad 623 Operators ManualDokument118 SeitenMN 123b 6100 099 VPad 623 Operators ManualAbdalazeez AlsayedNoch keine Bewertungen

- EpicorICETools UserGuide 100700 PDFDokument813 SeitenEpicorICETools UserGuide 100700 PDFare_nita02100% (1)

- Installation InstructionsDokument3 SeitenInstallation InstructionsThiago100% (1)

- ARTEMIS 0.5.1 Walkthrough Rev 1.3.1Dokument35 SeitenARTEMIS 0.5.1 Walkthrough Rev 1.3.1myst05010% (1)

- Current LogDokument48 SeitenCurrent LogPatrícia Arrózio PedrosoNoch keine Bewertungen

- Secure Coding Guidelines For Java SEDokument24 SeitenSecure Coding Guidelines For Java SEMilinda PradeepNoch keine Bewertungen

- Mozilla ThunderbirdDokument5 SeitenMozilla ThunderbirdYamen NasrNoch keine Bewertungen

- IMS DLI Essentials 1.0Dokument147 SeitenIMS DLI Essentials 1.0Jose Ricardo Andrade CortesNoch keine Bewertungen

- Hit 7300 TSMNDokument159 SeitenHit 7300 TSMNMohammed Kumayl100% (1)