Beruflich Dokumente

Kultur Dokumente

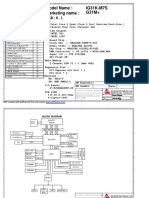

Mainboard p4845glm

Hochgeladen von

Ho Thanh BinhOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Mainboard p4845glm

Hochgeladen von

Ho Thanh BinhCopyright:

Verfügbare Formate

CH845G

REV:2.0

Title Page

Cover Sheet 1

Block Diagram 2

Socket 478 3,4

DECOUPLING 5

Clock Synthesizer 6 HH1 HH2 HH3

GMCH 7,8,9 1 1 1

DDR DIMMS & TERMINATION 10,11,12 NPTH157 NPTH157 NPTH157

AGP CONNECTOR 13

FH4 FH2 FH5 FH1 FH3

ICH4 14 ,15 ,16 1 1 1 1 1

FWH 17 FIDUCIAL FIDUCIAL FIDUCIAL FIDUCIAL FIDUCIAL

LPC 18

PCI Connectors 19 ,20

IDE Connectors 21

M1 M2 M3

USB Connectors 22 6 5 6 5 6 5

7 4 7 4 7 4

8 3 8 3 8 3

Parallel Port 23 9 2 9 2 9 2

MTHOLE MTHOLE MTHOLE

Serial Ports 24

KEYBOARD/MOUSE 25

M62 M63 M70

6 5 6 5 6 5

CNR 26 7 4 7 4 7 4

8 3 8 3 8 3

9 2 9 2 9 2

GAME PORT 27

MTHOLE MTHOLE MTHOLE

VGA CONNECTOR 28

AC97 CODEC 29

AUDIO CONNECTORS 30

PWM 31

REGULATORS 32

SYSTEM & POWER CONNECTORS 33

DDR POWER REGULATORS 34

Size Document Number Rev

A3 COVER SHEET 01

Date: Monday, August 19, 2002 Sheet 1 of 34

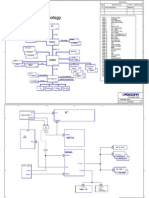

Block Diagram

VRM9.0 Intel Pentium 4 processor / Northwood

478-Pin Socket

400/533MHz

System Bus

1.6GB/S \

AGP4X MCH 2.1GB/S 2 DIMM

or 1.06GB/S Brookdale G Modules

2 Muxed DDR200/266

760 / 788

DVO Port FC-BGA

266MB/s

Hub interface 1.5

IDE Primary

ATA66/100 PCI CNTRL

PCI CONN 1

PCI CONN 2

PCI CONN 3

IDE Secondary

ICH4 PCI ADDR/DATA

Hi-Speed 421 mBGA

USB USB

6 Ports

480Mb/s

LPC Bus

AC97 AC'97 Link

3 Codec

support LAN SIO

LAN Flash

interface Bios

Keyboard Floppy Serial 1 Parallel Game Port

Mouse

Size Document Number Rev

A3 BLOCK DIAGRAM 01

Date: Monday, August 19, 2002 Sheet 2 of 34

VCORE

AC10

AC12

AC14

AC16

AC18

AD11

AD13

AD15

AD17

AD19

AA10

AA12

AA14

AA16

AA18

AB11

AB13

AB15

AB17

AB19

AE10

AE12

AE14

AE16

AE18

AE20

AF11

AF13

AF15

AF17

AF19

AF21

AC8

AD7

AD9

AA8

AB7

AB9

AE6

AE8

AF2

AF5

AF7

AF9

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

A10

A12

A14

A16

A18

A20

B11

B13

B15

B17

B19

E10

E12

E14

E16

E18

E20

K26

K25

F11

F13

F15

F17

F19

L25

J26

C8

D7

D9

A8

B7

B9

E8

U10A

F9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

DEP3

DEP2

DEP1

DEP0

A35 AB1

H_D0 B21 Y1

H_D1 D0 A34

B22 D1 A33 W2

H_D2 A23 V3

H_D3 D2 A32 H_A31

A25 D3 A31 U4

H_D4 C21 T5 H_A30

H_D5 D4 A30 H_A29

D22 D5 A29 W1

H_D6 B24 R6 H_A28

H_D7 D6 A28 H_A27

C23 D7 A27 V2

H_D8 C24 T4 H_A26

H_D9 D8 A26 H_A25

B25 D9 A25 U3

H_D10 G22 P6 H_A24

H_D11 D10 A24 H_A23

H21 D11 A23 U1

H_D12 C26 T2 H_A22

H_D13 D12 A22 H_A21

D23 D13 A21 R3

H_D14 J21 P4 H_A20

H_D15 D14 A20 H_A19

D25 D15 A19 P3

H_D16 H22 R2 H_A18

H_D17 D16 A18 H_A17

E24 D17 A17 T1

H_D18 G23 N5 H_A16

H_D19 D18 A16 H_A15

F23 D19 A15 N4

H_D20 F24 N2 H_A14

H_D21 D20 A14 H_A13

E25 D21 A13 M1

H_D22 F26 N1 H_A12

H_D23 D22 A12 H_A11

D26 D23 A11 M4

H_D24 L21 M3 H_A10

H_D25 D24 A10 H_A9

G26 D25 A9 L2

H_D26 H24 M6 H_A8

H_D27 D26 A8 H_A7

M21 D27 A7 L3

H_D28 L22 K1 H_A6

H_D29 D28 A6 H_A5

J24 D29 A5 L6

H_D30 K23 K4 H_A4

H_D31 D30 A4 H_A3

H25 D31 A3 K2

H_D32 M23

H_D33

H_D34

N22

D32

D33

SOCKET 478 VID0 AE5 CPUVID0 18,31

P21 D34 VID1 AE4 CPUVID1 18,31

H_D35 M24 AE3

H_D36 D35 VID2 CPUVID2 18,31

N23 D36 VID3 AE2 CPUVID3 18,31

H_D37 M26 AE1

H_D38 D37 VID4 CPUVID4 18,31

N26 D38

H_D39 N25 H3

H_D40 D39 REQ4 H_REQ4 7

R21 D40 REQ3 J3 H_REQ3 7

H_D41 P24 J4

H_D42 D41 REQ2 H_REQ2 7

R25 D42 REQ1 K5 H_REQ1 7

H_D43 R24 J1

H_D44 D43 REQ0 H_REQ0 7

T26 D44

H_D45 T25 AB4 H_BPRM5_PREQ#

H_D46 D45 BPM5 H_BPRM4_PRDY#

T22 D46 BPM4 AA5

H_D47 T23 Y6

H_D48 D47 BPM3

U26 D48 BPM2 AC4

H_D49 U24 AB5 H_BPM1

H_D50 D49 BPM1 H_BPM0

U23 D50 BPM0 AC6

H_D51 V25

H_D52 D51 VCORE

U21 D52

H_D53 V22 AD25 8 7

H_D54 D53 TESTHI12 R208 56

V24 D54 TESTHI11 A6 6 5

H_D55 W26 Y3 4 3

H_D56 D55 TESTHI10

Y26 D56 TESTHI9 W4 2 1

H_D57 W25 U6

H_D58 D57 TESTHI8 RN11

Y23 D58 TESTHI7 AB22

H_D59 Y24 AA20 56

H_D60 D59 TESTHI6

Y21 D60 TESTHI5 AC23

H_D61 AA25 AC24

H_D62 D61 TESTHI4 RN13

AA22 D62 TESTHI3 AC20

H_D63 AA24 AC21 56

D63 TESTHI2

TESTHI1 AA2 8 7

7 H_RS0# F1 RS0 TESTHI0 AD24 6 5

7 H_RS1# G5 RS1 4 3

F4 2 1

H1 VSS

H4 VSS

H23 VSS

H26 VSS

A11 VSS

A13 VSS

A15 VSS

A17 VSS

A19 VSS

A21 VSS

A24 VSS

A26 VSS

A3 VSS

A9 VSS

AA1 VSS

AA11VSS

AA13VSS

AA15VSS

AA17VSS

AA19VSS

AA23VSS

AA26VSS

AA4 VSS

AA7 VSS

AA9 VSS

AB10VSS

AB12VSS

AB14VSS

AB16VSS

AB18VSS

AB20VSS

AB21VSS

AB24VSS

AB3 VSS

AB6 VSS

AB8 VSS

AC11VSS

AC13VSS

AC15VSS

AC17VSS

AC19VSS

AC2 VSS

AC22VSS

AC25VSS

AC5 VSS

AC7 VSS

AC9 VSS

AD1 VSS

AD10VSS

AD12VSS

AD14VSS

AD16VSS

AD18VSS

AD21VSS

AD23VSS

AD4 VSS

AD8 VSS

AE11VSS

AE13VSS

AE15VSS

AE17VSS

AE19VSS

AE22VSS

AE24VSS

AE26VSS

AE7 VSS

AE9 VSS

AF1 VSS

AF10VSS

AF12VSS

AF14VSS

AF16VSS

AF18VSS

AF20VSS

AF26VSS

AF6 VSS

AF8 VSS

B10 VSS

B12 VSS

B14 VSS

B16 VSS

B18 VSS

B20 VSS

B23 VSS

B26 VSS

B4 VSS

B8 VSS

C11 VSS

C13 VSS

C15 VSS

C17 VSS

C19 VSS

C2 VSS

7 H_RS2# RS2

SOCKET478 1 2

3 4

5 6

7 8

7 H_D[63:0] H_D[63:0] RN17

56

7 H_A[31:3] H_A[31:3]

Intel Require Change From 39 ohm To 51 ohm

H_BPRM5_PREQ# R178 51

VCORE

H_BPRM4_PRDY# R176 51

H_BPM1 R174 51 CLOSE TO CPU

H_BPM0 R171 51

Size Document Number Rev

A3 SOCKET478-Part 1 01

Date: Monday, August 19, 2002 Sheet 3 of 34

CPU SIGNAL

VCORE

TERMINATION

R170 CLOSE TO CPU

49.9/1%

H_BREQ0# R212 51

VCORE

H_PWRGD R158 300

THERMTRIP# R215 62

R167 C146

C160 C147

100/1% 0.1uF

220pF 0.01uF

AA21

GTLREF GENERATION CIRCUITS VCORE

AA6

C25

D10

D12

D14

D16

D18

D20

D21

D24

C22

F20

C5

C7

C9

D3

D6

D8

E1

VCORE 47uF/TANB U10B

F6

TC2 H_TDI R210 150

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GTLREF0

GTLREF1

GTLREF2

GTLREF3

L5 4.7uH AE23 AC3

VCCIOPLL IERR H_TRST R213 680

MCERR V6

L4 4.7uH AD20 B6 H_FERR#

VCCA FERR H_FERR# 14

STPCLK Y4 H_STPCLK# 14

TC1 CLOSE TO CPU

+

AD22 VSSA BINIT AA3

INIT W5 H_INIT# 14,17

47uF/TANB AB2

RSP

R157 51 AC26

DBSY H5

H2

H_DBSY# 7 ITP/TAP TERMINATION

ITP_CLK0 DRDY H_DRDY# 7

R154 51 AD26 J6

ITP_CLK1 TRDY H_TRDY# 7

ADS G1 H_ADS# 7

7 H_DBI3 V21 G4 VCORE

DB#3 LOCK H_LOCK# 7

7 H_DBI2 P26 H6 H_BREQ0#

DB#2 BR0 H_BREQ0# 7

7 H_DBI1 G25 G2 H_TMS R211 39

DB#1 BNR H_BNR# 7

7 H_DBI0 E21 DB#0 HIT F3 H_HIT# 7

HITM E3 H_HITM# 7

7 H_A_STB1 R5 ADSTB1 BPRI D2 H_BPRI# 7

7 H_A_STB0 L5 E2 DBRESET# R161 150(NI)

ADSTB0 DEFER H_DEFER# 7

DBRESET# AE25 D4 H_TCK

DBRESET TCK H_TDI

TDI C1

F7 H_TMS

TMS H_TRST H_CPURST# R153 51

14 H_NMI E5 LINT1 TRST E6

14 H_INTR D1 D5 H_TDO

LINT0 TDO

PROCHOT C3

IGNNE B2 H_IGNNE# 14

6 CPUHCLK# AF23 B5 H_TDO R214 75

BCLK1 SMI H_SMI# 14

6 CPUHCLK AF22 BCLK0 A20M C6 H_A20M# 14

SLP AB26 H_SLP# 14

AB23 H_PWRGD

R184

R183

51

51

P1 COMP1

SOCKET 478 PWRGOOD

RESET AB25 H_CPURST# H_PWRGD

H_CPURST#

14

7

H_TCK R216 27

L24 COMP0

THERMDA B3 THRMDP 18

THERMDC C4 THRMDN 18 CLOSE TO ITP PORT

7 H_D_STBP3 W23 A2 R_THTRIP#

STBP3 THERMTRIP THERMTRIP# 15

7 H_D_STBP2 P23 R209

STBP2 0

7 H_D_STBP1 J23 STBP1 BSEL0 AD6 CPUBSEL0# 6

7 H_D_STBP0 F21 STBP0 BSEL1 AD5

7 H_D_STBN3 W22 STBN3

7 H_D_STBN2 R22 AC1 VCCVID

STBN2 AP0

7 H_D_STBN1 K22 STBN1 AP1 V5

7 H_D_STBN0 E22 STBN0

VCCVID AF4

TP1 TP A5 AF3

TP2 TP VCC_SENSE VCCVIDPRG

A4 VSS_SENSE C162 C167

E11 VSS

E13 0.1uF 4.7uF(NI)

VSS

E15 VSS VSS Y5

E17 VSS VSS Y25

E19 VSS VSS Y22

E23 VSS VSS Y2

E26 VSS VSS W6

E4 VSS VSS W3

E7 VSS VSS W24

E9 VSS VSS W21

F10 VSS VSS V4

F12 VSS VSS V26

F14 VSS VSS V23

F16 VSS VSS V1

F18 VSS VSS U5

F2 VSS VSS U25

F22 VSS VSS U22

F25 VSS VSS U2

F5 VSS VSS T6

F8 VSS VSS T3

G21 VSS VSS T24

G24 VSS VSS T21

G3 VSS VSS R4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M22

M25

N21

N24

R23

R26

K21

K24

P22

P25

L23

L26

J22

J25

M2

M5

G6

N3

N6

R1

K3

K6

P2

P5

L1

L4

J2

J5

SOCKET478

Size Document Number Rev

A3 SOCKET478-Part 2 01

Date: Monday, August 19, 2002 Sheet 4 of 34

Put on the North side of the processor

VCORE

C128 C129 C130 C131 C132 C133 C134 C135 C136 C137

10uF(NI) 10uF 10uF(NI) 10uF 10uF(NI) 10uF 10uF(NI) 10uF 10uF(NI) 10uF

Put in the processor cavity

VCORE

C172 C166 C165 C173 C163 C164 C177 C178 C179 C180 C161 C176 C181

10uF(NI) 10uF(NI) 10uF 10uF(NI) 10uF 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF 0.1uF(NI) 0.1uF(NI) 0.1uF(NI)

Put on the Sourth side of the processor

VCORE

C204 C205 C206 C207 C208 C209 C210 C211 C212 C213 C214 C215 C216 C217

10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI) 10uF(NI)

Size Document Number Rev

A3 DECOUPLING 01

Date: Monday, August 19, 2002 Sheet 5 of 34

Clock Synthesizer VCC3CLK

FB24

VCC3_3

+ CE17 BEAD120

10uF/16V

VCC3_3

FB23

C89 C94 C81 C84 C91 C97 C103 C101

C108 + CE16 BEAD120

0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

0.1uF 10uF/16V

13

18

30

33

41

45

24

U7

7 VDDPCI

VDDPCI

VDDREF

VDD3V66

VDD3V66

AVDD48

VDDCPU

VDDCPU

VDDA

C82 10pF 2 X1

Y2 47 R71 27.4/1%

CPUCLK0 CPUHCLK 4

C83 10pF 14.318MHz R75 27.4/1%

3 46

X2 CPUCLK0# CPUHCLK# 4

R74 33 PCICLKF0 FS0 5 44 R80 27.4/1%

18 PCICLK_LPC PCICLKF0/FS0 CPUCLK1 GMCHCLK 7

R78 33 PCICLKF1 FS1 6 43 R84 27.4/1%

14 PCICLK_ICH4 PCICLKF1/FS1 CPUCLK1# GMCHCLK# 7

R79 33 PCICLK0 WDEN 9

17 PCICLKFWH PCICLKF2/WDEN

10 PCICLK0/FS5 CPUCLK2 40

11 PCICLK1 CPUCLK2# 39

12 PCICLK2

R88 33 15

20 PCICLK1 PCICLK3 VCC3CLK R85 R81 R76 R72

R89 33 16 49.9/1% 49.9/1% 49.9/1% 49.9/1%

19 PCICLK2 PCICLK4

R92 33 17 38 R94 10K

19 PCICLK3 PCICLK5 MULTISEL

37 R93 475/1%

IREF

R101 33 20 R103 33

15 ICH4_3V66 3V66_1 SIO_CLK48 18

R107 33 21 35 FS3 R102 33

13 AGPCLK_CONN 3V66_2 48MHz_USB/FS3 USBCLK 15

R111 33 22 34 R108 33

8 GMCH_3V66 3V66_3 48MHz_DOT DOTCLK 8

C102 C100 C98 FS4 31 R68 33

3V66_0/VCH_48MHz/FS4

48 FS2 ICH4_CLK14 15

10pF(NI) 10pF(NI) 10pF(NI) REF0/FS2 R69 33

AC97CLK 29

R115 4.7K(NI)

VCC3CLK

26 VTTPWRGD

PD#/VTT_PWRGD R114 220

27

12,15,18,19,20,26 SMBDATA SDATA VRM_PWRGD 15,31,33

28

12,15,18,19,20,26 SMBCLK SCLK

23 R113 4.7K

RESET# VCC3CLK

GND

GND

GND

GND

GND

GND

GND

GND

GND

CLKRST# 33

14

19

25

29

32

36

42

W83194BR-B FS3 RX3 4.7K

4

FS2 RX4 4.7K

VCC3_3

R73 10K(NI) FS0

VCC3_3

R90

Watch dog 1.5K

Enable

R82

R83

WDEN

0

10K(NI)

JP1

1

4 CPUBSEL0# 2

3

MCHBSEL0# 8

R104

FS4

10K

Size Document Number Rev

A3 CLOCK SYNTHESIZER 01

Date: Monday, August 19, 2002 Sheet 6 of 34

12 MEMCLK2# MEMCLK4 12

H_D[63:0] 12 MEMCLK2

H_D[63:0] 3 MEMCLK4# 12

H_A[31:3] 12 MEMCLK0#

H_A[31:3] 3 MEMCLK3 12

12 MEMCLK0 MEMCLK3# 12

12 MEMCLK1# MEMCLK5 12

U11A 12 MEMCLK1 MEMCLK5# 12

H_D0 T30 W31 H_A3

HD#0 BROOKDALE-G HA#3

AM34

H_A4

AN11

AN21

AN34

AK22

AP11

AP21

AP33

H_D1

AL21

AL33

R33 AA33

AN9

AP9

H_D2 HD#1 HA#4 H_A5 U11B

R34 HD#2 HOST,HUB HA#5 AB30

H_A6

H_D3 N34 V34

H_D4 HD#3 HA#6 H_A7

R31 Y36 AN4 AN15

SCMD_CLK0

SCMD_CLK0#

SCMD_CLK1

SCMD_CLK1#

SCMD_CLK2

SCMD_CLK2#

SCMD_CLK3

SCMD_CLK3#

SCMD_CLK4

SCMD_CLK4#

SCMD_CLK5

SCMD_CLK5#

HD#4 HA#7 10 DM_MD0 SDQ_0 SMAA12/BS0 RM_MAA12 11,12

H_D5 L33 AC33 H_A8 10 DM_MD1 AP2 AL15 RM_MAA11 11,12

H_D6 HD#5 HA#8 H_A9 SDQ_1 SMAA11/DQS8

L36 HD#6 HA#9 Y35 10 DM_MD2 AT3 SDQ_2 SMAA10/DQ31 AK26 RM_MAA10 11,12

H_D7 P35 AA36 H_A10 10 DM_MD3 AP5 AK16 RM_MAA9 11,12

H_D8 HD#7 HA#10 H_A11 SDQ_3 SMAA9/SMA3

J36 HD#8 HA#11 AC34 10 DM_MD4 AN2 SDQ_4 SMAA8/SMA4 AN17 RM_MAA8 11,12

H_D9 K34 AB34 H_A12 10 DM_MD5 AP3 AP17 RM_MAA7 11,12

H_D10 HD#9 HA#12 H_A13 SDQ_5 SMAA7/SMA6

K36 HD#10 HA#13 Y34 10 DM_MD6 AR4 SDQ_6 SMAA6/SDQ29 AP19 RM_MAA6 11,12

H_D11 M30 AB36 H_A14 10 DM_MD7 AT4 AL17 RM_MAA5 11,12

H_D12 HD#11 HA#14 H_A15 SDQ_7 SMAA5/SMA8

M35 HD#12 HA#15 AC36 10 DM_MD8 AT5 SDQ_8 SMAA4/SMA11 AL19 RM_MAA4 11,12

H_D13 L34 AC31 H_A16 10 DM_MD9 AR6 AK20 RM_MAA3 11,12

H_D14 HD#13 HA#16 H_A17 SDQ_9 SMAA3/SMA7

K35 HD#14 HA#17 AF35 10 DM_MD10 AT9 SDQ_10 SMAA2/SMA9 AP23 RM_MAA2 11,12

H_D15 H36 AD36 H_A18 10 DM_MD11 AR10 AN25 RM_MAA1 11,12

H_D16 HD#15 HA#18 H_A19 SDQ_11 SMAA1/SDQ19

G34 HD#16 HA#19 AD35 10 DM_MD12 AT6 SDQ_12 SMAA0/SMA12 AL25 RM_MAA0 11,12

H_D17 G36 AE34 H_A20 10 DM_MD13 AP6 AK18 RM_MAB5 11,12

H_D18 HD#17 HA#20 H_A21 SDQ_13 SMAB5

J33 HD#18 HA#21 AD34 10 DM_MD14 AT8 SDQ_14 SMAB4 AN19 RM_MAB4 11,12

H_D19 D35 AE36 H_A22 10 DM_MD15 AP8 AN23 RM_MAB2 11,12

H_D20 HD#19 HA#22 H_A23 SDQ_15 SMAB2

F36 HD#20 HA#23 AF36 10 DM_MD16 AP10 SDQ_16 SMAB1 AP25 RM_MAB1 11,12

H_D21 F34 AE33 H_A24 10 DM_MD17 AT11

H_D22 HD#21 HA#24 H_A25 SDQ_17

E36 HD#22 HA#25 AF34 10 DM_MD18 AT13 SDQ_18 SBA1 AP27 RM_BS1 11,12

H_D23 H34 AG34 H_A26 10 DM_MD19 AT14 AN27

H_D24 HD#23 HA#26 H_A27 SDQ_19 SBA0 RM_BS0 11,12

F35 HD#24 HA#27 AG36 10 DM_MD20 AT10 SDQ_20

H_D25 D36 AE31 H_A28 AR12 AR2

H_D26 H35

HD#25

HD#26

HA#28

HA#29 AH35 H_A29 10

10

DM_MD21

DM_MD22 AR14

SDQ_21

SDQ_22

BROOKDALE-G SDQS0

SDQS1 AT7

DM_SDQS0

DM_SDQS1

10

10

H_D27 H_A30

H_D28

E33

E34

HD#27 HA#30 AG33

AG31 H_A31 10 DM_MD23 AP14

AT15

SDQ_23 DDR SDQS2 AT12

AT17

DM_SDQS2 10

HD#28 HA#31 10 DM_MD24 SDQ_24 SDQS3 DM_SDQS3 10

H_D29 B35 AP16 AR24

HD#29 10 DM_MD25 SDQ_25 SDQS4 DM_SDQS4 10

H_D30 G31 AB35 AT18 AT29

HD#30 HADSTB0# H_A_STB0 4 10 DM_MD26 SDQ_26 SDQS5 DM_SDQS5 10

H_D31 C36 AF30 AT19 AT34

HD#31 HADSTB1# H_A_STB1 4 10 DM_MD27 SDQ_27 SDQS6 DM_SDQS6 10

H_D32 D33 AR16 AL36

HD#32 10 DM_MD28 SDQ_28 SDQS7 DM_SDQS7 10

H_D33 D30 P36 AT16

HD#33 HIT# H_HIT# 4 10 DM_MD29 SDQ_29

H_D34 D29 M36 AP18 AP4

HD#34 HITM# H_HITM# 4 10 DM_MD30 SDQ_30 SDM0 DM_SDM0 10

H_D35 E31 T36 AR20 AR8

HD#35 ADS# H_ADS# 4 10 DM_MD31 SDQ_31 SDM1 DM_SDM1 10

H_D36 D32 T34 AR22 AP12

HD#36 BNR# H_BNR# 4 10 DM_MD32 SDQ_32 SDM2 DM_SDM2 10

H_D37 C34 M34 AP22 AR18

HD#37 BPRI# H_BPRI# 4 10 DM_MD33 SDQ_33 SDM3 DM_SDM3 10

H_D38 B34 U33 AP24 AT24

HD#38 BREQ0# H_BREQ0# 4 10 DM_MD34 SDQ_34 SDM4 DM_SDM4 10

H_D39 D31 U31 AT26 AP28

HD#39 DBSY# H_DBSY# 4 10 DM_MD35 SDQ_35 SDM5 DM_SDM5 10

H_D40 G29 N36 AT22 AR34

HD#40 DEFER# H_DEFER# 4 10 DM_MD36 SDQ_36 SDM6 DM_SDM6 10

H_D41 C32 U36 AT23 AL34

HD#41 DRDY# H_DRDY# 4 10 DM_MD37 SDQ_37 SDM7 DM_SDM7 10

H_D42 B31 V30 AT25

HD#42 HTRDY# H_TRDY# 4 10 DM_MD38 SDQ_38

H_D43 B32 T35 AR26 AL13

HD#43 HLOCK# H_LOCK# 4 10 DM_MD39 SDQ_39 SCKE3/SCK#5 RM_CKE3 11,12

H_D44 B30 AP26 AK14

HD#44 10 DM_MD40 SDQ_40 SCKE2/RSVD RM_CKE2 11,12

H_D45 B29 C26 AT28 AN13

HD#45 DINV3 H_DBI3 4 10 DM_MD41 SDQ_41 SCKE1/SDQ58 RM_CKE1 11,12

H_D46 E27 B33 AR30 AP13

HD#46 DINV2 H_DBI2 4 10 DM_MD42 SDQ_42 SCKE0/RSVD RM_CKE0 11,12

H_D47 C28 C35 AP30

HD#47 DINV1 H_DBI1 4 10 DM_MD43 SDQ_43

H_D48 B27 N33 AT27

HD#48 DINV0 H_DBI0 4 10 DM_MD44 SDQ_44

H_D49 D26 AR28 AL29

HD#49 10 DM_MD45 SDQ_45 SCS#0/SCKE2 RM_SCS0 11,12

H_D50 D28 V36 AT30 AP31

HD#50 HREQ0# H_REQ0 3 10 DM_MD46 SDQ_46 SCS#1/RSVD RM_SCS1 11,12

H_D51 B26 AA31 AT31 AK30

HD#51 HREQ1# H_REQ1 3 10 DM_MD47 SDQ_47 SCS#2/SCK#2 RM_SCS2 11,12

H_D52 G27 W33 AR32 AN31

HD#52 HREQ2# H_REQ2 3 10 DM_MD48 SDQ_48 SCS#3/SCAS# RM_SCS3 11,12

H_D53 H26 AA34 AT32

HD#53 HREQ3# H_REQ3 3 10 DM_MD49 SDQ_49

H_D54 B25 W35 AR36 AK28

HD#54 HREQ4# H_REQ4 3 10 DM_MD50 SDQ_50 SRAS#/SCKE0 RM_RAS# 11,12

H_D55 C24 AP35 AN29

HD#55 HI[10:0] 14 10 DM_MD51 SDQ_51 SCAS#/RSVD RM_CAS# 11,12

H_D56 B23 AF2 HI10 AP32 AP29

HD#56 HI10 10 DM_MD52 SDQ_52 SWE#/SDQ5 RM_WE# 11,12

H_D57 B24 AE2 HI9 AT33

HD#57 HI9 10 DM_MD53 SDQ_53

H_D58 E23 AF3 HI8 AP34 AK24 RDCLKO SR1 RDCLKI & RDCLKO 100mils

HD#58 HI8 10 DM_MD54 SDQ_54 SRCVEN_OUT#

H_D59 C22 AE5 HI7 AT35 AL23 RDCLKI 0(NI)

HD#59 HI7 10 DM_MD55 SDQ_55 SRCVEN_IN# LENGTH 5mils WIDTH

H_D60 G25 AE4 HI6 AN36

HD#60 HI6 10 DM_MD56 SDQ_56

H_D61 B22 AF4 HI5 AM36 AJ34 R204 60.4/1%

HD#61 HI5 10 DM_MD57 SDQ_57 SMY_RCOMP VCC2_5

H_D62 D24 AD8 HI4 AK36 AD16 R205 60.4/1%

HD#62 HI4 10 DM_MD58 SDQ_58 SMX_RCOMP

H_D63 G23 AC5 HI3 AJ36 AM2

HD#63 HI3 10 DM_MD59 SDQ_59 SM_VREF DDRVREF 12

AC7 HI2 10 DM_MD60 AP36

HI2 HI1 SDQ_60 C199 C202 C194

4 H_D_STBP0 L31 HDSTBP0# HI1 AB8 10 DM_MD61 AM35 SDQ_61

4 H_D_STBP1 J34 AA7 HI0 10 DM_MD62 AK35

HDSTBP1# HI0 SDQ_62 0.1uF 0.1uF 0.1uF

4 H_D_STBP2 E29 HDSTBP2# 10 DM_MD63 AK34 SDQ_63

4 H_D_STBP3 E25 HDSTBP3# HI_STBS AD4 HI_STBS 14

4 H_D_STBN0 N31 AC4 HI_STBF 14 82845G/GL BGA824

HDSTBN0# HI_STBF

4 H_D_STBN1 G33 HDSTBN1#

4 H_D_STBN2 C30 HDSTBN2# RS2# P34 H_RS2# 3

4 H_D_STBN3 D25 U34 H_RS1# 3 R201 R203

HDSTBN3# RS1#

RS0# R36 H_RS0# 3

4 H_CPURST# D22 60.4/1% 60.4/1%

CPURST# R173

6 GMCHCLK K30 24.9/1% R187

HCLK HX_RCOMP 24.9/1%

6 GMCHCLK# J31 HCLK# HX_RCOMP B28

D27 V35 HY_RCOMP

HD_VREF2 HY_RCOMP

H24 HD_VREF1 HX_SWING H28 H_XY_SWING 9 HS3

9 MCH_GTLREF H30 HD_VREF0 HY_SWING Y30

AD30 HA_VREF HI_VREF AD3 HUBREF_A 9,14

P30 HCC_VREF HI_RCOMP AC2 VCC1_5 1 1 8 8

HI_SWING AD2 HI_VSWING 9,14

R195 2 7

82845G/GL BGA824 68.1/1% 2 7 HS4

HS-RACK

3 3 6 6

4 4 5 5

MCHPAD(NI)

Size Document Number Rev

A3 GMCH PART1 01

Date: Monday, August 19, 2002 Sheet 7 of 34

U11C 13 G_AD[31:0] G_AD[31:0]

VCC1_5 13 G_SBA[7:0] G_SBA[7:0]

13 G_PIPE#

G_PIPE# H8 AGP/DVO V4 G_AD0

G_SBA0 GPIPE# GAD0/DVOBHSYNC G_AD1

C3 GSBA0/ADDIN0 GAD1/DVOBVSYNC V2

G_SBA1 C2 W4 G_AD2

G_SBA2 GSBA1/ADDIN1 GAD2/DVOBD1 G_AD3

D3 GSBA2/ADDIN2 GAD3/DVOBD0 W5

VCC2_5 G_SBA3 D2 U5 G_AD4

G_SBA4 GSBA3/ADDIN3 GAD4/DVOBD3 G_AD5

AB10

E4 U4

V14

P10

V10

T14

Y14

GSBA4/ADDIN4 GAD5/DVOBD2

W9

G_SBA5 G_AD6

G1

C1

D4

D6

R1

R9

A3

A7

K6

P6

V6

U11D

L1

L9

E2 GSBA5/ADDIN5 GAD6/DVOBD5 U2

G_SBA6 F3 V3 G_AD7

G_SBA7 GSBA6/ADDIN6 GAD7/DVOBD4 G_AD8

W19 AH8 F2 T2

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCCAGP

VCC VCCSM GSBA7/ADDIN7 GAD8/DVOBD5 G_AD9

Y19 VCC VCCSM AK8 GAD9/DVOBD9 T3

AA19 AG9 13 G_WBF# G5 T4 G_AD10

VCC VCCSM GWBF# GAD10/DVOBD8

1

T20 AJ9 + CE44 + CE40 + CE41 13 G_RBF# G7 R2 G_AD11

VCC VCCSM GRBF# GAD11/DVOBD11 G_AD12

W20

AB20

VCC VCCSM AL9

AD22 100uF(NI) 100uF(NI) 100uF(NI) G_ST0 C4

BROOKDALE-G GAD12/DVOBD10 R5

R7 G_AD13

VCC VCCSM 13 G_ST0 GST0 GAD13/DVOBCCLKINT

G_ST1 G_AD14

2

U21 VCC VCCSM AM22 13 G_ST1 B4 GST1 GAD14/DVOBFLDSTL T8

W21 AJ23 13 G_ST2

G_ST2 B3 P3 G_AD15

VCC VCCSM GST2 GAD15/MDDC DATA G_AD16

AA21 VCC VCCSM AL37 GAD16/DVOCVSYNC P8

T22 AU9 VCC3SBYM 13 G_ADSTB0 V8 K4 G_AD17

VCC VCCSM GAD_STB0/DVOBCLK GAD17/DVOCHSYNC G_AD18

V22 VCC VCCSM AK10 Add Two 22UF 13 G_ADSTB0# U7 GAD_STB0#/DVOBCLK# GAD18/DVOCBLANK# K2

Y22 AD24 13 G_ADSTB1 M8 J2 G_AD19

VCC VCCSM CAP GAD_STB1/DVOCCLK GAD19/DVOCD0 G_AD20

AB22 VCC VCCSM AJ11 13 G_ADSTB1# L7 GAD_STB1#/DVOCCLK# GAD20/DVOCD1 M3

A9 AL11 13 G_SBSTB F4 L5 G_AD21

VCC VCCSM GSBSTB GAD21/DVOCD2 G_AD22

B9 VCC VCCSM AU25 13 G_SBSTB# E5 GSBSTB# GAD22/DVOCD3 L4

C9 AM26 H4 G_AD23

VCC VCCSM GAD23/DVOCD4 G_AD24

D9 VCC VCCSM AU13 13 G_FRAME# M4 G_FRAME#/MDVI DATA GAD24/DVOCD7 G2

E9 AM14 13 G_IRDY# N7 K3 G_AD25

VCC VCCSM G_IRDY#/MI2CCLK GAD25/DVOCD6 G_AD26

B10 VCC VCCSM AJ27 13 G_TRDY# N5 G_TRDY#/MI2CDATA GAD26/DVOCD9 J4

C10 AJ1 13 G_STOP# P2 J5 G_AD27

VCC VCCSM 13 G_DEVSEL# G_STOP#/MDDC CLK GAD27/DVOCD8 G_AD28 R355

D10 VCC VCCSM AL1 N2 G_DEVSEL#/MDVI CLK GAD28/DVOCD11 J7

F10 AJ15 13 G_REQ# D5 H3 G_AD29 NC-0

VCC VCCSM G_REQ# GAD29/DVOCD10 G_AD30

H10 VCC VCCSM AP15 13 G_PAR P4 G_PAR/ADD_DETECT GAD30/DVOBCINTR# K8

A11 AU29 13 G_GNT# B5 G4 G_AD31

VCC VCCSM G_GNT# GAD31/DVOCFLDSTL

B11 VCC VCCSM AH2 13 G_C_BE3 H2 GCBE3#/DVOC5

C11 VCC VCCSM AJ2 13 G_C_BE2 M2 GCBE2#

D11 VCC VCCSM AK2 13 G_C_BE1 N4 GCBE1#/DVOBBLANK# GCLKIN AE7 GMCH_3V66 6

E11 AL2 R4 AJ31

G11

VCC

VCC

BROOKDALE-G VCCSM

VCCSM AM30

13 G_C_BE0 GCBE0#/DVOBD7 RSTIN#

DREFCLK D14

HPCIRST#

DOTCLK

14,17,18,20,21

6

J11 VCC POWER VCCSM AH3 L2 AGP RCOMP/DVOBCRCOMP PWROK E7 PWROK 15,33

B12 VCC VCCSM AJ3 13 VREF_AGP_MCH W2 AGP_VREF PSBSEL Y3 MCHBSEL0# 6

C12 AK3 R189

VCC VCCSM 8.2K

D12 VCC VCCSM AL3 28 HSYNC B7 G15 BLUE 28

2

HSYNC BLUE

F12 VCC VCCSM AH4 28 VSYNC C6 VSYNC ANALOG DISPLAY BLUE# H16 BLUE# 28

H12 VCC VCCSM AJ4 28 DDCA_CLK D7 DDCA_CLK GREEN E15 GREEN 28

G13 AK4 L9 28 DDCA_DATA C7 F16 GREEN# 28

VCC VCCSM DDCA_DATA GREEN#

J13 VCC VCCSM AL4 B16 REFSET RED C15 RED 28

H14 AU17 0.68uH D16 RED# 28

VCC VCCSM RED#

P14 VCC VCCSM AD18

J15 AJ5 82845G/GL BGA824

VCC VCCSM R172 R186 C184 R192

1

P15 VCC VCCSM AL5

P18 AU5 VCC1_5 R356 R357

VCC VCCSM NC-0 NC-0 121/1% 40.2/1% 0.1uF 8.2K(NI)

P16 VCC VCCSM AM18

P17 VCC VCCSM AJ19

AB16 VCC VCCSM AK32

Y16 AU33 C229

VCC VCCSM

V16 VCC VCCSM AH6

T16 AK6 4.7uF

VCC VCCSM

AA17 VCC VCCSM AD20

W17 VCC VCCSM AP20

2

U17 AG7 R222 L10

VCC VCCSM L0603-31

AB18 VCC VCCSM AJ7

W18 AL7 1 L8 VCCA_DAC L7

VCC VCCSM R163 10uH

T18 VCC VCCSM AP7

V19 AH10 1uH

VCC1_5 1 2 VCCA_DPLL VCORE

VCC VCCSM C155 C156

U19 VCC VCCSM AH12

K10 AH14 1

VCC VCCSM 0.01uF 0.1uF

1

K12 VCC VCCSM AH18

VCORE K14 AH22

VCC VCCSM

1

K16 VCC VCCSM AH26 + CE31 + CE33 R358 C158 C144 C145

NC-0

B18 AG1 22uF/10V(NI) 560uF/16V 0.1uF 0.1uF(NI) 0.1uF(NI)

VTTFSB VCCA_SM

2

C18 VTTFSB VCCA_SM AG2

1

D18 VTTFSB

C224 C192 + CE36

H18 VTTFSB VCCQSM AT20 FSB ADDR & CNTL

B19 AT21 0.1uF 0.1uF 100uF/25V

VTTFSB VCCQSM

2

C19 VTTFSB VCCQSM AU21

D19 L6

VTTFSB 0.82uH

E19 VTTFSB VTTDECAP A31

G19 AC37 VCC1_5 1 2 VCCA_FSB

VTTFSB VTTDECAP VCC1_5

J19 VTTFSB VTTDECAP R37

B20 L37 VCORE

VTTFSB VTTDECAP

C20 VTTFSB VTTDECAP G37

D20 CE30 C142

VTTFSB VCCA_FSB C153

F20 VTTFSB VCCA_FSB A17

H20 AD14 C170 C174 C183 C187 C149 22uF/10V 0.1uF C218 C143

VTTFSB VCCA_HI 0.1uF(NI)

P20 VTTFSB VCCA_HI AD10

P22 AD6 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF(NI) 0.1uF(NI)

VTTFSB VCCHI VCC1_5

P24 VTTFSB VCCHI AC9

T24 VTTFSB VCCHI AB14

V24 VTTFSB VCCHI AC1 FSB DATA

AB24 VTTFSB VCCHI AE3

F18 A13 VCCA_DPLL

VTTFSB VCCA_DPLL

Y24 VTTFSB VCCA_DAC B14

K18 A15 VCCA_DAC

VTTFSB VCCA_DAC

K20 VTTFSB VCCGPIO B6 VCC3_3

K22 VTTFSB

K26 AF10 R200 60.4/1%

VTTFSB SMX_RCOMP VCC2_5

M28 C152

VTTFSB R202

T28 VTTFSB

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

Y28 0.1uF

VTTFSB

AU37NC

AU36NC

AT37NC

AU2 NC

AU1 NC

AT1 NC

AJ35 NC

AH34NC

B1 NC

B37 NC

A36 NC

A2 NC

AD28 60.4/1%

VTTFSB

AB2

AB3

AA2

AA3

AA4

AA5

A37

82845G/GL

W7

Y2

Y4

Y8

BGA824

Size Document Number Rev

A3 GMCH PART2 01

Date: Thursday, August 29, 2002 Sheet 8 of 34

HI_VSWING 7,14

R199 R198 10 mil Trace,

AM24

AM10

AC24

AU23

AR23

AR17

AD17

AH30

AA24

AB17

AJ17

226/1% 100/1%

W24

AM3

AG4

AG3

AR9

AU3

AR3

AN3

AC3

AB4

G17

N37

C16

U24

R24

C31

A25

V17

E17

7mil Space

F24

Y17

T17

J17

U11E

VCC1_5 HUBREF_A 7,14

U18 C17

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS C188 C232 C219 R197 C186 C230 C191

V18 VSS VSS B17 PLACE NOTE:

Y18 VSS VSS AM16 CAP PLACE

AA18 AA16 0.01uF 0.01uF 0.1uF 100/1% 0.1uF 0.01uF 0.01uF

VSS VSS AT MIDPOINT

AL31 VSS VSS W16

AR31 VSS VSS U16 OF THE BUS.

AU31 VSS VSS W3

F32 VSS VSS U3

H32 VSS VSS R3 NEAR MCH NEAR ICH NEAR MCH NEAR ICH

K32 VSS VSS D17

M32 VSS VSS N3

P32 VSS VSS L3

T32 VSS VSS J3

V32 VSS VSS G3

Y32 VSS VSS E3

AB32 AT2 R160 10 mil Trace,

VSS VSS 49.9/1%

AD32 VSS VSS F30 7mil Space

AF32 VSS VSS AR29 VCORE MCH_GTLREF 7

AH32 VSS VSS AJ29

AM4 VSS VSS AG29

A5 AE29 C157 R165 C140

VSS VSS

C5 VSS VSS AC29

AG5 AA29 0.1uF 100/1% 0.1uF

VSS VSS

AN5 VSS VSS W29

AR5 R29

P19

VSS

VSS

BROOKDALE-G VSS

VSS U29

T19 VSS VSS VSS N29

AB19 VSS VSS L29 NEAR MCH

AD19 VSS VSS J29

AR19 VSS VSS C29

AM32 VSS VSS A29

A33 VSS VSS AU15

C33 VSS VSS AR15

AJ33 VSS VSS AD15

AN33 VSS VSS D15

AR33 VSS VSS B2

F6 VSS VSS AR1 10 mil Trace,

H6 AN1 C127 0.01uF

VSS VSS 7mil Space

M6 VSS VSS AE1

T6 VSS VSS AA1 VCORE H_XY_SWING 7

Y6 VSS VSS U1

AB6 N1 R159

VSS VSS 301/1% R164

AF6 VSS VSS J1

AM6 VSS VSS E1

U20 AM28 150/1%

VSS VSS

V20 VSS VSS F28

Y20 VSS VSS AU27

AA20 VSS VSS AR27

AM20 VSS VSS AL27

A21 VSS VSS AC14

B21 VSS VSS AA14

C21 VSS VSS W14

D21 VSS VSS U14

E21 R14 VCC2_5 SYSTEM MEMORY DECOUPLING

VSS VSS

G21 VSS VSS F14

J21 VSS VSS AR13

D34 VSS VSS AJ13

W34 VSS VSS J27

A35 C27 C226 C221 C223 C220 C222 C225 C198 C197

VSS VSS

E35 VSS VSS A27

G35 E13 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI)

VSS VSS

J35 VSS VSS D13

L35 VSS VSS C13

AN7 VSS VSS B13

AR7 VSS VSS AM12

AU7 VSS VSS AK12

B8 VSS VSS F26

C8 VSS VSS AR25

D8 VSS VSS AJ25

F8 J25 VCC1_5

VSS VSS

P21 VSS VSS AU11 GMCH DECOUPLING

T21 VSS VSS AR11

V21 VSS VSS AR37

Y21 AN37 C141 C154 C169 C182 C201 C151 C185 C171

VSS VSS

AB21 VSS VSS C25

AD21 AJ37 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI)

VSS VSS

AJ21 VSS VSS AG37

AR21 VSS VSS AE37

F22 VSS VSS AA37

H22 VSS VSS U37

M10 VSS VSS AH28

T10 VSS VSS AF28

Y10 AB28

C14 VSSA_DAC

B15 VSSA_DAC

VSS VSS

AH16 VSS VSS V28

AH20 VSS VSS P28

AH24 K28

U22 VSS

W22 VSS

AA22VSS

N35 VSS

R35 VSS

U35 VSS

AA35VSS

AC35VSS

AE35VSS

AG35VSS

AL35VSS

AN35VSS

AR35VSS

AU35VSS

B36 VSS

W36 VSS

AF8 VSS

AM8 VSS

G9 VSS

J9 VSS

N9 VSS

U9 VSS

AA9 VSS

AE9 VSS

A23 VSS

C23 VSS

D23 VSS

J23 VSS

P23 VSS

AD23VSS

AH36VSS

AT36VSS

C37 VSS

E37 VSS

J37 VSS

VSS VSS

VSS K24

82845G/GL BGA824

Size Document Number Rev

A3 GMCH PART3 01

Date: Monday, August 19, 2002 Sheet 9 of 34

11,12 RM_SDQS0 R233 10

DM_SDQS0 7

RN24 RN31

10 10

11,12 RM_MD6 1 2 DM_MD6 7 11,12 RM_MD32 1 2 DM_MD32 7

11,12 RM_MD2 3 4 11,12 RM_MD36 3 4 11,12 RM_SDQS1 R234 10

DM_MD2 7 DM_MD36 7 DM_SDQS1 7

11,12 RM_MD7 5 6 DM_MD7 7 11,12 RM_MD33 5 6 DM_MD33 7

11,12 RM_MD3 7 8 DM_MD3 7 11,12 RM_MD37 7 8 DM_MD37 7

11,12 RM_SDQS2 R236 10

DM_SDQS2 7

RN23 RN32

10 10

11,12 RM_MD0 1 2 DM_MD0 7 11,12 RM_MD34 1 2 DM_MD34 7

11,12 RM_MD4 3 4 11,12 RM_MD38 3 4 11,12 RM_SDQS3 R238 10

DM_MD4 7 DM_MD38 7 DM_SDQS3 7

11,12 RM_MD5 5 6 DM_MD5 7 11,12 RM_MD39 5 6 DM_MD39 7

11,12 RM_MD1 7 8 DM_MD1 7 11,12 RM_MD35 7 8 DM_MD35 7

11,12 RM_SDQS4 R240 10

DM_SDQS4 7

RN25 RN33

10 10

11,12 RM_MD8 1 2 DM_MD8 7 11,12 RM_MD40 1 2 DM_MD40 7

11,12 RM_MD9 3 4 11,12 RM_MD44 3 4 11,12 RM_SDQS5 R243 10

DM_MD9 7 DM_MD44 7 DM_SDQS5 7

11,12 RM_MD12 5 6 DM_MD12 7 11,12 RM_MD45 5 6 DM_MD45 7

11,12 RM_MD13 7 8 DM_MD13 7 11,12 RM_MD41 7 8 DM_MD41 7

11,12 RM_SDQS6 R245 10

DM_SDQS6 7

RN26 RN34

10 10

11,12 RM_MD14 1 2 DM_MD14 7 11,12 RM_MD42 1 2 DM_MD42 7

11,12 RM_MD15 3 4 11,12 RM_MD46 3 4 11,12 RM_SDQS7 R247 10

DM_MD15 7 DM_MD46 7 DM_SDQS7 7

11,12 RM_MD10 5 6 DM_MD10 7 11,12 RM_MD43 5 6 DM_MD43 7

11,12 RM_MD11 7 8 DM_MD11 7 11,12 RM_MD47 7 8 DM_MD47 7

11,12 RM_SDM0 R232 10

DM_SDM0 7

RN27 RN36

10 10

11,12 RM_MD20 1 2 DM_MD20 7 11,12 RM_MD54 1 2 DM_MD54 7

11,12 RM_MD16 3 4 11,12 RM_MD55 3 4 11,12 RM_SDM1 R235 10

DM_MD16 7 DM_MD55 7 DM_SDM1 7

11,12 RM_MD17 5 6 DM_MD17 7 11,12 RM_MD50 5 6 DM_MD50 7

11,12 RM_MD21 7 8 DM_MD21 7 11,12 RM_MD51 7 8 DM_MD51 7

11,12 RM_SDM2 R237 10

DM_SDM2 7

RN28 RN35

10 10

11,12 RM_MD18 1 2 DM_MD18 7 11,12 RM_MD48 1 2 DM_MD48 7

11,12 RM_MD22 3 4 11,12 RM_MD49 3 4 11,12 RM_SDM3 R239 10

DM_MD22 7 DM_MD49 7 DM_SDM3 7

11,12 RM_MD19 5 6 DM_MD19 7 11,12 RM_MD52 5 6 DM_MD52 7

11,12 RM_MD23 7 8 DM_MD23 7 11,12 RM_MD53 7 8 DM_MD53 7

11,12 RM_SDM4 R241 10

DM_SDM4 7

RN29 RN38

10 10

11,12 RM_MD24 1 2 DM_MD24 7 11,12 RM_MD62 1 2 DM_MD62 7

11,12 RM_MD28 3 4 11,12 RM_MD58 3 4 11,12 RM_SDM5 R242 10

DM_MD28 7 DM_MD58 7 DM_SDM5 7

11,12 RM_MD29 5 6 DM_MD29 7 11,12 RM_MD63 5 6 DM_MD63 7

11,12 RM_MD25 7 8 DM_MD25 7 11,12 RM_MD59 7 8 DM_MD59 7

11,12 RM_SDM6 R244 10

DM_SDM6 7

RN30 RN37

10 10

11,12 RM_MD26 1 2 DM_MD26 7 11,12 RM_MD60 1 2 DM_MD60 7

11,12 RM_MD30 3 4 11,12 RM_MD56 3 4 11,12 RM_SDM7 R246 10

DM_MD30 7 DM_MD56 7 DM_SDM7 7

11,12 RM_MD27 5 6 DM_MD27 7 11,12 RM_MD61 5 6 DM_MD61 7

11,12 RM_MD31 7 8 DM_MD31 7 11,12 RM_MD57 7 8 DM_MD57 7

Size Document Number Rev

A4 DDR SERIES TERMINATION_1 01

Date: Monday, August 19, 2002 Sheet 10 of 34

VTT_DDR VTT_DDR VTT_DDR VTT_DDR

RN39 RN47 RN55 RN62

56 56 56 56

1 2 1 2 RM_SDM2 10,12 1 2 RM_BS0 7,12 1 2 RM_MD51 10,12

3 4 RM_MD0 10,12 3 4 RM_MAA9 7,12 3 4 RM_MD35 10,12 3 4 RM_MD60 10,12

1

1

C281 5 6 RM_MD4 10,12 C282 5 6 RM_MD18 10,12 C270 5 6 RM_MD40 10,12 C265 5 6 RM_MD56 10,12

0.1uF 7 8 RM_MD5 10,12 0.1uF 7 8 RM_MAA7 7,12 0.1uF 7 8 RM_MD44 10,12 0.1uF 7 8 RM_MD61 10,12

C0603 C0603 C0603 C0603

2

2

RN40 RN48 RN56 RN63

56 56 56 56

1 2 RM_MD1 10,12 1 2 RM_MD22 10,12 1 2 RM_RAS# 7,12 1 2 RM_MD57 10,12

3 4 RM_SDM0 10,12 3 4 RM_MAA8 7,12 3 4 RM_MD45 10,12 3 4 RM_SDM7 10,12

1

1

C279 5 6 RM_SDQS0 10,12 C277 5 6 RM_MD23 10,12 C272 5 6 RM_WE# 7,12 C283 5 6 RM_SDQS7 10,12

0.1uF 7 8 RM_MD6 10,12 0.1uF 7 8 RM_MD19 10,12 0.1uF 7 8 RM_SCS0 7,12 0.1uF 7 8 RM_MD62 10,12

C0603 C0603 C0603 C0603

2

2

RN41 RN49 RN57 RN64

56 56 56 56

1 2 RM_MD2 10,12 1 2 RM_MD24 10,12 1 2 RM_MD41 10,12 1 2 RM_MD58 10,12

3 4 RM_MD7 10,12 3 4 RM_MD28 10,12 3 4 RM_SCS2 7,12 3 4 RM_MD63 10,12

1

1

C280 5 6 RM_MD3 10,12 C267 5 6 RM_MD29 10,12 C285 5 6 RM_CAS# 7,12 C266 5 6 RM_MD59 10,12

0.1uF 7 8 RM_MD8 10,12 0.1uF 7 8 RM_MD25 10,12 0.1uF 7 8 RM_SCS3 7,12 0.1uF 7 8

C0603 C0603 C0603 C0603

2

2

RN42 RN50 RN58

56 56 56

1 2 RM_MD9 10,12 1 2 RM_MAA3 7,12 1 2 RM_SCS1 7,12 R295 33 RM_MAA5 7,12

3 4 RM_MD12 10,12 3 4 RM_MD26 10,12 3 4 RM_SDM5 10,12

1

1

C297 5 6 RM_MD13 10,12 C286 5 6 RM_MD30 10,12 C296 5 6 RM_SDQS5 10,12 C274 R299 33 RM_MAA4 7,12

0.1uF 7 8 RM_SDQS1 10,12 0.1uF 7 8 RM_MD27 10,12 0.1uF 7 8 RM_MD42 10,12 0.1uF

C0603 C0603 C0603 C0603 R296 33 RM_MAB5 7,12

56 R297

2

2

RN43 RM_MAA6 7,12 RN59 R301 33 RM_MAB4 7,12

56 56 R298 56

1 2 RM_SDM1 10,12 RM_SDQS3 10,12 1 2 RM_MD46 10,12

3 4 RM_MD14 10,12 56 R300 3 4 RM_MD43 10,12

1

1

C284 5 6 RM_CKE1 7,12 C275 RM_SDM3 10,12 C271 5 6 RM_MD47 10,12

0.1uF 7 8 RM_MD15 10,12 0.1uF 56 R302 0.1uF 7 8 RM_MD48 10,12

C0603 C0603 RM_MD31 10,12 C0603

CE46 CE47

2

2

RN44 RN52 RN60 + +

56 56 56

1 2 RM_CKE3 7,12 1 2 RM_MAA0 7,12 1 2 RM_MD49 10,12 470uF/16V 470uF/16V

3 4 RM_MD10 10,12 3 4 RM_MAA10 7,12 3 4 RM_MD52 10,12

1

1

C268 5 6 RM_MD11 10,12 C290 5 6 RM_BS1 7,12 C278 5 6 RM_MD53 10,12

0.1uF 7 8 RM_CKE2 7,12 0.1uF 7 8 RM_MD32 10,12 0.1uF 7 8 RM_SDM6 10,12

C0603 C0603 C0603

2

2

RN45 RN53 RN61

56 56 56

1 2 RM_CKE0 7,12 1 2 RM_MD36 10,12 1 2 RM_SDQS6 10,12

3 4 RM_MAA12 7,12 3 4 RM_MD33 10,12 3 4 RM_MD54 10,12

1

C293 5 6 RM_MD20 10,12 C294 5 6 RM_MD37 10,12 1 C292 5 6 RM_MD55 10,12

0.1uF 7 8 RM_MD16 10,12 0.1uF 7 8 RM_SDQS4 10,12 0.1uF 7 8 RM_MD50 10,12

C0603 C0603 C0603

2

RN46 RN54 RN51

56 56 33

1 2 RM_MD17 10,12 1 2 RM_SDM4 10,12 1 2 RM_MAB2 7,12

3 4 RM_MD21 10,12 3 4 RM_MD34 10,12 3 4 RM_MAA2 7,12

1

C291 5 6 RM_SDQS2 10,12 C276 5 6 RM_MD38 10,12 C295 5 6 RM_MAB1 7,12

0.1uF 7 8 RM_MAA11 7,12 0.1uF 7 8 RM_MD39 10,12 0.1uF 7 8 RM_MAA1 7,12

C0603 C0603 C0603

2

Size Document Number Rev

A4 DDR SERIES TERMINATION_2 01

Date: Monday, August 19, 2002 Sheet 11 of 34

VCC2_5

VCC2_5

104

112

128

136

143

156

164

172

180

108

120

148

168

DIMM2

15

22

30

54

62

77

96

38

46

70

85

7

104

112

128

136

143

156

164

172

180

108

120

148

168

DIMM1

15

22

30

54

62

77

96

38

46

70

85

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

7

RM_MAA0 48 2 RM_MD0

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

RM_MAB1 A0 D0 RM_MD1

7,11 RM_MAB1 43 A1 D1 4

RM_MAA0 48 2 RM_MD0 RM_MAB2 41 6 RM_MD2

7,11 RM_MAA0 A0 D0 RM_MD0 10,11 7,11 RM_MAB2 A2 D2

RM_MAA1 43 4 RM_MD1 RM_MAA3 130 8 RM_MD3

7,11 RM_MAA1 A1 D1 RM_MD1 10,11 A3 D3

RM_MAA2 41 6 RM_MD2 RM_MAB4 37 94 RM_MD4

7,11 RM_MAA2 A2 D2 RM_MD2 10,11 7,11 RM_MAB4 A4 D4

RM_MAA3 130 8 RM_MD3 RM_MAB5 32 95 RM_MD5

7,11 RM_MAA3 A3 D3 RM_MD3 10,11 7,11 RM_MAB5 A5 D5

RM_MAA4 37 94 RM_MD4 RM_MAA6 125 98 RM_MD6

7,11 RM_MAA4 A4 D4 RM_MD4 10,11 A6 D6

RM_MAA5 32 95 RM_MD5 RM_MAA7 29 99 RM_MD7

7,11 RM_MAA5 A5 D5 RM_MD5 10,11 A7 D7

RM_MAA6 125 98 RM_MD6 RM_MAA8 122 12 RM_MD8

7,11 RM_MAA6 A6 D6 RM_MD6 10,11 A8 D8

RM_MAA7 29 99 RM_MD7 RM_MAA9 27 13 RM_MD9

7,11 RM_MAA7 A7 D7 RM_MD7 10,11 A9 D9

RM_MAA8 122 12 RM_MD8 RM_MAA10 141 19 RM_MD10

7,11 RM_MAA8 A8 D8 RM_MD8 10,11 A10 D10

RM_MAA9 27 13 RM_MD9 RM_MAA11 118 20 RM_MD11

7,11 RM_MAA9 A9 D9 RM_MD9 10,11 A11 D11

RM_MAA10 141 19 RM_MD10 RM_MAA12 115 105 RM_MD12

7,11 RM_MAA10 A10 D10 RM_MD10 10,11 A12 D12

RM_MAA11 118 20 RM_MD11 103 106 RM_MD13

7,11 RM_MAA11 A11 D11 RM_MD11 10,11 A13 D13

RM_MAA12 115 105 RM_MD12 109 RM_MD14

7,11 RM_MAA12 A12 D12 RM_MD12 10,11 D14

103 106 RM_MD13 RM_BS0 59 110 RM_MD15

A13 D13 RM_MD13 10,11 BA0 D15

109 RM_MD14 RM_BS1 52 23 RM_MD16

D14 RM_MD14 10,11 BA1 D16

RM_BS0 59 110 RM_MD15 113 24 RM_MD17

7,11 RM_BS0 BA0 D15 RM_MD15 10,11 BA2 D17

RM_BS1 RM_MD16 RM_MD18

7,11 RM_BS1 52 BA1 D16 23

RM_MD17

RM_MD16 10,11

RM_SCS2

DIMM2 D18 28

RM_MD19

113 BA2 D17 24 RM_MD17 10,11 7,11 RM_SCS2 157 CS0 D19 31

28 RM_MD18 RM_SCS3 158 114 RM_MD20

D18 RM_MD18 10,11 7,11 RM_SCS3 CS1 D20

RM_SCS0 RM_MD19 RM_MD21

7,11 RM_SCS0

RM_SCS1

157 CS0 DIMM1 D19 31

RM_MD20

RM_MD19 10,11 71 NC/CS2 D21 117

RM_MD22

7,11 RM_SCS1 158 CS1 D20 114 RM_MD20 10,11 163 NC/CS3 D22 121

71 117 RM_MD21 123 RM_MD23

NC/CS2 D21 RM_MD21 10,11 D23

163 121 RM_MD22 RM_SDM0 97 33 RM_MD24

NC/CS3 D22 RM_MD22 10,11 DQM0 D24

123 RM_MD23 RM_SDM1 107 35 RM_MD25

D23 RM_MD23 10,11 DQM1 D25

RM_SDM0 97 33 RM_MD24 RM_SDM2 119 39 RM_MD26

10,11 RM_SDM0 DQM0 D24 RM_MD24 10,11 DQM2 D26

RM_SDM1 107 35 RM_MD25 RM_SDM3 129 40 RM_MD27

10,11 RM_SDM1 DQM1 D25 RM_MD25 10,11 DQM3 D27

RM_SDM2 119 39 RM_MD26 RM_SDM4 149 126 RM_MD28

10,11 RM_SDM2 DQM2 D26 RM_MD26 10,11 DQM4 D28

RM_SDM3 129 40 RM_MD27 RM_SDM5 159 127 RM_MD29

10,11 RM_SDM3 DQM3 D27 RM_MD27 10,11 DQM5 D29

RM_SDM4 149 126 RM_MD28 RM_SDM6 169 131 RM_MD30

10,11 RM_SDM4 DQM4 D28 RM_MD28 10,11 DQM6 D30

RM_SDM5 159 127 RM_MD29 RM_SDM7 177 133 RM_MD31

10,11 RM_SDM5 DQM5 D29 RM_MD29 10,11 DQM7 D31

RM_SDM6 169 131 RM_MD30 140 53 RM_MD32

10,11 RM_SDM6 DQM6 D30 RM_MD30 10,11 DQM8 D32

RM_SDM7 177 133 RM_MD31 55 RM_MD33

10,11 RM_SDM7 DQM7 D31 RM_MD31 10,11 D33

140 53 RM_MD32 RM_WE# 63 57 RM_MD34

DQM8 D32 RM_MD32 10,11 WE D34

55 RM_MD33 RM_CAS# 65 60 RM_MD35

D33 RM_MD33 10,11 CAS D35

RM_WE# 63 57 RM_MD34 RM_RAS# 154 146 RM_MD36

7,11 RM_WE# WE D34 RM_MD34 10,11 RAS D36

RM_CAS# 65 60 RM_MD35 147 RM_MD37

7,11 RM_CAS# CAS D35 RM_MD35 10,11 D37

RM_RAS# 154 146 RM_MD36 RM_CKE2 21 150 RM_MD38

7,11 RM_RAS# RAS D36 RM_MD36 10,11 7,11 RM_CKE2 CKE0 D38

147 RM_MD37 RM_CKE3 111 151 RM_MD39

D37 RM_MD37 10,11 7,11 RM_CKE3 CKE1 D39

RM_CKE0 21 150 RM_MD38 61 RM_MD40

7,11 RM_CKE0 CKE0 D38 RM_MD38 10,11 D40

RM_CKE1 111 151 RM_MD39 MEMCLK3 16 64 RM_MD41

7,11 RM_CKE1 CKE1 D39 RM_MD39 10,11 7 MEMCLK3 CK0/DNU D41

61 RM_MD40 MEMCLK3# 17 68 RM_MD42

D40 RM_MD40 10,11 7 MEMCLK3# CK0/DNU D42

MEMCLK0 16 64 RM_MD41 MEMCLK4 137 69 RM_MD43

7 MEMCLK0 CK0/DNU D41 RM_MD41 10,11 7 MEMCLK4 CK1 D43

MEMCLK0# 17 68 RM_MD42 MEMCLK4# 138 153 RM_MD44

7 MEMCLK0# CK0/DNU D42 RM_MD42 10,11 7 MEMCLK4# CK1 D44

MEMCLK1 137 69 RM_MD43 MEMCLK5 76 155 RM_MD45

7 MEMCLK1 CK1 D43 RM_MD43 10,11 7 MEMCLK5 CK2/DNU D45

MEMCLK1# 138 153 RM_MD44 MEMCLK5# 75 161 RM_MD46

7 MEMCLK1# CK1 D44 RM_MD44 10,11 7 MEMCLK5# CK2/DNU D46

MEMCLK2 76 155 RM_MD45 162 RM_MD47

7 MEMCLK2 CK2/DNU D45 RM_MD45 10,11 D47

MEMCLK2# 75 161 RM_MD46 RM_SDQS0 5 72 RM_MD48

7 MEMCLK2# CK2/DNU D46 RM_MD46 10,11 DQS0 D48

162 RM_MD47 RM_SDQS1 14 73 RM_MD49

D47 RM_MD47 10,11 DQS1 D49

RM_SDQS0 5 72 RM_MD48 RM_SDQS2 25 79 RM_MD50

10,11 RM_SDQS0 DQS0 D48 RM_MD48 10,11 DQS2 D50

RM_SDQS1 14 73 RM_MD49 RM_SDQS3 36 80 RM_MD51

10,11 RM_SDQS1 DQS1 D49 RM_MD49 10,11 DQS3 D51

RM_SDQS2 25 79 RM_MD50 RM_SDQS4 56 165 RM_MD52

10,11 RM_SDQS2 DQS2 D50 RM_MD50 10,11 DQS4 D52

RM_SDQS3 36 80 RM_MD51 RM_SDQS5 67 166 RM_MD53

10,11 RM_SDQS3 DQS3 D51 RM_MD51 10,11 DQS5 D53

RM_SDQS4 56 165 RM_MD52 RM_SDQS6 78 170 RM_MD54

10,11 RM_SDQS4 DQS4 D52 RM_MD52 10,11 DQS6 D54

RM_SDQS5 67 166 RM_MD53 RM_SDQS7 86 171 RM_MD55

10,11 RM_SDQS5 DQS5 D53 RM_MD53 10,11 DQS7 D55

RM_SDQS6 78 170 RM_MD54 47 83 RM_MD56

10,11 RM_SDQS6 DQS6 D54 RM_MD54 10,11 DQS8 D56

RM_SDQS7 86 171 RM_MD55 VCC2_5 84 RM_MD57

10,11 RM_SDQS7 DQS7 D55 RM_MD55 10,11 D57

47 83 RM_MD56 SMBDATA 91 87 RM_MD58

DQS8 D56 RM_MD56 10,11 SDA D58

84 RM_MD57 SMBCLK 92 88 RM_MD59

D57 RM_MD57 10,11 SCL D59

SMBDATA 91 87 RM_MD58 174 RM_MD60

6,15,18,19,20,26 SMBDATA SDA D58 RM_MD58 10,11 D60

SMBCLK 92 88 RM_MD59 181 175 RM_MD61

6,15,18,19,20,26 SMBCLK SCL D59 RM_MD59 10,11 SA0 D61

174 RM_MD60

RM_MD60 10,11 182 178 RM_MD62

D60 RM_MD61 SA1 D62 RM_MD63

181 SA0 D61 175 RM_MD61 10,11 183 SA2 D63 179

VCC2_5 182 178 RM_MD62 RM_MD62 10,11

SA1 D62 RM_MD63

183 SA2 D63 179 RM_MD63 10,11 1 VREF CB0 44

82 VDDID CB1 45

7 DDRVREF DDRVREF 1 44 184 49

VREF CB0 VDDSPD CB2

82 VDDID CB1 45 CB3 51

184 49 R272 9 134

VDDSPD CB2 49.9/1% NC CB4

CB3 51 10 NC CB5 135

9 134 DDRVREF 101 142

NC CB4 VCC2_5 NC CB6

10 NC CB5 135 102 NC CB7 144

101 NC CB6 142 173 NC

102 144 167 90

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

NC CB7 NC/FETEN WP

173 NC

C243 167 90

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

NC/FETEN WP

100

116

124

132

139

145

152

160

176

R273 C242

11

18

26

34

42

50

58

66

74

81

89

93

0.1uF DIMM_184P

3

100

116

124

132

139

145

152

160

176

49.9/1% 0.1uF

11

18

26

34

42

50

58

66

74

81

89

93

DIMM_184P

3

VCC2_5

DIMM DECOUPLING

1

+ CE42 + CE37 C244 C245 C246 C247 C248 C249 C250 C251 C252

100uF(NI) 100uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI)

2

Size Document Number Rev

A3 DIMM1&2 01

Date: Monday, August 19, 2002 Sheet 12 of 34

VCC3_3 +12V

VCC1_5

VCC3_3SBY

C110 RN16

+5V 7 8 G_STOP#

0.1uF VCC1_5 5 6 G_TRDY#

3 4 G_DEVSEL#

1 2 G_FRAME#

AGP

C125 C114 8.2K(NI)

AGP BUS

0.1uF(NI) 0.1uF(NI) RN9

7 8 G_WBF#

G_AD[31:0] B1 A1 5 6 G_PIPE#

8 G_AD[31:0] OVRCNT# 12V

B2 A2 3 4 G_RBF#

5.0V SPARE G_ST2

B3 5.0V RESERVED A3 1 2

G_SBA[7:0] B4 A4

8 G_SBA[7:0] USB+ USB-

B5 A5 8.2K(NI)

G_C_BE0 PIRQ#B GND GND PIRQ#A

8 G_C_BE0 B6 INTB# INTA# A6

G_C_BE1 AGPCLK_CONN B7 A7 PCIRST# R181

8 G_C_BE1 G_C_BE2 CLK RST#

G_REQ# B8 A8 G_GNT# 6.8K

8 G_C_BE2 REQ# GNT# G_PERR_R#

G_C_BE3 B9 A9

8 G_C_BE3 VCC3.3 VCC3.3

G_ST0 B10 A10 G_ST1

G_FRAME# G_ST2 ST0 ST1 R182

8 G_FRAME# B11 ST2 RESERVED A11

G_DEVSEL# G_RBF# B12 A12 G_PIPE# 6.8K

8 G_DEVSEL# RBF# PIPE#

8 G_IRDY# G_IRDY# B13 A13 G_SERR_R#

G_TRDY# GND GND G_WBF#

8 G_TRDY# B14 SPARE SPARE A14

8 G_STOP# G_STOP# G_SBA0 B15 A15 G_SBA1

G_PAR SBA0 SBA1

8 G_PAR B16 VCC3.3 VCC3.3 A16

8 G_REQ# G_REQ# G_SBA2 B17 A17 G_SBA3

G_GNT# G_SBSTB SBA2 SBA3 G_SBSTB#

8 G_GNT# B18 SB_STB RESERVED A18

8 G_PIPE# G_PIPE# B19 A19 R177

G_SBA4 GND GND G_SBA5 8.2K(NI)

B20 SBA4 SBA5 A20

G_ADSTB0 G_SBA6 B21 A21 G_SBA7 G_IRDY#

8 G_ADSTB0 SBA6 SBA7

8 G_ADSTB0# G_ADSTB0# B22 A22

G_ADSTB1 RESERVED RESERVED R191

8 G_ADSTB1 B23 GND GND A23

8 G_ADSTB1# G_ADSTB1# B24 A24 8.2K(NI)

G_SBSTB 3.3Vaux RESERVED G_ADSTB0

8 G_SBSTB B25 VCC3.3 VCC3.3 A25

8 G_SBSTB# G_SBSTB# G_AD31 B26 A26 G_AD30

G_AD29 AD31 AD30 G_AD28 R175

B27 AD29 AD28 A27

8 G_ST0 G_ST0 B28 A28 8.2K(NI)

G_ST1 G_AD27 VCC3.3 VCC3.3 G_AD26 G_ADSTB1

8 G_ST1 B29 AD27 AD26 A29

8 G_ST2 G_ST2 G_AD25 B30 A30 G_AD24

AD25 AD24 R156

B31 GND GND A31

8 G_RBF# G_RBF# G_ADSTB1 B32 A32 G_ADSTB1# 8.2K(NI)

G_WBF# G_AD23 AD_STB1 RESERVED G_C_BE3 G_SBSTB

8 G_WBF# B33 AD23 C/BE3# A33

B34 VDDQ1.5 VDDQ1.5 A34

AGPCLK_CONN G_AD21 B35 A35 G_AD22 R127

6 AGPCLK_CONN AD21 AD22

G_AD19 B36 A36 G_AD20 8.2K(NI)

PIRQ#A AD19 AD20 G_GNT#

14,20 PIRQ#A B37 GND GND A37

14,20 PIRQ#B PIRQ#B G_AD17 B38 A38 G_AD18

G_C_BE2 AD17 AD18 G_AD16 R132

B39 C/BE2# AD16 A39

19,20 PCIRST# PCIRST# B40 A40 8.2K(NI)

G_IRDY# VDDQ1.5 VDDQ1.5 G_FRAME# G_ST0

B41 IRDY# FRAME# A41

14,19,20 PCI_PME# PCI_PME#

R134

KEY 1.5V 8.2K(NI)

G_ST1

G_DEVSEL# B46 A46 G_TRDY#

DEVSEL# TRDY# G_STOP# R126

B47 VDDQ1.5 STOP# A47

G_PERR_R# B48 A48 PCI_PME# 8.2K(NI)

PERR# SPARE G_REQ#

B49 GND GND A49

G_SERR_R# B50 A50 G_PAR

G_C_BE1 SERR# PAR G_AD15 R185

B51 C/BE1# AD15 A51

B52 A52 8.2K(NI)

G_AD14 VDDQ1.5 VDDQ1.5 G_AD13 G_PAR

B53 AD14 AD13 A53

G_AD12 B54 A54 G_AD11

AD12 AD11 R188

B55 GND GND A55

VCC1_5 G_AD10 B56 A56 G_AD9 8.2K(NI)

G_AD8 AD10 AD9 G_C_BE0 G_ADSTB0#

B57 AD8 C/BE0# A57

B58 VDDQ1.5 VDDQ1.5 A58

G_ADSTB0 B59 A59 G_ADSTB0# R169

G_AD7 AD_STB0 RESERVED G_AD6 8.2K(NI)

B60 AD7 AD6 A60

B61 A61 G_ADSTB1#

R207 G_AD5 GND GND G_AD4

B62 AD5 AD4 A62

G_AD3 B63 A63 G_AD2 R149

1K/1% AD3 AD2 8.2K(NI)

B64 VDDQ1.5 VDDQ1.5 A64

G_AD1 B65 A65 G_AD0 G_SBSTB#

VREF_AGP_MCH AD1 AD0

8 VREF_AGP_MCH B66 RESERVED RESERVED A66

R206 C200

1K/1% 0.1uF AGP124/1.5V

VCC1_5 VCC3_3

1

C168 C148 C193 C159 + CE34 C138 C126 C124

0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI) 100uF(NI) 0.1uF(NI) 0.1uF(NI) 0.1uF(NI)

2

Size Document Number Rev

A3 AGP CONNECTOR 01

Date: Monday, August 19, 2002 Sheet 13 of 34

ICH4 PART1 R263 68 H_A20M# H_A20M# 4

VCC3_3

R230 68 H_SLP# H_SLP# 4

RN12

1 2 FRAME#

3 4 IRDY# R257 68 H_IGNNE# H_IGNNE# 4

5 6 TRDY# VCORE

7 8 DEVSEL#

8.2K R253 68 H_INIT# H_INIT# 4,17

RN14 U12A

1 2 STOP# R271

3 4 PERR# 19,20 AD[31:0] AD[31:0]

ICH4

5 6 SERR# AD0 H5 62 R264 68 H_INTR H_INTR 4

AD0

7 8 PLOCK# AD1 J3 AD1

AD2 H3 AD2

8.2K AD3 K1

RN19 AD3 RH_A20M# R254 68 H_NMI

AD4 G5 AB23 H_NMI 4

PREQ#3 AD4 A20M# RH_SLP#

8 7 AD5 J4 AD5 CPUSLP# U21

6 5 PIRQ#F AD6 H4 AA21 H_FERR# H_FERR# 4

AD6 FERR# RH_IGNNE#

4 3 PREQ#5 AD7 J5 AD7 IGNNE# W21

2 1 PREQ#4 AD8 K2 V22 RH_INIT# R258 68 H_SMI# H_SMI# 4

AD8 INIT# RH_INTR

AD9 G2 AD9 INTR AB22

8.2K AD10 L1 V21 RH_NMI

AD10 NMI

CPU

RN21 AD11 G4 W23 RH_SMI#

P_REQ#A AD11 SMI# RH_STPCLK# R231 68 H_STPCLK#

8 7 AD12 L2 AD12 STPCLK# V23 H_STPCLK# 4

6 5 PIRQ#A AD13 H2 U22 RCIN# RCIN# 18

PIRQ#H AD13 RCIN# A20GATE

4 3 AD14 L3 Y22 A20GATE 18

PIRQ#D AD14 A20GATE RH_PWRGD

2 1 AD15 F5 AD15 CPUPWRGD Y23

AD16 F4 U23 R260 68 H_PWRGD H_PWRGD 4

8.2K AD16 DPSLP#

AD17 N1 AD17

AD18 E5 AD18 HI[10:0]

AD19 N2 AD19 HI[10:0] 7

AD20 E3 L19 HI0

AD20 HI0 HI1 VCC1_5

AD21 N3 L20

AD21 HI1 HI2

AD22 E4 AD22 HI2 M19 Place R

AD23 M5 M21 HI3 as close as

AD23 HI3 HI4

AD24 E2 P19 possible to ICH2.

AD24 HI4 HI5

AD25 P1 AD25 HI5 R19

AD26 E1 T20 HI6 R225

AD26 HI6 HI7

AD27 P2 AD27 HI7 R20

AD28 D3 P23 HI8 68.1/1%

AD28 HI8 HI9

AD29 R1 L22

HUB

AD29 HI9

PCI

AD30 D2 N22 HI10

AD30 HI10 R224 62

AD31 P4 K21

AD31 HI11

HI_STB/HI_STBS P21 HI_STBS 7

19,20 C_BE#0 C_BE#0 J2 N20 HI_STBF 7

C_BE#1 C_BE#0 HI_STB#/HI_STBF

19,20 C_BE#1 K4 C_BE#1 HICOMP R23

19,20 C_BE#2 C_BE#2 M4 M23 HUBREF_A 7,9

C_BE#3 C_BE#2 HIREF

19,20 C_BE#3 N4 C_BE#3 HI_VSWING R22 HI_VSWING 7,9

19,20 DEVSEL# DEVSEL# M3

FRAME# DEVESLE# PIRQ#A

19,20 FRAME# F1 FRAME# PIRQA# D5 PIRQ#A 13,20

19,20 IRDY# IRDY# L5 C2 PIRQ#B

IRDY# PIRQB# PIRQ#B 13,20

19,20 TRDY# TRDY# F2 B4 PIRQ#C VCC3_3

TRDY# PIRQC# PIRQ#C 20

19,20 STOP# STOP# F3 A3 PIRQ#D

STOP# PIRQD# PIRQ#D 20

19,20 PAR PAR G1

ICHRST# PAR PIRQ#E

U5 AC13 R106 8.2K

IRQ

PCIRST# IRQ14 IRQ14 21

VCC3_3SBY 19,20 PLOCK# PLOCK# M2 AA19

PLOCK# IRQ15 IRQ15 21

19,20 SERR# SERR# K5 J19 RCIN# R227 8.2K

PERR# SERR# APICCLK APICD0

19,20 PERR# L4 PERR# APICD0 H19

13,19,20 PCI_PME# W2 K20 APICD1 A20GATE R261 8.2K

R255 8.2K LAN_DISABLE P_REQ#A PME# APICD1 SERIRQ

B5 GPIO0/REQA# SERIRQ J22 SERIRQ 18

E8 SERIRQ R223 8.2K

R251 8.2K GPIO12 C231 33pF(NI) GPIO16/GNTA#

6 PCICLK_ICH4 P5 R220

PCICLK PIRQ#C R100 8.2K

R252 8.2K GPIO13 10K

19 PIRQ#E PIRQ#E C8 B1 PREQ#0 PIRQ#B R87 8.2K

GPIO2/PIRQE# REQ#0 PREQ#0 20

R228 8.2K LPC_PME# 19 PIRQ#F PIRQ#F D7 A2 PREQ#1

GPIO3/PIRQF# REQ#1 PREQ#1 19

19 PIRQ#G PIRQ#G C3 B3 PREQ#2

GPIO4/PIRQG# REQ#2 PREQ#2 19

19 PIRQ#H PIRQ#H C4 C7 PREQ#3

GPIO7 GPIO5/PIRQH# REQ#3 PREQ#4

R3 GPIO7 REQ#4 B6

18 LPC_PME# LPC_PME# V4 A6 PREQ#5 RN20

GPIO12 GPIO8 GPIO1/REQB#/REQ#5 PIRQ#G

V5 GPIO12 1 2

GPIO13 W3 C1 PGNT#0 PREQ#0 3 4

GPIO13 GNT#0 PGNT#0 20

V2 E6 PGNT#1 PREQ#1 5 6

GPIO25 GNT#1 PGNT#1 19

W1 A7 PGNT#2 PREQ#2 7 8

GPIO27 PGNT#2 19

PCI

LAN_DISABLE W4 GNT#2

15 LAN_DISABLE B7

GPIO

GPIO28 GNT#3 8.2K

17 GPIO32 J20 GP1O32 GNT#4 D6

G22 GP1O33 GPIO17/GNTB#/GNT#5 C5

F20 AC2 RN22

GP1O34 CLKRUN#/GPIO24

G20 GP1O35 2 1

F21 15 GPIO6 GPIO6 4 3

GP1O36 GPIO7

H20 GP1O37 LAN_RXD0 A10 CNR_RXD0 26 6 5

F23 A9 15,18 LDRQ#0 LDRQ#0 8 7

GP1O38 LAN_RXD1 CNR_RXD1 26

H22 GP1O39 LAN_RXD2 A11 CNR_RXD2 26

G23 B10 2.7K

GP1O40 LAN_TXD0 CNR_TXD0 26

H21 C10 CNR_TXD1 26

LAN

GP1O41 LAN_TXD1

F22 GP1O42 LAN_TXD2 A12 CNR_TXD2 26

VCC3_3 E23

+5V GP1O43

LAN_CLK C11 CNR_CLK 26

LAN_RSTSYNC B11 CNR_RSTSYNC 26

R306 U13A

82801DB

14

1K BGA421

2 1 ICHRST#

8,17,18,20,21 HPCIRST#

C236

7407

7

10pF(NI)

Size Document Number Rev

A3 ICH4 PART1 01

Date: Monday, August 19, 2002 Sheet 14 of 34

ICH4 PART2 VCC3_3

R277 10K VRMPG

R268 2.7K SMBCLK

33 RST_SW# R311 0 SYSRST#

R267 2.7K SMBDATA

R266 4.7K LPCPD# 6,31,33 VRM_PWRGD R276 0 VRMPG

R226 8.2K THERM#

VCC3_3SBY

R265 10K BATLOW#

U12B

R229 8.2K LDRQ#1

R256 8.2K SYSRST# T2 B13 AC_SDIN2 26

17,18 LAD0/FWH0 LAD0/FWH0 AC_SDIN2

17,18 LAD1/FWH1 R4 LAD1/FWH1 AC_SDIN1 A13 AC_SDIN1 26

AC97

R259 4.7K LPCPWRON T4 D13 AC_SDIN0 26,29

17,18 LAD2/FWH2 LAD2/FWH2 AC_SDIN0

LPC

17,18 LAD3/FWH3 U2 LAD3/FWH3 AC_SDOUT D9 AC_SDOUT 26,29

14,18 LDRQ#0 U3 LDRQ0# AC_BIT_CLK B8 AC_BITCLK 26,29

LDRQ#1 U4 LDRQ1# AC_SYNC C9 AC_SYNC 26,29

17,18 LFRAME#/FWH4 T5 LFRAME#/FWH4 AC_RST# C13 AC_RST# 26

R270 22K PWROK

22 USBP0P C20 USBP0+ PDCS1# Y13 PDCS#1 21

22 USBP0N D20 USBP0- SDCS1# AB21 SDCS#1 21

22 USBP1P A21 USBP1+ PDCS3# AB14 PDCS#3 21

22 USBP1N B21 USBP1- SDCS3# AC22 SDCS#3 21

22 USBP2P C18 USBP2+

22 USBP2N D18 USBP2- PDA[2:0] 21

22 USBP3P A19 AA13 PDA0

USBP3+ PDA0 PDA1

22 USBP3N B19 USBP3- PDA1 AB13

USB

5VSBY VCCRTC 22 USBP4P C16 W13 PDA2 SDA[2:0] 21

USBP4+ PDA2 SDA0

22 USBP4N D16 USBP4- SDA0 AA20

22 USBP5P A17 AC20 SDA1

USBP5+ SDA1 SDA2

22 USBP5N B17 USBP5- SDA2 AC21

R282 22 OC#1 B15 OC0#

1K C14 OC1#

D17

22 OC#2 A15 OC2# PDDREQ AA11 PDREQ 21

1 2 B14 OC3# SDDREQ AB18 SDREQ 21

22 OC#3 A14

D14

OC4#

OC5#

ICH4 PDDACK#

SDDACK#

Y12

AB19

PDDACK#

SDDACK#

21

21

R283 1N4148 C255 R217 A23 AC12

USBRBIAS PDIOR# PDIOR# 21

4.7K B23 USBRBIAS# SDIOR# Y18 SDIOR# 21

1uF W12

PDIOW# PDIOW# 21

22.6/1% AA18

SDIOW# SDIOW# 21

EEPROM

26 CNR_EE_CS D10 EE_CS PIORDY AB12 PIORDY 21

26 CNR_EE_DIN D11 EE_DIN SIORDY AC19 SIORDY 21

26 CNR_EE_DOUT A8 EE_DOUT

26 CNR_EE_SHCLK C12 EE_SHCLK PDD[15:0] 21

AB11 PDD0

PDD0 PDD1

PDD1 AC11

THERM# V1 Y10 PDD2

18 THERM# THRM# PDD2

4 THERMTRIP# W20 AA10 PDD3

R269 JP8 THRMTRIP# PDD3 PDD4

W18 SLP_S1#/GPIO19 PDD4 AA7

1 Y4 AB8 PDD5

18 SLP_S3# SLP_S3# PDD5

IDE

2 R290 Y2 Y8 PDD6

8.2K SLP_S4# PDD6 PDD7

3 AA2 SLP_S5# PDD7 AA8

R289 330K 8,33 PWROK PWROK AB6 AB9 PDD8

SYSRST# PWROK PDD8 PDD9

1K Y3 SYS_RESET# PDD9 Y9

LPCPWRON AA1 AC9 PDD10

18 LPCPWRON PWRBTN# PDD10

R284 24 ICH_RI# Y1 W9 PDD11

C240 RI# PDD11 PDD12

18 RSMRST# AA6 PDD12 AB10

2

2.2uF 1K LPCPD# RSMRST# PDD13

AB3 SUS_STAT#/LPCPD# PDD13 W10

D18 18 SUSCLK AA4 W11 PDD14

SMBDATA SUSCLK PDD14 PDD15

1N5817 6,12,18,19,20,26 SMBDATA AB4 SMBDATA PDD15 Y11

6,12,18,19,20,26 SMBCLK SMBCLK AC4 SMBCLK

33 EXTSMI# AA5 GPIO11/SMBALERT# SDD[15:0] 21

R291 LAN_DISABLE SDD0

1

14 LAN_DISABLE Y5 LAN_RST# SDD0 W17

T3 AB17 SDD1

18 VBAT VRMPG V19

C3_STAT#/GPIO21 SDD1

W16 SDD2

1K C259 GPIO6 VRMPWRGD/VGATE SDD2 SDD3

14 GPIO6 R2 AGPBUSY#/GPIO6 SDD3 AC16

SYSTEM

Y21 W15 SDD4

0.047uF STP_PCI#/GPIO18 SDD4 SDD5

W19 AB15

1

BATLOW# STP_CPU#/GPIO20 SDD5 SDD6

AB2 BATLOW#/TP0 SDD6 W14

BT1 Y20 AA14 SDD7

CPUPERF#/GPIO22 SDD7 SDD8

CR2032 J21 SSMUXSEL/GPIO23 SDD8 Y14

R292 V20 AC15 SDD9

DPRSLPVR SDD9 SDD10

2

10M W6 INTRUDER# SDD10 AA15

AC3 Y15 SDD11

SMLINK0 SDD11 SDD12

AB1 SMLINK1 SDD12 AB16

AC7 Y16 SDD13

RTCX1 SDD13 SDD14

AC6 RTCX2 SDD14 AA17

VIBAS Y6 Y17 SDD15

R262 RTCRST# VIBAS SDD15

W7 RTCRST#

33 ICH_SPKR H23 SPKR

6 ICH4_CLK14 J23 CLK14

10M 6 USBCLK F19

Y3 CLK48

6 ICH4_3V66 T21 CLK66

82801DB

C257 C256 C233 BGA421

32.768KHz

18pF 18pF 18pF(NI)

Size Document Number Rev

A3 ICH4 PART2 01

Date: Monday, August 19, 2002 Sheet 15 of 34

ICH4 PART3

VCC3_3 VCC3_3SBY

VCC1_5SBY

C241

0.1uF(NI)

VCC1_5

U12C

K10

K12

VCC1_5

VCC1_5

ICH4 GND

GND

C21

C23

K18 VCC1_5 GND C6

K22 VCC1_5 GND D1

P10 VCC1_5 GND D12

T18 VCC1_5 GND D15

U19 VCC1_5 GND D17

C150 V14 VCC1_5 GND D19

GND D21

0.1uF(NI) E12 D23

VCCSUS1_5 GND

E13 VCCSUS1_5 GND D4

E20 VCCSUS1_5 GND D8

F14 VCCSUS1_5 GND D22

G18 VCCSUS1_5 GND E10

R6 VCCSUS1_5 GND E14

T6 VCCSUS1_5 GND E16

U6 VCCSUS1_5 GND E17

GND E18

A5 VCC3_3 GND E19

AC17 VCC3_3 GND E21

C196 AC8 VCC3_3 GND E22

B2 VCC3_3 GND F8

0.1uF H18 G19

VCC3_3 GND

H6 VCC3_3 GND G21

+5V J1 G3

VCC3_3 GND

J18 VCC3_3 GND G6

K6 VCC3_3 GND H1

C258 0.1uF(NI) M10 J6

VCC3_3 GND

P12 VCC3_3 GND K11

P6 VCC3_3 GND K13

U1 VCC3_3 GND K19

V10 VCC3_3 GND K23

V16 VCC3_3 GND K3

V18 VCC3_3 GND L10

GND L11

E11 VCCSUS3_3 GND L12

F10 VCCSUS3_3 GND L13

F15 VCCSUS3_3 GND L14

C203 F16 VCCSUS3_3 GND L21

F17 VCCSUS3_3 GND M1

0.1uF F18 VCCSUS3_3 GND M11

K14 VCCSUS3_3 GND M12

V7 VCCSUS3_3 GND M13

V8 VCCSUS3_3 GND M20

V9 VCCSUS3_3 GND M22

GND N10

A1 GND GND N11

A16 GND GND N12

A18 N13 VCC3_3 +5V

GND GND

A20 GND GND N14

A22 GND GND N19

A4 GND GND N21 Distribute near the VCCSUS

1

AA12 N23 D15 power pins of the ICH.

GND GND

AA16 GND GND N5

AA22 P11 R193

GND GND

AA3 GND GND P13

AA9 P20 1N5817 1K

GND GND

2

AB20 GND GND P22

AB7 GND GND P3

AC1 R18 ICH5VREF

GND GND

AC10 GND GND R21

AC14 GND GND R5

AC18 GND GND T1

VCCLAN1_5/VCCSUS1_5

VCCLAN1_5/VCCSUS1_5

VCCLAN3_3/VCCSUS3_3

VCCLAN3_3/VCCSUS3_3

AC23 GND GND T19

AC5 T23 C195 C189

GND GND 0.1uF 1uF(NI)

B12 GND GND U20

B16 GND GND V15

B18 GND GND V17

B20 GND GND V3

E15 V5REF_SUS

B22 GND GND W22

AA23V_CPU_IO

P14 V_CPU_IO

U18 V_CPU_IO

B9 W5

AB5 VCCRTC

GND GND

C22 VCCPLL

C15 W8

E7 V5REF

V6 V5REF

VCCHI

VCCHI

VCCHI

VCCHI

GND GND

C17 GND GND Y19

C19 GND GND Y7

M14

P18

T22

L23

82801DB

E9

F6

F7

F9

BGA421

5VSBY

VCORE

VCCRTC VCC1_5

C239 C238 C234 C227

0.1uF 0.1uF 0.1uF(NI) 0.01uF(NI)

Size Document Number Rev

A3 ICH4 PART3 01

Date: Monday, August 19, 2002 Sheet 16 of 34

FirmWare Hub (FWH) Socket VCC3_3 Distribute close to

each power pin

VCC3_3

NOTE: This is a Socketed Implementation C303

0.1uF(NI)

RX5

NC-4.7K

6 PCICLKFWH

8,14,18,20,21 HPCIRST#

VCC3_3

RX6

VCC3_3 NC-4.7K

R344 C301

32

31

30

U16 0.1uF(NI)

1

470

VCC

VPP

CLK

RST#

FGPI2

FGPI3

FGPI4

5 29

21 S66DETECT FGPI1 IC

6 28 VCC3_3 +5V

21 P66DETECT FGPI0 GNDA

7 WP# VCCA 27

R348

8 26 R323 R349

14 GPIO32

0(NI) 9

TBL#

ID3

FWH GND

VCC 25

300 4.7K

R343 R341 10 SST49LF002A 24

ID2 INIT#

2

10K 10K 11 23 Q17

ID1 FWH4

1

12 22 Q22

ID0 RFU

2

R350

3904

3

13 21 1

FWH0 RFU H_INIT# 4,14

FWH1

FWH2

FWH3

3904

GND

RFU

RFU

RFU

4.7K

3

14

15

16

17

18

19

20

15,18 LAD0/FWH0

15,18 LAD1/FWH1

15,18 LAD2/FWH2

15,18 LAD3/FWH3

15,18 LFRAME#/FWH4

Size Document Number Rev

A4 FWH 01

Date: Monday, August 19, 2002 Sheet 17 of 34

IRRX

IRTX

R21 220

6,12,15,19,20,26 SMBDATA RI#1 24

VCC3_3

DCD#1 24

R20 220

6,12,15,19,20,26 SMBCLK TXD1 24

-5VIN

RXD#1 24

-12VIN

DTR#1 24 IR

+12VIN

RTS#1 24

+3.3VIN 1

DSR#1 24

+5.0VIN

CTS#1 24

VCORE_IN R2 10K 2

5VSBY

HM_VREF

SUSCLK 15

VTIN3 IRRX 3

SLP_S3# 15

R3 10K

5VSBY

FB1 0 HMAVCC 4

+5V PSON# 33

C8 IRTX 5

LPCPWROK 33

R4 10K

VCC3_3SBY

0.1uF

RSMRST# 15

FB2 0 HMAGND

C93 C90 C80

PWRBTN# 33

15 VBAT

470pF 470pF 0.1uF

LPCPWRON 15

+5V

MDAT 25

MCLK 25

102

101

100

U2

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

Temperature Sensing

-5VIN

RIB#

SINB

VTIN3

+3.3VIN

-12VIN

+12VIN

IRRX/GP25

IRTX/GP26

PSIN#

SUSCLKIN

SUSCIN/GP30

CIRRX/GP34

SCL/GP21

SDA/GP22

PLED/GP23

VREF

VCOREA

VCOREB

AVCC

AGND

VSS

DCDB#

SOUTB

DTRB#

RTSB#

DSRB#

CTSB#

VCC

CASEOPEN#

VBAT

RSMRST#/GP33

PSOUT#

MDAT

MCLK

WDTO/GP24

PWRCTL#/GP31

PWROK/GP32

VTIN2 103 64

VTIN1 VTIN2 SUSLED/GP35

104 VTIN1 KDAT 63 KDAT 25

15 THERM# 105 OVT# KCLK 62 KCLK 25

3,31 CPUVID4 106 VID4 VSB 61 5VSBY

107 60 R9 10K/1% HM_VREF

3,31 CPUVID3 VID3 KBRST RCIN# 14 FOR SYSTEM

3,31 CPUVID2 108 VID2 GA20M 59 A20GATE 14

3,31 CPUVID1 109 VID1 KBLOCK# 58 KEYLOCK# 33

110 57 VTIN1 RT1 10K(THRM) HMAGND

T¢X

3,31 CPUVID0 VID0 RIA# RI#0 24

FAN_TAC3 111 56

FANIO3 DCDA# DCD#0 24

FAN_TAC2 112 55

FAN_TAC1 FANIO2 VSS

113 FANIO1 SOUTA 54 TXD0 24

114 53 R10 30K HM_VREF

VCC SINA RXD#0 24 FOR CPU

115 FANPWM2 DTRA# 52 DTR#0 24

116 FANPWM1 RTSA# 51 RTS#0 24

117 50 VTIN2 C4 3300pF HMAGND

VSS DSRA# DSR#0 24 4 THRMDP

33 BEEP 118 BEEP CTSA# 49 CTS#0 24

27 MIDI_IN 119 MSI/GP20 VCC 48 +5V 4 THRMDN

27 MIDI_OUT 120 47 STROBE# 23

27 J1BUTTON2 121

MSO/IRQIN0

GPSA2/GP17

W83627HF STB#

AFD# 46 ALF# 23

27 J2BUTTON2 122 GPSB2/GP16 ERR# 45 ERROR# 23

123 44 R11 10K/1% HM_VREF

27 JOY1Y GPY1/GP15 INIT# PAR_INIT# 23 FOR OPTION

27 JOY2Y 124 GPY2/P16/GP14 SLIN# 43 SLCTIN# 23

27 JOY2X 125 GPX2/P15/GP13 PD0 42

DSKCHG#

DRVDEN0

DRVDEN1

LFRAME#

VTIN3 HMAGND

LRESET#

27 JOY1X 126 41

RDATA#

GPX1/P14/GP12 PD1

SERIRQ

TRAK0#

INDEX#

PCICLK

127 40

HEAD#

LDRQ#

VCC3V

STEP#

27 J2BUTTON1

CLKIN

GPSB1/P13/GP11 PD2

MOA#

MOB#

PME#

BUSY

DSB#

DSA#

ACK#

SLCT

LAD3

LAD2

LAD1

LAD0

128 39

WD#

DIR#

WE#

WP#

VCC

VSS

PD7

PD6

PD5

PD4

27 J1BUTTON1 GPSA1/P12/GP10 PD3

PE

2

PDR0 23

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

FDD Signals Trace 8 or 10 mil PDR1 23

W83627HF

1

2

3

4

5

6

7

8

9

PDR2 23

FDC

PDR3 23 RT2

1 2 RWC#

PDR4 23

3 4 PDR5 23

5 6 DS1#

PDR6 23

7 8 INDEX#

PDR7 23

9 10 MOA#

ACK# 23

11 12 DSB#

BUSY 23

13 14 DSA#

15 16 MOB#

PE

SLCT#

23

23

Voltage Sensing

17 18 DIR#

19 20 STEP#

HPCIRST# 8,14,17,20,21

21 22 WD#

+5V

23 24 WE#

25 26 TRAK0# R1 10K/1% VCORE_IN

VCC3_3 VCORE

27 28 WP#

29 30 RDATA#

31 32 HEAD# R13 10K/1% +3.3VIN

DSKCHG# VCC3_3

33 34

+5V

R12 10K/1% +5.0VIN

+5V

6 SIO_CLK48

14 LPC_PME#

R15 28K/1% +12VIN

6 PCICLK_LPC +12V

14,15 LDRQ#0

C29 C99 C175

14 SERIRQ

HMAGND R14 10K/1%

15,17 LAD3/FWH3

0.1uF(NI) 0.1uF(NI) 0.1uF(NI)

15,17 LAD2/FWH2

15,17 LAD1/FWH1

R16 232K/1% -12VIN

15,17 LAD0/FWH0 -12V

15,17 LFRAME#/FWH4

HM_VREF R17 56K/1%

C73

+5V 22pF(NI) +5V +5V R19 120K/1% -5VIN

-5V

+12V +12V +12V HM_VREF R18 56K/1%

2

D5 R77 D8 R95 2 D19 R303

1N4148 1K 1N4148 1K 1N4148 1K

CPUFAN PWRFAN CHSFAN

FAN_TAC1 FAN_TAC2 FAN_TAC3

1

3 3 3

2 2 2

1 C88 1 C92 1 C264

0.1uF 0.1uF 0.1uF

Size Document Number Rev

A3 LPC&FDC 01

Date: Monday, August 19, 2002 Sheet 18 of 34

PCI CONNECTORS

1 AND 2

VCC3_3 VCC3_3 VCC3_3SBY VCC3_3 VCC3_3

-12V +5V -12V +5V VCC3_3SBY

+5V +12V +5V

+12V

PCI2 PCI1

B1 -12V TRST# A1 B1 -12V TRST# A1

B2 TCK +12V A2 B2 TCK +12V A2

B3 GND TMS A3 B3 GND TMS A3

B4 TDO TDI A4 B4 TDO TDI A4

B5 +5V +5V A5 B5 +5V +5V A5

B6 A6 PIRQ#F B6 A6 PIRQ#G

PIRQ#G +5V INTA# PIRQ#H PIRQ#F 14 PIRQ#H +5V INTA# PIRQ#E

14 PIRQ#G PIRQ#E

B7 INTB# INTC# A7

PIRQ#H 14 PIRQ#F

B7 INTB# INTC# A7

B8 A8 B8 A8

14 PIRQ#E B9

INTD# +5V

A9 B9

INTD# +5V

A9

PRSNT1# RESERVED PRSNT1# RESERVED

B10 RESERVED +5V A10 B10 RESERVED +5V A10

B11 PRSNT2# RESERVED A11 B11 PRSNT2# RESERVED A11

B12 GND GND A12 B12 GND GND A12

B13 GND GND A13 B13 GND GND A13

B14 RESERVED 3.3V AUX A14 B14 RESERVED 3.3V AUX A14

B15 A15 PCIRST# B15 A15

B16

GND RST#

A16 B16

GND RST#

A16

PCIRST# 13,20

6 PCICLK2 B17

CLK +5V

A17

6 PCICLK3 B17

CLK +5V

A17

B18

GND GNT#

A18

PGNT#1 14 B18

GND GNT#

A18

PGNT#2 14

14 PREQ#1 B19

REQ# GND

A19 PCI_PME# 14 PREQ#2 B19

REQ# GND

A19 PCI_PME#

AD31 B20

+5V PME#

A20 AD30 AD31 B20

+5V PME#

A20 AD30 PCI_PME# 13,14,20

AD29 AD31 AD30 AD29 AD31 AD30

B21 AD29 +3.3V A21 B21 AD29 +3.3V A21

B22 A22 AD28 B22 A22 AD28

AD27 GND AD28 AD26 AD27 GND AD28 AD26

B23 AD27 AD26 A23 B23 AD27 AD26 A23

AD25 B24 A24 AD24 AD25 B24 A24 AD24

AD25 GND R130 AD25 GND R129

B25 +3.3V AD24 A25 B25 +3.3V AD24 A25

C_BE#3 B26 A26 R_AD17 AD17 C_BE#3 B26 A26 R_AD18 AD18

C/BE3# IDSEL C/BE3# IDSEL

B27 AD23 +3.3V A27 B27 AD23 +3.3V A27

AD23 B28 A28 AD22 100 AD23 B28 A28 AD22 100

AD21 GND AD22 AD20 AD21 GND AD22 AD20

B29 AD21 AD20 A29 B29 AD21 AD20 A29

AD19 B30 A30 AD19 B30 A30

AD19 GND AD18 AD19 GND AD18

B31 +3.3V AD18 A31 B31 +3.3V AD18 A31

AD17 B32 A32 AD16 AD17 B32 A32 AD16

C_BE#2 AD17 AD16 C_BE#2 AD17 AD16

B33 C/BE2# +3.3V A33 B33 C/BE2# +3.3V A33

B34 A34 FRAME# B34 A34 FRAME#

IRDY# B35

GND FRAME#

A35 IRDY# B35

GND FRAME#

A35

FRAME# 14,20

14,20 IRDY# B36

IRDY# GND

A36 TRDY# B36

IRDY# GND

A36 TRDY#

B37

+3.3V TRDY#

A37 DEVSEL# B37

+3.3V TRDY#

A37

TRDY# 14,20

14,20 DEVSEL# B38

DEVSEL# GND

A38 STOP# B38

DEVSEL# GND

A38 STOP#

B39

GND STOP#

A39 PLOCK# B39

GND STOP#

A39

STOP# 14,20

14,20 PLOCK# B40

LOCK# +3.3V

A40 SMBCLK PERR# B40

LOCK# +3.3V

A40 SMBCLK

14,20 PERR# B41

PERR# SDONE

A41 SMBDATA B41

PERR# SDONE

A41 SMBDATA SMBCLK 6,12,15,18,20,26

B42

+3.3V SBO#

A42 SERR# B42

+3.3V SBO#

A42

SMBDATA 6,12,15,18,20,26

14,20 SERR# B43

SERR# GND

A43 PAR B43

SERR# GND

A43 PAR

C_BE#1 B44

+3.3V PAR

A44 AD15 C_BE#1 B44

+3.3V PAR

A44 AD15 PAR 14,20

C/BE1# AD15 C/BE1# AD15

B45 AD14 +3.3V A45 B45 AD14 +3.3V A45

AD14 B46 A46 AD13 AD14 B46 A46 AD13

AD12 GND AD13 AD11 AD12 GND AD13 AD11

B47 AD12 AD11 A47 B47 AD12 AD11 A47

AD10 B48 A48 AD10 B48 A48

AD10 GND AD9 AD10 GND AD9

B49 GND AD9 A49 B49 GND AD9 A49

AD8 B52 A52 C_BE#0 AD8 B52 A52 C_BE#0

AD7 AD8 C/BE0# AD7 AD8 C/BE0#

B53 AD7 +3.3V A53 B53 AD7 +3.3V A53

B54 A54 AD6 B54 A54 AD6

AD5 +3.3V AD6 AD4 AD5 +3.3V AD6 AD4

B55 AD5 AD4 A55 B55 AD5 AD4 A55

AD3 B56 A56 AD3 B56 A56

AD3 GND AD2 AD3 GND AD2

B57 GND AD2 A57 B57 GND AD2 A57

AD1 B58 A58 AD0 AD1 B58 A58 AD0

AD1 AD0 AD1 AD0

B59 +5V +5V A59 B59 +5V +5V A59

ACK64#2 B60 A60 REQ64#2 ACK64#3 B60 A60 REQ64#3

ACK64# REQ64# ACK64# REQ64#

B61 +5V +5V A61 B61 +5V +5V A61

B62 +5V +5V A62 B62 +5V +5V A62

PCI_CON PCI_CON

14,20 C_BE#[3:0]

14,20 AD[31:0]

VCC3_3

RN18A1 8 2.7K ACK64#3

RN18B2 7 2.7K REQ64#2

RN18C3 6 2.7K ACK64#2

RN18D4 5 2.7K REQ64#3 Size Document Number Rev

A3 PCI 1 , 2 01

Date: Monday, August 19, 2002 Sheet 19 of 34

PCI CONNECTORS 3

VCC3_3 VCC3_3 VCC3_3SBY

-12V +5V

+5V +12V

PCI3

B1 -12V TRST# A1

B2 TCK +12V A2

B3 GND TMS A3

B4 TDO TDI A4

B5 +5V +5V A5

B6 A6

+5V INTA# PIRQ#A 13,14

13,14 PIRQ#B B7 INTB# INTC# A7

PIRQ#C 14

B8 A8

14 PIRQ#D B9

INTD# +5V

A9

PRSNT1# RESERVED

B10 RESERVED +5V A10

B11 PRSNT2# RESERVED A11

B12 GND GND A12

B13 GND GND A13

B14 RESERVED 3.3V AUX A14

B15 A15

B16

GND RST#

A16

PCIRST# 13,19

6 PCICLK1 B17

CLK +5V

A17

B18

GND GNT#

A18

PGNT#0 14

14 PREQ#0 B19

REQ# GND

A19

AD31 B20

+5V PME#

A20 AD30 PCI_PME# 13,14,19

AD29 AD31 AD30

B21 AD29 +3.3V A21

B22 A22 AD28 C107

AD27 GND AD28 AD26

B23 AD27 AD26 A23

AD25 B24 A24 AD24 47pF(NI)

AD25 GND R131

B25 +3.3V AD24 A25

C_BE#3 B26 A26 R_AD16 AD16

C/BE3# IDSEL

B27 AD23 +3.3V A27

AD23 B28 A28 AD22 100

AD21 GND AD22 AD20

B29 AD21 AD20 A29

AD19 B30 A30

AD19 GND AD18

B31 +3.3V AD18 A31

AD17 B32 A32 AD16

C_BE#2 AD17 AD16

B33 C/BE2# +3.3V A33

B34 A34

B35

GND FRAME#

A35

FRAME# 14,19

14,19 IRDY# B36

IRDY# GND

A36

B37

+3.3V TRDY#

A37

TRDY# 14,19

14,19 DEVSEL# B38

DEVSEL# GND

A38

B39

GND STOP#

A39

STOP# 14,19

14,19 PLOCK# B40

LOCK# +3.3V

A40

14,19 PERR# B41

PERR# SDONE

A41

SMBCLK 6,12,15,18,19,26

B42

+3.3V SBO#

A42

SMBDATA 6,12,15,18,19,26

14,19 SERR# B43

SERR# GND

A43

C_BE#1 B44

+3.3V PAR

A44 AD15 PAR 14,19

C/BE1# AD15

B45 AD14 +3.3V A45

AD14 B46 A46 AD13

AD12 GND AD13 AD11

B47 AD12 AD11 A47

AD10 B48 A48

AD10 GND AD9

B49 GND AD9 A49

AD8 B52 A52 C_BE#0

AD7 AD8 C/BE0#

B53 AD7 +3.3V A53

B54 A54 AD6

AD5 +3.3V AD6 AD4

B55 AD5 AD4 A55

AD3 B56 A56

AD3 GND AD2

B57 GND AD2 A57

AD1 B58 A58 AD0

AD1 AD0

B59 +5V +5V A59

ACK64#1 B60 A60 REQ64#1

ACK64# REQ64#

B61 +5V +5V A61

B62 +5V +5V A62

PCI_CON

14,19 C_BE#[3:0]

14,19 AD[31:0]

VCC3_3

+5V

VCC3_3

R307

1K R180 2.7K ACK64#1

U13B

3 4 PCIRST# R179 2.7K REQ64#1

8,14,17,18,21 HPCIRST# PCIRST# 13,19

7407

Size Document Number Rev

A3 PCI 3 01