Beruflich Dokumente

Kultur Dokumente

M.tech CPLD & Fpga Architecture & Applications

Hochgeladen von

srinivas0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

6K Ansichten1 SeiteCPLD and FPGA ARCHITECTURE and APPLICATIONS (VLSI System Design) Time: 3 hours Answer any FIVE questions All questions carry equal marks.

Originalbeschreibung:

Originaltitel

m.tech Cpld & Fpga Architecture & Applications

Copyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCPLD and FPGA ARCHITECTURE and APPLICATIONS (VLSI System Design) Time: 3 hours Answer any FIVE questions All questions carry equal marks.

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

6K Ansichten1 SeiteM.tech CPLD & Fpga Architecture & Applications

Hochgeladen von

srinivasCPLD and FPGA ARCHITECTURE and APPLICATIONS (VLSI System Design) Time: 3 hours Answer any FIVE questions All questions carry equal marks.

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 1

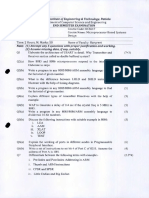

NR

Code No: 54203/MT

M.Tech. I-Semester Regular Examinations, March-2008.

CPLD & FPGA ARCHITECTURE & APPLICATIONS

(VLSI System Design)

Time: 3 hours Max. Marks: 60

Answer any FIVE questions

All questions carry equal marks.

---

1.a) Distinguish between ROM’s, PLAs and PALS.

b) Mention the features of Altera Flex logic-1000 series CPLD.

2.a) Compare Altera series Max-5000 and 7000 series PLDs.

b) Give the Design Flow for xilinx FPGA’s.

3.a) Give the routing architectures and logic Blocks of FPGA.

b) Give the architecture and salient features of optimized

Reconfigurable cell Array (ORCA) of AT&T.

4.a) Give the xilinx XC4000 features and compare them with Altera’s

Flex 8000 series FPGA.

b) Explain about Top Down Design flow of FSM.

5.a) Explain about Linked state Machines and one-Hot state machine.

b) Explain about the term Synchronization. Give its significance.

6.a) Describe the methodology of Architectures centred around non-

registered PLDS.

b) With an example explain about one Hot design Method using

ASMs.

7.a) Explain about Linked State Machines

b) Give the basic concepts and properties of Petrinetes for state

machines.

8. Write notes on any TWO:

a) Meta stability

b) Parallel Adder sequential circuits

c) ‘FPGA Advantage’ EDA Tool.

-----

Das könnte Ihnen auch gefallen

- 54203-Mt-cpld and Fpga Architecture and ApplicationsDokument1 Seite54203-Mt-cpld and Fpga Architecture and ApplicationsvasuvlsiNoch keine Bewertungen

- 54124-mt - CPLD & Fpga Architecture & ApplicationsDokument1 Seite54124-mt - CPLD & Fpga Architecture & ApplicationsSRINIVASA RAO GANTANoch keine Bewertungen

- M.tech CPLD & Fpga Architecture & ApplicationsDokument2 SeitenM.tech CPLD & Fpga Architecture & ApplicationssrinivasNoch keine Bewertungen

- Question Paper CodeDokument3 SeitenQuestion Paper CodeDinesh SrinivasanNoch keine Bewertungen

- 54208-mt - Design For TestabilityDokument2 Seiten54208-mt - Design For TestabilitySRINIVASA RAO GANTA100% (1)

- QP M Tech 4th Sem 21 VASDDokument2 SeitenQP M Tech 4th Sem 21 VASDAshadur RahamanNoch keine Bewertungen

- M.tech CPLD & Fpga Architecture & ApplicationsDokument2 SeitenM.tech CPLD & Fpga Architecture & Applicationssrinivas100% (1)

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDokument1 SeiteWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksSarath Chandra SuraganiNoch keine Bewertungen

- Intelligent Manufacturing SystemsDokument5 SeitenIntelligent Manufacturing SystemsVenkata RamuduNoch keine Bewertungen

- 1 Semester Model Question PapersDokument17 Seiten1 Semester Model Question PapersBalaji MohantyNoch keine Bewertungen

- Question Bank For Mid-2 r13 (Vlsi) .Dokument6 SeitenQuestion Bank For Mid-2 r13 (Vlsi) .rppvchNoch keine Bewertungen

- Ap7202-Asic and FpgaDokument12 SeitenAp7202-Asic and FpgaMOTHI.R MEC-AP/ECENoch keine Bewertungen

- Vlsi Question PapersDokument1 SeiteVlsi Question PapersjahnaviNoch keine Bewertungen

- Real Time Embedded Systems M TechDokument2 SeitenReal Time Embedded Systems M Techammayi9845_930467904Noch keine Bewertungen

- WWW - Manaresults.Co - In: CPLD and Fpga Architectures and ApplicationsDokument1 SeiteWWW - Manaresults.Co - In: CPLD and Fpga Architectures and ApplicationskopperundeviNoch keine Bewertungen

- Fpga Interview QuestionsDokument7 SeitenFpga Interview QuestionsJun ZhangNoch keine Bewertungen

- MM Solvedn 2Dokument14 SeitenMM Solvedn 2Chinnu Edwin ANoch keine Bewertungen

- Unit-1& at QB With AnswersDokument52 SeitenUnit-1& at QB With Answersm.shobhaNoch keine Bewertungen

- Page 1 of 2Dokument2 SeitenPage 1 of 2Siddarth NyatiNoch keine Bewertungen

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDokument2 SeitenAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNoch keine Bewertungen

- WWW Manaresults Co inDokument1 SeiteWWW Manaresults Co inSudheer BabuNoch keine Bewertungen

- Month & Year: March, 2019 Semester: Seventh Subject Code: 14CS IT 706 (Common To CSE and IT) Subject Name: Embedded SystemsDokument5 SeitenMonth & Year: March, 2019 Semester: Seventh Subject Code: 14CS IT 706 (Common To CSE and IT) Subject Name: Embedded Systemskeerthi mickelNoch keine Bewertungen

- Embedded System Design QPsDokument8 SeitenEmbedded System Design QPsJ HARSHA YADAVNoch keine Bewertungen

- Adca / Mca (Iii Year) 7t' Term-End Examination December, 2011 Cs-12: Computer ArchitectureDokument3 SeitenAdca / Mca (Iii Year) 7t' Term-End Examination December, 2011 Cs-12: Computer Architecturehaider_ali980Noch keine Bewertungen

- Subject: - Computer Organization and Architecture (01CT0301) Date:-6/12/2022 Total Marks:-100 Time: - 2 To 5 PMDokument3 SeitenSubject: - Computer Organization and Architecture (01CT0301) Date:-6/12/2022 Total Marks:-100 Time: - 2 To 5 PMdivyarajc073Noch keine Bewertungen

- Microprocessor Interfacing April2003 NR 321402Dokument4 SeitenMicroprocessor Interfacing April2003 NR 321402Nizam Institute of Engineering and Technology LibraryNoch keine Bewertungen

- Embedded Systems and Technologies (M. Tech. IAR)Dokument3 SeitenEmbedded Systems and Technologies (M. Tech. IAR)Gupta RanveerNoch keine Bewertungen

- FPGA Based System DesignDokument2 SeitenFPGA Based System Designammayi9845_930467904Noch keine Bewertungen

- ETC Raisoni Endsem PaperDokument14 SeitenETC Raisoni Endsem PaperYogesh Jounjalkar100% (1)

- Fpga Interview QuestionsDokument11 SeitenFpga Interview QuestionsNavathej BangariNoch keine Bewertungen

- Unit Wise Imp QuestionsDokument3 SeitenUnit Wise Imp Questionsvk2you009100% (1)

- AFD Important QuestionsDokument6 SeitenAFD Important QuestionsManikandan RajuNoch keine Bewertungen

- 5 Oct11Dokument12 Seiten5 Oct11Manu SeaNoch keine Bewertungen

- 2011 Eda For Vlsi Design: CS/B.TECH (ECE) (Separate Supple) /SEM-7/EC-702/2011Dokument7 Seiten2011 Eda For Vlsi Design: CS/B.TECH (ECE) (Separate Supple) /SEM-7/EC-702/2011John CaterNoch keine Bewertungen

- 07a80402 EmbeddedandrealtimesystemsDokument6 Seiten07a80402 EmbeddedandrealtimesystemsSharanya ThirichinapalliNoch keine Bewertungen

- Term End Examination - November 2014 Course: ITE305 - Embedded Systems Slot: A1+TA1 Class NBR: 6169 Time: Three Hours Max - Marks:100 PART - A (8 X 5 40 Marks) Answer ALL QuestionsDokument2 SeitenTerm End Examination - November 2014 Course: ITE305 - Embedded Systems Slot: A1+TA1 Class NBR: 6169 Time: Three Hours Max - Marks:100 PART - A (8 X 5 40 Marks) Answer ALL QuestionsSiddarth NyatiNoch keine Bewertungen

- WWW - Universityquestions.in: Department of Electronics and Communication EngineeringDokument10 SeitenWWW - Universityquestions.in: Department of Electronics and Communication EngineeringsowmyaNoch keine Bewertungen

- WWW - Universityquestions.in: Department of Electronics and Communication EngineeringDokument10 SeitenWWW - Universityquestions.in: Department of Electronics and Communication EngineeringsowmyaNoch keine Bewertungen

- Fpga Based System DesignDokument30 SeitenFpga Based System DesignKrishna Kumar100% (1)

- 9D57106c ASIC DesignDokument1 Seite9D57106c ASIC DesignsubbuNoch keine Bewertungen

- Ucs617 3Dokument1 SeiteUcs617 3Suprit BeheraNoch keine Bewertungen

- UCS631Dokument1 SeiteUCS631Lets clear Jee mathsNoch keine Bewertungen

- QB Mpi Cse 5 Sem CT-2Dokument1 SeiteQB Mpi Cse 5 Sem CT-2Sanjana GovindaniNoch keine Bewertungen

- 2018-Dec ECD-311 58Dokument2 Seiten2018-Dec ECD-311 58Tusshar PaulNoch keine Bewertungen

- 4507 CPLD and FPGA ArchitecturesDokument1 Seite4507 CPLD and FPGA ArchitecturesshobiNoch keine Bewertungen

- Electronics MPDokument8 SeitenElectronics MPk lakshmi prasannaNoch keine Bewertungen

- Fpga Interview QuestionsDokument9 SeitenFpga Interview QuestionsV SharmaNoch keine Bewertungen

- 9A15502 Digital System DesignDokument4 Seiten9A15502 Digital System Designsivabharathamurthy100% (1)

- Ap7202-Asic and FpgaDokument10 SeitenAp7202-Asic and FpgaJayapalNoch keine Bewertungen

- Time: Three Hours Maximum Marks: GS: 70 NGS:100Dokument2 SeitenTime: Three Hours Maximum Marks: GS: 70 NGS:100Arun Pratap SinghNoch keine Bewertungen

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDokument3 SeitenEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANoch keine Bewertungen

- 9A04602 Microprocessors & Microcontrollers5Dokument1 Seite9A04602 Microprocessors & Microcontrollers5subbuNoch keine Bewertungen

- Jntu MDokument3 SeitenJntu MVijay SagarNoch keine Bewertungen

- Question Paper Code:: Reg. No.Dokument3 SeitenQuestion Paper Code:: Reg. No.Joshua DuffyNoch keine Bewertungen

- Ac Theory Module10Dokument11 SeitenAc Theory Module10srinivasNoch keine Bewertungen

- SQL Server Transaction Log ManagementDokument209 SeitenSQL Server Transaction Log ManagementCarlos Eduardo100% (1)

- EdgeDokument27 SeitenEdgesrinivasNoch keine Bewertungen

- I Love You in 100 LanguagesDokument2 SeitenI Love You in 100 LanguagesMadelapizNoch keine Bewertungen

- TransformatoriDokument21 SeitenTransformatoriantoniomkdNoch keine Bewertungen

- ECE 2-1 r13Dokument12 SeitenECE 2-1 r13srinivasNoch keine Bewertungen

- Ac TheoryDokument15 SeitenAc TheoryAnonymous vKD3FG6RkNoch keine Bewertungen

- Ac Theory Module07Dokument8 SeitenAc Theory Module07srinivasNoch keine Bewertungen

- Ac Theory Moqwdule09Dokument12 SeitenAc Theory Moqwdule09Vikas VernekarNoch keine Bewertungen

- Ac Theory Module05Dokument12 SeitenAc Theory Module05srinivasNoch keine Bewertungen

- Ac Theory Module06Dokument9 SeitenAc Theory Module06srinivasNoch keine Bewertungen

- Probability and StatisticsDokument15 SeitenProbability and StatisticssrinivasNoch keine Bewertungen

- DC Transients: What Happens When Things ChangeDokument10 SeitenDC Transients: What Happens When Things Changethangaraj_icNoch keine Bewertungen

- Unit 4: PTSP Unit Iv Questions & AnswersDokument10 SeitenUnit 4: PTSP Unit Iv Questions & AnswerssrinivasNoch keine Bewertungen

- AC CircuitDokument10 SeitenAC CircuitSandun LakminaNoch keine Bewertungen

- Ac Theory Module02Dokument13 SeitenAc Theory Module02bec08busNoch keine Bewertungen

- Unit 7: 1. Derive An Expression For Power Spectral Density? AnsDokument11 SeitenUnit 7: 1. Derive An Expression For Power Spectral Density? AnssrinivasNoch keine Bewertungen

- PTSPQNAUNITVIIIDokument13 SeitenPTSPQNAUNITVIIIsrinivasNoch keine Bewertungen

- Introduction To Wireless NetworksDokument22 SeitenIntroduction To Wireless NetworkssrinivasNoch keine Bewertungen

- UNIT-3: 1. Explain The Terms Following Terms: (A) Mean (B) Mean Square Value. AnsDokument13 SeitenUNIT-3: 1. Explain The Terms Following Terms: (A) Mean (B) Mean Square Value. AnssrinivasNoch keine Bewertungen

- PTSP Q&A Unit 2Dokument16 SeitenPTSP Q&A Unit 2dsrilatharajuNoch keine Bewertungen

- Unit - 1: 1. Explain About The Partition of A Sampling Space Theorem? AnsDokument14 SeitenUnit - 1: 1. Explain About The Partition of A Sampling Space Theorem? AnssrinivasNoch keine Bewertungen

- Computer Networks and Information SecurityDokument35 SeitenComputer Networks and Information SecuritysrinivasNoch keine Bewertungen

- Unit 6: 1. Explain The Classification of Random Process With Neat Sketches. AnsDokument12 SeitenUnit 6: 1. Explain The Classification of Random Process With Neat Sketches. Anssrinivas0% (1)

- Benefits of MarketingDokument2 SeitenBenefits of MarketingsrinivasNoch keine Bewertungen

- THESISDokument88 SeitenTHESISmahwishkamilNoch keine Bewertungen

- M.tech Advanced Digital Signal ProcessingDokument2 SeitenM.tech Advanced Digital Signal ProcessingsrinivasNoch keine Bewertungen

- 54105-Mt-Vlsi Technology and DesignDokument2 Seiten54105-Mt-Vlsi Technology and DesignSrinivasa Rao G100% (2)

- MT Digital System DesignDokument1 SeiteMT Digital System Designvasudevareddy100% (1)

- The Non-Technical Founder: How a 16-Year Old Built a Six Figure Software Company Without Writing Any CodeVon EverandThe Non-Technical Founder: How a 16-Year Old Built a Six Figure Software Company Without Writing Any CodeBewertung: 4 von 5 Sternen4/5 (1)

- ChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveVon EverandChatGPT Side Hustles 2024 - Unlock the Digital Goldmine and Get AI Working for You Fast with More Than 85 Side Hustle Ideas to Boost Passive Income, Create New Cash Flow, and Get Ahead of the CurveNoch keine Bewertungen

- Fundamentals of Data Engineering: Plan and Build Robust Data SystemsVon EverandFundamentals of Data Engineering: Plan and Build Robust Data SystemsBewertung: 5 von 5 Sternen5/5 (1)

- ChatGPT Millionaire 2024 - Bot-Driven Side Hustles, Prompt Engineering Shortcut Secrets, and Automated Income Streams that Print Money While You Sleep. The Ultimate Beginner’s Guide for AI BusinessVon EverandChatGPT Millionaire 2024 - Bot-Driven Side Hustles, Prompt Engineering Shortcut Secrets, and Automated Income Streams that Print Money While You Sleep. The Ultimate Beginner’s Guide for AI BusinessNoch keine Bewertungen

- Change Management for Beginners: Understanding Change Processes and Actively Shaping ThemVon EverandChange Management for Beginners: Understanding Change Processes and Actively Shaping ThemBewertung: 4.5 von 5 Sternen4.5/5 (3)

- Designing Data-Intensive Applications: The Big Ideas Behind Reliable, Scalable, and Maintainable SystemsVon EverandDesigning Data-Intensive Applications: The Big Ideas Behind Reliable, Scalable, and Maintainable SystemsBewertung: 5 von 5 Sternen5/5 (6)

- Business Intelligence Strategy and Big Data Analytics: A General Management PerspectiveVon EverandBusiness Intelligence Strategy and Big Data Analytics: A General Management PerspectiveBewertung: 5 von 5 Sternen5/5 (5)

- Managing Humans: Biting and Humorous Tales of a Software Engineering ManagerVon EverandManaging Humans: Biting and Humorous Tales of a Software Engineering ManagerBewertung: 4 von 5 Sternen4/5 (90)

- Product Operations: How successful companies build better products at scaleVon EverandProduct Operations: How successful companies build better products at scaleNoch keine Bewertungen

- Design and Build Modern Datacentres, A to Z practical guideVon EverandDesign and Build Modern Datacentres, A to Z practical guideBewertung: 3 von 5 Sternen3/5 (2)

- Microsoft Project 2019 For DummiesVon EverandMicrosoft Project 2019 For DummiesBewertung: 5 von 5 Sternen5/5 (1)

- Microservices Patterns: With examples in JavaVon EverandMicroservices Patterns: With examples in JavaBewertung: 5 von 5 Sternen5/5 (2)

- CATIA V5-6R2015 Basics - Part I : Getting Started and Sketcher WorkbenchVon EverandCATIA V5-6R2015 Basics - Part I : Getting Started and Sketcher WorkbenchBewertung: 4 von 5 Sternen4/5 (10)

- Notion for Beginners: Notion for Work, Play, and ProductivityVon EverandNotion for Beginners: Notion for Work, Play, and ProductivityBewertung: 4 von 5 Sternen4/5 (8)

- Creating Online Courses with ChatGPT | A Step-by-Step Guide with Prompt TemplatesVon EverandCreating Online Courses with ChatGPT | A Step-by-Step Guide with Prompt TemplatesBewertung: 4 von 5 Sternen4/5 (4)

- Python for Beginners: A Crash Course Guide to Learn Python in 1 WeekVon EverandPython for Beginners: A Crash Course Guide to Learn Python in 1 WeekBewertung: 4.5 von 5 Sternen4.5/5 (7)

- The Complete Business Process Handbook: Body of Knowledge from Process Modeling to BPM, Volume 1Von EverandThe Complete Business Process Handbook: Body of Knowledge from Process Modeling to BPM, Volume 1Bewertung: 4.5 von 5 Sternen4.5/5 (7)

- Artificial Intelligence in Practice: How 50 Successful Companies Used AI and Machine Learning to Solve ProblemsVon EverandArtificial Intelligence in Practice: How 50 Successful Companies Used AI and Machine Learning to Solve ProblemsBewertung: 4.5 von 5 Sternen4.5/5 (38)

- Excel Formulas That Automate Tasks You No Longer Have Time ForVon EverandExcel Formulas That Automate Tasks You No Longer Have Time ForBewertung: 5 von 5 Sternen5/5 (1)