Beruflich Dokumente

Kultur Dokumente

Shematic Falcon

Hochgeladen von

knarfboyCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Shematic Falcon

Hochgeladen von

knarfboyCopyright:

Verfügbare Formate

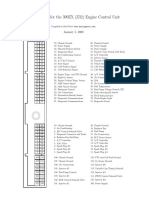

CR-1

@FALCON_LIB.FALCON(SCH_1):PAGE1

PAGE

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

[18]

[19]

[20]

[21]

[22]

[23]

[24]

[25]

[26]

[27]

[28]

[29]

[30]

[31]

[32]

RULES:

1.)

2.)

3.)

4.)

5.)

6.)

7.)

8.)

9.)

10.)

12.)

13.)

14.)

15.)

CONTENTS

PAGE

COVER PAGE

CLOCK DIAGRAM

RESET/ENABLE

DIAGRAM

CPU, CLOCKS + EEPROM + STRAPPING

CPU, FSB

CPU, FSB POWER + PLL POWER

CPU, CORE POWER

CPU, POWER

CPU, DECOUPLING

CPU, DECOUPLING

CPU, DECOUPLING

GPU, FSB

GPU, VIDEO + PCIEX + EEPROM

GPU, MEMORY CONTROLLER A + B

GPU, MEMORY CONTROLLER C + D

GPU, PLL POWER + FSB POWER

GPU, CORE POWER + MEM POWER

GPU, DECOUPLING

MEMORY, A (TOP)

MEMORY, A MIRRORED (BOTTOM)

MEMORY, B (TOP)

MEMORY, B MIRRORED (BOTTOM)

MEMORY, C (TOP)

MEMORY, C MIRRORED (BOTTOM)

MEMORY, D (TOP)

MEMORY, D MIRRORED (BOTTOM)

HANA, CLOCKS + STRAPPING

HANA, VIDEO + FAN + JTAG

CONN, HDMI

HANA, POWER + DECOUPLING

HANA, POWER + DECOUPLING

POWER TRACE EMI CAPS

(APPLIED

[33]

[34]

[35]

[36]

[37]

[38]

[39]

[40]

[41]

[42]

[43]

[44]

[45]

[46]

[47]

[48]

[49]

[50]

[51]

[52]

[53]

[54]

[55]

[56]

[57]

[58]

[59]

[60]

[61]

[62]

[63]

[64]

[65-6]

SCHEMATIC

1.0

CONTENTS

REV

PCBA NUMBER

X8XXXXX-001

SB, PCIEX + SMM GPIO + JTAG

SB, SMC

SB, FLASH + USB + SPI

SB, ETHERNET + AUDIO + SATA

SB, STANDBY POWER + DECOUPLE

SB, MAIN POWER + DECOUPLE

SB OUT, ETHERNET

SB OUT, AUDIO

SB OUT, FLASH

SB OUT, FAN + INFRARED + BUTTONS

CONN, AVIP

CONN, RJ45 + USB COMBO

CONN, GAME PORTS + MEMORY PORTS

MISC, V_5P0 DUAL, DEBUG MAPPING

CONN, ODD AND HDD

CONN, ARGON + POWER

VREGS, INPUT + OUTPUT FILTERS

VREGS, CPU CONTROLLER

VREGS, GPU OUTPUT PHASE 1,2,3

VREGS, GPU CONTROLLER

VREGS, GPU OUTPUT PHASE 1,2

VREGS, SWITCHED 1.8,

5.0V

VREGS, LINEAR REGULATORS

XDK, DEBUG CONN

DEBUG BOARD, CPU + GPU BREAKOUT

DEBUG BOARD, CPU CONN

DEBUG BOARD, CPU CONN + TERM

DEBUG BOARD, CPU TERM

DEBUG BOARD, TITAN + YETI CONN

DEBUG BOARD, GPU CONN + TERM

XDK, LEDS, BDCM PHY

LABELS AND MOUNTING, PCI SWIZ

MEM QUAL BOARDS

PLEASE

BOM RELEASE

DATE

SIGNATURE

FALCON

RETAIL

REV 1.0

FAB D

FALCON_FABD

Tue

May 08

18:21:43

XX/XX/06

DATE

PB NUMBER

SPEC

X80XXXX-00X

DRN BY

MICROSOFT XBOX

TITLE

APVD

2007

REFER TO THE XENON DESIGN

CHK BY

ENGR

APVD

DRAWING

PAGE]

BOM RELEASE DATE

XX/XX/06

FALCON

WHEN POSSIBLE)

MSB TO LSB IS TOP TO BOTTOM

WHEN POSSIBLE:

INPUTS ON LEFT,

OUTPUTS ON RIGHT

ORDER OF PAGES=CHIP INTERFACES,

TERMINATION,

POWER, DECOUPLING

AVOID USING OFF PAGE CONNECTORS FOR ON PAGE CONNECTIONS

LANED SIGNALS ARE GROUPED ON SYMBOLS

TRANSIMITTER

NAME USED AS PREFIX WITH RX AND TX CONNECTIONS

SUFFIX V_ IS USED FOR VOLTAGE RAIL SIGNAL NAMES

SUFFIX _DP AND _DN ARE USED FOR DIFFERIENTAL

PAIRS

UNNAMED NETS ARE NAMED WITH /2 TEXT SIZE

SUFFIX _N FOR ACTIVE LOW OR N JUNCTION

SUFFIX _P FOR P JUNCTION

SUFFIX _EN FOR ENABLE

'CLK'

FOR CLOCKS, 'RST'

FOR RESETS

PWRGD FOR POWER GOOD

[PAGE_TITLE=COVER

REV

D

APVD

SCH,

MICROSOFT

CONFIDENTIAL

PBA,

FALCON

PROJECT NAME

FALCON_RETAIL

PAGE

1/82

REV

1.0

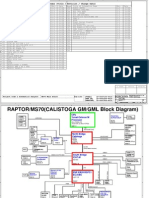

CR-2

@FALCON_LIB.FALCON(SCH_1):PAGE2

RJ45/USB

CONN

ENET

PHY

AVIP

CONN

FAN

CONN

I2S_MCLK(12.288MHZ)

I2S_BCLK(3.072MHZ)

AUDIO

DAC

OUT OF DATE *

POWER

CONN

ANA_XTAL_IN(27MHZ)

GPU VR

DEBUG

CONN

ANA

BCKUP

DVD

SATA

CONN

IS

CLOCK DIAGRAM

ENET_CLK(25MHZ)

SB

THIS

ANA

GPU VR

CNTL

STBY_CLK(48MHZ)

SATA_CLK_REF(25MHZ)

SATA_CLK_DP/DN(100MHZ)

PCIEX_CLK_DP/DN(100MHZ)

AUD_CLK(24.576MHZ)

CPU_CLK_DP/DN(100MHZ)

GPU_CLK_DP/DN

DVD

PWR

CONN

ANA

BCKUP

VR

FLSH

HDD

CONN

3P3

CPU

GPU

MA_CLK1_DP/DN(800MHZ)

MA_CLK0_DP/DN(800MHZ)

MB_CLK1_DP/DN(800MHZ)

MB_CLK0_DP/DN(800MHZ)

1P8

MEM

CLAM C+D

MC_CLK1_DP/DN(800MHZ)

MC_CLK0_DP/DN(800MHZ)

MD_CLK1_DP/DN(800MHZ)

MD_CLK0_DP/DN(800MHZ)

RISCWATCH

CONN

PIX_CLK_OUT_DP/DN(100MHZ)

(100MHZ)

TITAN

CONN

VR

VMEM VR

5P0

MPORT VR

MEM

CLAM A+B

EFUSE

CPU

VR

JTAG

VR

CPU VR

CNTL

VR

GAME

CONN

IR

EJECT

SW

<PAGE_TITLE=CLOCK

MEM

CONN

DIAGRAM>

MEM

CONN

BIND

SW

ARGON

CONN

DRAWING

FALCON_FABD

Tue May 08 11:47:32

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

2/82

REV

1.0

CR-3

@FALCON_LIB.FALCON(SCH_1):PAGE3

ENET

PHY

AVIP

CONN

ENET_RST_N

EXT_PWR_ON_N

RJ45/USB

CONN

POWER

CONN

FAN

CONN

RESET/ENABLE

AUD_CLAMP

AUD_RST_N

DIAGRAM

AUDIO

DAC

PSU_V12P0_EN

GPU VR

HANA_CLK_OE

HANA_RST_N

HANA

VREG_GPU_EN_N

SB_RST_N

SMC_RST_N

DVD

SATA

CONN

SB

VREG_GPU_PWRGD

EXT_PWR_ON_N

CPU_CHECKSTOP_N

CPU_RST_N

CPU_PWRGD

GPU_RST_N

RISCWATCH

CONN

MEM

CLAM C+D

MEM_RST

MEM_SCAN_EN

MEM_SCAN_TOP_EN

MEM_SCAN_BOT_EN

3P3

VR

DEBUG

CONN

CPU

VR

GPU

CPU

MEM_RST

MEM_SCAN_EN

MEM_SCAN_TOP_EN

MEM_SCAN_BOT_EN

HDD

CONN

VREG_CPU_PWRGD

SMC_DBG_EN

GPU_RST_DONE

VREG_3P3_EN

DVD

PWR

CONN

GPU VR

CNTL

VREG_1P8_EN_N

VREG_5P0_EN_N

CPU_PWRGD

TITAN

CONN

MEM

CLAM A+B

VMEM VR

5P0

EFUSE

JTAG

VR

CPU VR

CNTL

VR

VREG_EFUSE_EN

VREG_CPU_EN

GAME

CONN

IR

EJECT

SW

[PAGE_TITLE=RESET/ENABLE

MEM

CONN

MEM

CONN

DIAGRAM]

BIND

SW

ARGON

CONN

DRAWING

FALCON_FABD

Tue May 08 11:47:32

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

3/82

REV

1.0

CR-4

@FALCON_LIB.FALCON(SCH_1):PAGE4

58

34

FT2P11

3.92K

402

R7R10 2

3.92K

402

V_GPUCORE

1K

402

R6R6

10K

5%

CH

402

R7R11

6.19K

402

R6R4

R6R9

1%

CH

R6R5

1K

402

27

C7R112

27

1%

CH

IN

360PF

10%

50V

EMPTY

603

IN

10K

5%

CH

402

5%

CH

1

2

SMT

10K

5%

CH

402

R7D1

10K

5%

CH

402

10K

5%

EMPTY

402

C7

VREG_EFUSE_EN

FSB_CLK_DP

FSB_CLK_DN

FSB_HF_CLKOUT_DP

FSB_HF_CLKOUT_DN

AF20

AG20

CPU_FSB_HF_CLKOUT_DP

CPU_FSB_HF_CLKOUT_DN

OUT

OUT

CPU_FSB_CLK_SEL

AE16

FSB_CLK_SEL

AH23

AH22

CPU_EXT_CLK_EN

FSB_IMPED_CAL_DP

FSB_IMPED_CAL_DN

CPU_FSB_IMPED_CAL_DP

CPU_FSB_IMPED_CAL_DN

AD16

EXT_CLK_EN

OUT

OUT

CPU_PLL_BYPASS

AF14

PLL_BYPASS

AG14

PULSE_LIMIT_BYPASS

CPU_SYS_CONFIG0

CPU_SYS_CONFIG1

AH3

AE2

SYS_CONFIG0

SYS_CONFIG1

0

1

2

3

4

AF8

AG8

AH7

AH8

AH9

POST_IN0

POST_IN1

POST_IN2

POST_IN3

POST_IN4

CPU_SPI_SI

C4

V_CPUCORE

R7R8

100

5%

EMPTY

402

10K

5%

CH

402

1

10K

5%

EMPTY

402

10K

5%

CH

402

10K

5%

CH

402

1K

402

R7R1

AE22

AD22

ANL_1

ANL_2

CPU_SRVID

CPU_VGATE

A2

AH14

SRVID

VGATE

10K

5%

EMPTY

402

CPU_RES0_DP

CPU_RES0_DN

VDDS0_DP

VDDS0_DN

AF11

AH10

CPU_VDDS0_DP

CPU_VDDS0_DN

VDDS1_DP

VDDS1_DN

AG2

AH1

CPU_VDDS1_DP

CPU_VDDS1_DN

AE14

CPU_PSRO0_OUT

1

2

TP7R4

R7R2

2

2

1%

CH

10K

5%

CH

402

FTP

FTP

FTP

FTP

FTP

1

1

1

1

1

IN

TP

R7R9

CPU_SPI_CLK

CPU_SPI_EN

CPU_SPI_SO

OUT

OUT

4

4

TEMP_DP

TEMP_DN

AH18

AH19

CPU_TEMP_P

CPU_TEMP_N

IN

OUT

28

28

C5

B6

A5

B5

A6

C6

CPU_VREG_APS0

CPU_VREG_APS1

CPU_VREG_APS2

CPU_VREG_APS3

CPU_VREG_APS4

CPU_VREG_APS5

VID0

VID1

VID2

VID3

VID4

VID5

1

1

1

CPU

R7R1

R7R2

LOKI

ASPEN

1.40K

EMPTY

10K

OUT

OUT

OUT

OUT

OUT

OUT

1

1

1

FTP FT7T2

FTP FT7T1

FTP FT7T7

1K

IN

R6E2

1K

402

V_MEM

4

3

2

1

0

5%

CH

R7E7

CPU_SPI_SO

1K

402

DB7R1

B4

A3

A4

X806937-001

CPU_SPI_CLK

PROBE

1

2

SPI_CLK

SPI_EN

SPI_SO

5%

CH

6

5

CPU_SPI_CLK_R

CPU_SPI_SO_R

7

1

3

CPU_SPI_EN_R

SCK

SDI

HOLD_N*

CS_N*

WP_N*

VCC

SDO

R6E1

50

50

50

50

50

50

10K

5%

CH

402

.1UF

10%

6.3V

X5R

402

R7F3

10K

5%

EMPTY

402

CPU_SPI_SI_R

1

GND

C6F1

AT25020A

X800552-001

IN

CPU_SPI_EN

CLOCKS + EEPROM + STRAPPING]

10K

5%

CH

402

R7F2

1K

402

5%

CH

10K

402

1

2

5%

CH

10K

402

R7U3

R7E8

R7F1

1K

402

R7F7

CPU_SPI_SI

5%

CH

OUT

R7F4

V_MEM

2

10K

5%

CH

402

V_MEM

1

EMPTY

OUT

FTP FT7T5

FTP FT7T4

FTP FT7T3

V_MEM

U7E1

10K

5%

EMPTY

402

TP7R2

SMT

TE

R7R14

1%

CH

PROBE

1

2

SMT

PSRO0_OUT

R7R18

PROBE

AH12

AH13

RESISTOR0_DP

RESISTOR0_DN

V_MEM

FT7R4

FT7R6

FT7R2

FT7R1

FT7R5

[PAGE_TITLE=CPU,

AF2

SMT

56

OUT

TP7R3

SPI_SI

CPU_ANL_1

CPU_ANL_2

R7R19

EFU_POWERON

1

10K

5%

EMPTY

402

R7R23

R7R3

R7R22

R7R5

R7R13

R7R20

10K

5%

EMPTY

402

OUT

OUT

CPU_TEST_EN

1.40K

402

10K

5%

CH

402

OUT

IN

V_1P8

V_GPUCORE

R7T18

57

10K

5%

CH

402

PROBE

1

2

HARD_RESET_B

POWER_GOOD

100

5%

EMPTY

402

CPU_CORE_IF_BGR_PLL

SMT

MUST BE ACCESSIBLE

R7R12

TP7R1

AH15

AF1

AD14

V_GPUCORE

IC

CORE_IF_BGR_PLL

DB7R2

R7R15

10K

5%

CH

402

CORE_CLK_DP

CORE_CLK_DN

AH21

AH20

FSB_CLK_DP

FSB_CLK_DN

CPU_POST_IN<0..4>

R7R21

AG23

AF23

R7D2

V_GPUCORE

1 OF 10

LOKI

CPU_PULSE_LIMIT_BYPASS

LAYOUT:

U7D1

PROBE

5%

CH

R7R17

0

402

CPU_CLK_DP_C

TP6D1

R6R7

R6D5

CPU_CLK_DN1

5%

CH

CPU_CLK_DN_C

10K

5%

EMPTY

402

R6D4

0

402

360PF

10%

50V

EMPTY

603

R6R8

CLOCKS + EEPROM + STRAPPING

CPU_CLK_DP 1

C7R113

5%

CH

10K

5%

EMPTY

402

CPU_PWRGD_V1P1_N

1%

CH

V_GPUCORE

R7R16 2

FTP

CPU,

1%

CH

6.19K

402

CPU_PWRGD

IN

R7R4

FTP

FT2P12

34

CPU_RST_V1P1_N

OUT

CPU_RST_N

IN

100

5%

CH

402

5%

EMPTY

CPU_SPI_WP_N

IN

DRAWING

FALCON_FABD

Tue May 08 18:24:08

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

4/82

REV

1.0

CR-5

@FALCON_LIB.FALCON(SCH_1):PAGE5

CPU,

U7D1

FSB

2 OF 10

IC

LOKI

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

IN

IN

FSB_GP_CP0_FLAG_DP

FSB_GP_CP0_FLAG_DN

AB27

AB28

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

FSB_GP_CP0_DATA0_DP

FSB_GP_CP0_DATA0_DN

FSB_GP_CP0_DATA1_DP

FSB_GP_CP0_DATA1_DN

FSB_GP_CP0_DATA2_DP

FSB_GP_CP0_DATA2_DN

FSB_GP_CP0_DATA3_DP

FSB_GP_CP0_DATA3_DN

FSB_GP_CP0_DATA4_DP

FSB_GP_CP0_DATA4_DN

FSB_GP_CP0_DATA5_DP

FSB_GP_CP0_DATA5_DN

FSB_GP_CP0_DATA6_DP

FSB_GP_CP0_DATA6_DN

FSB_GP_CP0_DATA7_DP

FSB_GP_CP0_DATA7_DN

T26

T25

T28

T27

U27

U28

V26

V25

W27

W28

Y26

Y25

Y28

Y27

AA27

AA28

IN

IN

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

IN

IN

FSB_GP_CP0_CLK_DP

FSB_GP_CP0_CLK_DN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

V28

V27

CP_GP0_CLK_DP

CP_GP0_CLK_DN

AE27

AE28

FSB_CP_GP0_CLK_DP

FSB_CP_GP0_CLK_DN

OUT

OUT

12

12

CP_GP0_FLAG_DP

CP_GP0_FLAG_DN

AH25

AH26

FSB_CP_GP0_FLAG_DP

FSB_CP_GP0_FLAG_DN

OUT

OUT

12

12

CP_GP0_DATA0_DP

CP_GP0_DATA0_DN

CP_GP0_DATA1_DP

CP_GP0_DATA1_DN

CP_GP0_DATA2_DP

CP_GP0_DATA2_DN

CP_GP0_DATA3_DP

CP_GP0_DATA3_DN

CP_GP0_DATA4_DP

CP_GP0_DATA4_DN

CP_GP0_DATA5_DP

CP_GP0_DATA5_DN

CP_GP0_DATA6_DP

CP_GP0_DATA6_DN

CP_GP0_DATA7_DP

CP_GP0_DATA7_DN

AB26

AB25

AC27

AC28

AD28

AD27

AD25

AD26

AF28

AF27

AF25

AF26

AG27

AG28

AH28

AH27

FSB_CP_GP0_DATA0_DP

FSB_CP_GP0_DATA0_DN

FSB_CP_GP0_DATA1_DP

FSB_CP_GP0_DATA1_DN

FSB_CP_GP0_DATA2_DP

FSB_CP_GP0_DATA2_DN

FSB_CP_GP0_DATA3_DP

FSB_CP_GP0_DATA3_DN

FSB_CP_GP0_DATA4_DP

FSB_CP_GP0_DATA4_DN

FSB_CP_GP0_DATA5_DP

FSB_CP_GP0_DATA5_DN

FSB_CP_GP0_DATA6_DP

FSB_CP_GP0_DATA6_DN

FSB_CP_GP0_DATA7_DP

FSB_CP_GP0_DATA7_DN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

CP_GP1_CLK_DP

CP_GP1_CLK_DN

M28

M27

FSB_CP_GP1_CLK_DP

FSB_CP_GP1_CLK_DN

OUT

OUT

12

12

CP_GP1_FLAG_DP

CP_GP1_FLAG_DN

R28

R27

FSB_CP_GP1_FLAG_DP

FSB_CP_GP1_FLAG_DN

OUT

OUT

12

12

CP_GP1_DATA0_DP

CP_GP1_DATA0_DN

CP_GP1_DATA1_DP

CP_GP1_DATA1_DN

CP_GP1_DATA2_DP

CP_GP1_DATA2_DN

CP_GP1_DATA3_DP

CP_GP1_DATA3_DN

CP_GP1_DATA4_DP

CP_GP1_DATA4_DN

CP_GP1_DATA5_DP

CP_GP1_DATA5_DN

CP_GP1_DATA6_DP

CP_GP1_DATA6_DN

CP_GP1_DATA7_DP

CP_GP1_DATA7_DN

J28

J27

K28

K27

L25

L26

L28

L27

N25

N26

N28

N27

P28

P27

R25

R26

FSB_CP_GP1_DATA0_DP

FSB_CP_GP1_DATA0_DN

FSB_CP_GP1_DATA1_DP

FSB_CP_GP1_DATA1_DN

FSB_CP_GP1_DATA2_DP

FSB_CP_GP1_DATA2_DN

FSB_CP_GP1_DATA3_DP

FSB_CP_GP1_DATA3_DN

FSB_CP_GP1_DATA4_DP

FSB_CP_GP1_DATA4_DN

FSB_CP_GP1_DATA5_DP

FSB_CP_GP1_DATA5_DN

FSB_CP_GP1_DATA6_DP

FSB_CP_GP1_DATA6_DN

FSB_CP_GP1_DATA7_DP

FSB_CP_GP1_DATA7_DN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

GP_CP0_CLK_DP

GP_CP0_CLK_DN

GP_CP0_FLAG_DP

GP_CP0_FLAG_DN

GP_CP0_DATA0_DP

GP_CP0_DATA0_DN

GP_CP0_DATA1_DP

GP_CP0_DATA1_DN

GP_CP0_DATA2_DP

GP_CP0_DATA2_DN

GP_CP0_DATA3_DP

GP_CP0_DATA3_DN

GP_CP0_DATA4_DP

GP_CP0_DATA4_DN

GP_CP0_DATA5_DP

GP_CP0_DATA5_DN

GP_CP0_DATA6_DP

GP_CP0_DATA6_DN

GP_CP0_DATA7_DP

GP_CP0_DATA7_DN

FSB_GP_CP1_CLK_DP

FSB_GP_CP1_CLK_DN

E28

E27

FSB_GP_CP1_FLAG_DP

FSB_GP_CP1_FLAG_DN

J26

J25

GP_CP1_FLAG_DP

GP_CP1_FLAG_DN

FSB_GP_CP1_DATA0_DP

FSB_GP_CP1_DATA0_DN

FSB_GP_CP1_DATA1_DP

FSB_GP_CP1_DATA1_DN

FSB_GP_CP1_DATA2_DP

FSB_GP_CP1_DATA2_DN

FSB_GP_CP1_DATA3_DP

FSB_GP_CP1_DATA3_DN

FSB_GP_CP1_DATA4_DP

FSB_GP_CP1_DATA4_DN

FSB_GP_CP1_DATA5_DP

FSB_GP_CP1_DATA5_DN

FSB_GP_CP1_DATA6_DP

FSB_GP_CP1_DATA6_DN

FSB_GP_CP1_DATA7_DP

FSB_GP_CP1_DATA7_DN

C26

C25

C28

C27

D27

D28

E26

E25

F27

F28

G26

G25

G28

G27

H27

H28

GP_CP1_DATA0_DP

GP_CP1_DATA0_DN

GP_CP1_DATA1_DP

GP_CP1_DATA1_DN

GP_CP1_DATA2_DP

GP_CP1_DATA2_DN

GP_CP1_DATA3_DP

GP_CP1_DATA3_DN

GP_CP1_DATA4_DP

GP_CP1_DATA4_DN

GP_CP1_DATA5_DP

GP_CP1_DATA5_DN

GP_CP1_DATA6_DP

GP_CP1_DATA6_DN

GP_CP1_DATA7_DP

GP_CP1_DATA7_DN

GP_CP1_CLK_DP

GP_CP1_CLK_DN

X806937-001

V_GPUCORE

1

2

[PAGE_TITLE=CPU,

FSB]

C6R15

.1UF

10%

6.3V

X5R

402

1

2

C6R18

.1UF

10%

6.3V

X5R

402

1

2

C6R14

.1UF

10%

6.3V

X5R

402

1

2

C6R25

.1UF

10%

6.3V

X5R

402

1

2

C6R37

.1UF

10%

6.3V

X5R

402

1

2

C6T19

.1UF

10%

6.3V

X5R

402

1

2

C6T7

.1UF

10%

6.3V

X5R

402

1

2

C6T27

.1UF

10%

6.3V

X5R

402

1

2

C6T33

.1UF

10%

6.3V

X5R

402

1

2

C6T32

.1UF

10%

6.3V

X5R

402

1

2

C6R6

.1UF

10%

6.3V

X5R

402

DRAWING

FALCON_FABD

Tue May 08 18:24:09

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

5/82

REV

1.0

CR-6

@FALCON_LIB.FALCON(SCH_1):PAGE6

CPU,

FSB POWER + PLL

POWER

V_1P8

V_GPUCORE

V_CPUPLL

U7D1

FB7R1

1

1

2

C7R1

1

2

FB

603

1K

0.2A

0.7DCR

.1UF

10%

6.3V

X5R

402

C7R7

.1UF

10%

6.3V

X5R

402

C7R116

.1UF

10%

6.3V

X5R

402

4 of

C7R114

.1UF

10%

6.3V

X5R

402

ST7R1

2

V_EFUSE

SHORT

FB6D1

1

1

2

C6D1

10K

402

1K

0.2A

0.7DCR

R7T2

CPU_VDDE

5%

CH

FB

603

.1UF

10%

6.3V

X5R

402

2.2UF

10%

6.3V

X5R

603

V_CPU_CORE_HF_VDDA_PLL

V_CPU_CORE_HF_GNDA_PLL

ST6D1

2

V_CPU_CORE_IF_VDDA_PLL

V_CPU_CORE_IF_GNDA_PLL

SHORT

V_CPU_FSB_HF_VDDA_PLL

V_CPU_FSB_HF_GNDA_PLL

FB6R1

1

1

2

C6R2

V_CPU_FSB_IF_VDDA_PLL

1K

0.2A

0.7DCR

V_CPU_FSB_IF_GNDA_PLL

FB

603

V_CPU_VDDA_RNG

.1UF

10%

6.3V

X5R

402

V_CPU_GNDA_RNG

C6R4

VDD_IO

VDDE

VDDE_SEC

AG17

AF17

CORE_HF_VDDA_PLL

CORE_HF_GNDA_PLL

AH17

AH16

CORE_IF_VDDA_PLL

CORE_IF_GNDA_PLL

AD20

AE20

FSB_HF_VDDA_PLL

FSB_HF_GNDA_PLL

AD18

AE18

FSB_IF_VDDA_PLL

FSB_IF_GNDA_PLL

AH11

AG11

VDDA_RNG

GNDA_RNG

2.2UF

10%

6.3V

X5R

603

2

ST6R1

2

AH4

A7

B7

C6D4

10

IC

LOKI

2.2UF

10%

6.3V

X5R

603

2

1

C7R115

VDD_FSB0

VDD_FSB1

VDD_FSB2

VDD_FSB3

VDD_FSB4

VDD_FSB5

VDD_FSB6

VDD_FSB7

VDD_FSB8

VDD_FSB9

VDD_FSB10

VDD_FSB11

VDD_FSB12

VDD_FSB13

VDD_FSB14

VDD_FSB15

VDD_FSB16

VDD_FSB17

VDD_FSB18

VDD_FSB19

VDD_FSB20

VDD_FSB21

VDD_FSB22

VDD_FSB23

VDD_FSB24

VDD_FSB25

VDD_FSB26

VDD_FSB27

VDD_FSB28

VDD_FSB29

VDD_FSB30

VDD_FSB31

VDD_FSB32

VDD_FSB33

VDD_FSB34

AA25

AB24

AC25

AD24

AE25

AF24

AG25

AH24

B11

B15

B19

B23

B27

C24

D8

D12

D16

D20

D25

E24

F25

G24

H25

J24

K25

L24

M25

N24

P25

R24

T24

U25

V24

W25

Y24

SHORT

FB6R2

1

1

2

C6R3

1K

0.2A

0.7DCR

FB

603

.1UF

10%

6.3V

X5R

402

2

1

ST6R2

2

C6R5

2.2UF

10%

6.3V

X5R

603

X806937-001

SHORT

FB7D1

1

C7D1

1K

0.2A

0.7DCR

FB

603

1UF

10%

16V

EMPTY

603

2

1

ST7D1

2

C7D2

2.2UF

10%

6.3V

X5R

603

SHORT

[PAGE_TITLE=CPU,

FSB POWER + PLL

POWER]

DRAWING

FALCON_FABD

Tue May 08 18:24:09

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

6/82

REV

1.0

CR-7

@FALCON_LIB.FALCON(SCH_1):PAGE7

CPU,

V_CPUCORE

V_CPUCORE

IC

U7D1

5 of

V_CPUCORE

U7D1

10

6 of

LOKI

AA2

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB1

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC2

AC4

AC6

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD1

AD3

AD5

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD21

AD23

AE1

AE4

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

CORE POWER

10

V_CPUCORE

IC

V_CPUCORE

U7D1

AE6

AE8

AE10

AE12

AF4

AF7

AF10

AF13

AG3

AG6

AG9

AG12

G2

G4

G6

G8

G10

G12

G14

G16

G18

G20

G22

H1

H3

H5

H7

H9

H11

H13

H15

H17

H19

H21

H23

J2

J4

J6

J8

J10

J12

J14

J16

J18

J20

J22

K1

K3

K5

K7

K9

K11

K13

K15

K17

K19

K21

K23

L2

L4

L6

L8

L10

L12

L14

L16

L18

L20

L22

M1

M3

M5

M7

M9

M11

M13

M15

M17

M19

M21

M23

N2

N4

N6

N8

N10

N12

N14

N16

N18

N20

N22

P1

P3

P5

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD134

VDD135

VDD136

VDD137

VDD138

VDD139

VDD140

VDD141

VDD142

X806937-001

10

LOKI

LOKI

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD95

V_CPUVCS

IC

7 of

VDD143

VDD144

VDD145

VDD146

VDD147

VDD148

VDD149

VDD150

VDD151

VDD152

VDD153

VDD154

VDD155

VDD156

VDD157

VDD158

VDD159

VDD160

VDD161

VDD162

VDD163

VDD164

VDD165

VDD166

VDD167

VDD168

VDD169

VDD170

VDD171

VDD172

VDD173

VDD174

VDD175

VDD176

VDD177

VDD178

VDD179

VDD180

VDD181

VDD182

VDD183

VDD184

VDD185

VDD186

VDD187

VDD188

VDD189

P7

P9

P11

P13

P15

P17

P19

P21

P23

R2

R4

R6

R8

R10

R12

R14

R16

R18

R20

R22

T1

T3

T5

T7

T9

T11

T13

T15

T17

T19

T21

T23

U2

U4

U6

U8

U10

U12

U14

U16

U18

U20

U22

V1

V3

V5

V7

V9

V11

V13

V15

V17

V19

V21

V23

W2

W4

W6

W8

W10

W12

W14

W16

W18

W20

W22

Y1

Y3

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

VDD190

VDD191

VDD192

VDD193

VDD194

VDD195

VDD196

VDD197

VDD198

VDD199

VDD200

VDD201

VDD202

VDD203

VDD204

VDD205

VDD206

VDD207

VDD208

VDD209

VDD210

VDD211

VDD212

VDD213

VDD214

VDD215

VDD216

VDD217

VDD218

VDD219

VDD220

VCS0

VCS1

VCS2

VCS3

VCS4

VCS5

VCS6

VCS7

VCS8

VCS9

VCS10

VCS11

VCS12

VCS13

VCS14

VCS15

B1

B3

C1

C2

C3

D1

D3

D4

D5

E2

E4

E6

F1

F3

F5

F7

X806937-001

X806937-001

[PAGE_TITLE=CPU,

CORE POWER]

DRAWING

FALCON_FABD

Tue May 08 18:24:10

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

7/82

REV

1.0

CR-8

@FALCON_LIB.FALCON(SCH_1):PAGE8

CPU,

U7D1

9 of

10

U7D1

10

IC

10

LOKI

LOKI

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

IC

U7D1

IC

8 of

AA1

AA3

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AA24

AA26

AB2

AB4

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC1

AC3

AC5

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AC24

AC26

AD2

AD4

AD6

AD8

AD10

AD12

AE3

AE5

AE7

AE9

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AE24

AE26

POWER

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

AF3

AF6

AF9

AF12

AF15

AF16

AF18

AF19

AF21

AF22

AG4

AG7

AG10

AG13

AG15

AG16

AG18

AG19

AG21

AG22

AG24

AG26

B2

B9

B13

B17

B21

B25

B28

D2

D6

D10

D14

D18

D22

D24

D26

E1

E3

E5

E7

E9

E11

E13

E15

E17

E19

E21

E23

F2

F4

F6

F8

F10

F12

F14

F16

F18

F20

F22

F24

F26

G1

G3

G5

G7

G9

G11

G13

G15

G17

G19

G21

G23

H2

H4

H6

H8

H10

H12

H14

H16

H18

H20

H22

H24

H26

J1

J3

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K4

K6

K8

K10

K12

K14

K16

K18

K20

K22

K24

K26

L1

L3

L5

L7

L9

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

X806937-001

of

10

LOKI

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

L11

L13

L15

L17

L19

L21

L23

M2

M4

M6

M8

M10

M12

M14

M16

M18

M20

M22

M24

M26

N1

N3

N5

N7

N9

N11

N13

N15

N17

N19

N21

N23

P2

P4

P6

P8

P10

P12

P14

P16

P18

P20

P22

P24

P26

R1

R3

R5

R7

R9

R11

R13

R15

R17

R19

R21

R23

T2

T4

T6

T8

T10

T12

T14

T16

T18

T20

T22

U1

U3

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

U24

U26

V2

V4

V6

V8

V10

V12

V14

V16

V18

V20

V22

W1

W3

W5

W7

W9

W11

W13

W15

W17

W19

W21

W23

W24

W26

Y2

Y4

Y6

Y8

Y10

Y12

Y14

Y16

Y18

VSS291

VSS292

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

Y20

Y22

X806937-001

X806937-001

[PAGE_TITLE=CPU,

POWER]

DRAWING

FALCON_FABD

Tue May 08 18:24:10

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

8/82

REV

1.0

CR-9

@FALCON_LIB.FALCON(SCH_1):PAGE9

CPU,

V_CPUCORE

C7T94

4.7UF 10%

6.3V

EMPTY

805

C7T93

4.7UF 10%

6.3V

EMPTY

805

C7T33

4.7UF 10%

6.3V

X5R

805

C7R2

4.7UF 10%

6.3V

X5R

805

C7E10

C7T32

4.7UF 10%

6.3V

X5R

805

C7R26

4.7UF 10%

6.3V

X5R

805

C7E9

4.7UF 10%

6.3V

EMPTY

805

C7T1

4.7UF 10%

6.3V

X5R

805

C7T6

4.7UF 10%

6.3V

X5R

805

[PAGE_TITLE=CPU,

DECOUPLING]

C7E6

C7D12

4.7UF 10%

6.3V

X5R

805

C7D19

C7D3

4.7UF 10%

6.3V

X5R

805

4.7UF 10%

6.3V

EMPTY

805

C7E5

4.7UF 10%

6.3V

X5R

805

C7D5

4.7UF 10%

6.3V

EMPTY

805

C7R121

4.7UF 10%

6.3V

EMPTY

805

C7R23

4.7UF 10%

6.3V

X5R

805

C7R24

C7R3

4.7UF 10%

6.3V

X5R

805

4.7UF 10%

6.3V

X5R

805

C7E1

4.7UF 10%

6.3V

X5R

805

C7R119

4.7UF 10%

6.3V

EMPTY

805

C7R120

4.7UF 10%

6.3V

EMPTY

805

4.7UF 10%

6.3V

X5R

805

DECOUPLING

4.7UF 10%

6.3V

EMPTY

805

C7R90

4.7UF 10%

6.3V

X5R

805

C7E2

4.7UF 10%

6.3V

X5R

805

C7T83

4.7UF 10%

6.3V

X5R

805

C7D11

4.7UF 10%

6.3V

X5R

805

C7T84

4.7UF 10%

6.3V

X5R

805

C6T1

4.7UF 10%

6.3V

X5R

805

C7R30

4.7UF 10%

6.3V

X5R

805

C7R27

4.7UF 10%

6.3V

X5R

805

C7D8

4.7UF 10%

6.3V

X5R

805

C7D4

4.7UF 10%

6.3V

X5R

805

C7D18

4.7UF 10%

6.3V

EMPTY

805

C7D7

4.7UF 10%

6.3V

X5R

805

C7R91

C6R7

4.7UF 10%

6.3V

X5R

805

C6R10

4.7UF 10%

6.3V

X5R

805

C7R28

4.7UF 10%

6.3V

X5R

805

C7R29

4.7UF 10%

6.3V

X5R

805

C7T4

4.7UF 10%

6.3V

X5R

805

4.7UF 10%

6.3V

X5R

805

C7T5

4.7UF 10%

6.3V

X5R

805

C7R5

4.7UF 10%

6.3V

X5R

805

C7R4

4.7UF 10%

6.3V

X5R

805

C7R25

4.7UF 10%

6.3V

X5R

805

DRAWING

FALCON_FABD

Tue May 08 18:24:11

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

9/82

REV

1.0

CR-10

@FALCON_LIB.FALCON(SCH_1):PAGE10

CPU,

V_CPUCORE

C7R49

.1UF 10%

6.3V

X5R

402

C7R44

.1UF 10%

6.3V

X5R

402

C6R29

.1UF 10%

6.3V

X5R

402

C6R28

.1UF 10%

6.3V

X5R

402

C6R17

.1UF 10%

6.3V

X5R

402

C7R76

.1UF 10%

6.3V

X5R

402

C6R39

.1UF 10%

6.3V

X5R

402

C6R42

.1UF 10%

6.3V

X5R

402

C7R67

.1UF 10%

6.3V

X5R

402

C7T3

.1UF 10%

6.3V

X5R

402

[PAGE_TITLE=CPU,

DECOUPLING]

C7T9

.1UF 10%

6.3V

X5R

402

C7R22

.1UF 10%

6.3V

X5R

402

C7R35

.1UF 10%

6.3V

X5R

402

C7R34

.1UF 10%

6.3V

X5R

402

C7R19

.1UF 10%

6.3V

X5R

402

C7R43

.1UF 10%

6.3V

X5R

402

C6R16

.1UF 10%

6.3V

X5R

402

C6R19

.1UF 10%

6.3V

X5R

402

C7R61

.1UF 10%

6.3V

X5R

402

C6R35

.1UF 10%

6.3V

X5R

402

C6R44

.1UF 10%

6.3V

X5R

402

C6R32

.1UF 10%

6.3V

X5R

402

C7R102

.1UF 10%

6.3V

X5R

402

C7R81

.1UF 10%

6.3V

X5R

402

C7R68

.1UF 10%

6.3V

X5R

402

C7R69

.1UF 10%

6.3V

X5R

402

C7R57

.1UF 10%

6.3V

X5R

402

C6R20

.1UF 10%

6.3V

X5R

402

C6R21

.1UF 10%

6.3V

X5R

402

C6T26

.1UF 10%

6.3V

X5R

402

DECOUPLING

C7R52

.1UF 10%

6.3V

X5R

402

C7R51

.1UF 10%

6.3V

X5R

402

C7R50

.1UF 10%

6.3V

X5R

402

C6T6

.1UF 10%

6.3V

X5R

402

C6R36

.1UF 10%

6.3V

X5R

402

C6R23

.1UF 10%

6.3V

X5R

402

C7R58

.1UF 10%

6.3V

X5R

402

C7R59

.1UF 10%

6.3V

X5R

402

C7R60

.1UF 10%

6.3V

X5R

402

C7T2

.1UF 10%

6.3V

X5R

402

C6T10

.1UF 10%

6.3V

X5R

402

C7T22

.1UF 10%

6.3V

X5R

402

C7T27

.1UF 10%

6.3V

X5R

402

C7R48

.1UF 10%

6.3V

X5R

402

C7T51

C7T21

.1UF 10%

6.3V

X5R

402

C6T2

.1UF 10%

6.3V

X5R

402

C7T10

.1UF 10%

6.3V

X5R

402

C7R111

.1UF 10%

6.3V

X5R

402

.1UF 10%

6.3V

X5R

402

C7T37

.1UF 10%

6.3V

X5R

402

C7R89

.1UF 10%

6.3V

X5R

402

C6T25

.1UF 10%

6.3V

X5R

402

C7R99

.1UF 10%

6.3V

X5R

402

C7R100

.1UF 10%

6.3V

X5R

402

DRAWING

FALCON_FABD

Tue May 08 18:24:11

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

10/82

REV

1.0

CR-11

@FALCON_LIB.FALCON(SCH_1):PAGE11

CPU,

DECOUPLING

V_CPUCORE

V_CPUVCS

N:EMPTIES

1

C7R31

.1UF 10%

6.3V

X5R

402

C7T54

.1UF 10%

6.3V

X5R

402

C6T16

.1UF 10%

6.3V

X5R

402

C7R56

.1UF 10%

6.3V

X5R

402

C6R26

.1UF 10%

6.3V

X5R

402

C6T9

.1UF 10%

6.3V

X5R

402

C6T3

.1UF 10%

6.3V

X5R

402

C7R21

.1UF 10%

6.3V

X5R

402

C6R41

.1UF 10%

6.3V

X5R

402

C6R13

.1UF 10%

6.3V

X5R

402

[PAGE_TITLE=CPU,

C7T25

.1UF 10%

6.3V

X5R

402

C6T24

.1UF 10%

6.3V

X5R

402

C6T13

.1UF 10%

6.3V

X5R

402

C7R20

.1UF 10%

6.3V

X5R

402

C7R42

.1UF 10%

6.3V

X5R

402

C7R41

.1UF 10%

6.3V

X5R

402

C7R40

.1UF 10%

6.3V

X5R

402

C7R39

.1UF 10%

6.3V

X5R

402

C6T21

.1UF 10%

6.3V

X5R

402

C6R12

.1UF 10%

6.3V

X5R

402

DECOUPLING]

C7T38

.1UF 10%

6.3V

X5R

402

C7R110

.1UF 10%

6.3V

X5R

402

C6T14

.1UF 10%

6.3V

X5R

402

C7T28

.1UF 10%

6.3V

X5R

402

C7R14

.1UF 10%

6.3V

X5R

402

C7T49

.1UF 10%

6.3V

X5R

402

C6T22

.1UF 10%

6.3V

X5R

402

C7T41

.1UF 10%

6.3V

X5R

402

C7R33

.1UF 10%

6.3V

X5R

402

C7R32

.1UF 10%

6.3V

X5R

402

C7T58

.1UF 10%

6.3V

X5R

402

C6R24

.1UF 10%

6.3V

X5R

402

C7T56

.1UF 10%

6.3V

X5R

402

C7T50

.1UF 10%

6.3V

X5R

402

C7R106

.1UF 10%

6.3V

X5R

402

C7T11

.1UF 10%

6.3V

X5R

402

C7T40

.1UF 10%

6.3V

X5R

402

C7R75

.1UF 10%

6.3V

X5R

402

C7T47

.1UF 10%

6.3V

X5R

402

C7T46

.1UF 10%

6.3V

X5R

402

C6T17

.1UF 10%

6.3V

X5R

402

C7R95

.1UF 10%

6.3V

X5R

402

C6T18

.1UF 10%

6.3V

X5R

402

C7R101

.1UF 10%

6.3V

X5R

402

C7T57

.1UF 10%

6.3V

X5R

402

C7T55

.1UF 10%

6.3V

X5R

402

C7R83

.1UF 10%

6.3V

X5R

402

C7T39

.1UF 10%

6.3V

X5R

402

C7T26

.1UF 10%

6.3V

X5R

402

C7T48

.1UF 10%

6.3V

X5R

402

C7R66

.1UF 10%

6.3V

EMPTY

402

C6T4

.1UF 10%

6.3V

EMPTY

402

C7T15

.1UF 10%

6.3V

EMPTY

402

C7T24

.1UF 10%

6.3V

EMPTY

402

C6T11

.1UF 10%

6.3V

EMPTY

402

C7R74

.1UF 10%

6.3V

EMPTY

402

C6R30

.1UF 10%

6.3V

EMPTY

402

C7R82

.1UF 10%

6.3V

EMPTY

402

C7T23

.1UF 10%

6.3V

EMPTY

402

C7R65

.1UF 10%

6.3V

EMPTY

402

DRAWING

FALCON_FABD

Tue May 08 18:24:12

C7T7

.1UF 10%

6.3V

X5R

402

C7T14

.1UF 10%

6.3V

X5R

402

C7T12

.1UF 10%

6.3V

X5R

402

C7T13

C7T29

.1UF 10%

6.3V

X5R

402

C7T30

.1UF 10%

6.3V

X5R

402

C7T31

.1UF 10%

6.3V

X5R

402

.1UF 10%

6.3V

X5R

402

C7T8

.1UF 10%

6.3V

X5R

402

C7T16

.1UF 10%

6.3V

X5R

402

C7T17

.1UF 10%

6.3V

X5R

402

C7T18

.1UF 10%

6.3V

X5R

402

C7T19

.1UF 10%

6.3V

X5R

402

C7T20

.1UF 10%

6.3V

X5R

402

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

11/82

REV

1.0

CR-12

@FALCON_LIB.FALCON(SCH_1):PAGE12

V_MEM

GPU,

V_GPUCORE

R5C12 1

2

1K

402

R5R1

1K

402

1K

5%

CH

402

1

49.9

402

R4R9

GPU Y2

5%

CH

FSB_BYPCLK_DP

FSB_BYPCLK_DN

FSB_BYPCLK_SEL

B29

A29

D25

J34

J33

J30

J29

CP_GP0_CLK_DP

CP_GP0_CLK_DN

CP_GP0_FLAG_DP

CP_GP0_FLAG_DN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

FSB_CP_GP0_DATA0_DP

FSB_CP_GP0_DATA0_DN

FSB_CP_GP0_DATA1_DP

FSB_CP_GP0_DATA1_DN

FSB_CP_GP0_DATA2_DP

FSB_CP_GP0_DATA2_DN

FSB_CP_GP0_DATA3_DP

FSB_CP_GP0_DATA3_DN

FSB_CP_GP0_DATA4_DP

FSB_CP_GP0_DATA4_DN

FSB_CP_GP0_DATA5_DP

FSB_CP_GP0_DATA5_DN

FSB_CP_GP0_DATA6_DP

FSB_CP_GP0_DATA6_DN

FSB_CP_GP0_DATA7_DP

FSB_CP_GP0_DATA7_DN

M29

M30

L32

L31

K33

K34

L30

L29

J31

J32

K30

K29

H34

H33

H31

H32

CP_GP0_DATA0_DP

CP_GP0_DATA0_DN

CP_GP0_DATA1_DP

CP_GP0_DATA1_DN

CP_GP0_DATA2_DP

CP_GP0_DATA2_DN

CP_GP0_DATA3_DP

CP_GP0_DATA3_DN

CP_GP0_DATA4_DP

CP_GP0_DATA4_DN

CP_GP0_DATA5_DP

CP_GP0_DATA5_DN

CP_GP0_DATA6_DP

CP_GP0_DATA6_DN

CP_GP0_DATA7_DP

CP_GP0_DATA7_DN

5

5

5

5

IN

IN

IN

IN

FSB_CP_GP1_CLK_DP

FSB_CP_GP1_CLK_DN

FSB_CP_GP1_FLAG_DP

FSB_CP_GP1_FLAG_DN

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

FSB_CP_GP1_DATA0_DP

FSB_CP_GP1_DATA0_DN

FSB_CP_GP1_DATA1_DP

FSB_CP_GP1_DATA1_DN

FSB_CP_GP1_DATA2_DP

FSB_CP_GP1_DATA2_DN

FSB_CP_GP1_DATA3_DP

FSB_CP_GP1_DATA3_DN

FSB_CP_GP1_DATA4_DP

FSB_CP_GP1_DATA4_DN

FSB_CP_GP1_DATA5_DP

FSB_CP_GP1_DATA5_DN

FSB_CP_GP1_DATA6_DP

FSB_CP_GP1_DATA6_DN

FSB_CP_GP1_DATA7_DP

FSB_CP_GP1_DATA7_DN

1%

EMPTY

GPU

R5R3

R4R9

B13L

GUNGA

STUFF

EMPTY

EMPTY

STUFF

V33

V34

T33

T34

FSB_IMPED_CAL

FSB_IMPED_NCAL

R5R3

4.87K

1%

CH

402

1

2

VERSION

13

GP_CP0_CLK_DP

GP_CP0_CLK_DN

GP_CP0_FLAG_DP

GP_CP0_FLAG_DN

P33

P34

L34

L33

FSB_GP_CP0_CLK_DP

FSB_GP_CP0_CLK_DN

FSB_GP_CP0_FLAG_DP

FSB_GP_CP0_FLAG_DN

GP_CP0_DATA0_DP

GP_CP0_DATA0_DN

GP_CP0_DATA1_DP

GP_CP0_DATA1_DN

GP_CP0_DATA2_DP

GP_CP0_DATA2_DN

GP_CP0_DATA3_DP

GP_CP0_DATA3_DN

GP_CP0_DATA4_DP

GP_CP0_DATA4_DN

GP_CP0_DATA5_DP

GP_CP0_DATA5_DN

GP_CP0_DATA6_DP

GP_CP0_DATA6_DN

GP_CP0_DATA7_DP

GP_CP0_DATA7_DN

T29

T30

T31

T32

R34

R33

R29

R30

N34

N33

P29

P30

N31

N32

M34

M33

FSB_GP_CP0_DATA0_DP

FSB_GP_CP0_DATA0_DN

FSB_GP_CP0_DATA1_DP

FSB_GP_CP0_DATA1_DN

FSB_GP_CP0_DATA2_DP

FSB_GP_CP0_DATA2_DN

FSB_GP_CP0_DATA3_DP

FSB_GP_CP0_DATA3_DN

FSB_GP_CP0_DATA4_DP

FSB_GP_CP0_DATA4_DN

FSB_GP_CP0_DATA5_DP

FSB_GP_CP0_DATA5_DN

FSB_GP_CP0_DATA6_DP

FSB_GP_CP0_DATA6_DN

FSB_GP_CP0_DATA7_DP

FSB_GP_CP0_DATA7_DN

AA31

AA32

Y33

Y34

W30

W29

W33

W34

V29

V28

V31

V32

U33

U34

U30

U29

CP_GP1_DATA0_DP

CP_GP1_DATA0_DN

CP_GP1_DATA1_DP

CP_GP1_DATA1_DN

CP_GP1_DATA2_DP

CP_GP1_DATA2_DN

CP_GP1_DATA3_DP

CP_GP1_DATA3_DN

CP_GP1_DATA4_DP

CP_GP1_DATA4_DN

CP_GP1_DATA5_DP

CP_GP1_DATA5_DN

CP_GP1_DATA6_DP

CP_GP1_DATA6_DN

CP_GP1_DATA7_DP

CP_GP1_DATA7_DN

T28

AA28

FSB_IMPED_PCAL

FSB_IMPED_NCAL

OUT

OUT

OUT

OUT

5

5

5

5

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

GP_CP1_CLK_DP

GP_CP1_CLK_DN

GP_CP1_FLAG_DP

GP_CP1_FLAG_DN

AC33

AC34

Y29

Y30

FSB_GP_CP1_CLK_DP

FSB_GP_CP1_CLK_DN

FSB_GP_CP1_FLAG_DP

FSB_GP_CP1_FLAG_DN

OUT

OUT

OUT

OUT

5

5

5

5

GP_CP1_DATA0_DP

GP_CP1_DATA0_DN

GP_CP1_DATA1_DP

GP_CP1_DATA1_DN

GP_CP1_DATA2_DP

GP_CP1_DATA2_DN

GP_CP1_DATA3_DP

GP_CP1_DATA3_DN

GP_CP1_DATA4_DP

GP_CP1_DATA4_DN

GP_CP1_DATA5_DP

GP_CP1_DATA5_DN

GP_CP1_DATA6_DP

GP_CP1_DATA6_DN

GP_CP1_DATA7_DP

GP_CP1_DATA7_DN

AC28

AC29

AD29

AD30

AD34

AD33

AB29

AB30

AC32

AC31

AA29

AA30

AB33

AB34

AA34

AA33

FSB_GP_CP1_DATA0_DP

FSB_GP_CP1_DATA0_DN

FSB_GP_CP1_DATA1_DP

FSB_GP_CP1_DATA1_DN

FSB_GP_CP1_DATA2_DP

FSB_GP_CP1_DATA2_DN

FSB_GP_CP1_DATA3_DP

FSB_GP_CP1_DATA3_DN

FSB_GP_CP1_DATA4_DP

FSB_GP_CP1_DATA4_DN

FSB_GP_CP1_DATA5_DP

FSB_GP_CP1_DATA5_DN

FSB_GP_CP1_DATA6_DP

FSB_GP_CP1_DATA6_DN

FSB_GP_CP1_DATA7_DP

FSB_GP_CP1_DATA7_DN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

CP_GP1_CLK_DP

CP_GP1_CLK_DN

CP_GP1_FLAG_DP

CP_GP1_FLAG_DN

C2E4

IN

R2E5

0

402

.1UF 10%

6.3V

X5R

402

FSB_BYPCLK_DP

FSB_BYPCLK_DN

FSB_BYPCLK_SEL

FSB_CP_GP0_CLK_DP

FSB_CP_GP0_CLK_DN

FSB_CP_GP0_FLAG_DP

FSB_CP_GP0_FLAG_DN

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

V_GPUCORE

IC

1 OF 12

IN

IN

IN

IN

5

5

5

5

R5R2

U4D1

5%

CH

U2E2

R2R5

EMPTY

SN74LVC1G125

5

2

3

MEM_SCAN_EN_BUFF

VCC

IN

GND

OUT

OE_N

4

1

0

5%

CH

402

MEM_SCAN_EN

1

X801565-001

V_MEM

.1UF 10%

6.3V

X5R

402

13

IN

25

19

22

26

20

23

21

24

R4F8

1K

5%

CH

402

R2D11

1K

5%

CH

402

R2D12 2

0

402

OUT

C2R12

MEM SCAN BUFFERS

STUFFED

EMPTY

10K

0OHM

R2R5:

V_MEM

5%

CH

R5C11

1K

5%

EMPTY

402

FSB

5%

CH

U2D1

EMPTY

SN74LVC1G125

MEM_SCAN_TOP_EN_BUFF

5

2

3

VCC

IN

GND

OUT

OE_N

4

1

MEM_SCAN_TOP_EN

1

R4F7

X801565-001

OUT

19

25

21

23

OUT

20

26

22

24

1

1K

5%

CH

402

R2T2

1K

5%

CH

402

V_MEM

C4R70

X02125-001

1000PF

10%

50V

X7R

402

V_MEM

C2D5

1

0

402

.1UF 10%

6.3V

X5R

402

V_GPUCORE

13

FSB DECOUPLING

IN

R2R6

5%

CH

U2R1

EMPTY

SN74LVC1G125

MEM_SCAN_BOT_EN_BUFF

5

2

3

VCC

IN

GND

OUT

OE_N

R4U6

2

4

1

1K

5%

CH

402

R2T1

1K

5%

CH

402

MEM_SCAN_BOT_EN

X801565-001

C4R27

.1UF

10%

6.3V

X5R

402

[PAGE_TITLE=GPU,

FSB]

C4R33

.1UF

10%

6.3V

X5R

402

C4R45

.1UF

10%

6.3V

X5R

402

C4T22

.1UF

10%

6.3V

X5R

402

C5R18

.1UF

10%

6.3V

X5R

402

C4R65

.1UF

10%

6.3V

X5R

402

C4R60

.1UF

10%

6.3V

X5R

402

C4T13

.1UF

10%

6.3V

X5R

402

13

IN

DRAWING

FALCON_FABD

Tue May 08 18:24:13

GPU_SCAN_BUFF_EN_N

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

12/82

REV

1.0

CR-13

@FALCON_LIB.FALCON(SCH_1):PAGE13

GPU,

VIDEO

2 OF 12

U4D1

FT2P14

34

R5D1

562

402

27

27

PEX_SB_GPU_L1_DP

PEX_SB_GPU_L1_DN

PEX_SB_GPU_L0_DP

PEX_SB_GPU_L0_DN

IN

IN

IN

IN

PEX_PCAL

1%

CH

R5D2

V_GPUPCIE

2K

402

R4R3

1

1.47K

402

27

27

28

28

28

28

R5D2

R5D1

R4R3

2K, 1%

49.9,

1%

562,

1%

EMPTY

1.47K,

EMPTY

40.2

402

A25

A24

NB_CLK_DP

NB_CLK_DN

E11

RST_IN_N*

B27

A27

B23

A23

PEX_RX1_DP

PEX_RX1_DN

PEX_RX0_DP

PEX_RX0_DN

A28

B28

B21

PEX_PCAL

PEX_NCAL

PEX_ICAL

40.2,

240,

13

PIX_CLK_IN_DP

PIX_CLK_IN_DN

C22

C23

G14

G15

NB_THERMD_P

NB_THERMD_N

ED_THERMD_P

ED_THERMD_N

G16

R4R8

1

40.2

402

V_MEM

1.5K

1%

CH

402

SROM_SO

AG16

V8

GPU_TCLK

GPU_TDO

GPU_TDI

GPU_TMS

GPU_TRST

GPU_TRST_ED

MEM_CALA

MEM_CALB

E13

D12

E12

G12

G11

G13

34

OUT

PEX_GPU_SB_L1_DP_C

PEX_GPU_SB_L1_DN_C

PEX_GPU_SB_L0_DP_C

PEX_GPU_SB_L0_DN_C

GPU_PIX_CLK_1X

PIX_DATA<14..0>

B14

B17

A17

D16

B16

A16

D15

B15

A15

A14

D13

B13

A13

B12

A12

D11

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

A11

B11

SROM_EN_PSRO_OUT

SROM_SI

SROM_SCLK

SROM_CS

G17

E16

E15

E14

28

OUT

OUT

V_MEM

OUT

33

58

C4D2

PEX_GPU_SB_L1_DN

OUT

33

58

28

PEX_GPU_SB_L0_DP

OUT

33

58

C4D7

PEX_GPU_SB_L0_DN

OUT

33

58

.1UF 10%

6.3V

X5R

402

R4D1

C4D3

.1UF 10%

6.3V

X5R

402

1

1K

5%

EMPTY

402

DB4D1

TP

R4D2

GPU_VSYNC_OUT

GPU_HSYNC_OUT

VSYNC_OUT

HSYNC_OUT

PEX_GPU_SB_L1_DP

.1UF 10%

6.3V

X5R

402

28

OUT

28

OUT

GPU_SROM_EN_PSRO_OUT

GPU_SPI_SO

GPU_SPI_CLK

GPU_SPI_CS_N

1K

5%

CH

402

13

13

13

OUT

OUT

OUT

TCLK

TDO

TDI

TMS

TRST

TRST_ED

MEM_RST

MEM_SCAN_EN_BUFF

MEM_SCAN_TOP_EN_BUFF

MEM_SCAN_BOT_EN_BUFF

AG11

AN13

G9

G10

MEM_RST

MEM_SCAN_EN

MEM_SCAN_OEN_A

MEM_SCAN_OEN_B

OUT

OUT

OUT

OUT

2

20

19

12

12

12

21

22

23

24

25

26

R2E1

X02125-001

R2E2

B26

A26

B22

A22

C4D1

.1UF 10%

6.3V

X5R

402

MEM_CALB

1%

CH

V_MEM

FTP FT2P13

GPU_RST_DONE

D14

PIX_DATA14

PIX_DATA13

PIX_DATA12

PIX_DATA11

PIX_DATA10

PIX_DATA9

PIX_DATA8

PIX_DATA7

PIX_DATA6

PIX_DATA5

PIX_DATA4

PIX_DATA3

PIX_DATA2

PIX_DATA1

PIX_DATA0

MEM_CALA

1%

CH

D10

C10

34

GPU_SPI_SI

IN

IC

RST_DONE

1%

1%

IN

+ EEPROM + JTAG

PEX_TX1_DP

PEX_TX1_DN

PEX_TX0_DP

PEX_TX0_DN

R4R8

1%

1%

VERSION

PIX_CLK_OUT

GPU_TCLK_R

1%

CH

R4T1

R4T1

1% 40.2,

240,

R3C28 2

1.27K

402

1K

5%

CH

402

R4F6

1K

5%

CH

402

R2E4

J2D2

2X4HDR

1

3

5

7

1.5K

1%

CH

402

J5C2

HDR

2X3HDR

V_1P8

1

3

5

2

4

6

8

R2D10

PEX_NCAL

ANA_PIX_CLK_2X_DP

ANA_PIX_CLK_2X_DN

GPU_TEMP_P

GPU_TEMP_N

EDRAM_TEMP_P

EDRAM_TEMP_N

IN

IN

IN

OUT

IN

OUT

B13L

GUNGA

1%

CH

PEX_ICAL

1%

CH

GPU

GPU Y2

GPU_CLK_DP

GPU_CLK_DN

IN

IN

GPU_RST_N

IN

33

33

33

33

FTP

+ PCIEX

2

4

6

GPU_SPI_SI

GPU_SPI_WP_N

13

13

OUT

OUT

V_1P8

1

1

1.5K

1%

CH

402

R2E3

1.5K

1%

CH

402

13

13

IN

GPU_SPI_CLK

IN

GPU_SPI_SO

IN

GPU_SPI_CS_N

10K

5%

CH

402

R5P3

10K

5%

CH

402

+ PCIEX

5%

CH

R5C8

5%

CH

5%

CH

EMPTY

AT25020A

GPU_SPI_CLK_R

GPU_SPI_SO_R

GPU_SPI_CS_N_R

6

5

SCK

SDI

7

1

3

HOLD_N*

CS_N*

WP_N*

VCC

SDO

GND

C5C3

V_MEM

.1UF

10%

6.3V

X5R

402

VIDEO

GPU_SPI_SI

OUT

2

V_1P8

R4C6

R4C3

1K

402

R5C10

12

VIDEO

R5C5

1K

402

[PAGE_TITLE=GPU,

1

V_1P8

1K

402

OUT

10K

5%

CH

402

U4C1

13

GPU_SCAN_BUFF_EN_N

HDR

R4C7

R2D9

1.5K

1%

CH

402

X800552-001

2

10K

402

2

10K

402

R4C4

5%

CH

R4C5

1

1

5%

EMPTY

+ EEPROM + JTAG]

GPU_SPI_WP_N

IN

13

C3C2

4.7UF

10%

6.3V

X5R

805

DECOUPLING

C3R9

.1UF

10%

6.3V

X5R

402

C4R26

.1UF

10%

6.3V

X5R

402

C3R8

.1UF

10%

6.3V

X5R

402

10K

5%

CH

402

13

DRAWING

FALCON_FABD

Tue May 08 18:24:13

2007

MICROSOFT

CONFIDENTIAL

PROJECT NAME

FALCON_RETAIL

PAGE

13/82

REV

1.0

CR-14

@FALCON_LIB.FALCON(SCH_1):PAGE14

GPU,

U4D1

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

MA_DQ23

MA_DQ22

MA_DQ21

MA_DQ20

MA_DQ19

MA_DQ18

MA_DQ17

MA_DQ16

MA_WDQS2

MA_RDQS2

MA_DM2

AP15

AN15

AM15

AN14

AN16

AL13

AP17

AM13

AP14

AL15

AP16

MA_DQ23

MA_DQ22

MA_DQ21

MA_DQ20

MA_DQ19

MA_DQ18

MA_DQ17

MA_DQ16

MA_WDQS2

MA_RDQS2

MA_DM2

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

MA_DQ15

MA_DQ14

MA_DQ13

MA_DQ12

MA_DQ11

MA_DQ10

MA_DQ9

MA_DQ8

MA_WDQS1

MA_RDQS1

MA_DM1

AH16

AK20

AK16

AH20

AH17

AJ19

AJ18

AH18

AK19

AK17

AM17

MA_DQ15

MA_DQ14

MA_DQ13

MA_DQ12

MA_DQ11

MA_DQ10

MA_DQ9

MA_DQ8

MA_WDQS1

MA_RDQS1

MA_DM1

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

20 19

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

MA_DQ7

MA_DQ6

MA_DQ5

MA_DQ4

MA_DQ3

MA_DQ2

MA_DQ1

MA_DQ0

MA_WDQS0

MA_RDQS0

MA_DM0

AK15

AH11

AH15

AK11

AH13

AK12

AJ13

AH12

AM12

AJ14

AK14

MA_DQ7

MA_DQ6

MA_DQ5

MA_DQ4

MA_DQ3

MA_DQ2

MA_DQ1

MA_DQ0

MA_WDQS0

MA_RDQS0

MA_DM0

AK6

AP13

MA_VREF1

MA_VREF0

V_MEM

AP19

AN19

AL18

AN20

AN18

AM20

AN17

AL20

AP20

AM18

AP18

MA_DQ31

MA_DQ30

MA_DQ29

MA_DQ28

MA_DQ27

MA_DQ26

MA_DQ25

MA_DQ24

MA_WDQS3

MA_RDQS3

MA_DM3

1

549

1%

CH

402

.1UF

10%

6.3V

X5R

402

AH10

AK10

AN12

AP12

MA_A12

MA_A11

MA_A10

MA_A9

MA_A8

MA_A7

MA_A6

MA_A5

MA_A4

MA_A3

MA_A2

MA_A1

MA_A0

AN4

AP7

AP4

AP8

AN11

AP9

AN10

AP11

AN9

AN8

AN7

AN5

AP6

MA_BA2

MA_BA1

MA_BA0

AP10

AM10

AP5

MA_CKE

MA_WE_N*

MA_CAS_N*

MA_RAS_N*

MA_CS1_N*

MA_CS0_N*

AN6

AJ9

AK8

AK7

AK9

AL10

MA_CLK1_DP

MA_CLK1_DN

MA_CLK0_DP

MA_CLK0_DN

MA_A<12..0>

OUT

OUT

OUT

OUT

OUT

12

11

10

9

8

7

6

5

4

3

2

1

0

MA_BA<2..0>

2

1

0

MA_CKE

MA_WE_N

MA_CAS_N

MA_RAS_N

MA_CS1_N

MA_CS0_N

OUT

OUT

OUT

OUT

OUT

OUT

OUT

19

19

19

19

19

19

20

20

19

19

19

19

20

20

20

20

20

20

20

21

21

21

21

21

21

21

21

21

21

21

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

22

22

22

22

22

22

22

22

22

22

22

21

21

21

21

21

21

21

21

21

21

21

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

MB_DQ23

MB_DQ22

MB_DQ21

MB_DQ20

MB_DQ19

MB_DQ18

MB_DQ17

MB_DQ16

MB_WDQS2

MB_RDQS2

MB_DM2

AM23

AP23

AL23

AN23

AN25

AP22

AP25

AN21

AN22

AP24

AN24

MB_DQ23

MB_DQ22

MB_DQ21

MB_DQ20

MB_DQ19

MB_DQ18

MB_DQ17

MB_DQ16

MB_WDQS2

MB_RDQS2

MB_DM2

22

22

22

22

22

22

22

22

22

22

22

21

21

21

21

21

21

21

21

21

21

21

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

MB_DQ15

MB_DQ14

MB_DQ13

MB_DQ12

MB_DQ11

MB_DQ10

MB_DQ9

MB_DQ8

MB_WDQS1

MB_RDQS1

MB_DM1

AH26

AN32

AK26

AN31

AN29

AN30

AK28

AK29

AK30

AN28

AK27

MB_DQ15

MB_DQ14

MB_DQ13

MB_DQ12

MB_DQ11

MB_DQ10

MB_DQ9

MB_DQ8

MB_WDQS1

MB_RDQS1

MB_DM1

22

22

22

22

22

22

22

22

22

22

22

21

21

21

21

21

21

21

21

21

21

21

BI

BI

BI

BI

BI

BI

BI

BI

OUT

IN

OUT

MB_DQ7

MB_DQ6

MB_DQ5

MB_DQ4

MB_DQ3

MB_DQ2

MB_DQ1

MB_DQ0

MB_WDQS0

MB_RDQS0

MB_DM0

AK25

AH21

AH25

AK21

AH23

AK22

AJ23

AH22

AM22

AJ24

AK24

MB_DQ7

MB_DQ6

MB_DQ5

MB_DQ4

MB_DQ3

MB_DQ2

MB_DQ1

MB_DQ0

MB_WDQS0

MB_RDQS0

MB_DM0

AG33

AP21

MB_VREF1

MB_VREF0

V_MEM

MA_VREF1

IC

1

MB_CLK1_DP

MB_CLK1_DN

MB_CLK0_DP

MB_CLK0_DN

1.27K

1%

CH

402

MB_A12

MB_A11

MB_A10

MB_A9

MB_A8

MB_A7

MB_A6

MB_A5

MB_A4

MB_A3

MB_A2

MB_A1

MB_A0

AK32

AE29

AE34

AJ30

AK33

AJ33

AK34

AM32

AJ34

AE30

AF28

AE33

AF29

MB_BA2

MB_BA1

MB_BA0

AH30

AH33

AG30

MB_CKE

MB_WE_N*

MB_CAS_N*

MB_RAS_N*

MB_CS1_N*

MB_CS0_N*

AG34

AF33

AF32

AF31

AH34

AF34

1

MEMORY CONTROLLER A,

DECOUPLING

2

TO CHANGE GPU VREF, CHANGE THESE RESISTORS

R4T3,

R4T6,

R5E1, R4T5,

R4R5, R4R2, R4T2,

VALUE

[PAGE_TITLE=GPU,

1.27K

1%

CH

402

1

2

C4T45

.1UF

10%

6.3V

X5R

402

TO MATCH THE TABLE

R4R7

THESE ARE THE GPU VREFS NEEDED

FOR VARIOUS MEMORIES.

CONSULT

WITH MEM TEAM FOR USAGE.

C4R3

4.7UF

10%

6.3V

X5R

805

C4T29

.22UF

10%

6.3V

X5R

402

C4T32

C4T42

.22UF

10%

6.3V

X5R

402

.22UF

10%

6.3V

X5R

402

C4T44

R5E1

C5E1

.1UF

10%

6.3V

X5R

402

1.27K

1%

CH

402

.22UF

10%

6.3V

X5R

402

C4T27

.22UF

10%

6.3V

X5R

402

C4T41

.22UF

10%

6.3V

X5R

402

12

11

10

9

8

7

6

5

4

3

2

1

0

2

1

0

MB_BA<2..0>

MB_CKE

MB_WE_N

MB_CAS_N

MB_RAS_N

MB_CS1_N

MB_CS0_N

OUT

OUT

OUT

OUT

OUT

22

22

21

21

21

22

OUT

OUT

OUT

OUT

OUT

OUT

OUT

21

21

21

21

21

21

21

22

22

22

22

22

22

MEMORY CONTROLLER B,

DECOUPLING

C4T47

549

1%

CH

402

4.7UF

10%

6.3V

X5R

805

C4T31

.22UF

10%

6.3V

X5R

402

C4T34

.22UF

10%

6.3V

X5R

402

C5T2

.22UF

10%

6.3V

X5R

402

C4T39

.22UF

10%

6.3V

X5R

402

MB_VREF0

.22UF

10%

6.3V

X5R

402

R4T5

C4T35

MB_CLK1_DP

MB_CLK1_DN

MB_CLK0_DP

MB_CLK0_DN

MB_A<12..0>

R4T8

V_MEM

MA_VREF0

R4T6

V_MEM

MB_VREF1

549

1%

CH

402

AM33

AM34

AL33

AL34

V_MEM

549

1%

CH

402

R4T7

RESISTOR