Beruflich Dokumente

Kultur Dokumente

Sathyabama University: Register Number

Hochgeladen von

nksarathy0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

8 Ansichten2 SeitenSathaya Bama UNIV QP

Originaltitel

205125-235456-782103-SECX5018

Copyright

© © All Rights Reserved

Verfügbare Formate

DOC, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenSathaya Bama UNIV QP

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOC, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

8 Ansichten2 SeitenSathyabama University: Register Number

Hochgeladen von

nksarathySathaya Bama UNIV QP

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOC, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 2

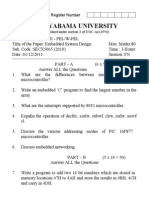

Register Number

SATHYABAMA UNIVERSITY

(Established under section 3 of UGC Act,1956)

Course & Branch :M.E - EMBED/VLSI/W-VLSI

Title of the Paper :VLSI Design

Max. Marks :80

Sub. Code :782103-SECX5018

Time : 3 Hours

Date :27/05/2011

Session :AN

______________________________________________________________________________________________________________________

1.

PART - A

(6 x 5 = 30)

Answer ALL the Questions

Compare CMOS and Bipolar technologies.

2.

Write the design rules for NMOS logic.

3.

What do you mean by steering logic design?

4.

What is clocked CMOS logic?

5.

What is true single phase clock (TSPC) latches and flip flops?

6.

Write about barrel shifter.

7.

8.

PART B

(5 x 10 = 50)

Answer ALL the Questions

Derive the expression for threshold voltage and drain current for

MOS transistor.

(or)

What are the secondary effects of an MOS transistor? Explain in

detail about threshold voltage-body effect and channel length

modulation.

9.

Explain with neat diagram the various CMOS inverter logic

levels.

(or)

10. Explain a combinational logic design implementation using

CMOS and NMOS inverters with suitable example.

11. Explain about Programmable logic arrays with the AND/OR and

AND/NOR representations.

(or)

12. With the neat diagram explain about dynamic MOS storage

circuits.

13. Explain in detail about traditional domino circuits and skew

tolerant domino circuits.

(or)

14. Explain in detail the design standards and advantages of NORA

CMOS.

15. Explain the booth algorithm and how it is implemented in

multiplication.

(or)

16. Write the different standards used to perform addition operation

and explain about 4 bit Manchester adder.

Das könnte Ihnen auch gefallen

- VLSI Design exam questionsDokument2 SeitenVLSI Design exam questionsnksarathyNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberlavanyachandranNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument2 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)Vidya MuthukrishnanNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument2 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)Monica MorinNoch keine Bewertungen

- Sathyabama University Question PaperDokument2 SeitenSathyabama University Question PaperamiestudentNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumbervempadareddyNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberGoverdhan GovaNoch keine Bewertungen

- Register Number and Aerodynamics ExamDokument2 SeitenRegister Number and Aerodynamics ExamBalaji RakeshNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberVijay VivegananthanNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberAmmuRaNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberVinoth SudalaiNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberVinoth SudalaiNoch keine Bewertungen

- Elements of Aeronatics Sathyabama PDFDokument2 SeitenElements of Aeronatics Sathyabama PDFsenthilkumareceNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument2 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)Mahendranath RamakrishnanNoch keine Bewertungen

- 18-M.Tech (VLSI Design and Embedded System) PDFDokument31 Seiten18-M.Tech (VLSI Design and Embedded System) PDFAhilan AppathuraiNoch keine Bewertungen

- sathyabama-IIsem-Advanced Internet Technology-683203-783202Dokument2 Seitensathyabama-IIsem-Advanced Internet Technology-683203-783202ShankarNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument2 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)Mahendranath RamakrishnanNoch keine Bewertungen

- Women's Institute VLSI Seminar ReportDokument21 SeitenWomen's Institute VLSI Seminar ReportSravan VannadiNoch keine Bewertungen

- Final OS BISOS304Dokument3 SeitenFinal OS BISOS304suneetha prabhuNoch keine Bewertungen

- Mca 4th AssignDokument9 SeitenMca 4th AssignSmriti SinghNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument2 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)Anonymous TxPyX8cNoch keine Bewertungen

- Real Time Embedded Systems Exam QuestionsDokument1 SeiteReal Time Embedded Systems Exam QuestionsJesebel James DennisNoch keine Bewertungen

- C-chart analysis of missing rivets in busesDokument1 SeiteC-chart analysis of missing rivets in busesdaksh shuklaNoch keine Bewertungen

- EE411: Introduction To VLSI Design Course SyllabusDokument9 SeitenEE411: Introduction To VLSI Design Course SyllabusSohail MashwaniNoch keine Bewertungen

- M.E VlsiDokument25 SeitenM.E VlsiDurai SelvanNoch keine Bewertungen

- BOLJAT - A Tool For Designing Composite Bolted Joints Using Three-Dimensional Finite Element AnalysisDokument42 SeitenBOLJAT - A Tool For Designing Composite Bolted Joints Using Three-Dimensional Finite Element AnalysisdzsergeyNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberAshok KumarNoch keine Bewertungen

- Vlsi Design ECE5014Dokument5 SeitenVlsi Design ECE5014SriramNoch keine Bewertungen

- BCA (3) Assignment - 2011Dokument4 SeitenBCA (3) Assignment - 2011Chinmay KamilaNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register NumberAmmuRaNoch keine Bewertungen

- Semester V: 1. Explain What Is CMOS VLSI? and Current and Future Trends in VLSIDokument3 SeitenSemester V: 1. Explain What Is CMOS VLSI? and Current and Future Trends in VLSIlokeahaNoch keine Bewertungen

- MEVD-102 CMOS VLSI Design DEC 2010Dokument1 SeiteMEVD-102 CMOS VLSI Design DEC 2010Prakash SinhaNoch keine Bewertungen

- Mech3403 2013 Sem-1 CrawleyDokument9 SeitenMech3403 2013 Sem-1 CrawleyTamsin VenterNoch keine Bewertungen

- Satthyabama-Isem-Data Comunication and Computer Networks 6C0500-7C0500Dokument2 SeitenSatthyabama-Isem-Data Comunication and Computer Networks 6C0500-7C0500ShankarNoch keine Bewertungen

- Models and Analysis for Distributed SystemsVon EverandModels and Analysis for Distributed SystemsSerge HaddadNoch keine Bewertungen

- VLSI Lab CompendiumDokument52 SeitenVLSI Lab CompendiumSaad Ali Khan SherwaniNoch keine Bewertungen

- Introduction To Model Order ReductionDokument31 SeitenIntroduction To Model Order ReductionSrinivas AcharyaNoch keine Bewertungen

- VLSI Design Paper Code and UnitsDokument2 SeitenVLSI Design Paper Code and UnitsarupNoch keine Bewertungen

- SCHEME - G Fifth Semester (CO)Dokument42 SeitenSCHEME - G Fifth Semester (CO)RazeenKhanNoch keine Bewertungen

- Course Plan VLSI Design July 2013Dokument4 SeitenCourse Plan VLSI Design July 2013HacraloNoch keine Bewertungen

- Eitex: Very ShortDokument4 SeitenEitex: Very Shortkathirvelus9408Noch keine Bewertungen

- Embedded Systems: Analysis and Modeling with SysML, UML and AADLVon EverandEmbedded Systems: Analysis and Modeling with SysML, UML and AADLFabrice KordonNoch keine Bewertungen

- MACHINEDESIGNDokument35 SeitenMACHINEDESIGNBrandon AllenNoch keine Bewertungen

- Exam Cell Automation System: Brundhaelcij@vemanait - Edu.inDokument5 SeitenExam Cell Automation System: Brundhaelcij@vemanait - Edu.inAarush VermaNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument3 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)Senthilkumar PachiyappanNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument2 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)yaswanthmalaikaniNoch keine Bewertungen

- OutlineDokument1 SeiteOutlineVarg VikernesNoch keine Bewertungen

- Industrial Electronics SylubusDokument5 SeitenIndustrial Electronics SylubusganeshrpujarNoch keine Bewertungen

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Dokument2 SeitenSathyabama University: (Established Under Section 3 of UGC Act, 1956)Parthipan JayaramNoch keine Bewertungen

- A 10-Year Mechatronics Curriculum Development - Part-II - IEEEDokument7 SeitenA 10-Year Mechatronics Curriculum Development - Part-II - IEEEFatima AhsanNoch keine Bewertungen

- Structured Design Methods For MEMS Final Report: A Workshop Sponsored by The National Science FoundationDokument131 SeitenStructured Design Methods For MEMS Final Report: A Workshop Sponsored by The National Science FoundationMangey Ram NagarNoch keine Bewertungen

- Web Tech Course FileDokument213 SeitenWeb Tech Course FileDevein BediNoch keine Bewertungen

- Embedded Mechatronic Systems, Volume 1: Analysis of Failures, Predictive ReliabilityVon EverandEmbedded Mechatronic Systems, Volume 1: Analysis of Failures, Predictive ReliabilityNoch keine Bewertungen

- COMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Dokument3 SeitenCOMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Binte ZahraNoch keine Bewertungen

- Damage Mechanics in Metal Forming: Advanced Modeling and Numerical SimulationVon EverandDamage Mechanics in Metal Forming: Advanced Modeling and Numerical SimulationNoch keine Bewertungen

- Previous Question Papers For Four Year B. Tech I Semester Regular Examinations February 2012Dokument20 SeitenPrevious Question Papers For Four Year B. Tech I Semester Regular Examinations February 2012prasaad08Noch keine Bewertungen

- CS Syllabus 2012 Admissions OnwardsDokument78 SeitenCS Syllabus 2012 Admissions OnwardsAnurag DeterminedNoch keine Bewertungen

- Sathyabama University: Register NumberDokument2 SeitenSathyabama University: Register Number1balamanianNoch keine Bewertungen

- M.E.VLSI DesignDokument43 SeitenM.E.VLSI DesignThahsin ThahirNoch keine Bewertungen

- 2b WLANDokument59 Seiten2b WLANnksarathyNoch keine Bewertungen

- Prerana EC - RevampedDokument1 SeitePrerana EC - RevampednksarathyNoch keine Bewertungen

- SPDP Scheme Document - SC ST StudentsDokument2 SeitenSPDP Scheme Document - SC ST StudentsnksarathyNoch keine Bewertungen

- Wireless Lans and Ieee 802.11 Mac: Cse 6590 Winter 2012Dokument59 SeitenWireless Lans and Ieee 802.11 Mac: Cse 6590 Winter 2012nksarathyNoch keine Bewertungen

- M.E.VLSI DesignDokument43 SeitenM.E.VLSI DesignThahsin ThahirNoch keine Bewertungen

- Introduction and Overview: - Course ContentDokument20 SeitenIntroduction and Overview: - Course ContentnksarathyNoch keine Bewertungen

- Evs P - IDokument1 SeiteEvs P - InksarathyNoch keine Bewertungen