Beruflich Dokumente

Kultur Dokumente

Difference Between SRAM & DRAM

Hochgeladen von

my_scribd_docs90%(21)90% fanden dieses Dokument nützlich (21 Abstimmungen)

36K Ansichten2 SeitenEach cell which can store a single bit requires a capacitor (which stores bit as charge) and a transistor. Transistors. 3. Does not need to be refreshed 3. Needs to be refreshed every periodically as flips flops retain few milliseconds to retain data the data. 5. Low density / less memory per due to more circuitry of the capacitor leaks. 4. Slower access time compared to 6. More costly in terms of cost per bit compared to DRAM due to low chip density. Being refreshed.

Originalbeschreibung:

Copyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

DOCX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenEach cell which can store a single bit requires a capacitor (which stores bit as charge) and a transistor. Transistors. 3. Does not need to be refreshed 3. Needs to be refreshed every periodically as flips flops retain few milliseconds to retain data the data. 5. Low density / less memory per due to more circuitry of the capacitor leaks. 4. Slower access time compared to 6. More costly in terms of cost per bit compared to DRAM due to low chip density. Being refreshed.

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

90%(21)90% fanden dieses Dokument nützlich (21 Abstimmungen)

36K Ansichten2 SeitenDifference Between SRAM & DRAM

Hochgeladen von

my_scribd_docsEach cell which can store a single bit requires a capacitor (which stores bit as charge) and a transistor. Transistors. 3. Does not need to be refreshed 3. Needs to be refreshed every periodically as flips flops retain few milliseconds to retain data the data. 5. Low density / less memory per due to more circuitry of the capacitor leaks. 4. Slower access time compared to 6. More costly in terms of cost per bit compared to DRAM due to low chip density. Being refreshed.

Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 2

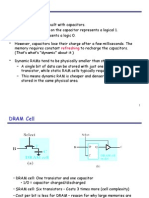

Difference between Static RAM & Dynamic RAM

SRAM DRAM

1. Stores bits in memory cells 1. Memory cells are composed of

composed of flip flops. capacitors and transistors.

2. Each cell which can store a 2. Each cell requires a capacitor

single bit requires six (which stores bit as charge) & a

transistors. transistor.

3. Does not need to be refreshed 3. Needs to be refreshed every

periodically as flips flops retain few milliseconds to retain data

the data. because the charge of the

4. Faster access time compared to capacitor leaks.

DRAM, therefore used as caches 4. Slower access time compared to

mostly. SRAM as it cannot be read while

5. Low density/less memory per being refreshed.

chip due to more circuitry 5. High chip density/more memory

required for a single cell. per chip compared to SRAM due

6. More power consumption than to less circuitry for a single cell.

DRAM because of low chip 6. Less power consumption than

density. SRAM because of simple

7. More costly in terms of cost per circuitry.

bit compared to DRAM due to 7. Less costly than SRAM because

low chip density. of high chip density and

therefore used as main memory

in PCs.

Das könnte Ihnen auch gefallen

- Sram and Dram: by Hy, Khanh, Minh, TR - My and NgôDokument6 SeitenSram and Dram: by Hy, Khanh, Minh, TR - My and NgôLTHNoch keine Bewertungen

- Single Phase Two Wire, Split STS Prepaid/AMI Smart Meter: HighlightsDokument2 SeitenSingle Phase Two Wire, Split STS Prepaid/AMI Smart Meter: HighlightsElisiö Dicälä Homem da LéiNoch keine Bewertungen

- Huawei Smart Logger 2000 DatasheetDokument3 SeitenHuawei Smart Logger 2000 DatasheetAzree Mohd NoorNoch keine Bewertungen

- Adjust eight-wheel trolley wheels with ZPMC documentDokument3 SeitenAdjust eight-wheel trolley wheels with ZPMC documenttest testtNoch keine Bewertungen

- Perangkat PACDokument32 SeitenPerangkat PACDedy SetiawanNoch keine Bewertungen

- Difference Between SRAM DRAMDokument2 SeitenDifference Between SRAM DRAMSneha PalNoch keine Bewertungen

- Difference Between Static RAM & Dynamic RAM: Sram DramDokument1 SeiteDifference Between Static RAM & Dynamic RAM: Sram DramYogesh Kumar DewanganNoch keine Bewertungen

- Difference Between Static RAM & Dynamic RAM: Sram DramDokument4 SeitenDifference Between Static RAM & Dynamic RAM: Sram Dramamol maliNoch keine Bewertungen

- What Is A Neural Network?Dokument3 SeitenWhat Is A Neural Network?Abhisek SarkarNoch keine Bewertungen

- SRAM and DRAMDokument2 SeitenSRAM and DRAMBiju AngaleesNoch keine Bewertungen

- Computer Memory Is A Temporary Storage AreaDokument3 SeitenComputer Memory Is A Temporary Storage AreaMilitary BaseNoch keine Bewertungen

- Group ReportDokument10 SeitenGroup ReportDK SevenNoch keine Bewertungen

- Random Access MemoryDokument37 SeitenRandom Access MemorysalmanabkpNoch keine Bewertungen

- Coa Unit-4Dokument27 SeitenCoa Unit-4singhshiva8082Noch keine Bewertungen

- Lecture 15Dokument19 SeitenLecture 157t854s6wd2Noch keine Bewertungen

- Dynamic Memory Refreshes CapacitorsDokument8 SeitenDynamic Memory Refreshes CapacitorsNava KrishnanNoch keine Bewertungen

- 20BSCS010 Presentation of Types of RamDokument18 Seiten20BSCS010 Presentation of Types of RamAmeer JaanNoch keine Bewertungen

- Memory Related To VLSIDokument63 SeitenMemory Related To VLSIIndrajeet GautamNoch keine Bewertungen

- UNIT 2 Managing Storage DevicesDokument34 SeitenUNIT 2 Managing Storage Devicesprashantkumarmuz2004Noch keine Bewertungen

- Chapter (4) Upgrading MemoryDokument80 SeitenChapter (4) Upgrading MemoryGame TekaNoch keine Bewertungen

- What Are The Differences Between SRAM and Dram?Dokument1 SeiteWhat Are The Differences Between SRAM and Dram?yaheewNoch keine Bewertungen

- Unit 5 Memory OrganizationDokument104 SeitenUnit 5 Memory OrganizationNarsingh Pal YadavNoch keine Bewertungen

- Refreshing capacitors in DRAM memory cellsDokument8 SeitenRefreshing capacitors in DRAM memory cellsTuan Anh NguyenNoch keine Bewertungen

- How RAM Works 28 by NafeesDokument10 SeitenHow RAM Works 28 by NafeesnafeesNoch keine Bewertungen

- E2805 B 43Dokument4 SeitenE2805 B 43Verma JagdeepNoch keine Bewertungen

- Ca Unit 5 PrabuDokument37 SeitenCa Unit 5 Prabu6109 Sathish Kumar JNoch keine Bewertungen

- How RAM WorksDokument9 SeitenHow RAM WorksPablo Miguel FelsteadNoch keine Bewertungen

- Difference Between Static and Dynamic RAMDokument2 SeitenDifference Between Static and Dynamic RAMMamun RassalNoch keine Bewertungen

- "Memory Interface" in (Microprocessor Systems and Interfacing)Dokument22 Seiten"Memory Interface" in (Microprocessor Systems and Interfacing)MUHAMMAD ABDULLAHNoch keine Bewertungen

- Ram & Rom: Random Access MemoryDokument3 SeitenRam & Rom: Random Access MemoryRudra ShrikumarNoch keine Bewertungen

- Chapter 4 Memory ElementDokument87 SeitenChapter 4 Memory ElementWann FarieraNoch keine Bewertungen

- Computer Hardware Image GalleryDokument7 SeitenComputer Hardware Image Gallerymathur1995Noch keine Bewertungen

- "Memory Interface" in (Microprocessor and Assembly Language)Dokument22 Seiten"Memory Interface" in (Microprocessor and Assembly Language)MUHAMMAD ABDULLAHNoch keine Bewertungen

- Types of RAMDokument2 SeitenTypes of RAMAdrian BarrenoNoch keine Bewertungen

- Primary MemoryDokument20 SeitenPrimary MemoryAayushmanNoch keine Bewertungen

- Chapter 2Dokument66 SeitenChapter 2mayazyounasNoch keine Bewertungen

- Computer Memory2Dokument8 SeitenComputer Memory2Rajeev DebnathNoch keine Bewertungen

- Capter 10Dokument35 SeitenCapter 10Roha CbcNoch keine Bewertungen

- Dram VS SramDokument2 SeitenDram VS SramEvan SubediNoch keine Bewertungen

- RAMDokument9 SeitenRAMSourin SahaNoch keine Bewertungen

- Different Types of MemoryDokument34 SeitenDifferent Types of MemoryPirapuraj PonnampalamNoch keine Bewertungen

- SRAM&DRAMDokument8 SeitenSRAM&DRAMSayan SarkarNoch keine Bewertungen

- Semiconductor Memory DesignDokument27 SeitenSemiconductor Memory Designkavita_1992Noch keine Bewertungen

- EC304Dokument14 SeitenEC304api-3853441Noch keine Bewertungen

- Memory OrganizationDokument70 SeitenMemory OrganizationrahqansayeedNoch keine Bewertungen

- Piyush PPT of ZRAMDokument16 SeitenPiyush PPT of ZRAMPiyush SharmaNoch keine Bewertungen

- Memory DevicesDokument20 SeitenMemory DevicesMD AZIZUL HOQUENoch keine Bewertungen

- Microsoft Office Word Document جديد (3) Dokument3 SeitenMicrosoft Office Word Document جديد (3) anon_21074691Noch keine Bewertungen

- 04 - Internal Memory - StudDokument17 Seiten04 - Internal Memory - Studtipu tipuNoch keine Bewertungen

- William Stallings Computer Organization and Architecture 7th Edition Internal MemoryDokument37 SeitenWilliam Stallings Computer Organization and Architecture 7th Edition Internal Memoryagustin92Noch keine Bewertungen

- RAM & Its TypesDokument4 SeitenRAM & Its TypesdoferiNoch keine Bewertungen

- Volatile Memory - WikipediaDokument5 SeitenVolatile Memory - WikipediaAhmed IlyasNoch keine Bewertungen

- Memory System Design and CharacteristicsDokument87 SeitenMemory System Design and CharacteristicsrajkumarNoch keine Bewertungen

- Reading Practice A. Read The Following Text: Computer - MemoryDokument6 SeitenReading Practice A. Read The Following Text: Computer - MemoryMiele Jm-Noch keine Bewertungen

- Random Access MemoryDokument2 SeitenRandom Access MemoryジョージNoch keine Bewertungen

- Computer Assignment 1Dokument6 SeitenComputer Assignment 1Muhammad Hassnain AhmadNoch keine Bewertungen

- Memory Hierarchy Levels: Block (Aka Line) : Unit of Copying If Accessed Data Is Present in Upper LevelDokument16 SeitenMemory Hierarchy Levels: Block (Aka Line) : Unit of Copying If Accessed Data Is Present in Upper LevelalexNoch keine Bewertungen

- Types of MemoryDokument14 SeitenTypes of MemorySriram RamakrishnanNoch keine Bewertungen

- Presentation1 LOCDokument10 SeitenPresentation1 LOCanjliNoch keine Bewertungen

- Fujitsu - Virtualization and Softwarization Technologies For End-To-End NetworkingDokument10 SeitenFujitsu - Virtualization and Softwarization Technologies For End-To-End Networkingmy_scribd_docsNoch keine Bewertungen

- Recommendations On Introducing Virtual Network Operators in Telecom Sector' - TRA IndiaDokument75 SeitenRecommendations On Introducing Virtual Network Operators in Telecom Sector' - TRA Indiamy_scribd_docsNoch keine Bewertungen

- Network Virtualization - A View From The BottomDokument8 SeitenNetwork Virtualization - A View From The Bottommy_scribd_docsNoch keine Bewertungen

- Is Pluto a Planet DebateDokument30 SeitenIs Pluto a Planet Debatemy_scribd_docsNoch keine Bewertungen

- The Hubble Space Telescope Advanced Camera For Surveys Coma Cluster SurveyDokument49 SeitenThe Hubble Space Telescope Advanced Camera For Surveys Coma Cluster Surveymy_scribd_docsNoch keine Bewertungen

- The Hubble Space Telescope Advanced Camera For Surveys Coma Cluster SurveyDokument49 SeitenThe Hubble Space Telescope Advanced Camera For Surveys Coma Cluster Surveymy_scribd_docsNoch keine Bewertungen

- The Milky Way and Other GalaxiesDokument4 SeitenThe Milky Way and Other Galaxiesmy_scribd_docsNoch keine Bewertungen

- Pluto and Charon With The Hubble Space Telescope. Ii. Resolving Changes On Pluto's Surface and A Map For CharonDokument16 SeitenPluto and Charon With The Hubble Space Telescope. Ii. Resolving Changes On Pluto's Surface and A Map For Charonmy_scribd_docsNoch keine Bewertungen

- Dynamic PlanetDokument9 SeitenDynamic Planetmy_scribd_docsNoch keine Bewertungen

- Trax 2 GuideDokument12 SeitenTrax 2 Guidemy_scribd_docsNoch keine Bewertungen

- Evidence of Recent Flows of Liquid Water On The Surface of MarsDokument2 SeitenEvidence of Recent Flows of Liquid Water On The Surface of Marsmy_scribd_docsNoch keine Bewertungen

- Vanadium DioxideDokument25 SeitenVanadium Dioxidemy_scribd_docsNoch keine Bewertungen

- I Grill 3Dokument19 SeitenI Grill 3my_scribd_docsNoch keine Bewertungen

- Is Pluto a Planet DebateDokument30 SeitenIs Pluto a Planet Debatemy_scribd_docsNoch keine Bewertungen

- Windows 98/NT Keyboard ShortcutsDokument5 SeitenWindows 98/NT Keyboard Shortcutsmy_scribd_docsNoch keine Bewertungen

- Latin Route WordsDokument38 SeitenLatin Route Wordsemiliow_1Noch keine Bewertungen

- Introduction To Vi: Dr. Mike MurphyDokument9 SeitenIntroduction To Vi: Dr. Mike Murphymy_scribd_docsNoch keine Bewertungen

- Ac SystemDokument37 SeitenAc SystemButnaru EmanuelNoch keine Bewertungen

- Message-Passing Interface For Microsoft Windows 3.1Dokument70 SeitenMessage-Passing Interface For Microsoft Windows 3.1my_scribd_docsNoch keine Bewertungen

- Turabian GuideDokument18 SeitenTurabian Guidemy_scribd_docsNoch keine Bewertungen

- Hypertension in Children and AdolescentsDokument39 SeitenHypertension in Children and Adolescentsmy_scribd_docsNoch keine Bewertungen

- Dell Latitude E5430/E5530Dokument8 SeitenDell Latitude E5430/E5530my_scribd_docsNoch keine Bewertungen

- NS Tutorial: Mobile and Wireless Network Simulation: Ya Xu Usc/Isi September 10th, 1999Dokument36 SeitenNS Tutorial: Mobile and Wireless Network Simulation: Ya Xu Usc/Isi September 10th, 1999gssaini99Noch keine Bewertungen

- Lumia With Windows 10 UG en USDokument137 SeitenLumia With Windows 10 UG en USNasreen HakimNoch keine Bewertungen

- Assistive Technology SoftwareDokument5 SeitenAssistive Technology Softwaremy_scribd_docsNoch keine Bewertungen

- Blood PressureDokument60 SeitenBlood PressureEnerolisa ParedesNoch keine Bewertungen

- Automotive Air Conditioning Training ManualDokument88 SeitenAutomotive Air Conditioning Training ManualSyful Amadeus100% (4)

- Four-Stroke Engine BasicsDokument14 SeitenFour-Stroke Engine Basicsha naNoch keine Bewertungen

- Children Are Not Little AdultsDokument40 SeitenChildren Are Not Little AdultsSolomon AmosNoch keine Bewertungen

- Fundamentals of HVAC ControlsDokument68 SeitenFundamentals of HVAC Controlsbenson100% (2)

- Preventive MaintenanceDokument19 SeitenPreventive Maintenancefaizan9970% (1)

- 1 Gaona BrianDokument218 Seiten1 Gaona BrianElias Nicol100% (1)

- 489-F Latest JudgmentDokument15 Seiten489-F Latest JudgmentMoving StepNoch keine Bewertungen

- LOGIC - Key Concepts of Propositions, Arguments, Deductive & Inductive ReasoningDokument83 SeitenLOGIC - Key Concepts of Propositions, Arguments, Deductive & Inductive ReasoningMajho Oaggab100% (2)

- PH.D Scholars List 01022016Dokument64 SeitenPH.D Scholars List 01022016vishalNoch keine Bewertungen

- Scan To Folder Easy Setup GuideDokument20 SeitenScan To Folder Easy Setup GuideJuliana PachecoNoch keine Bewertungen

- Wonderland Staking and Minting Calculator (4,4)Dokument8 SeitenWonderland Staking and Minting Calculator (4,4)Dina Maya0% (4)

- 2018 CML Updates and Case Presentations: Washington University in ST Louis Medical SchoolDokument113 Seiten2018 CML Updates and Case Presentations: Washington University in ST Louis Medical SchoolIris GzlzNoch keine Bewertungen

- Release Waiver and Quitclaim: Security Services IncDokument1 SeiteRelease Waiver and Quitclaim: Security Services IncJobelle SaquitonNoch keine Bewertungen

- Quieting of TitleDokument11 SeitenQuieting of TitleJONA PHOEBE MANGALINDANNoch keine Bewertungen

- GR 11 SLK Pe 1 Week 2 1ST Sem PDFDokument10 SeitenGR 11 SLK Pe 1 Week 2 1ST Sem PDFwinslet villanuevaNoch keine Bewertungen

- How The Government Was Formed After Prophet MuhammadDokument48 SeitenHow The Government Was Formed After Prophet MuhammadMUSALMAN BHAINoch keine Bewertungen

- Environmental Sanitation LessonDokument4 SeitenEnvironmental Sanitation LessonMARIS GRACE CARVAJALNoch keine Bewertungen

- Chapter-1 of F.mensurationDokument8 SeitenChapter-1 of F.mensurationpradeeppoddarNoch keine Bewertungen

- Group 2Dokument3 SeitenGroup 2sharmisthahalder21Noch keine Bewertungen

- Learning CurveDokument7 SeitenLearning CurveSyed FaizanNoch keine Bewertungen

- ALL INDIA NURSING TEST REVIEWDokument102 SeitenALL INDIA NURSING TEST REVIEWDr-Sanjay SinghaniaNoch keine Bewertungen

- Jean Elizabeth HamptonDokument3 SeitenJean Elizabeth HamptonTamannaNoch keine Bewertungen

- 99 Names of Allah SWT and Mohammed (PBUH)Dokument11 Seiten99 Names of Allah SWT and Mohammed (PBUH)api-26870382100% (1)

- Chapter 4-Historical RecountDokument14 SeitenChapter 4-Historical RecountRul UlieNoch keine Bewertungen

- Mimw With CoverDokument13 SeitenMimw With Coverank123qwerNoch keine Bewertungen

- India's Contribution To World PeaceDokument2 SeitenIndia's Contribution To World PeaceAnu ChoudharyNoch keine Bewertungen

- Philo 12Dokument2 SeitenPhilo 12Rachel LaganNoch keine Bewertungen

- Evolution of Media and Social ImpactDokument24 SeitenEvolution of Media and Social ImpactLeorick Miciano0% (1)

- Daß Ich Erkenne, Was Die Welt Im Innersten Zusammenhält (Lines 382-83) So That I Know What Holds The Innermost World TogetherDokument2 SeitenDaß Ich Erkenne, Was Die Welt Im Innersten Zusammenhält (Lines 382-83) So That I Know What Holds The Innermost World TogetherEmanuel MoşmanuNoch keine Bewertungen

- Fano - Description of States in Qunatum Mechanics by Density Matrix and OperatorsDokument20 SeitenFano - Description of States in Qunatum Mechanics by Density Matrix and OperatorsAlexNoch keine Bewertungen

- The Fundamentals of Lighting PDFDokument20 SeitenThe Fundamentals of Lighting PDFVasilis Karageorgiou100% (1)

- Week4.pdf 82849 1 1583836882000 PDFDokument17 SeitenWeek4.pdf 82849 1 1583836882000 PDFsssmmm8Noch keine Bewertungen

- 5.5 Inch 24.70 VX54 6625 4000 2 (Landing String)Dokument2 Seiten5.5 Inch 24.70 VX54 6625 4000 2 (Landing String)humberto Nascimento100% (1)

- BA 424 Chapter 1 NotesDokument6 SeitenBA 424 Chapter 1 Notesel jiNoch keine Bewertungen