Beruflich Dokumente

Kultur Dokumente

LIC Lab Manual

Hochgeladen von

kunarajOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

LIC Lab Manual

Hochgeladen von

kunarajCopyright:

Verfügbare Formate

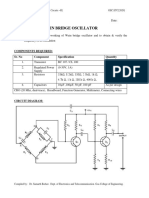

INVERTING AMPLIFIER:

5KΩ

1KΩ

V0

RPS

(0-10V)

833Ω

TABULAR COLUMN:

S.NO: Vin Vout Av = Vout/Vin

(Volts) (Volts)

MODEL GRAPH:

0 Vi(v)

Slope = - 5

Vo(sat)

Vo(v)

LINEAR INTEGRATED CIRCUITS LAB P age |1

1(a). INVERTING AND NON-INVERTING AMPLIFIER

EX.NO. :

DATE :

AIM: -

To design and verify the experimental and theoritical loop gains of amplifiers

using IC 741 in the inverting and non-inverting modes.

APPARATUS REQUIRED:

Equipments & Components Range Quantity

1.Dual Power Supply (0-30)V 1

2.Resistors 1KΩ 1

10KΩ 2

3.Regulated Power supply (0-30)V 1

4.Voltmeter (0-50)V 1

5.IC-741 1

DESIGN:

INVERTING AMPLIFIER:

Let the desired gain be 5 and VCC =15v & -VCC =-15v.We know

That gain for inverting amplifier AV = -Rf / R1

Rf

That is |AV| =| |

R1

Let R1 =1Kohm & given AV = 5

Rf

So 5 =

1KΩ

Rf = 5Kohm [Since 5Kohms is not a standard value, two 2.5 Kohms resistors are used

in series or two 10 Kohms is used in parallel are used for Rf].

R 1R f

And Rcomp = = 833 ohms [Since 833ohms is not a standard value, 1

R1 + R f

Kohms & 5Kohms resistors are used in parallel]

NON- INVERTING AMPLIFIER:

Let the desired gain be 6 and VCC =15v & -VCC =-15v.We know that gain for non

Rf

inverting amplifier AV = 1+

R1

LINEAR INTEGRATED CIRCUITS LAB P age |2

NON-INVERTING AMPLIFIER: 5KΩ

1 KΩ

Vo

833 Ω

VI (0 – 10 V)

TABULAR COLUMN:

S.NO: Vin Vout Av =Vout/Vin

(Volts) (Volts)

LINEAR INTEGRATED CIRCUITS LAB P age |3

Let R1 =1Kohm & given AV= 6

Rf

So 6 = 1+

1KΩ

Rf = 5Kohm [Since 5Kohms is not a standard value, two 2.5 Kohms resistors are used

in series or two 10 Kohms is used in parallel are used for Rf]. And

R 1R f

Rcomp = = 833 ohms [Since 833ohms is not a standard value, 1 Kohms &

R1 + R f

5Kohms resistors are used in parallel]

TO CALCULATE VI (MAX): -

Vo (sat) =VCC =15v-0.7v =14.3v

VI(max) = Vo (sat) /gain

For inverting amplifier VI(max) =14.3 v/-5 =-3v

For non inverting amplifier VI (max) =14.3 v/6 =2.4v

THEORY:

The basic equation for the op-amp is Ae = V0 where A is open loop gain of the

Op-amp at an operating frequency f and is positive. e is measured as per the arrow

direction shown in the fig 1. This equation is valid for the open loop condition and closed

loop condition [only for negative feedback]. Using the above formula all the gain

equations for the different amplifier configuration can be derived. It is very important to

note that A varies with frequency.

V0

e =

A

A is of the order of 105 to 106 at 5 Hz

Hence e = 0 for range of frequencies.

This implies that the non-inverting terminal voltage follows the inverting terminal

voltage or the inverting terminal voltage follows the non-inverting terminal

voltage. In other words the potential difference between the inverting and non-inverting

terminal is zero volt at a specified frequency the above condition will not be valid.

Rf

Gain equation for inverting amplifier A= -

R1

Rf

For non inverting amplifier A=1+

R1

A

For voltage follower A= =1

A +1

LINEAR INTEGRATED CIRCUITS LAB P age |4

MODEL GRAPH:

Vo(v)

Vo(sat)

Slope = 6

Vi(v)

TABULAR COLUMN:

S.NO: Vin Vout Av =Vout/Vin

(Volts) (Volts)

MODEL GRAPH:

Vo(v)

Vo(sat)

Slope = 1

Vi(v)

LINEAR INTEGRATED CIRCUITS LAB P age |5

MAX WATTAGE OF RESISTANCE:

Resistances used in the design are 1Kohm and 10Kohms .The maximum voltages

V2

across the resistance will be supply voltage. Hence wattage of resistance is .

R

V2 225 225

= or which is so much lower than 1/8W or 1/4W.So resistances with

R 1KΩ 10KΩ

5% tolerance, carbon film resistor with 1/8W or 1/4W is used.

PROCEDURE:

1. Connections are made as shown in circuit diagrams .

2. The input voltage is given and the output voltage is noted. The maximum input

voltage that can be given to the circuit is VI[max].

3. In all the config when VI = 0, V0 = 0.

4. The close loop gain is calculated for each input voltage and transfer

characteristics is drawn for each configuration.

5. The slope of the characteristics between input and output voltage gives the small

signal AC closed loop gain as represented in model graph.

RESULT:

Slope of the DC characteristics between input and output voltage gives the small

signal AC closed loop gain provided the condition outlined in theory regarding open loop

gain with frequency is maintained.

LINEAR INTEGRATED CIRCUITS LAB P age |6

CIRCUIT DIAGRAM:

R 2 = 100KΩ

R1=1KΩ

Vo

AFO

a

AFO R 1 =1KΩ

a

R 2 = 100K Ω

TABULAR COLUMN:

S.NO: V1 V2 V0 (Volts) gain

(Volts) (Volts)

LINEAR INTEGRATED CIRCUITS LAB P age |7

1(b).DIFFERENTIAL AMPLIFIER

EX.NO.:

DATE:

AIM:

To design and test the operation of Differential amplifier.

APPARATUS REQUIRED:

Equipments & Components Range Quantity

1.Dual Power Supply (0-30)V 1

2.Resistors 1KΩ 2

100KΩ 2

3.AFO (0-1)MHz 1

4.CRO (0-20)KHz 1

5.IC-741 1

DESIGN:

Gain = 100, & Let R1 = 1 KΩ

AD = R2 / R1

So R2 = AD * R 1

R2 = 100 * 1KΩ = 100KΩ.

THEORY:

A Circuit that amplifies the difference between two signals is called a differential

amplifier. This type of amplifier is very useful in instrumentation circuits.

For differential amplifier, though the circuit is not symmetric, but because of the

mismatch, the gain at the output with respect to positive terminal is slightly different in

magnitude to that of negative terminal. So even with the same voltage applied to both the

inputs, the output is not zero.

LINEAR INTEGRATED CIRCUITS LAB P age |8

LINEAR INTEGRATED CIRCUITS LAB P age |9

PROCEDURE:

1. Connections are given as per the circuit diagram.

2. Set the input Voltages V1 = 50mV & V2 =40mV.

3. Note down the Output Voltage

4. Vary the input Voltages and note down the output voltages.

5. Calculate the gain & Compare it with the Theoritical gain.

RESULT:

Thus the Differential amplifier is designed & tested.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 10

CIRCUIT DIAGRAM:

DIFFERENTIATOR:

31.8 KΩ

3.1KΩ

0.1µF VO (CRO)

Vin = a AFO

1Vpp,

50Hz

INTEGRATOR:

0.1µF

100KΩ

10KΩ

VO (CRO)

AFO

Vin= 0.1Vppa

50Hz

SPECIFICATION FOR IC741:

+Vcc = +15V, - Vcc = -15V

Ambient Temparature : 250 C

Input offset voltage : 6 mV(Max)

Input offset current : 200nA(Max)

Input bias current : 500nA(Max)

Input resistance : 2MΩ

Output resistance : 75Ω

Total Power dissipation : 85mW.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 11

2. DIFFERENTIATOR & INTEGRATOR

EX.NO.:

DATE:

AIM:

To design and study the operation of 1) Differentiator

2) Integrator.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1.Dual Power Supply (0-30)V 1

2.Resistors 31.8KΩ,3.1KΩ,10KΩ,100KΩ each 1

1KΩ 3

3.Capacitors 0.1µF 1

4.IC741 1

6.AFO (0-1)MHz 1

7.CRO (0-20)MHz 1

DESIGN:

DIFFERENTIATOR:

The transfer function of differentiator is given by

V0 - sR f C1

=

Vi 1 + sC1 R 1

If sC1R1 <<1then V0 / VI = -sRfC1

The above equation can be rewritten as

f 1

AV = where far =

fa 6.28 R f C1

Let fa =fmax=50 Hz, assume C1 =0.1 µFD

1

Rf = = 31.8KΩ

6.28f a C1

To prevent loading Rf =10R1

Rf

So R1 = = 3.1KΩ

10

INTEGRATOR:

To find R1 & Rf in the lossy integrator, so that the peak gain is 20dB and the gain

is 3dB down from it’s peak when ω = 10,000rad/sec.

Assume C = 0.001µF

We know that A(dB) = 20log10 Rf / R1 / [1+(ωRfCf)2]1/2

LINEAR INTEGRATED CIRCUITS LAB P a g e | 12

PINDIAGRAM FOR IC741:

1 8

2 IC741 7

3 6

4 5

1 = Offset Null, 2 = Inverting input terminal, 3 = Non inverting input terminal, 4 = -Vcc,

5 = Offset Null, 6 = Output, 7 = +Vcc, 8 = No connection

MODEL GRAPH:

DIFFERENTIATOR:

Vi(v)

0V

t (msec)

Vo(v)

0V

t (msec)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 13

To find the peak value in decibel

Put ω = 0. So A(dB) = 20.

So R1 = Rf / 10.

At ω = 10,000 rad/sec, gain in dB is down by 3dB from it’s peak of 20dB & thus is 17dB.

So 20 log10 10/[1+(104 * 10-9 * Rf )2]1/2+ = 17dB

By solving 1+(10-5 * Rf )2 = 103/10

(10-5 * Rf )2 = 1

Rf = 100KΩ, So R1 = 10KΩ.

VERIFICATION:

From the design C1 = 0.1MFD & R1 =3.1kΩ

So SR1C1 =0.097

Consider an input with

Vmax =1v and f=50Hz

VI =Vmax sinwt =sinwt

We know that

dVI d

Vo = -RfC1 = -31.8 * 103 *0.1 * 10-6 (sin wt)

dt dt

= (-0.00318)(6.28f)cos(6.28ft)

The transfer function of integrator is given by

1

Rf *

VO sC f Rf

=- =-

VI 1 R 1 ( R f sC f + 1)

R 1 (R f + )

sC f

If sRfCf >>1 then

VO Rf

=-

VI R 1 ( R f sC f )

1

= -

sR1C f

1

Vo = - ∫ VI dt

R 1C f

Let Cf = 0.1MFD & R1 =10kohm

Vo = Vm sin wt =0.1 sin wt

0.1

Then Vo = - 3 _6 ∫ sin wt = -100 cos wt/w

10 *10 * 0.1 *10

If f =50 Hz, Vo = -0.3cos wt

LINEAR INTEGRATED CIRCUITS LAB P a g e | 14

DIFFERENTIATOR:

Vi(v)

0V t (msec)

Vo(V)

0V

t (msec)

TABULAR COLUMN:

Amplitude(V) Time period(ms)

Input

Output

LINEAR INTEGRATED CIRCUITS LAB P a g e | 15

LINEAR INTEGRATED CIRCUITS LAB P a g e | 16

INTEGRATOR:

Vi(v)

0V t (msec)

Vo (V)

0V t(msec)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 17

LINEAR INTEGRATED CIRCUITS LAB P a g e | 18

INTEGRATOR:

Vi (V)

0V

t(msec)

Vo(V)

0V

t(msec)

TABULAR COLUMN:

Amplitude(V) Timeperiod(ms)

Input

Output

LINEAR INTEGRATED CIRCUITS LAB P a g e | 19

THEORY:

DIFFERENTIATOR:

The circuit which produces the differentiation of the input voltage at it’s output is

called differentiator. The Differentiator circuit can be obtained without using active

devices like op-amp, transistors etc. In such a case Differentiator is called passive

Differentiator. Differentiator using an active device like op-amp is called active

differentiator. This can be obtained by exchanging the positions of R & C in the basic

integrator circuit. Vo = -C1 Rf dVin / dt

The negative sign indicates that there is a phase shift of 1800 between input & output.

The main advantage of differentiator is the small time constant required for

differentiation.

INTEGRATOR:

In an integrator circuit , the output voltage is the integration of the input voltage.

The integrator circuit can be obtained without using active devices like op-amp,

transistors etc. In such a case an integrator is called passive integrator. While an

integrator using an active devices like op-amp is called active integrator.

Vo = - 1/R1Cf ∫ Vin dt + Vo (0)

0

where Vo (0) is the constant of integration indicating the initial output voltage. The

negative sign indicates that there is a phase shift of 1800 between input & output.The

main advantage of such an active integrator is the large time constant.

PROCEDURE:

DIFFERENTIATOR:

1. Circuit connections are given as shown in fig

2. A sine wave with 1VPP and 50Hz frequency is given as input.

3. The output is obtained in the CRO and is verified with the theoritical verification

4. Graph is drawn as shown in model graph.

INTEGRATOR:

1. Circuit connections are given as shown in fig

2. A sine wave with 0.1VPP and 50Hz frequency is given as input.

3. The output is obtained in the CRO and is verified with the theoritical verification.

4. Graph is drawn as shown in model graph.

RESULT:

Thus the operation of Inverting Summer, integrator and differentiator was studied

and the output was verified with the theoritical calculation.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 20

CIRCUIT DIAGRAM:

IC741

10k

+ 100k

120k

IC741

+

10k

10k 120k

100k

10k IC741 IC741

+ + 10k

Vin

TABULAR COLUMN:

Input Voltage (Volts) Output Voltage(Volts)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 21

3.INSTRUMENTATION AMPLIFIER

EX.NO :

DATE :

AIM:

To construct the Instrumentation amplifier using IC-741 for the gain 250.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1.Dual Power Supply (0-30)V 4

2.Resistors 10KΩ, 5

100KΩ 2

120KΩ 2

4.IC741 3

6.RPS (0-15)V 1

7.CRO (0-20)MHz 1

THEORY:

The output of the transducer has to be amplified to drive the indicating or driving

system. This function is performed by instrumentation amplifier. The important features

are: 1) High gain accuracy, 2) High Common mode rejection ratio, 3) High gain stability

with low temparature coefficient,4) Low DC offset, 5) Low output impedance.

PROCEDURE:

1. Connections are given as per the circuit diagram.

2. Set the DC input voltage as 1 mV.

3. Note down the output voltage.

4. Calculate the gain and compare it with theoretical gain.

5. Repeat it for different input values.

RESULT:

Thus the Instrumentation amplifier was constructed & Verified.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 22

CIRCUIT DIAGRAM:

Rf = 4.7KΩ + 1.2KΩ

R1 = 10KΩ

Vo (CRO)

AFO R=1.6KΩ R=1.6KΩ

Vin = a 0.1µF 0.1µF

1Vpp

PIN DIAGRAM FOR IC741:

1 8

2 IC741 7

3 6

4 5

1 = Offset Null, 2 = Inverting input terminal, 3 = Non inverting input terminal, 4 = -Vcc,

5 = Offset Null, 6 = Output, 7 = +Vcc, 8 = No connection

SPECIFICATION FOR IC741:

+Vcc = +15V, - Vcc = -15V

Ambient Temparature : 250 C

Input offset voltage : 6 mV(Max)

Input offset current : 200nA(Max)

Input bias current : 500nA(Max)

Input resistance : 2MΩ

Output resistance : 75Ω

Total Power dissipation : 85mW.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 23

4(a). SECOND ORDER LOW PASS FILTER

EX.NO :

DATE :

AIM:

To design and study the frequency response of second order butter worth filter

with cutoff frequency of 1000Hz.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Dual Power Supply (0-30)V 1

2.Resistors 4.7KΩ,1.2KΩ,10KΩ each 1

1.5KΩ,100Ω each 2

3.Capacitors 0.1µF 1

4.IC741 1

5.CRO (0-20)MHz 1

6.AFO (0-1)MHz 1

DESIGN:

The general equation for transfer function is

VO A o Y1 Y2

=

VI [Y1 Y2 + Y4 (Y1 + Y2 + Y3 ) + Y2 Y3 (1 - A O )]

In a LPF Y4 = Y3 = sC and Y1 = Y2 =1/R

AO

H(s) = R2

1 sC sC 2

[ 2 + (3 - Ao) +( ) ]

R R R

Let 1/RC = w1

A O w 12

Then H(s) =

s s

[1 + (3 - A O ) + ( )2 ]

w1 w1

w1 / s is the normalized frequency.

Let (3 - Ao) =α

For maximally flat response (3 - Ao) should be equal to 1.414.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 24

TABULAR COLUMN: Vin =

Gain Av(db) =

Frequency Vout 20 log

(Hertz) (Volts) [Vout/Vin]

MODEL GRAPH:

Av(db)

AV (Max)

0.707AV (Max)

Pass band Stop band

Frequency(Hz)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 25

When s=w1, H(s) = Ao / 1.414 which gives the half power frequency.

If the desired cutoff frequency is 1KHz

Then

1/RC = w1

1

f1 =

2 πRC

Let C = 0.1µF

f1 = 1 kHz

1

1KHz =

6.28 * 0.1 *10 -6 * R

R = 1.6Kohms.

From 3-Ao = 1.414 we can find the theoritical pass band gain.

3-Ao = 1.414

Ao = 1.586

Rf

Also the op-amp is used in the non-inverting mode so, Ao = 1+ = 1.586

R1

Rf

= 0.586 (or) Rf =0.586 R1

R1

Let R1 = 10Kohm

Rf = 5.86[use 4.7k in series with 1.2K]

THEORY:

A Filter is a circuit that is designed to pass a specified band of frequencies while

attenuating all the signals outside the band. It is a frequency selective circuit. The filters

are basically classified as Active filters & Passive filters.

The Passive filter networks use only passive elements such as resistors, inductors

and capacitors. Active filter circuits use the active elements such as op-amps, transistors

along with the resistors, inductors & capacitors.

A Low pass filter has a constant gain from 0 Hz to a high cutoff frequency fH.

The circuit allows the range of frequencies from 0 to fH . This range is known as

Passband. The range of frequencies beyond fH is completely attenuated & hence called

stopband.

For a second order Butterworth active filter the roll-off rate should be -

40db/decade or -12db/octave.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 26

LINEAR INTEGRATED CIRCUITS LAB P a g e | 27

PROCEDURE:

1. Connections are made as shown in fig .

2. Set a sinusoidal input with peak 1v. Change the frequency of AFO in steps of

100Hz and note down the output amplitude from the CRO.

3. Find the gain in db for each input.

4. Plot the gain Vs frequency in semi log graph. Graph is drawn as shown in model

graph.

5. Verify if the roll-off rate is -40db/decade or -12db/octave.

RESULT:

Thus the Second order low pass filter was designed and frequency response plot

was drawn.

Theoritical cut-off frequency =

Practical cut-off frequency =

LINEAR INTEGRATED CIRCUITS LAB P a g e | 28

CIRCUIT DIAGRAM:

C2 = 0.01µF

R3 = 100KΩ

R1 = 4.7KΩ C1 = 0.01µF

Vin Vo (CRO)

a

R2 = 6.2KΩ

RL = 10KΩ

PINDIAGRAM FOR IC741:

1 8

2 IC741 7

3 6

4 5

1 = Offset Null, 2 = Inverting input terminal, 3 = Non inverting input terminal,

4 = -Vcc, 5 = Offset Null, 6 = Output, 7 = +Vcc, 8 = No connection

SPECIFICATION FOR IC741:

+Vcc = +15V, - Vcc = -15V Input bias current : 500nA(Max)

Input resistance : 2MΩ Output resistance : 75Ω

Total Power dissipation : 85mW. Ambient Temparature : 250 C

Input offset voltage : 6 mV(Max) Input offset current : 200nA(Max)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 29

4(b). SECOND ORDER BAND PASS FILTER

EX.NO :

DATE :

AIM:

To design and study the frequency response of second order Band pass filter with

Central frequency 1KHz, Q = 3 & gain = 10.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Dual Power Supply (0-30)V 1

2.Resistors 4.7KΩ,6.2KΩ,100KΩ each 1

3.Capacitors 0.01µF 2

4.IC741 1

5.CRO (0-20)MHz 1

6.AFO (0-1)MHz 1

DESIGN:

f C = 1KHz, AF = 10 & Q = 3.

Let C 1 = C 2 = 0.01µF,

R 1 = Q / 2Πf C C AF

= 3 / (2Π* 1000* 0.01*10-6 * 10)

= 4.77KΩ

R 2 = Q / 2Πf C C (2Q2 – AF )

= 3 / [2Π* 1000*0.01*10-6 (2*32* - 10)]

= 5.97KΩ.

R 3 = Q / Πf C C

= 3 / Π*103*0.01*10-6

= 95.5KΩ.

So Choose R 1 = 4.7KΩ, R 2 = 6.2KΩ , R3 = 100KΩ.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 30

MODEL GRAPH:

AF

0.707AF

Gain(dB)

fL fC fH Frequency(Hz)

TABULAR COLUMN: Vin =

Gain Av(db) = 20

Frequency Vout log [Vout/Vin]

(Hertz) (Volts)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 31

THEORY:

There are Two types of Bandpass filters which are classified as per figure of merit

or Quality factor. 1) Narrow bandpass filter (Q>10) 2) Wide bandpass filter(Q <10).

This Filter is unique in following respects:

- It has two feedback paths, hence the name multiple feedback filter.

- The Op-amp is used in inverting mode.

Generally the narrow band pass filter is designed for specific values of Center frequency

& Q.

PROCEDURE :

1. Connections are given as shown in fig .

2. Set a sinusoidal input with peak 1v. Change the frequency of AFO in steps of

10Hz and note down the output amplitude from the CRO.

3. Find the gain in db for each input.

4. Plot the gain Vs frequency in semilog graph. Graph is drawn as shown in model

graph.

RESULT:

Thus the Second order Band pass filter was designed and frequency response plot

was drawn.

Practical central frequency =

Bandwidth =

LINEAR INTEGRATED CIRCUITS LAB P a g e | 32

ASTABLE MULTIVIBRATOR USING OP AMP

4.55 KΩ

0.1µF VO(CRO)

10 KΩ

10 KΩ

MODEL GRAPH:

Vo

t t

TABULAR COLUMN:

Amplitude(V) Time period(ms)

Output

LINEAR INTEGRATED CIRCUITS LAB P a g e | 33

5(a). ASTABLE MULTIVIBRATOR USING OP-AMP

EX.NO :

DATE :

AIM:

To design and construct an astable multivibrator using IC Operational amplifier 741.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Dual Power Supply (0-30)V 1

2.Resistors 10KΩ, 2

4.5KΩ,1KΩ,27KΩ each 1

3.Capacitors 0.1µF 1

4.IC741 1

5.CRO (0-20)MHz 1

6.AFO (0-1)MHz

THEORY:

An astable multivibrator is a square waveform generator. Square wave is generated by

forcing the op-amp to operate in the saturation region. The astable multivibrator is a free

running symmetrical multivibrator because it does not require any external trigger.

DESIGN:

Feedback factor = R2/(R1+R2)

Time period of the square wave T =2RC ln[(1+β)/(1-β)]

Let R1 =R2 10KΩ then β=0.5

Assume C = 0.1µF

For a time period of 1ms

T= 2RC ln 3

Rf = 4.55KΩ

Component values:

R1 =10KΩ R2 = 10KΩ

Rf = 4.55KΩ C = 0.1µF

LINEAR INTEGRATED CIRCUITS LAB P a g e | 34

LINEAR INTEGRATED CIRCUITS LAB P a g e | 35

PROCEDURE:

1.Circuit connections are made with the components of designed values.

2.The square wave output is obtained at the output pin of the op amp.

3.The amplitude and time period of the output waveform is noted and it is

plotted on the graph.

RESULT:

An astable multivibrator is designed and constructed and the square wave output is

obtained.

Time period of the square waveform (theoritical):

Time period of the square waveform (practical):

LINEAR INTEGRATED CIRCUITS LAB P a g e | 36

MONOSTABLE MULTIVIBRATOR USING OP AMP

1KΩ

V0

OA79

1µF

10KΩ

VIN

1KΩ

0.01µF

OA79

22KΩ

LINEAR INTEGRATED CIRCUITS LAB P a g e | 37

5(b). MONOSTABLE MULTIVIBRATOR USING OP-AMP

EX.NO :

DATE :

AIM:

To design monostable multivibrator circuits using op-amp.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Dual Power Supply (0-30)V 1

2.Resistors 1KΩ, 2

10KΩ,22KΩ each 1

3.Capacitors 0.1µF,0.01µF 1

4.IC741 1

5.CRO (0-20)MHz 1

6.AFO (0-1)MHz 1

7.Diode 0A79 2

THEORY:

Monostable multivibrator has one stable state and one quasi-stable state. One shots

are used to set the timing of an event or to control a sequence of events in a digital

system. A triggering pulse initiates the one shot action and generates a pulse of desired

width. If additional triggers are applied to one - shot, when it is in the quasi-stable state,

they are ineffective. The one shot needs time to recover after if returns to the stable state

subsequent to a triggering event. Therefore, triggering pulses should not be applied so

often to cause the ON time of the one-shot to exceed the duty cycle specified. If the duty

cycle of a one shot exceeds the maximum specified value, there is jitter in the output

pulse. That is the width of each pulse will not be constant.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 38

MODEL GRAPH:

VIN

T (msec)

Vo

+Vsat

t (msec)

-Vsat

TABULAR COLUMN:

Amplitude(V) Timeperiod(ms)

Output

LINEAR INTEGRATED CIRCUITS LAB P a g e | 39

PROCEDURE:

Monostable multivibrator using op-amp:

1. Connections are made as per the figure.

2. Negative triggering pulse with 1 KHz repetition rate are applied.

3. The input and output waveforms are observed on a dual trace CRO and plotted.

4. The value of the pulse width is obtained theoretically from the following

relationship.

T = RfC ln[ 1+R2/R1].

RESULT: -

An Mono stable multivibrator is designed and constructed and the square wave

output is obtained.

Time period of the output waveform (theoritical)=

Time period of the output waveform (practical) =

LINEAR INTEGRATED CIRCUITS LAB P a g e | 40

SCHMITT TRIGGER USING OP AMP:

1 KΩ

VO(CRO)

AFO a

27 KΩ

1 KΩ

MODEL GRAPH:

Vi

VUT

T (msec)

VLT

V0

+VSAT

T (msec)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 41

-VSAT

5(c). SCHMITT TRIGGER

EX.NO :

DATE :

AIM:

To design Schmitt trigger circuit using op-amp.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Dual Power Supply (0-30)V 1

2.Resistors 1.5KΩ, 2

5.6KΩ,22KΩ,760Ω,1KΩ each 1

3.Capacitors 0.1µF,0.01µF 1

4.IC741 1

5.CRO (0-20)MHz 1

6.AFO (0-1)MHz 1

7.Diode 0A79 1

DESIGN:

R2

Vut = Vsat

R1 + R 2

R2

Vlt = -Vsat

R1 + R 2

Let Vut = +0.5v, Vlt =-0.5v

For IC 741, with supply voltages 615v, Vsat = 14v & -Vsat = -14v

R2

Then 0.5 = 14v

R1 + R 2

R1= 27R2

Let R1=1kohm,then R2=27kohm

THEORY:

The schmitt trigger is a circuit, which converts a slow changing waveform into a

fast changing waveform. In an schmitt trigger the o/p is in one of the two levels namely

signal voltage Vsat or -Vsat. When the i/p voltage is rising, the level of the output changes

when the input passes through a specific voltage Vut known as upper threshold voltage.

Similarly when a falling input voltage passes through a specific voltage Vlt known as

LINEAR INTEGRATED CIRCUITS LAB P a g e | 42

lower threshold voltage, the level of the output changes. Vut is greater than Vlt. The

difference between the two voltages is known as HYSTERESIS.

MODEL GRAPH:

+VSAT

VUT t(msec)

-VSAT

+VSAT

VLT t(msec)

-VSAT

+VSAT

VLT VUT t(msec)

-VSAT

LINEAR INTEGRATED CIRCUITS LAB P a g e | 43

PROCEDURE:

Schmitt trigger using op-amp:

1. The circuit is connected as shown in figure .

2. The i/p dc voltage is increased from 0 to 5v and the o/p voltage is measured. The

output curve is drawn and Vut, Vlt and hysteresis are found out.

3. A sinusoidal input of peak 5v and 1khz is given. The input and output waveforms

are observed simultaneously on a dual trace CRO and plotted.

TABULAR COLUMN:

AMPLITUDE(V) TIMEPERIOD(ms)

INPUT(Sine Wave)

OUTPUT(Square wave)

VUT

VLT

RESULT:

A Schmitt trigger designed and constructed and the square wave output is

obtained.

Upper threshold voltage =

Lower threshold voltage =

Square output:

LINEAR INTEGRATED CIRCUITS LAB P a g e | 44

Amplitude =

Time period =

390KΩ

RC PHASE SHIFT OSCILLATOR:

13KΩ

VO

15KΩ

0.1µF 0.1µF 0.1µF

1.5KΩ 1.5KΩ 1.5KΩ

MODEL GRAPH:

V0(V)

t(msec)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 45

6(a). RC PHASE SHIFT OSCILLATOR

EX.NO :

DATE :

AIM:

To design and construct the RC phase shift oscillator of frequency of 500Hz

and to plot the sinusoidal waveform.

Equipments & Range Quantity

Components

1. Dual Power Supply (0-30)V 1

2.Resistors 1.5 KΩ, 3

13KΩ,390KΩ,15KΩ 1

3.Capacitors 0.1µF, 3

4.IC741 1

5.CRO (0-20)MHz 1

6.AFO (0-1)MHz 1

1

DESIGN:

The frequency of oscillation of RC phase shift oscillator is given by

1

fO =

2 πRC 6

Assume C =0.1 microfarad.

Desired frequency of oscillator, f0 = 500Hz

1

Then 500 =

2 π * R * 0.1 * 10 _ 6 * 6

∴R =1.3K ohm [use 1.2K in series with 100ohm]

To avoid loading effect

R1 = 10 R

So R1 = 10 * 1.3 K =13 KΩ

For the loop gain AVβ to be greater than 1,Rf should be equal to 29R1

R 1R f

So Rf =29R1 =390kohms and Rcomp= =15kohms.

R1 + R f

LINEAR INTEGRATED CIRCUITS LAB P a g e | 46

Only polyester condenser should be used. Ceramic condenser should not be used. The

condenser value is specified by voltage rating, tolerance & capacitor value. Standard

values are 65v, 100v, 125v, 250v, and 400v

LINEAR INTEGRATED CIRCUITS LAB P a g e | 47

MAX WATTAGE OF RESISTANCE:

Resistances used in the design are 1Kohm and 10Kohms .The maximum voltages

across the resistance will be supply voltage. Hence wattage of resistance is V2 / R.

V2 /R=225 / 1.3K or 225 / 13K or225 / 390K or225 / 15K which is so much lower than

1/8W or 1/4W.So resistances with 5% tolerance, carbon film resistor with ⅛w or ¼w is

used.

THEORY:

The closed loop circuit of the RC phase shift oscillator is opened at point A. The

input of the op-amp is sullied from AFO under open loop conditions. The loop gain must

be equal to 1 or slightly greater than 1 at the oscillating frequency and the phase shift

must be equal to zero. The oscillator does not produce oscillation. This is the way of

checking the oscillator working. The gain of the op-amp and attenuation of the phase

shifting circuit must be separately determined and then multiplied to get the open loop

gain at fo and this must be greater than 1.To adjust the gain a 470kohms carbon POT is

chosen for 390k.The gain of the op-amp should be -29and the attenuation should be-

1/29.The i/p voltage can be of the order of 0.1vpeak so that an o/p voltage of 2.9v peak

will be obtained.

PROCEDURE:

1. Construct the circuit as shown in circuit diagram in fig

2. Observe the output waveform on the CRO.

3. Adjust the feedback resistor Rf to get a perfect sine waveform.

4. Measure the amplitude and frequency and plot the waveform. Graph is drawn as

shown in model graph.

TABULAR COLUMN:

Amplitude(V) Time period(ms)

Output

RESULT:

RC phase shift oscillator is designed to oscillate at 500Hz and the frequency of the output

waveform is =

LINEAR INTEGRATED CIRCUITS LAB P a g e | 48

CIRCUIT DIAGRAM:

31.8 KΩ

0.01µF

15.9 KΩ

1.59 KΩ

VO(CRO)

0.01µF

1.59 KΩ

SPECIFICATION FOR IC741:

+Vcc = +15V, - Vcc = -15V

Ambient Temparature : 250 C

Input offset voltage : 6 mV(Max)

Input offset current : 200nA(Max)

Input bias current : 500nA(Max)

Input resistance : 2MΩ

Output resistance : 75Ω

Total Power dissipation : 85mW.

PINDIAGRAM FOR IC741:

1 8

2 IC741 7

3 6

4 5

1 = Offset Null, 2 = Inverting input terminal, 3 = Non inverting input terminal, 4 = -Vcc,

5 = Offset Null, 6 = Output, 7 = +Vcc, 8 = No connection

LINEAR INTEGRATED CIRCUITS LAB P a g e | 49

6(b). WIEN BRIDGE OSCILLATOR

EX.NO :

DATE :

AIM:

To design and construct the Wien Bridge oscillator of frequency of 10kHz and to

plot the sinusoidal waveform.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1.Dual Power Supply (0-30)V 1

2.Resistors 31.8KΩ,15.9KΩ each 1

1.59KΩ 2

3.Capacitors 0.01µF 2

4.IC741 1

5.CRO (0-20)MHz 1

DESIGN:

The frequency of oscillation of Wien Bridge oscillator is given by

1

fO =

2 πRC

Assume C =0.01 microfarad.

Desired frequency of oscillator, f0 = 10KHz

1

Then 10000 =

2π * R * 0.01*10 _ 6

R =1.59K ohm

To avoid loading effect

R1 = 10 R

So R1 = 10 * 1.59 K =15.9 KΩ

For the loop gain Av to be greater than 1,Rf should be equal to 2R1

So Rf =2R1 =31.8kohms.

Only polyester condenser should be used. Ceramic condenser should not be used. The

condenser value is specified by voltage rating ,tolerance &capacitor value. Standard

values are 65v, 100v, 125v, 250v,and 400v.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 50

MODEL GRAPH:

V0(V)

t(msec)

TABULAR COLUMN:

Amplitude(V) Time period(ms)

Output

LINEAR INTEGRATED CIRCUITS LAB P a g e | 51

THEORY:

This is also RC Oscillator, which uses RC type of feedback network. The closed

loop circuit of the wein bridge oscillator gives the negative feedback. To compensate the

change ,an adaptive negative feedback is used. Since the op-amp works as a non inverting

amplifier, the feedback network need not provide any phaseshift.

The circuit can be viewed as weinbridge with a series RC network in one arm & a

parallel RC network in the adjoining arm. Resistors R1 & Rf are connected in remaining

two arms. The condition of zero phase shift is obtained by balancing the bridge.

PROCEDURE:

1. Construct the circuit as shown in circuit diagram .

2. Observe the output waveform on the CRO.

3. Adjust the feedback resistor Rf to get a perfect sine waveform.

4. Measure the amplitude and frequency and plot the waveform.

RESULT:

Thus the Wien Bridge oscillator circuit is designed output waveform is obtained .

Theoritical frequency : 10KHz

Practical frequency :

LINEAR INTEGRATED CIRCUITS LAB P a g e | 52

CIRCUIT DIAGRAM :

+Vcc =+5v

7.25KΩ RA

4 8

7

OA79 3.625K

Ω

RB IC555

6 3 Vo

0.1µF

2

5 1

0.01µF

PIN DIAGRAM FOR IC555:

1 8

2 IC555 7

3 6

4 5

1 = Ground, 2 = Trigger, 3 = output, 4 = Reset, 5 = Control voltage,

6 = Threshold, 7 = Discharge, 8 = +Vcc

LINEAR INTEGRATED CIRCUITS LAB P a g e | 53

7(a). ASTABLE MULTIVIBRATOR USING TIMER

EX.NO :

DATE :

AIM:

To Construct astable multivibrator using IC555 timer & to generate a 1KHz

square waveform.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Power Supply (0-30)V 1

2.Resistors 3.625KΩ,7.25KΩ each 1

3.Capacitors 0.01µF 1

0.1µF 1

4.IC555 1

5.CRO (0-20)MHz 1

6.Diode 0A79 1

DESIGN:

Case (I)

Given f = 1KHz and D =0.5

1.45

Frequency of astable multivibrator, f =

( R A + R B )C

1.45

Then C=

( R A + R B )f

RB

D= = 0.5

(R A + R B )

0.5RA +0.5RB = RB

RA = RB

Let C = 0.1µF, RA =RB =R

1.45

f=

( R A + R B )C

1.45 1.45

f= =>1KHz =

2RC 2 * 0.1 *10 -6 * R

R = 7.2Kohm

LINEAR INTEGRATED CIRCUITS LAB P a g e | 54

SPECIFICATION FOR IC555:

Supply Voltage : +5V to +18V.

Maximum current : 200mA.

FORMULA FOR DUTY CYCLE:

Duty Cycle % = Ton / Ton + Toff *100.

MODEL GRAPH:

Vo(v)

Vcc

2/3 Vcc

1/3 Vcc

0

t(ms)

TABULAR COLUMN:

Amplitude(V) Timeperiod(ms)

Output

LINEAR INTEGRATED CIRCUITS LAB P a g e | 55

Case (ii)

Given f = 1KHz and D =0.25

1.45

Frequency of astable multivibrator, f =

( R A + 2 R B )C

1.45

Then C=

( R A + 2R B )f

RB

D= = 0.25

R A + 2R B

RA +2RB = 4RB

RA = 2RB

Let C = 0.1µF, RA = 2RB

1.45

f=

( R A + 2 R B )C

1.45 1.45

f= =>1KHz =

4R B C 4 * 0.1*10-6 * R B

RB = 3.625Kohm

Then RA =7.25Kohms

THEORY:

The 555 timer is a highly stable device for generating accurate time delay or

oscillation. A single 555 timer can provide time delay ranging from microseconds to

hours whereas counter timer can have a maximum timing range of days.

An astable multi vibrator is a square wave form generator. Square wave form is

generated by forcing the Op-amp to operate in the saturation region. It is a free running

symmetrical multivibrator because it does not require any external trigger.

PROCEDURE:

1. The connections are given as shown in the circuit diagram .

2. The square wave form is obtained at output pin of Op-amp.

3. Note the amplitude & Time period of the of the waveform & Plot it in

The graph.

4. Duty cycle is calculated using the formula given.

RESULT:

Thus IC555 timer was operated in astable mode to generate square wave.

Theoritical Duty cycle : 25%

Practical Duty cycle : -----------.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 56

CIRCUIT DIAGRAM:

+VCC = +5V

10KΩ

OA79 10KΩ

4 8

2

0.001µ F 6

a

VIN

7

IC 555

3

Vo

0.1µF

5 1

0.01µF

PINDIAGRAM FOR IC555:

1 8

2 IC555 7

3 6

4 5

1 = Ground, 2 = Trigger, 3 = output, 4 = Reset, 5 = Control voltage,

6 = Threshold, 7 = Discharge, 8 = +Vcc

LINEAR INTEGRATED CIRCUITS LAB P a g e | 57

7(b).MONOSTABLE MULTIVIBRATOR USING TIMER

EX.NO :

DATE :

AIM:

To Operate the IC555 timer in Monostable mode to generate a 1KHz square

waveform.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Power Supply (0-30)V 1

2.Resistors 10KΩ 2

3.Capacitors 0.01µF 1

0.1µF 1

0.001µF 1

4.IC555 1

5.CRO (0-20)MHz 1

6.Diode0A79 1

7.AFO (0-1)MHz 1

DESIGN:

Time period of monostable multivibrator = 1.1RC.

T = 1msec.

Assume C = 0.1µF,

Then R = T/1.1C

R = 1*10-3 / 1.1*0.1*10-6

R ≅ 10KΩ.

THEORY:

Monostable multivibrator has one stable state & one quasistable state.One shots

are used to set the timing of an event or to control a sequence of events in a digital

system. A triggering pulse initiates the oneshot action & generates a pulse of desired

width .The oneshot needs time to recover after it returns to the stable state subsequent to

a triggering event. Therefore triggering pulses should not be applied so often to cause the

on time of the oneshot to exceed the duty cycle specified. If the duty cycle of a oneshot

exceeds the maximum specified value, there is a jitter in the output pulse. That is the

width of each pulse will not be constant.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 58

SPECIFICATION FOR IC555:

Supply Voltage : +5V to +18V.

Maximum current : 200mA.

MODEL GRAPH:

VIN

(V)

t(ms)

Vo

t(ms)

TABULAR COLUMN:

Amplitude(V) Time period(ms)

Output

LINEAR INTEGRATED CIRCUITS LAB P a g e | 59

PROCEDURE:

1. The connections are given as shown in the circuit diagram (Fig 17.2).

2. The negative trigger pulses of frequency 1KHZ are applied at the trigger input.

3. The output waveform is observed and pulse duration is measured.

4. Theoritically the pulse duration is calculated as

thigh =1.1RAC

RESULT:

Thus IC555 timer was operated in Monostable mode to generate square waveform.

Theoritical pulse duration = 1msec.

Practical pulse duration = --------.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 60

CIRCUIT DIAGRAM: 723 VOLTAGE REGULATOR

10 V DC (0-100mA)

6 12 11 10Ω + -

10 a

680Ω

1kΩ 10kΩ

IC 723

2

1kΩ 3.3kΩ

5 33kΩ

2.2kΩ

4

7 13

0.001µF

MODEL GRAPH:

Load regulation:

VL(V)

RL(mA)

Line regulation:

VL (V)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 61

8(a). DC POWER SUPPLY USING LM723

AIM:

To study the operation of 723-voltage regulator IC and to obtain Load

regulation & Line regulation.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Power Supply (0-30) V 1

2.Resistors 620Ω, 1

2.2KΩ, 1

10Ω, 1

33KΩ, 1

3.3KΩ, 1

3.Capacitor 0.001µF 1

4.IC723 1

5.Ammeter (0-50) mA 1

6.Voltmeter (0-10) V 1

7.Decade resistor box

THEORY:

IC723:

IC 723 general-purpose voltage regulator is inherently low current

device, but can be boosted to provide 5 amps or more current by connecting

external components. It has two separate sections. The Zener diode, a constant

current source and reference amplifier produce a fixed voltage of about 7 volts at

the terminal Vref. The constant current source forces the Zener diode to operate at

a fixed point so that the Zener outputs a fixed voltage.

The other section of the IC consists of an error amplifier, a series pass

current limit transistor Q2.the error amplifier compares a sample of the output

voltage applied at the inverting input terminal to the reference voltage Vref applied

at the NI input terminal. The error signal controls the conduction of Q1.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 62

LINEAR INTEGRATED CIRCUITS LAB P a g e | 63

PROCEDURE:

1. Connections are made as shown in the circuit diagram

2. The power supply voltage Vin is adjusted to 10 V and Vref is

measured at pin 6.

3. The load current IL and load voltage VL are measured and recorded for

various values of RL.

4.To measure line regulation, load resistance is kept constant and load

voltage VL is measured for various values of Vin.

5.Graphs are plotted with IL versus VL and Vin versus VL.

RESULT:

Thus the DC Power supply using IC 723 is performed and graphs are

plotted.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 64

CIRCUIT DIAGRAM:

LM317

Vin Vout

ADJ R1=240Ω

Vin

C2 =1µF Multimeter

R2 =3KΩ

C1 = 10µF

MODELGRAPH:

VL (v)

Vin (V)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 65

8(b). DC POWER SUPPLY USING LM317

EX.NO :

DATE :

AIM:

(i) To design an adjustable voltage regulator using LM317 for the following

specifications.

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Power Supply (0-30)V 1

2.Resistors 240Ω 1

3.Capacitors 10µF,1µF 1

4.LM317 1

6.Voltmeter (0-20) V 1

7.Decade resistor box 1

THEORY:

LM317 is a adjustable voltage regulator. They have the following performance

and reliability advantages over the fixed types.

*Improved system performance by having line and load regulation of a factor of

10 or better.

*Improved overload protection allows greater output current over operating

temparature range.

*Improved system reliability with each device being subjected to 100% thermal

limit burn- in.

Thus the adjustable voltage regulators have become more popular because of versatility,

performance, and reliability.

DESIGN:

Designing an adjustable voltage regulator LM317 to satisfy the following

specifications:

Output voltage Vo = 5 to 12V.

Output current Io = 1.0A

IAdj = 100 micro amps maximum. If we use R1 = 240ohm., then for Vo = 5V the value of

R2 = from equation

Vo =VREF ( 1+ R2 / R1) + IAdjR2.

Where VREF = 1.25V(Reference voltage between the output and adjustment terminals.

5 = 1.25(1+R2/240) + (10-4)R2

R2 = 3.75/(5.3)(10-3)

= 0.71kohm.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 66

LINEAR INTEGRATED CIRCUITS LAB P a g e | 67

similarly for Vo = 12V, the value of R2 is

12 = 1.25(1+R2/240) + (10-4)R2

R2 = 10.75/(5.3)(10-3)

= 2.01kohm.

PROCEDURE:

1.Connections are made as shown in the circuit diagram

2.The power supply voltage Vin is adjusted to be greater than or equal to

15V.

3. The load voltage VL are measured and recorded for various values of

R2.

4.To measure line regulation, load resistance is kept constant and load

voltage VL is measured for various values of Vin.

5.Graph is plotted with Vin versus VL

RESULT:

Thus the DC Power supply using LM317 is designed and graph is plotted..

LINEAR INTEGRATED CIRCUITS LAB P a g e | 68

Block diagram of NE 565 PLL +VCC

10

Input 2 3.6KΩ 7

Input 3 Phase Demodulated

Detector Amp. output

5

Phase 6 Reference

Comparator output

4

VCO VCO

Output

8 CT 9 1

+VCC RT CT

-VCC

CIRCUIT DIAGRAM FOR PLL:

+6V

RT 6.8K Ω C 1µF

C1 0.001µF

10 8

2

7 Demodulated

output

VIN a 6 Reference

NE 565 Output

5

3 VCO output (fo)

4

9 1

µF

0.001µ -6V

LINEAR INTEGRATED CIRCUITS LAB P a g e | 69

9. PLL CHARACTERISTICS AND FREQUENCYMULTIPLIER USING

NE565.

EX.NO :

DATE :

AIM:

To study the operation of NE565 PLL and to use it as frequency multiplier

APPARATUS REQUIRED:

Equipments & Range Quantity

Components

1. Power Supply (0-30)V 1

2.Resistors 6.8KΩ,20KΩ,2KΩ,10KΩ, each 1

4.7KΩ, 1

3.Capacitors 0.001µF,1µF,10µF,0.01µF 1

4.IC565 1

5.Transistor 2N2222 1

6.IC7490 1

7.AFO (0-1)MHz 1

8.CRO (0-20)MHz 1

THEORY:

IC NE565 phase locked loop is available as a 14-pin DIP package. The block

diagram is shown in figure1. The output frequency of the VCO (both inputs 2,3

grounded) is given by f0 = 0.25/RtCt Hz where Rt and Ct are the external resistor and

capacitor connected to pin8 and pin9 .The VCO free running is adjusted with Rt and Ct to

be at the center of the input frequency range. It may be seen that phase locked loop is

internally broken between the VCO output and the phase comparator input. A short

circuit between pins 4 and 5 connects the VCO output to the phase comparator so as to

compare f0 with input signal fs. A capacitor c is connected between pin7 and pin

10(supply terminal) to make a low pass filter with the internal resistance of 3.6k.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 70

PLL AS FREQUENCY MULTIPLIER:

+6V

20 kΩ

C=10µF

RT 2KΩ

C1=0.001µF

11 8

2

7

VIN

a 10kΩ

NE 565 4

3 5

9 1

fin

0.01µF -6V +6V

11

5 4.7kΩ

7490

(÷5)

1

2N2222

LINEAR INTEGRATED CIRCUITS LAB P a g e | 71

PROCEDURE:

Study of PLL:

1. Connections are made as shown in fig

2. The free running frequency of Vco at pin4 is measured with the input signal Vin

set equal to zero. It is compared with the calculated value = 0.25/RtCt

3. The input signal of 1Vpp square wave at a 1khz frequency is applied to pin2. The

signal is displayed on the scope.

4. The input frequency is increased gradually till the PLL is locked to the input

frequency. This frequency f1is the lower end of the capture range. The input

frequency is further increased to a frequency f2 till PLL tracks the input signal.

This frequency f2 gives the upper end of the lock range. If input frequency is

increased further the loop will get unlocked.

5. The input frequency is decreased gradually till the PLL is again locked. This is the

frequency f3, the upper end of the capture range. The input frequency is decreased

further until the loop is unlocked. This frequency f4 gives the lower end of the

lock range.

6.

The lock range ∆fL = f2-f4. It is compared with the calculated value of ±

7.8f0/12.also the capture range is ∆fc = f3-f1. It is compared with the calculated

value of capture range ∆fc = ± [∆fL/2Πx3.6x103xc] ½

PLL as frequency multiplier:

1. Connections are made as shown in fig. The circuit uses a 4 bit binary counter 7490

as a divide by 5 circuit.

2. The input signal is set at 1vpp square wave at 500Hz.

3. gThe VCO frequency is varied by adjusting the 20k potentiometer till the PLL is

locked. The output frequency is measured. It should be 5 times the input

frequency.

4. The step 2 and 3 are repeated for input frequency of 1KHZ and 1.5KHZ

RESULT:

PLL is studied and used as frequency multiplier

LINEAR INTEGRATED CIRCUITS LAB P a g e | 72

Schematic Diagram: Instrumentation Amplifier

Waveform:: Instrumentation Amplifier

LINEAR INTEGRATED CIRCUITS LAB P a g e | 73

11.SIMULATION USING PSPICE

(i) INSTRUMENTATION AMPLIFIER

EX.NO :

DATE :

Aim

To simulate instrumentation amplifier circuit using PSPICE circuit simulator and to verify the

corresponding graphs plotted.

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “DC sweep”.

4. Choose “voltage source” and complete the remaining options like start value and end

value.

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform will pop up after the simulation is done.

* Schematics Netlist *

R_R8 $N_0002 $N_0001 10k

R_R9 $N_0004 $N_0003 10k

R_R3 $N_0006 $N_0005 10k

R_R10 $N_0008 $N_0007 10k

R_R5 $N_0008 $N_0009 10k

R_R6 $N_0010 $N_0003 100k

R_R7 $N_0001 0 100k

R_R2 $N_0005 $N_0004 120k

R_R1 $N_0006 $N_0002 120k

E_U9 $N_0004 0 VALUE {LIMIT(V($N_0009,$N_0005)*1E6,-15V,+15V)}

E_U10 $N_0007 0 VALUE {LIMIT(V(0,$N_0008)*1E6,-15V,+15V)}

E_U11 $N_0010 0 VALUE {LIMIT(V($N_0001,$N_0003)*1E6,-15V,+15V)}

E_U12 $N_0002 0 VALUE {LIMIT(V($N_0007,$N_0006)*1E6,-15V,+15V)}

V_Vin $N_0009 0 25mV

Result

Thus the instrumentation amplifier circuit is simulated and the required graphs are

plotted.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 74

Schematic Diagram: Low pass-- second order filter

Waveform: Low pass- second oorder filter

LINEAR INTEGRATED CIRCUITS LAB P a g e | 75

(ii) LOW PASS – SECOND ORDER FILTER

EX.NO :

DATE :

Aim

To simulate low pass – second order filter circuit using PSPICE circuit simulator and to verify its

frequency response graph.

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “AC sweep”.

4. Choose “Decade” for graph type and complete the remaining options like start frequency

and end frequency .

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform will pop up after the simulation is done.

* Schematics Netlist *

R_R4 0 $N_0001 10k

R_R3 $N_0003 $N_0002 2.5k

R_R2 $N_0002 $N_0004 2.5k

C_C1 $N_0005 $N_0002 0.1u

R_R1 $N_0001 $N_0005 6.9k

V_Vin $N_0003 0 DC 0V AC 5V

E_U1 $N_0005 0 VALUE {LIMIT(V($N_0004,$N_0001)*1E6,-15V,+15V)}

C_C2 0 $N_0004 0.1u

Result

Thus the low pass – second order filter circuit is simulated and the required frequency

response graphs are plotted.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 76

Schematic Diagram: High pass

pass- second order filter

Waveform: High pass- second order filter

LINEAR INTEGRATED CIRCUITS LAB P a g e | 77

(iii) HIGH PASS – SECOND ORDER FILTER

EX.NO :

DATE :

Aim

To simulate high pass – second order filter circuit using PSPICE circuit simulator and to verify

its frequency response graph.

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “AC sweep”.

4. Choose “Decade” for graph type and complete the remaining options like start frequency

and end frequency .

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform will pop up after the simulation is done.

* Schematics Netlist *

V_V1 $N_0001 0 DC 0V AC 5V

E_U2 $N_0004 0 VALUE {LIMIT(V($N_0002,$N_0003)*1E6,-15V,+15V)}

C_C2 $N_0001 $N_0005 0.1u

C_C1 $N_0005 $N_0002 0.1u

R_R1 $N_0003 $N_0004 5.86k

R_R2 0 $N_0003 10k

R_R3 0 $N_0002 1.6k

R_R4 $N_0004 $N_0005 1.6k

Result

Thus the high pass – second order filter circuit is simulated and the required frequency

response graphs are plotted.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 78

Schematic Diagram: Band pass – second order filter

Waveform: Band pass – second order filter

LINEAR INTEGRATED CIRCUITS LAB P a g e | 79

(iv) BAND PASS – SECOND ORDER FILTER

EX.NO :

DATE :

Aim

To simulate band pass – second order filter circuit using PSPICE circuit simulator and to verify

its frequency response graph.

Software required

PSPICE students’ version 9.1

Procedure

7. Draw the schematic diagram in pspice schematic editor

8. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

9. Now select the option “AC sweep”.

10. Choose “Decade” for graph type and complete the remaining options like start frequency

and end frequency .

11. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

12. The waveform will pop up after the simulation is done.

* Schematics Netlist *

E_U1 $N_0002 0 VALUE {LIMIT(V(0,$N_0001)*1E6,-15V,+15V)}

R_R2 $N_0004 $N_0003 4.7k

R_R3 $N_0002 $N_0001 100k

C_C2 $N_0001 $N_0002 0.01u

C_C1 $N_0004 $N_0001 0.01u

V_Vin $N_0003 0 DC 0V AC 5V

R_R4 0 $N_0002 10k

R_R1 0 $N_0004 6.2k

Result

Thus the band pass – second order filter circuit is simulated and the required frequency

response graphs are plotted.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 80

Schematic Diagram: Astable multivibrator using opamp

Waveform: Astable multivibrator

LINEAR INTEGRATED CIRCUITS LAB P a g e | 81

(v) ASTABLE MULTIVIBRATOR USING OPAMP

EX.NO :

DATE :

Aim

To simulate astable multivibrator circuit (opamp based) using PSPICE circuit simulator and to

verify the waveform

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “transient”.

4. Choose appropriate print step (eg:10 ns) and final time.

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform window will pop up after the simulation.

* Schematics Netlist *

R_R3 $N_0002 $N_0001 4.55k

E_U1 $N_0001 0 VALUE {LIMIT(V($N_0003,$N_0002)*1E6,-15V,+15V)}

R_R2 0 $N_0003 10k

R_R1 $N_0003 $N_0001 10k

C_C1 0 $N_0002 0.1u IC=0.001V

Result

Thus the astable multivibrator circuit using opamp is simulated and the required

waveforms are obtained.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 82

Schematic Diagram: Monostable

stable multivibrator using opamp

Waveform: Monostable multivibrator using opamp

LINEAR INTEGRATED CIRCUITS LAB P a g e | 83

(vi). MONOSTABLE MULTIVIBRATOR USING OPAMP

EX.NO :

DATE :

Aim

To simulate monostable multivibrator circuit (opamp based) using PSPICE circuit simulator and

to verify the waveform.

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “transient”.

4. Choose appropriate print step (eg:10 ns) and final time.

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform window will pop up after the simulation.

* Schematics Netlist *

R_R1 $N_0002 $N_0001 1k

D_D2 $N_0003 $N_0004 D1N4002

R_R3 0 $N_0003 1k

D_D3 $N_0002 0 D1N4002

R_R2 $N_0003 $N_0001 10k

R_R5 $N_0006 $N_0005 4.55k

R_R6 0 $N_0007 10k

R_R7 $N_0007 $N_0005 10k

C_C2 0 $N_0002 1u

R_R4 0 $N_0004 22k

E_U2 $N_0005 0 VALUE {LIMIT(V($N_0007,$N_0006)*1E6,-15V,+15V)}

E_U1 $N_0001 0 VALUE {LIMIT(V($N_0003,$N_0002)*1E6,-15V,+15V)}

C_C3 0 $N_0006 0.05u IC=0.001V

C_C1 $N_0005 $N_0004 10u

Result

Thus the astable multivibrator circuit using opamp is simulated and the required

waveforms are obtained.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 84

Schematic Diagram:

agram: SCHMITT TRIGGER

Waveform: SCHMITT TRIGGER

LINEAR INTEGRATED CIRCUITS LAB P a g e | 85

(vii). SCHMITT TRIGGER USING OPAMP

EX.NO :

DATE :

Aim

To simulate Schmitt Trigger circuit (opamp based) using PSPICE circuit simulator and to verify

the waveform.

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “transient”.

4. Choose appropriate print step (eg:10 ns) and final time.

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform window will pop up after the simulation.

* Schematics Netlist *

R_R2 0 $N_0001 1k

R_R1 $N_0001 $N_0002 27k

E_U1 $N_0002 0 VALUE {LIMIT(V($N_0001,$N_0003)*1E6,-15V,+15V)}

R_R3 $N_0004 $N_0003 1k

V_V1 $N_0004 0 STIMULUS=sine

Result

Thus the Schmitt Trigger circuit using opamp is simulated and the required waveforms

are obtained.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 86

Schematic Diagram: RC phase shift oscillator

Waveform:: RC phase shift oscillator

LINEAR INTEGRATED CIRCUITS LAB P a g e | 87

(viii). RC PHASE SHIFT OSCILLATOR

EX.NO :

DATE :

Aim

To simulate the RC phase shift oscillator using PSPICE circuit simulator and to verify the

waveform

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “transient”.

4. Choose appropriate print step (eg:10 ns) and final time.

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform window will pop up after the simulation.

* Schematics Netlist *

C_C3 $N_0001 $N_0002 0.1u

R_R1 $N_0003 $N_0002 390k

R_R2 $N_0004 $N_0003 13k

R_R6 0 $N_0004 1.5k

R_R5 0 $N_0005 1.5k

R_R4 0 $N_0001 1.5k

C_C1 $N_0005 $N_0001 0.1u

R_R3 0 $N_0006 15k

C_C2 $N_0004 $N_0005 0.1u IC=.001

X_U2A $N_0003 $N_0006 v+ v- $N_0002 LM324

V_V2 0 v- 15V

V_V1 v+ 0 15V

Result

Thus the RC phase shift oscillator using opamp is simulated and the required waveforms

are obtained.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 88

Schematic Diagram : Wien bridge oscillator

Waveform : Wien bridge oscillator

LINEAR INTEGRATED CIRCUITS LAB P a g e | 89

(ix). WIEN BRIDGE OSCILLATOR

EX.NO :

DATE :

Aim

To simulate the wien bridge oscillator using PSPICE circuit simulator and to verify the

waveform

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “transient”.

4. Choose appropriate print step (eg:10 ns) and final time.

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform window will pop up after the simulation.

* Schematics Netlist *

C_C2 $N_0001 $N_0002 0.01u

C_C1 0 $N_0003 0.01u IC=.1

E_U1 $N_0002 0 VALUE {LIMIT(V($N_0003,$N_0004)*1E6,-15V,+15V)}

R_R4 $N_0004 $N_0002 31.8k

R_R3 0 $N_0004 15.9k

R_R2 $N_0003 $N_0001 1.59k

R_R1 0 $N_0003 1.59k

Result

Thus the wien bridge oscillator using opamp is simulated and the required waveforms are

obtained.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 90

Schematic Diagram: Astable multivibrator using 555 timer

Waveform: Astable multivibrator

LINEAR INTEGRATED CIRCUITS LAB P a g e | 91

(x). ASTABLE MULTIVIBRATOR USING 555 TIMER

EX.NO :

DATE :

Aim

To simulate the astable multivibrator (555 timer based) using PSPICE circuit simulator and to

verify the waveform

Software required

PSPICE students’ version 9.1

Procedure

1. Draw the schematic diagram in pspice schematic editor

2. Go choose the icon “set up -> analysis”, for choosing proper analysis options.

3. Now select the option “transient”.

4. Choose appropriate print step (eg:10 ns) and final time.

5. Now choose the icon “set up -> Examine netlist”, and if the netlist has no errors, choose

the “simulate” option which is under “set up”.

6. The waveform window will pop up after the simulation.

* Schematics Netlist *

D_D2 $N_0001 $N_0002 D1N4002

V_V1 $N_0003 0 5V

C_C2 0 $N_0004 .01u

C_C1 0 $N_0002 .01u

R_R1 $N_0001 $N_0002 3.63k

R_R2 $N_0001 $N_0003 7.3k

X_X1 0 $N_0002 $N_0005 $N_0003 $N_0004 $N_0002 $N_0001 $N_0003 555D

+ PARAMS: MAXFREQ=3E6

R_R3 0 $N_0005 100k

Result

Thus the astable multivibrator circuit using 555 timer is simulated and the required

waveforms are obtained.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 92

HALF WAVE RECTIFIER

10K

1N4007

10K

VO(CRO

AFO )

a 1N4007

10KΩ

VI(v)

t(msec)

Vo(v)

t(msec)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 93

12.ADDITIONAL EXPERIMENTS

(a). PRECISION RECTIFIER

EX.NO :

DATE :

AIM:

To construct and study the working of half wave and full wave precision rectifiers.

APPARATUS REQUIRED:

1. IC 741 -2Nos

2. Diode(1N4007) -2 Nos

3. Resistor 10Kohm -6 Nos

4. Dual power supply (0-30) v-1 No

5. AFO (0 to 1 MHZ) -1 No

6. CRO (0 to 20 MHZ) -1 No

DESIGN:

All the resistances are chosen as 10 Kohms and this condition make output voltage

is equal to the input voltage.

THEORY:

Matched diodes are used .To get matched diodes CA3046 transistor array is used.

This CA3046 in an IC with 5 transistors in a DIP package. If matched are not used for

FWR the positive halves of the rectified wave will not be equal. Precision rectifier

rectifies voltages of the order of millivolts much lower than the cut in voltage of diodes.

All the resistances are chosen in kilo ohm range so that the AFO is not loaded and much

greater than the o/p resistance of AFO (50 ohm).

MAX WATTAGE OF RESISTANCE:

Resistances used in the design are 1Kohm and 10Kohms .The maximum voltages

across the resistance will be supply voltage. Hence wattage of resistance is V2 / R.

V2 /R= 225 / 10K which is so much lower than 1/8W or 1/4W.So resistances with 5%

tolerance, carbon film resistor with 1/8W or 1/4W is used.

PROCEDURE:

1. Connections are made as shown in fig

2. The transfer characteristic of the FWR is done for direct voltages of positive and

negative values.

3. For this a variable supply with course knob of the supply fully anticlockwise and

fine knob is adjusted to get voltage in the range of 1-50mv in both polarities.

4. Various I/p voltages are applied to FWR and o/p voltages are noted. For the

measurement of input and output voltage DMM in dc range is used.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 94

FULL WAVE RECTIFIER:

10KΩ 10KΩ 10KΩ

10KΩ 1N4007

VO(CRO)

AFO

a

10KΩ

1N4007

10KΩ

Vin

t(msec)

VO(v)

t(msec)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 95

5. Experiment is to done for both polarities of input voltage. Note that slope=1 and

small signal gain is equal to slope. The transfer characteristics is shown in fig.

6. Alternatively an ac input can also be given from an AFO, with amplitude in

millivolts range. The input and output waveforms are viewed on the CRO &

plotted as shown in model graph.

TABULAR COLUMN:

Voltage Time Frequency

Half wave

Input.

Output

Full wave

Input

Output

RESULT:

The input and output waveforms of the HWR & FWR are plotted.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 96

COMPARATOR WITH POSITIVE Vref

1 KΩ

VO(CRO)

_

AFO a

1 KΩ

Vref = 0.5V

MODEL GRAPH:

Vi

VREF

T (msec)

Vo

+VSAT

T (msec)

-VSAT

LINEAR INTEGRATED CIRCUITS LAB P a g e | 97

(b). COMPARATOR

EX.NO :

DATE :

AIM:

To design the comparator in non-inverting mode using op-amp.

APPARATUS REQUIRED: -

1. IC741 -1No

2. Resistor 1Kohm -2 Nos

3. AFO -1 No

4. CRO -1 No

5. RPS -1 No

6. Linear IC trainer -1 No

7. Dual power supply -1 No

THEORY: -

A comparator is a circuit, which compares a signal voltage applied at one input of

an op-amp with a known reference voltage at the other input. It is basically an open loop

op-amp with output I V (=Vcc). There are two types of comparators. (a) Non-inverting

comparator (b) inverting comparator

NON- INVERTING COMPARATOR: -

In this circuit, a fixed reference voltage V reference is applied to inverting input

and a time varying signal Vi is applied to non- inverting input. The output voltage is at -

Vsat for Vi < Vref and V0 goes to t Vsat for Vi > Vref. The Vref may be positive or

negative voltage.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 98

COMPARATOR WITH NEGATIVE Vref

1 KΩ

VO(CRO)

AFO --

a

1 KΩ

Vref = -o.5V

VI

T (msec)

-VREF

V0

+VSAT

T (msec)

-VSAT

LINEAR INTEGRATED CIRCUITS LAB P a g e | 99

PROCEDURE: -

1. The circuit is connected as shown in figure and reference=+0.5V is applied.

2. The signal generator is adjusted so that VI = 2 Vpp sine wave at 1KHz

3. Using a CRO the input and output waveforms are observed simultaneously. The

output waveform is plotted.

4. The circuit is connected as shown in fig and Vref =-0.5V is applied steps 2 and 3

are repeated.

RESULT:

The operation of the comparator is studied.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 100

TRIANGULAR WAVE GENERATOR

0.01µF

VO

MODEL GRAPH:

Vo

T(msec)

LINEAR INTEGRATED CIRCUITS LAB P a g e | 101

(c).TRIANGULAR WAVEFORM GENERATOR

EX.NO :

DATE :

AIM:

To construct and study the operation of a triangular waveform generator using IC

741.

APPARATUS REQUIRED:

1. IC741 -2Nos

2. Resistor 10Kohm -2 Nos

3. 1Mohm -1 No

4. 100kohm -1 No

5. Capacitor 0.01MFD -1 No

6. 0.05MFD -1 No

7. Pot 100kohm -1 No

8. CRO -1 No

9. RPS -1 No

10. Linear IC trainer. -1 No

THEORY:

A triangular is generated by integrating a square waveform. The circuit uses a

square waveform generator and integrator. The frequencies of the two waveforms are

equal while the amplitude of triangular waveform is smaller. The decrease in amplitude is

because the reactance of the feedback capacitor C2 decreases with increase in frequency.

The resistor R2 is connected in parallel with C2 to avoid saturation problems at low

frequencies.

PROCEDURE:

1. Connections are made as shown in circuit diagram .

2. The output voltages VO1 and VO2 are noted.

3. The amplitude and time period of the square wave VO1 and triangular wave

VO2 are recorded.

RESULT:

A triangular wave generator is constructed using IC741 and studied.

LINEAR INTEGRATED CIRCUITS LAB P a g e | 102

Das könnte Ihnen auch gefallen

- Electronic Circuits Lab Manual Clippers and AmplifiersDokument29 SeitenElectronic Circuits Lab Manual Clippers and AmplifiersAshwath NadahalliNoch keine Bewertungen

- LIC Manual NewDokument84 SeitenLIC Manual NewVandhana PramodhanNoch keine Bewertungen

- LIC Lab Manual Anna UniversityDokument83 SeitenLIC Lab Manual Anna Universityankitha rajanNoch keine Bewertungen

- LIC Lab ManualDokument65 SeitenLIC Lab ManualBala Subramanian0% (1)

- LIC Lab ManualDokument79 SeitenLIC Lab ManualSakthikumar Balasundaram67% (3)

- Ranganathan Polytechnic College Coimbatore.: Simulation Practical Lab ManualDokument32 SeitenRanganathan Polytechnic College Coimbatore.: Simulation Practical Lab ManualBala SVD100% (1)

- ECD Lab EEC 752Dokument17 SeitenECD Lab EEC 752juhi99360% (5)

- Einfochips Interview QuestionsDokument1 SeiteEinfochips Interview Questionsshafi hasmani100% (1)

- R20 JNTUK EEE IOT LAB Manual Final PrintDokument58 SeitenR20 JNTUK EEE IOT LAB Manual Final PrintDr koteswararao seelamNoch keine Bewertungen

- EE8461-Linear and Digital Integrated Circuits-Lab ManualDokument96 SeitenEE8461-Linear and Digital Integrated Circuits-Lab ManualSETNHILNoch keine Bewertungen

- Expt 5 - Wein Bridge Oscillator (2020)Dokument3 SeitenExpt 5 - Wein Bridge Oscillator (2020)samarthNoch keine Bewertungen

- Lab ManualDokument66 SeitenLab ManualcommunicationridersNoch keine Bewertungen

- Network Analysis Notes CompiledDokument50 SeitenNetwork Analysis Notes CompiledmaruthinmdcNoch keine Bewertungen

- Title: Design of A Flash Analog To Digital ConverterDokument4 SeitenTitle: Design of A Flash Analog To Digital Converteranon_776365175Noch keine Bewertungen

- Week 7 - Direct-Current Bridge PDFDokument43 SeitenWeek 7 - Direct-Current Bridge PDFWeng YeeNoch keine Bewertungen

- Atal FDP On Sensor Technology - 2Dokument3 SeitenAtal FDP On Sensor Technology - 2Rameshkumar JayaramanNoch keine Bewertungen

- Lab # 01 To Study The Transient Response of RL Series Circuit MaterialsDokument4 SeitenLab # 01 To Study The Transient Response of RL Series Circuit MaterialsYasir100% (1)

- Ec8361-Adc Lab ManualDokument118 SeitenEc8361-Adc Lab ManualmuminthajNoch keine Bewertungen

- GURU NANAK DEV ENGINEERING COLLEGE QUESTION BANKDokument2 SeitenGURU NANAK DEV ENGINEERING COLLEGE QUESTION BANKSavita SomaNoch keine Bewertungen

- Buffer AmplifierDokument9 SeitenBuffer AmplifierDicky D.M.Noch keine Bewertungen

- DC Characteristics of Op-AmpDokument7 SeitenDC Characteristics of Op-AmpVENKATESWARLU MUVVA (PA2111004040011)Noch keine Bewertungen

- Lica Lab Manual PDFDokument42 SeitenLica Lab Manual PDFKashif AliNoch keine Bewertungen

- Electronics Circuits Lab ManualDokument109 SeitenElectronics Circuits Lab ManualIndische Mädchen100% (2)

- STLD Lab Manual ExperimentsDokument42 SeitenSTLD Lab Manual ExperimentssaikiranNoch keine Bewertungen

- MOSFET - Working, Types, Operation, Advantages & ApplicationsDokument28 SeitenMOSFET - Working, Types, Operation, Advantages & ApplicationsgezahegnNoch keine Bewertungen

- Eca NotesDokument220 SeitenEca NotesKiranmai KonduruNoch keine Bewertungen

- Microprocessor and Microcontroller Course Objectives and OutcomesDokument2 SeitenMicroprocessor and Microcontroller Course Objectives and OutcomescoolkannaNoch keine Bewertungen

- Notes On Applied Physics (Based On R19 Regulation) - by Shaik Gouse BashaDokument285 SeitenNotes On Applied Physics (Based On R19 Regulation) - by Shaik Gouse BashaShaik Gouse Basha71% (7)

- ABC DQ TransformationDokument2 SeitenABC DQ TransformationRoop Kapur0% (1)

- Electronic Circuits & Logic Design Lab ManualDokument83 SeitenElectronic Circuits & Logic Design Lab ManualsunandaalurNoch keine Bewertungen

- 1.circuits and Simulation Integrated Laboratory 2013 RegulationDokument46 Seiten1.circuits and Simulation Integrated Laboratory 2013 RegulationNandha KumarNoch keine Bewertungen

- Worked ExamplesDokument11 SeitenWorked ExamplesAli AltahirNoch keine Bewertungen

- Slides - LabVIEW 3 Hour Hands-On With myDAQDokument73 SeitenSlides - LabVIEW 3 Hour Hands-On With myDAQRockyFu100% (1)

- The Digital Encoder: 4-To-2 Bit Binary EncoderDokument10 SeitenThe Digital Encoder: 4-To-2 Bit Binary EncoderJohn Brix BalisterosNoch keine Bewertungen

- List of Edc ManualDokument88 SeitenList of Edc ManualPatricia Grace PerezNoch keine Bewertungen

- Power Electronics Lab Manual With LogoDokument69 SeitenPower Electronics Lab Manual With LogoPunith Gowda M BNoch keine Bewertungen

- EMI Q BankDokument21 SeitenEMI Q BankShiv KumarNoch keine Bewertungen

- EC8462 LIC Lab ManualDokument98 SeitenEC8462 LIC Lab ManualPrakash Velayudham VNoch keine Bewertungen

- EC8462Dokument86 SeitenEC8462ur's joeNoch keine Bewertungen

- EC II Unit 3Dokument33 SeitenEC II Unit 3Thiyagarajan VelayuthamNoch keine Bewertungen

- DC - Ac Inv.Dokument82 SeitenDC - Ac Inv.Jegadeeswari GNoch keine Bewertungen

- Advance Communication Lab-15ECL76Dokument39 SeitenAdvance Communication Lab-15ECL76Pradeep kumarNoch keine Bewertungen

- Lap Manual Pspice PDFDokument17 SeitenLap Manual Pspice PDFred_heartedNoch keine Bewertungen

- 12 - Operational AmplifiersDokument27 Seiten12 - Operational Amplifierssgw67Noch keine Bewertungen

- Inverting Amplifiers Lab ReportDokument9 SeitenInverting Amplifiers Lab ReportRaihan JannatiNoch keine Bewertungen

- Lecture Notes On Electronics CircuitsDokument54 SeitenLecture Notes On Electronics CircuitsKashif AhmedNoch keine Bewertungen

- Transistor at Low FrequenciesDokument40 SeitenTransistor at Low Frequenciesjoydeep12100% (1)

- Power Electronics Lab ManualDokument47 SeitenPower Electronics Lab Manualshaan_patil100% (1)

- Download Full Wave Rectifier Circuits and FiltersDokument10 SeitenDownload Full Wave Rectifier Circuits and FiltersVenkata PavanNoch keine Bewertungen

- Department of Electrical and Electronics Engineering: List of Experiments SL - No Name of The Experiment Page NoDokument51 SeitenDepartment of Electrical and Electronics Engineering: List of Experiments SL - No Name of The Experiment Page Nosuresh270Noch keine Bewertungen

- 47-Wavelet Based Power Quality Disturbances Analysis of BLDC Motor Drive PDFDokument10 Seiten47-Wavelet Based Power Quality Disturbances Analysis of BLDC Motor Drive PDFveerannaNoch keine Bewertungen

- Digital Communication Lab Manual ExperimentsDokument50 SeitenDigital Communication Lab Manual ExperimentsAniket BhowmikNoch keine Bewertungen

- BEEE 2marks (With Ans)Dokument25 SeitenBEEE 2marks (With Ans)Nanda SubramanianNoch keine Bewertungen