Beruflich Dokumente

Kultur Dokumente

Kim S Abstract

Hochgeladen von

api-2723161830 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

105 Ansichten1 SeiteFPGA Prototyping and Software Construction for ASIC and USB Interface for stereo vision hardware accelerator. This study determines the extent to which functionality of ASICs and interface between the chip and USB peripheral controller (FX3) can be verified. As the interface between ASIC and FX3 involves 12 signals, debugging of the behavior requires designers to observe real--time signals and transitions.

Originalbeschreibung:

Originaltitel

kim s abstract

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenFPGA Prototyping and Software Construction for ASIC and USB Interface for stereo vision hardware accelerator. This study determines the extent to which functionality of ASICs and interface between the chip and USB peripheral controller (FX3) can be verified. As the interface between ASIC and FX3 involves 12 signals, debugging of the behavior requires designers to observe real--time signals and transitions.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

105 Ansichten1 SeiteKim S Abstract

Hochgeladen von

api-272316183FPGA Prototyping and Software Construction for ASIC and USB Interface for stereo vision hardware accelerator. This study determines the extent to which functionality of ASICs and interface between the chip and USB peripheral controller (FX3) can be verified. As the interface between ASIC and FX3 involves 12 signals, debugging of the behavior requires designers to observe real--time signals and transitions.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 1

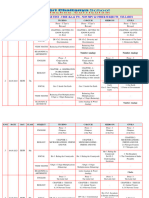

FPGA

Prototyping and Software Construction for ASIC and USB Interface

for Stereo Vision Hardware Accelerator

Sungil Kim1, Ziyun Li2, Hun-Seok Kim2, and David T. Blaauw2

1Department of Electrical and Computer Engineering, Auburn University 200 Broun Hall,

Auburn,

AL

36830

2Department

of

Electrical

Engineering

and

Computer

Science,

University

of

Michigan

1301

Beal Avenue, Ann Arbor, MI 48109

ASICs (Application-Specific Integrated Circuits) development cost is increasing due to

emerging design and computational complexity, while time to market is decreasing due to

fast-growing technology. To reduce potential failures and cost, ASIC design that uses FPGA

(Field-Programmable Gate Array) prototyping to verify functionality of the circuit is both

effective and reliable, especially for real-time systems like stereo cameras. We develop a

faster stereo vision hardware accelerator that consumes less power than a GPU-based

stereo camera by addressing the data communication between the ASIC chip, FX3, and host

PC. Yet, streaming from the chip and into the chip needs verification. This study determines

the extent to which functionality of ASICs and Interface between the chip and USB

peripheral controller (FX3) can be verified. Coupled with software verification, FPGA

performs the logic behavior of the chip to run at near real time with data transfer rate of 2

Gigabits per second. As the interface between ASIC and FX3 involves 12 signals (i.e., clock,

flags, read/write strobe, address, 32-bit data), debugging of the behavior requires designers

to observe real-time signals and transitions. Using Xilinx ChipScope Pro, we verify the

handshaking and timing. From the host side, we prototype with compatible software

libraries for USB interfaces. After processing left and right images, the developed software

verifies the bidirectional data transfer. These results suggest FPGA prototyping is

particularly effective for handling real-time signals. The verifying step via FPGA prototyping

can significantly reduce chip failure and manufacturing cost and increase design pace.

Das könnte Ihnen auch gefallen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- XY Model Symmetric (Broken) Phase Normal (Supercon-Ducting) PhaseDokument12 SeitenXY Model Symmetric (Broken) Phase Normal (Supercon-Ducting) PhaseKay WuNoch keine Bewertungen

- Buddhism in AndhraDokument16 SeitenBuddhism in AndhraRaghavendrarao ChukkaNoch keine Bewertungen

- HRM BBA AssignmentsDokument2 SeitenHRM BBA AssignmentsNitin GargNoch keine Bewertungen

- Bkai3043 Topic 1Dokument16 SeitenBkai3043 Topic 1Ros Shinie BalanNoch keine Bewertungen

- A10 0250 (Rev. H 2000.09) EN - TECHNICAL SPECIFICATIONS SAFETY - REGULATION DEFINITION - PRESENTATIONDokument9 SeitenA10 0250 (Rev. H 2000.09) EN - TECHNICAL SPECIFICATIONS SAFETY - REGULATION DEFINITION - PRESENTATIONDiego CamargoNoch keine Bewertungen

- Functional Specification05830264312 PDFDokument96 SeitenFunctional Specification05830264312 PDFEleonoraNoch keine Bewertungen

- Global Major Incidents List 1902-2009Dokument56 SeitenGlobal Major Incidents List 1902-2009utopianzhereNoch keine Bewertungen

- Utm EnglishDokument23 SeitenUtm Englishapi-240506461Noch keine Bewertungen

- Egg Osmosis LabDokument5 SeitenEgg Osmosis Labapi-391626668Noch keine Bewertungen

- Cost Comp - MF UF Vs TraditionalDokument8 SeitenCost Comp - MF UF Vs TraditionalahanraNoch keine Bewertungen

- NCERT Solutions For Class 12 English Flamingo Chapter 8Dokument3 SeitenNCERT Solutions For Class 12 English Flamingo Chapter 8AKASH KUMARNoch keine Bewertungen

- Capgemini 2017 Informe AnualDokument360 SeitenCapgemini 2017 Informe Anualjoseosteopatia3693Noch keine Bewertungen

- Standards Booklet For Igsce Sociology (0495)Dokument64 SeitenStandards Booklet For Igsce Sociology (0495)Ingrit AgustinNoch keine Bewertungen

- NSCP 2015Dokument1.032 SeitenNSCP 2015Rouzurin Ross100% (1)

- 8 4 Function NotationDokument16 Seiten8 4 Function Notationapi-233527181Noch keine Bewertungen

- Number System ConversionDokument5 SeitenNumber System Conversionrakotogogo1Noch keine Bewertungen

- Grammar: Present Simple and Present ContinuousDokument9 SeitenGrammar: Present Simple and Present ContinuousMarialucia LugnaniNoch keine Bewertungen

- Class Notes Microsoft Office Word DocumentDokument89 SeitenClass Notes Microsoft Office Word DocumentAriyani 'ayiex' EstiningrumNoch keine Bewertungen

- Leadership in The Construction Industry 2008Dokument24 SeitenLeadership in The Construction Industry 2008Gishan SanjeewaNoch keine Bewertungen

- PFI ES-27-1994 - Visual Examination - The Purpose, Meaning and Limitation of The TermDokument4 SeitenPFI ES-27-1994 - Visual Examination - The Purpose, Meaning and Limitation of The TermThao NguyenNoch keine Bewertungen

- OCOM FTA ReviewerDokument5 SeitenOCOM FTA ReviewerJulluis DagoNoch keine Bewertungen

- КТП 6-сынып 2022-23Dokument14 SeitenКТП 6-сынып 2022-23AraikaNoch keine Bewertungen

- mt1173 Vle PDFDokument287 Seitenmt1173 Vle PDFKhushal JhajahriaNoch keine Bewertungen

- Nei Nastran in Cad 2011 BrochureDokument8 SeitenNei Nastran in Cad 2011 Brochurexuanphuong2710Noch keine Bewertungen

- The Eight Types of Interview QuestionsDokument2 SeitenThe Eight Types of Interview QuestionsKayla Camille A. Miguel100% (1)

- Rhetoric AnalysisDokument3 SeitenRhetoric AnalysisSam RussellNoch keine Bewertungen

- 6th STD Balbharti English Textbook PDFDokument116 Seiten6th STD Balbharti English Textbook PDFꜱᴀꜰᴡᴀɴ ꜱᴋNoch keine Bewertungen

- Infinity Meta Weekly Ot - Ka & TN - Non MPC & Other Subjects - SyllabusDokument2 SeitenInfinity Meta Weekly Ot - Ka & TN - Non MPC & Other Subjects - SyllabusR PranavNoch keine Bewertungen

- Theatre at HierapolisDokument7 SeitenTheatre at HierapolisrabolaNoch keine Bewertungen

- Leonardo Tutorial Final Vers5 ENGLISHDokument241 SeitenLeonardo Tutorial Final Vers5 ENGLISHCostin-Sebastian ManuNoch keine Bewertungen