Beruflich Dokumente

Kultur Dokumente

Sheet#1: Show Them in Proper Relation To The Enable Input. Assume That Q Starts LOW

Hochgeladen von

Sherweet A. AlsaadanyOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Sheet#1: Show Them in Proper Relation To The Enable Input. Assume That Q Starts LOW

Hochgeladen von

Sherweet A. AlsaadanyCopyright:

Verfügbare Formate

Sheet#1

1. Given the input waveforms in Figure applied to an active-HIGH S-R latch.

a. Draw output waveform Q.

b. Draw Q if the same input is applied to an active-Low S-R latch.

2.

For a gated S-R latch. Determine the Q and Q outputs for the inputs in Figure.

Show them in proper relation to the enable input. Assume that Q starts LOW.

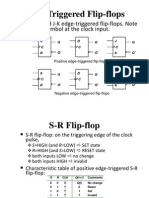

3. Two edge-triggered S-R flip-flops are shown in Figure. If the inputs are as shown.

Draw the Q output of each flip-flop relative to the clock and explain the difference

between the two. The flip-flops are initially RESET.

1|Page

4. For a positive edge-triggered J-K flip-flop with inputs as shown in Figure,

determine the Q output relative to the clock. Assume that Q starts LOW.

5. The following serial data are applied to the flip-flop through the AND gates as indicated

in figure. Determine the resulting serial data that appear on the Q output. There is one

clock pulse for each bit time. Assume that Q is initially 0 and that PRE and CLR are

HIGH. Rightmost bits are applied first.

J1: 10100 11, J2: 0111010, J3: 1111000

K1: 0001110, K2: 1101100, K3: 1010101

6. Determine the Q waveform relative to the clock if the signals shown in Figure are applied

to the inputs of the J-K flip-flop. Assume that Q is initially LOW.

2|Page

7. A D flip-flop is connected as shown in Figure. Determine the Q output in relation to the

clock. What specific function does this device perform?

3|Page

Das könnte Ihnen auch gefallen

- 01 SheetDokument4 Seiten01 Sheetmohamedems719Noch keine Bewertungen

- Problems 4 (Chapter 5) PDFDokument6 SeitenProblems 4 (Chapter 5) PDF217152 Nguyễn Phương Nhật HiềnNoch keine Bewertungen

- Latches, Flip-Flops, Timers ExplainedDokument36 SeitenLatches, Flip-Flops, Timers ExplainedMuhammad Umair AslamNoch keine Bewertungen

- SR LatchDokument11 SeitenSR LatchMinSoo Tom KimNoch keine Bewertungen

- Topic 5 - Flip Flops Sequential CircuitsDokument16 SeitenTopic 5 - Flip Flops Sequential CircuitsShivneet KumarNoch keine Bewertungen

- HW2904 6Dokument3 SeitenHW2904 6Nigel CastilloNoch keine Bewertungen

- Experiment 3Dokument4 SeitenExperiment 3Ishan Satya PrakashNoch keine Bewertungen

- Flip Flop Mealy and Moore ModelDokument25 SeitenFlip Flop Mealy and Moore Modelsurajpb1989100% (1)

- EE 2310 Homework #3 Solutions - Flip Flops and Flip-Flop CircuitsDokument4 SeitenEE 2310 Homework #3 Solutions - Flip Flops and Flip-Flop CircuitsJaffer RazaNoch keine Bewertungen

- Flipflops and WaveformsDokument22 SeitenFlipflops and WaveformsmadhuriNoch keine Bewertungen

- DE Module 03Dokument20 SeitenDE Module 03Rishabh TiwariNoch keine Bewertungen

- Digital Electronics 1 - Understanding Asynchronous and Synchronous CountersDokument62 SeitenDigital Electronics 1 - Understanding Asynchronous and Synchronous CountersSanaAzharKhanNoch keine Bewertungen

- PracticalDokument10 SeitenPracticalSumeet SauravNoch keine Bewertungen

- Digital Systems 2 - Chapter 7 - Assignment 1 - LatchesDokument2 SeitenDigital Systems 2 - Chapter 7 - Assignment 1 - LatchesBonolo TselaNoch keine Bewertungen

- Experiment 10 J-K Flip-Flop TestingDokument2 SeitenExperiment 10 J-K Flip-Flop TestingFaiza Tabassam 546-FET/BSEE/F19Noch keine Bewertungen

- De Assignment 3Dokument2 SeitenDe Assignment 32K19/CO/281 PRANAV BHATNAGARNoch keine Bewertungen

- CSCI350-S22-Assignment 4Dokument1 SeiteCSCI350-S22-Assignment 4Atharva TemkarNoch keine Bewertungen

- How Flip Flops Work as Basic Memory UnitsDokument6 SeitenHow Flip Flops Work as Basic Memory UnitsSriharsha Pidaparthi100% (1)

- Chapter 1: Counters and State Machine Design: 1.2.1 Clocked SR Flip-FlopDokument22 SeitenChapter 1: Counters and State Machine Design: 1.2.1 Clocked SR Flip-FlopAkik SapreNoch keine Bewertungen

- Sequential Circuits: Latches and Flip-FlopsDokument32 SeitenSequential Circuits: Latches and Flip-FlopsRohan BorgalliNoch keine Bewertungen

- DDCO QBDokument20 SeitenDDCO QB333jayanth333Noch keine Bewertungen

- Technological Studies: Applied Electronics (AH) Sequential Logic DevicesDokument116 SeitenTechnological Studies: Applied Electronics (AH) Sequential Logic DevicesPham PunNoch keine Bewertungen

- Latches and Flip-Flops: Experiment E10Dokument9 SeitenLatches and Flip-Flops: Experiment E10Resy ApolinarioNoch keine Bewertungen

- ECE590 - Tutorial 6 (UiTM)Dokument3 SeitenECE590 - Tutorial 6 (UiTM)NazhammerheartNoch keine Bewertungen

- Automatic Water Pump ControllerDokument19 SeitenAutomatic Water Pump ControllerSrinivasRaoNoch keine Bewertungen

- ExptDokument7 SeitenExptM SHOAIB KHALIDNoch keine Bewertungen

- Asynchronous 4-Bit Counter CircuitDokument5 SeitenAsynchronous 4-Bit Counter CircuitPranav Ranjith KumarNoch keine Bewertungen

- Gated SR Latch: CSE 271 - Introduction To Digital Systems Supplementary Reading Some Basic Memory ElementsDokument8 SeitenGated SR Latch: CSE 271 - Introduction To Digital Systems Supplementary Reading Some Basic Memory ElementsJohnNoch keine Bewertungen

- Ring Counter:: ST ND RD STDokument28 SeitenRing Counter:: ST ND RD STJatin AroraNoch keine Bewertungen

- Asynchronous Counters: CSE 271 - Introduction To Digital Systems Supplementary Reading Counters With T Flip-FlopsDokument4 SeitenAsynchronous Counters: CSE 271 - Introduction To Digital Systems Supplementary Reading Counters With T Flip-FlopsSelvasundar Kumar100% (2)

- Lecture 7: Memory: DOC112: Computer Hardware Lecture 7 1Dokument4 SeitenLecture 7: Memory: DOC112: Computer Hardware Lecture 7 1Taqi Shah0% (1)

- DIGITAL ELECTRONICS II - JK Flipflop With Asynchronous Inputs-1-1Dokument18 SeitenDIGITAL ELECTRONICS II - JK Flipflop With Asynchronous Inputs-1-1Freddy MutuaNoch keine Bewertungen

- Synchronous Counter Design and AnalysisDokument12 SeitenSynchronous Counter Design and AnalysisRajasekar PichaimuthuNoch keine Bewertungen

- Unit 5 Sequential CircuitDokument21 SeitenUnit 5 Sequential CircuitAnurag GoelNoch keine Bewertungen

- Experiment No 10Dokument10 SeitenExperiment No 10atulNoch keine Bewertungen

- Digital Electronics 1-Sequential Circuit CountersDokument20 SeitenDigital Electronics 1-Sequential Circuit CountersSatyam GuptaNoch keine Bewertungen

- Part A: Flip Flops: Sequential CircuitsDokument18 SeitenPart A: Flip Flops: Sequential CircuitssuriantoNoch keine Bewertungen

- Experiment 6: ObjectiveDokument9 SeitenExperiment 6: Objectivedjun033Noch keine Bewertungen

- Synchronous Counters: All About CircuitsDokument8 SeitenSynchronous Counters: All About CircuitsmonzuracNoch keine Bewertungen

- D Flip-FlopDokument35 SeitenD Flip-FlopSwati Kasht100% (1)

- Design of Sequential CircuitsDokument14 SeitenDesign of Sequential CircuitsRaj RoyNoch keine Bewertungen

- Introduction to Sequential DevicesDokument62 SeitenIntroduction to Sequential DevicesSarath Chandra SNoch keine Bewertungen

- Lec 13 - Chap 9 - CountersDokument28 SeitenLec 13 - Chap 9 - CountersAliRazaNoch keine Bewertungen

- Counters ElectronicsDokument5 SeitenCounters Electronicsmicah micahNoch keine Bewertungen

- Flip-Flop LabDokument7 SeitenFlip-Flop Labjose mirandaNoch keine Bewertungen

- Basic Flip Flop Circuits ExplainedDokument7 SeitenBasic Flip Flop Circuits ExplainedFord StephenNoch keine Bewertungen

- Sequential Circuits Problems (I) : Prof. Sin-Min Lee Department of Mathematics and Computer ScienceDokument35 SeitenSequential Circuits Problems (I) : Prof. Sin-Min Lee Department of Mathematics and Computer ScienceHal SmithNoch keine Bewertungen

- Digital Logic Design Chapter 6.... FullDokument36 SeitenDigital Logic Design Chapter 6.... FullOkezaki TemoyoNoch keine Bewertungen

- 3 Flip-Flops: 3.1 RS LatchesDokument28 Seiten3 Flip-Flops: 3.1 RS LatchesMiguel Valera MartinezNoch keine Bewertungen

- Counters and Applications of CountersDokument7 SeitenCounters and Applications of CountersJayant KirpekarNoch keine Bewertungen

- Product-of-Sums Simplification (POS)Dokument9 SeitenProduct-of-Sums Simplification (POS)aregaNoch keine Bewertungen

- Design of Counters Using Various Flip-FlopsDokument12 SeitenDesign of Counters Using Various Flip-FlopsSuresh Bharath100% (1)

- UntitledDokument8 SeitenUntitledlalita chauhanNoch keine Bewertungen

- Gated or Clocked SR Flip FlopDokument4 SeitenGated or Clocked SR Flip FlopSATYAM MAHAPATRANoch keine Bewertungen

- Edge-Triggered Flip-Flops and Their TypesDokument27 SeitenEdge-Triggered Flip-Flops and Their TypesUsama NaveedNoch keine Bewertungen

- Assignment 3 Attempt Any 5 Question and Submit It On BB Submission Is 15 Jan, 2022Dokument5 SeitenAssignment 3 Attempt Any 5 Question and Submit It On BB Submission Is 15 Jan, 2022EakanshNoch keine Bewertungen

- Experiment 5 Monsoon, 2008 Latches and Flip-Flops: Digital Logic & ProcessorDokument2 SeitenExperiment 5 Monsoon, 2008 Latches and Flip-Flops: Digital Logic & ProcessorUtkar ShNoch keine Bewertungen

- Learning Objectives:: Topic 2.2 - Sequential Systems. 2.2.2 - Binary CountersDokument62 SeitenLearning Objectives:: Topic 2.2 - Sequential Systems. 2.2.2 - Binary CountersSreekanth PagadapalliNoch keine Bewertungen

- Sequential Logic Circuits ExplainedDokument56 SeitenSequential Logic Circuits ExplainedBonsa100% (1)

- FSI - From Eastern To Western ArabicDokument54 SeitenFSI - From Eastern To Western ArabicSherweet A. AlsaadanyNoch keine Bewertungen

- Perfect Tense DeutschDokument2 SeitenPerfect Tense DeutschSherweet A. AlsaadanyNoch keine Bewertungen

- Develop An Activity DiagramDokument5 SeitenDevelop An Activity DiagramSherweet A. AlsaadanyNoch keine Bewertungen

- ECE366-5332 - Communication Networks - Quiz 1 - Group A - Spring 2017Dokument2 SeitenECE366-5332 - Communication Networks - Quiz 1 - Group A - Spring 2017Sherweet A. AlsaadanyNoch keine Bewertungen

- L04 - Intellectual Property RightsDokument7 SeitenL04 - Intellectual Property RightsSherweet A. AlsaadanyNoch keine Bewertungen

- SSDDokument6 SeitenSSDHarinniy IlanchezhianNoch keine Bewertungen

- ABCD Risk Management TeachingDokument16 SeitenABCD Risk Management TeachingSherweet A. AlsaadanyNoch keine Bewertungen

- Lecture 6 – part 1: Framing Techniques in Digital CommunicationDokument8 SeitenLecture 6 – part 1: Framing Techniques in Digital CommunicationSherweet A. AlsaadanyNoch keine Bewertungen

- Text Book and References for Communication NetworksDokument35 SeitenText Book and References for Communication NetworksToota TuttaNoch keine Bewertungen

- Data Communications ECE345: Prof. Dr. Samy El-Hennawey MSA UniversityDokument54 SeitenData Communications ECE345: Prof. Dr. Samy El-Hennawey MSA UniversitySherweet A. AlsaadanyNoch keine Bewertungen

- 8086 MicroprocessorDokument8 Seiten8086 MicroprocessordiNoch keine Bewertungen

- Diodes, Home Work Solutions: 3.1 Problem 3.11Dokument13 SeitenDiodes, Home Work Solutions: 3.1 Problem 3.11Sherweet A. AlsaadanyNoch keine Bewertungen

- 2b Submitted Emerging Markets Topic ReviewDokument16 Seiten2b Submitted Emerging Markets Topic ReviewSherweet A. AlsaadanyNoch keine Bewertungen

- Digital Logic Design 1 WorksheetDokument3 SeitenDigital Logic Design 1 WorksheetSherweet A. AlsaadanyNoch keine Bewertungen

- Electrical Measurement & InstrumentsDokument22 SeitenElectrical Measurement & InstrumentsSherweet A. AlsaadanyNoch keine Bewertungen

- Part IA Computing Course Tutorial Guide to C++ ProgrammingDokument74 SeitenPart IA Computing Course Tutorial Guide to C++ ProgrammingSherweet A. AlsaadanyNoch keine Bewertungen