Beruflich Dokumente

Kultur Dokumente

Fonseca 14.1

Hochgeladen von

Maximiliano2BaracOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Fonseca 14.1

Hochgeladen von

Maximiliano2BaracCopyright:

Verfügbare Formate

5

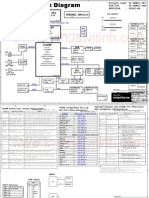

Fonseca 14.1" DIS Schematics Document

rPGA988A Mobile Arrandale

Intel Ibex Peak-M

C

2010-03-22

REV : -1

B

DY : Nopop Component

B_TPM:Use Lom TPM

C_TPM:Use China TPM

A

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Date:

5

Monday, March 22, 2010

Cover Page

Rev

-1

Fonseca 14.1" DIS

Sheet

1

of

89

Fonseca 14" DIS Block Diagram

D

Clock Generator

SLG8SP585VTR

Thermal & Fan

EMC4022

DDR III DIMM1

1333Mhz

18

DDR III DIMM2

1333Mhz

19

39

ATI M92LP-S2

PEG

Intel Mobile CPU

Channel A

gDDR3

800MHz

INPUTS

80,81,82,83

OUTPUTS

eDP

rPGA988A 8~14

+PWR_SRC

46

TPS51125

MAX4885EETG+

14.1" eDP-LCD

+VCC_CORE

SYSTEM DC/DC

CRT

VSW

INPUTS

CRT CONN

75

OUTPUTS

+3.3V_ALW

55

+PWR_SRC

DMIx4

+5V_ALW

BL Converter

BTO(1)

54

Smart CARD

Socket

O2

OZ77CR6

67

BTO(2)

SYSTEM DC/DC

Display Port (C)

USB2.0

34

47

ISL62883

VRAM

64Mx16bx4 (512MB)

84,85

4

Arrandale

Channel B

Project name: DF3-14D

Project code: 91.4GQ01.001

PCB P/N

: 48.4GQ01.011

Revision

: 09281 - 1

CPU DC/DC

X1

Intel PCH

50

TPS51116

Display Port (B)

INPUTS

OUTPUTS

USB2.0

PC CARD

Socket

Ibex Peak-M

72

Ricoh

1394 Connector

PCIE

12 USB 2.0/1.1 ports

BTO(3)

Power SW(NewCard)

New Card

Connector

72

INT2

HDD CONN

LPC I/F

75

+1.8V_RUN

OP AMP

2CH

SPEAKER

(1W/1W)

SPI

Bluetooth (Option)

SYSTEM LDO

Module

RT9035

73

51

INPUTS

OUTPUTS

+3.3V_SUS

Camera (Option)

+1.8V_DELAY

60

Module

SPI FLASH

32Mb + 16Mb

USB2.0

63

MDC (Option)

Module

IO Board

62

76

73

LPC

FLASH

8Mb

36

76

IO Board

76

RJ45

76

IO Board

ESW

LPC

IO Board

BCM5761E

86

TPS51511

USB Port x 2

X2

LOM

35

SYSTEM DC/DC

RJ11

X2

TCM (Option)

ZTE, Jetway

INPUTS

OUTPUTS

+PWR_SRC

+VCC_GFX_CORE

1/2 Mini-Card

BATTERY CHARGER

WLAN Module

35

(AC, Battery Existence)

64

INPUTS

Int KB

BC

TouchPad

KSI/KSO

ECE1077

EC

PS2

MEC 5045

37

IO Board

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

38

Finger Printer

Title

AES2880 (Option)

78

Size

Document Number

Custom

Date:

+PBATT

<Core Design>

76

ECE 5028

FP Board

OUTPUTS

+DC_IN_SS

WWAN Module

SIO Expander

BC

68

45

TI BQ24745

64

Mini-Card

A

59

USB Port x 2

WLAN Switch

+3.3V_SUS

74

59

LPC

OUTPUTS

HP Jack

30

ODD CONN

INPUTS

INT1

20~28

51

RT9035

MIC Jack

IDT

92HD81

SMBus

SATA

+1.05V_VTT

SYSTEM LDO

HD AUDIO

PCI/PCI BRIDGE

SATA

OUTPUTS

TLV320AIC3004

Azalia

CODEC

ACPI 1.1

72

Free Fall Sensor

40

DE351DL

52

INPUTS

+PWR_SRC

4 SATA ports

PCIE

SATA

E/Family

73

Module

6 PCIE ports

USB2.0

TPS2231MRGPR

SYSTEM DC/DC

Docking

High Definition Audio

32

X2

Digital MIC

10/100/1000Mb ETHERNET

SD/SDHC/MMC

Socket

71

+0.75V_DDR_VTT

TPS51218

R5U242

71

+1.5V_SUS

+PWR_SRC

USB2.0

SATA

PCIE

Block Diagram

Thursday, March 18, 2010

Rev

Fonseca 14.1" DIS

Sheet

1

-1

of

89

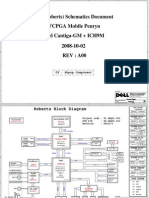

Regulator

ADAPTER

LDO

ISL62883

47

+VCC_CORE47

Switch

BATTERY

+PWR_SRC

+3V_ALW_246

TPS51218

TPS51116

TPS51511 86

52

50

TPS51125

CHARGER

BQ24745

+5V_ALW_246

46

+1.05V_VTT

+GPU_CORE +1.1V_GFX_PCIE

52

86

+1.5V_SUS

86

+0.75V_DDR_VTT

50

50

SIR460DP

42

+5V_ALW

+3.3V_ALW

46

+1.5V_RUN

42

46

SI4800BDY

42

SI4800BDY

42

SI4800BDY

42

+15V_ALW

SI3456DDV

35

SI2301CDS

42

SI3456DDV

42

SI4800BDY

42

46

+3.3V_SUS

42

+3.3V_DELAY

42

+5V_MOD

42

+5V_RUN

+3.3V_RUN

42

42

+3.3V_LAN

35

RT9035

51

+1.5V_RUN_CPU

42

RT9035

51

SI3456DDV

42

+CAMERA_VDD73

+1.8V_RUN

51

NJT4030PT1G

35

+1.8V_DEALY

51

<Core Design>

Wistron Corporation

+1.2V_LOM 35

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

+3.3V_ALW_PCH 42

Title

Power Diagram

Size

Document Number

Custom

Date:

5

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

Sheet

1

of

89

2.2K

2.2K

PCH_SMB_CLK

PCH_SMB_DATA

+3.3V_RUN

2.2K

2N7002

2N7002

202

200

202

200

PCH

ibex Peak-M

2.2K

C6

G8

G12

2.2K

+3.3V_ALW_PCH

H14

C8

PCH_SML0CLK

PCH_SML0DATA

+3.3V_ALW_PCH

DIMM A(DM1) SMB

Addr=[A0]

DIMM B(DM2) SMB

Addr=[A4]

D

53

51

XDP1

53

51

XDP2

Dummy

2.2K

E10

Dummy

2.2K

KBC_SCL1

KBC_SDA1

A5

+3.3V_ALW_PCH

14

13

2.2K

FFSensor

DE351DL

SMB Addr=[3A]

2.2K

B6

+3.3V_LAN

A50

B53

LAN_SMBCLK

LAN_SMBDAT

2.2K

2N7002

2N7002

LOM

A3

A4

BCM5761E

SMB Addr=[XX]

EC

Dummy

Dummy

MEC5045

2.2K

2.2K

+3.3V_ALW

A7

B7

2.2K

+3.3V_RUN

2.2K

2N7002

2N7002

CKG_SMBCLK

CKG_SMBDAT

2.2K

B4

A3

SMB Addr=[D2]

+3.3V_ALW

2.2K

DOCK_SMB_ALERT#

133

DOCK_SMB_CLK

DOCK_SMB_DAT

127

129

2.2K

Docking

SMB Addr=[C4/72/70/48]

2.2K

+3.3V_ALW

B5

A4

SLG8SP585VTR

10K

+3.3V_ALW

A2

CLK Gen

32

31

2.2K

+LCDVDD

2.2K

2N7002

2N7002

LCD_SMBCLK

LCD_SMBDAT

13

12

LCD Panel

(eDP Type)

SMB Addr=[XX]

2.2K

+3.3V_ALW

A56

B59

100 ohm

2.2K

PBAT_SMBCLK

PBAT_SMBDAT

3

4

100 ohm

2.2K

Battery

connector

SMB Addr=[XX]

+3.3V_ALW

B50

A47

2.2K

CHARGER_SMBCLK

CHARGER_SMBDAT

10

9

2.2K

2.2K

+3.3V_RUN

2N7002

2N7002

AUD_DOCK_SMBCLK

AUD_DOCK_SMBDAT

SMB Addr=[12]

2.2K

+3.3V_ALW

B49

B48

Charger

BQ24745RHDR

2.2K

8

9

ADC/DAC

TLV320AIC3004

SMB Addr=[30]

A

2.2K

+3.3V_ALW

A49

B52

2.2K

CARD_SMBCLK

CARD_SMBDAT

20

19

ExpressCard

<Core Design>

connector

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A2

Date:

SMBus Diagram

Document Number

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

Sheet

1

of

89

Audio Block Diagram

Thermal Block Diagram

D

AUD_EXT_MIC_L

HP0_PORT_A_L

AUD_EXT_MIC_R

MIC

HP0_PORT_A_R

AUD_VREFOUT_B

60

VREFOUT_A_OR_F

HP1_PORT_B_L

HP1_PORT_B_R

Earphone

AUD_HP_OUT_L

AUD_HP_OUT_R

60

DP1

MMBT3904-3-GP

SC470P50V3JN-2GP

DN1

CPU

PORT_C_L

PORT_C_R

DP2

VREFOUT_C

MMBT3904-3-GP

SC470P50V3JN-2GP

Thermal

EMC4022

DN2

Skin

Anti-Parallel Diodes

Codec

92HD81

DP3

MMBT3904-3-GP

SC470P50V3JN-2GP

DN3

VGA

SPKR_PORT_D_L+

AUD_SPK_L+

AUD_SPK_L+_R

SPKR_PORT_D_L-

AUD_SPK_L-

AUD_SPK_L-_R

SPKR_PORT_D_R-

AUD_SPK_R+

AUD_SPK_R+_R

SPKR_PORT_D_R+

AUD_SPK_R-

SPEAKER

DP4

MMBT3904-3-GP

SC470P50V3JN-2GP

DN4

60

AUD_SPK_R-_R

DIMM

Anti-Parallel Diodes

0R3-0-U-V-GP

DP5

PORT_E_L

AUD_DOCK_HP_OUT_L_C

PORT_E_R

AUD_DOCK_HP_OUT_R_C

PORT_F_L

AUD_DOCK_MIC_IN_L

PORT_F_R

AUD_DOCK_MIC_IN_R

75

DN5

SCD47U25V3KX-1GP

THERMTRIP1#

CPU_ThermalTrip

THERMTRIP2#

DOCKING

TLV320AIC3004

DAI_BCLK#

DOCK

HP

DAI_LRCK#

DAI_DO#

DAI_DI

DOCK

MIC

DMIC_CLK/GPIO1

DMIC0/GPIO2

0R2J-2-GP

AUD_DMIC_CLK

Digital

50

MIC

AUD_DMIC_CLK_G_C

AUD_DMIC_IN0

AUD_DMIC_IN0_C

33R2J-2-GP

74

SC1U16V3KX-2GP

PCH_ThermalTrip

THERMTRIP3#

+3.3V_SUS

<Core Design>

SC1U10V3KX-3GP

39

30

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

AUDIO/THERMAL Diagram

Document Number

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

Sheet

1

of

89

PCH Strapping

SPKR

Calpella Schematic Checklist Rev: 1.6

Reboot option at power-up

Default Mode: Internal weak Pull-down.

No Reboot Mode with TCO Disabled: Connect to Vcc3_3 with 8.2-k ~ 10-k weak

pull-up resistor.

Processor Strapping

Calpella Schematic Checklist Rev: 1.6

Schematics Notes

Name

INIT3_3V#

Internal pull-up. Leave as "No Connect"

GNT3#/

GPIO55

Default Mode: Internal pull-up.

Low (0) = Top Block Swap Mode

Note: Connect to ground with 4.7-k weak pull-down resistor.

CRB uses a 1 k ; do not stuff resistor

INTVRMEN

High (1) = Integrated VRM is enabled

Low (0) = Integrated VRM is disabled

Note: CRB uses a 330-k resistor.

GNT0#,

GNT1#

Default (SPI): Leave both GNT0# and GNT1# floating. No pull up required

Pin Name

Strap Description

Configuration (Default value for each bit is

1 unless specified otherwise)

Default

Value

CFG[4]

Embedded

DisplayPort

Presence

1: Disabled - No Physical Display Port attached to

Embedded DisplayPort.

0: Enabled - An external Display Port device is

connected to the Embedded Display Port.

1: Normal Operation.

0: Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

CFG[3]

PCI-Express Static

Lane Reversal

CFG[0]

PCI-Express

1: Single PCI-Express Graphics

Configuration Select 0: Bifurcation enabled

1

1

Boot from PCI: Connect GNT1# to ground with 1-k pull-down resistor.

Leave GNT0# Floating.

Boot from LPC: Connect both GNT0# and GNT1# to ground with 1-k pull-down

resistor.

Default - Internal pull-up.

Low (0)= Configures DMI for ESI compatible operation (for servers only.

Not for mobile/desktops).

GNT2#/

GPIO53

C

SPI_MOSI

Enable Intel Anti-Theft Technology: Connect to Vcc3_3 with 8.2-k weak pull-up

resistor.

Disable Intel Anti-Theft Technology:Left floating, no pull-down required.

NV_ALE

Enable Intel Anti-Theft Technology: Connect to +NVRAM_VCCQ with 8.2-k weak

pull-up resistor [CRB has it pulled up with 1-k no-stuff resistor]

Disable Intel Anti-Theft Technology: Leave floating (internal pull-down).

NV_CLE

DMI termination voltage. Weak internal pull-up. Do not pull low.

HDA_DOCK_EN#

/GPIO[33]

Low (0):

Flash Descriptor Security will be overridden.

Also, when this signals is sampled on the rising edge of PWROK then

it will also disable Intel ME and its features.

High (1): Security measure defined in the Flash Descriptor will be enabled.

Platform design should provide appropriate pull-up or pull-down

depending on the desired settings.

If a jumper option is used to tie this signal to GND as required by

the functional strap, the signal should be pulled low through a weak pull-down

in order to avoid asserting HDA_DOCK_EN# inadvertently.

Note:

CRB recommends 1-k pull-down for FD Override.

There is an internal pull-up of 20 k for HDA_DOCK_EN# which is only

enabled at boot/reset for strapping functions.

HDA_SDO

Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

HDA_SYNC

Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

PCIE Routing

LANE1

LANE2

LANE3

LANE4

- Intel ME Crypto Transport Layer Security TLS) cipher suite with no

confidentiality.

High (1) - Intel ME Crypto Transport Layer Security (TLS) cipher suite with

confidentiality.

Note:

This is an unmuxed signal.

This signal has a weak internal pull-down of 20K which is enabled when PWROK is

low.

Sampled at rising edge of RSMRST#.

CRB has a 1K pull-up on this signal to +3.3VA rail.

USB Routing

USB

WWAN

Pair

WLAN

PCMCIA

Express Card

Low (1)

GPIO15

GPIO8

Weak internal pull-up. Do not pull low. Sampled at rising edge of RSMRST#.

GPIO27

Default = Do not connect (floating). Internal pull-up.

High(1) = Enables the internal VccVRM to have a clean supply for analog rails.

No need to use on-board filter circuit.

Low (0) = Disables the VccVRM.

Need to use on-board filter circuits for analog rails.

LANE5

None

LANE6

10M/100M/1G LAN

LANE7

Not available for HM55

LANE8

Not available for HM55

Device

USB0 @ MB

USB1 @ MB

USB2 @ IO Board

USB3 @ IO Board

WLAN

Bluetooth

Not available for HM55

Not available for HM55

DOCKING PORT1

DOCKING PORT2

10

Finger Printer

11

Camera

12

PCCard/ SmartCard/ ExpCard

13

WWAN

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

Table of Content

Document Number

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

Sheet

1

of

89

SSID = CLOCK

+3.3V_RUN

+3.3V_RUN

2

1

37 CKG_SMBDAT

+3.3V_RUN

+3.3V_RUN_CLKGEN

C709

37 CKG_SMBCLK

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3

4

C708

C707

C706

C705

SCD1U16V2ZY-2GP

C704

DY

2

DY

SC1U10V2KX-1GP

DY

C703

SC10U10V5ZY-1GP

C702

RN702

SRN2K2J-1-GP

Q701

1 L702

2

0R0805-PAD-2-GP

DMN66D0LDW -7-GP

CLK_SDATA

R709

R710

+3.3V_RUN_CLKGEN

DY

DY

CLK_SCLK_HDDFALL

0R2J-2-GP

40

CLK_SDATA_HDDFALL

0R2J-2-GP

40

C712

+1.05V_RUN_CLKGEN_IO

C713

SRC_2#

SRC_2

11

10

SRC_1/SATA#

SRC_1/SATA

18

2

1

15

VDD_CPU_IO

29

17

VDD_SRC_IO

VDD_27

CLK_GPU27M_SS 81

CLK_GPU27M_NSS

CLK_GPU_27M_SS

CPU_STOP#

CKPWRGD/PD#

REF_0/CPU_SEL

16

25

30

CPU_STOP#

CK_PW RGD

FSC

CLK_XTAL_IN

CLK_XTAL_OUT

EC702

SC10P50V2JN-4GP

CLK_SDATA

CLK_SCLK

2

R704

1

10KR2J-3-GP

R705

CLK_PCH_14M 23

33R2J-2-GP

SDA

SCL

31

32

C714

SC4D7P50V2CN-1GP

For EMI

VSS_27

8

26

33

DY

VSS_SATA

CPU_1#

CPU_1

VSS_DOT

XTAL_IN

XTAL_OUT

19

20

VSS_SRC

CPU_0#

CPU_0

28

27

GND

22

23

12

CLK_CPU_BCLK#

CLK_CPU_BCLK

23 CLK_CPU_BCLK#

23 CLK_CPU_BCLK

EC703

SC10P50V2JN-4GP

+3.3V_RUN

VSS_CPU

CLK_PCIE_SATA#

CLK_PCIE_SATA

23 CLK_PCIE_SATA#

23 CLK_PCIE_SATA

27MHZ

SLG8SP585VTR-GP 27MHZ_SS

6

7

2

33R2J-2-GP

14

13

CLK_GPU27M_NSS 81

DOT_96#

DOT_96

CLKIN_DMI#

CLKIN_DMI

1

R703

4

3

21

23 CLKIN_DMI#

23 CLKIN_DMI

DREFCLK#

DREFCLK

VSS_REF

23 DREFCLK#

23 DREFCLK

VDD_DOT

-1.10/0310

VDD_REF

24

VDD_CPU

U701

VDD_SRC

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

Damping need to check

series resistance

-1.10/0310

DY

SC10U10V5ZY-1GP

C711

C710

SC1U10V2KX-1GP

1 L701

2

0R0805-PAD-2-GP

+1.05V_RUN_CLKGEN_IO

+1.05V_VTT

DY

CLK_SCLK

+3.3V_RUN_CLKGEN

Main Source: 71.08585.003 (SLG8SP585VTR)

2nd Source: 71.93197.003 (ICS9LRS3197AKLFT)

3rd Source: 71.00875.D03 (RTM875N-632-VB-GRT)

R706

10KR2J-3-GP

CK_PW RGD

Q702

2N7002A-7-GP

+1.05V_VTT

VR_CLKEN# 47

R701

DY 4K7R2J-2-GP

FSC

X701

CLK_XTAL_IN

R707

10KR2J-3-GP

FSC

SPEED

133MHz

(Default)

<Core Design>

CLK_XTAL_OUT

X-14D31818M-37GP

C715

SC15P50V2JN-2-GP

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

C701

SC15P50V2JN-2-GP

Title

100MHz

Size

A3

Date:

Clock Generator - SLG8SP585

Document Number

Sheet

1

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

of

89

SSID = CPU

22

22

22

22

DMI_PTX_CRXP0

DMI_PTX_CRXP1

DMI_PTX_CRXP2

DMI_PTX_CRXP3

B24

D23

B23

A22

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

22

22

22

22

DMI_CTX_PRXN0

DMI_CTX_PRXN1

DMI_CTX_PRXN2

DMI_CTX_PRXN3

D24

G24

F23

H23

DMI_TX0#

DMI_TX1#

DMI_TX2#

DMI_TX3#

22

22

22

22

DMI_CTX_PRXP0

DMI_CTX_PRXP1

DMI_CTX_PRXP2

DMI_CTX_PRXP3

D25

F24

E23

G23

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

4

3

RN801

SRN1KJ-7-GP

1

2

FDI_TX0#

FDI_TX1#

FDI_TX2#

FDI_TX3#

FDI_TX4#

FDI_TX5#

FDI_TX6#

FDI_TX7#

D22

C21

D20

C18

G22

E20

F20

G19

FDI_TX0

FDI_TX1

FDI_TX2

FDI_TX3

FDI_TX4

FDI_TX5

FDI_TX6

FDI_TX7

F17

E17

FDI_FSYNC0

FDI_FSYNC1

C17

FDI_INT

F18

D17

FDI_LSYNC0

FDI_LSYNC1

R801

PEG_IRCOMP_R

EXP_RBIAS

2 49D9R2F-GP

B26

A26

B27

A25

PEG_RX0#

PEG_RX1#

PEG_RX2#

PEG_RX3#

PEG_RX4#

PEG_RX5#

PEG_RX6#

PEG_RX7#

PEG_RX8#

PEG_RX9#

PEG_RX10#

PEG_RX11#

PEG_RX12#

PEG_RX13#

PEG_RX14#

PEG_RX15#

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

PEG_CRX_GTX_N15

PEG_CRX_GTX_N14

PEG_CRX_GTX_N13

PEG_CRX_GTX_N12

PEG_CRX_GTX_N11

PEG_CRX_GTX_N10

PEG_CRX_GTX_N9

PEG_CRX_GTX_N8

PEG_CRX_GTX_N7

PEG_CRX_GTX_N6

PEG_CRX_GTX_N5

PEG_CRX_GTX_N4

PEG_CRX_GTX_N3

PEG_CRX_GTX_N2

PEG_CRX_GTX_N1

PEG_CRX_GTX_N0

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

PEG_CRX_GTX_P15

PEG_CRX_GTX_P14

PEG_CRX_GTX_P13

PEG_CRX_GTX_P12

PEG_CRX_GTX_P11

PEG_CRX_GTX_P10

PEG_CRX_GTX_P9

PEG_CRX_GTX_P8

PEG_CRX_GTX_P7

PEG_CRX_GTX_P6

PEG_CRX_GTX_P5

PEG_CRX_GTX_P4

PEG_CRX_GTX_P3

PEG_CRX_GTX_P2

PEG_CRX_GTX_P1

PEG_CRX_GTX_P0

PEG_TX0#

PEG_TX1#

PEG_TX2#

PEG_TX3#

PEG_TX4#

PEG_TX5#

PEG_TX6#

PEG_TX7#

PEG_TX8#

PEG_TX9#

PEG_TX10#

PEG_TX11#

PEG_TX12#

PEG_TX13#

PEG_TX14#

PEG_TX15#

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

PEG_CTX_GRX_C_N15

PEG_CTX_GRX_C_N14

PEG_CTX_GRX_C_N13

PEG_CTX_GRX_C_N12

PEG_CTX_GRX_C_N11

PEG_CTX_GRX_C_N10

PEG_CTX_GRX_C_N9

PEG_CTX_GRX_C_N8

PEG_CTX_GRX_C_N7

PEG_CTX_GRX_C_N6

PEG_CTX_GRX_C_N5

PEG_CTX_GRX_C_N4

PEG_CTX_GRX_C_N3

PEG_CTX_GRX_C_N2

PEG_CTX_GRX_C_N1

PEG_CTX_GRX_C_N0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

C817

C816

C815

C814

C813

C812

C811

C810

C809

C808

C807

C806

C805

C804

C803

C802

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

PEG_CTX_GRX_N15

PEG_CTX_GRX_N14

PEG_CTX_GRX_N13

PEG_CTX_GRX_N12

PEG_CTX_GRX_N11

PEG_CTX_GRX_N10

PEG_CTX_GRX_N9

PEG_CTX_GRX_N8

PEG_CTX_GRX_N7

PEG_CTX_GRX_N6

PEG_CTX_GRX_N5

PEG_CTX_GRX_N4

PEG_CTX_GRX_N3

PEG_CTX_GRX_N2

PEG_CTX_GRX_N1

PEG_CTX_GRX_N0

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_CTX_GRX_C_P15

PEG_CTX_GRX_C_P14

PEG_CTX_GRX_C_P13

PEG_CTX_GRX_C_P12

PEG_CTX_GRX_C_P11

PEG_CTX_GRX_C_P10

PEG_CTX_GRX_C_P9

PEG_CTX_GRX_C_P8

PEG_CTX_GRX_C_P7

PEG_CTX_GRX_C_P6

PEG_CTX_GRX_C_P5

PEG_CTX_GRX_C_P4

PEG_CTX_GRX_C_P3

PEG_CTX_GRX_C_P2

PEG_CTX_GRX_C_P1

PEG_CTX_GRX_C_P0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

C828

C823

C871

C832

C827

C822

C831

C826

C821

C830

C825

C820

C829

C824

C819

C818

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

PEG_CTX_GRX_P15

PEG_CTX_GRX_P14

PEG_CTX_GRX_P13

PEG_CTX_GRX_P12

PEG_CTX_GRX_P11

PEG_CTX_GRX_P10

PEG_CTX_GRX_P9

PEG_CTX_GRX_P8

PEG_CTX_GRX_P7

PEG_CTX_GRX_P6

PEG_CTX_GRX_P5

PEG_CTX_GRX_P4

PEG_CTX_GRX_P3

PEG_CTX_GRX_P2

PEG_CTX_GRX_P1

PEG_CTX_GRX_P0

<Core Design>

Intel(R) FDI

FDI_INT

E22

D21

D19

D18

G21

E19

F21

G18

PCI EXPRESS -- GRAPHICS

DMI_RX0#

DMI_RX1#

DMI_RX2#

DMI_RX3#

AUBURNDALE

A24

C23

B22

A21

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

DMI

DMI_PTX_CRXN0

DMI_PTX_CRXN1

DMI_PTX_CRXN2

DMI_PTX_CRXN3

1 OF 9

CPU1A

22

22

22

22

R802

2 750R2F-GP

PEG_CTX_GRX_P[0..15]

PEG_CTX_GRX_N[0..15]

PEG_CTX_GRX_P[0..15] 80

PEG_CTX_GRX_N[0..15] 80

PEG_CRX_GTX_N[0..15]

PEG_CRX_GTX_N[0..15] 80

PEG_CRX_GTX_P[0..15]

PEG_CRX_GTX_P[0..15] 80

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU - PCIE/DMI/FDI (1/7)

Size

A3

Document Number

Date:

Friday, March 19, 2010

Sheet

Rev

-1

Fonseca 14.1" DIS

of

89

SSID = CPU

Processor Compensation Signals

COMP1

H_COMP0

AT26

COMP0

49D9R2F-GP

49D9R2F-GP

H_CPURST#

68R2-GP

H_SKTOCC#

37 H_SKTOCC#

AH24

H_CATERR#

PECI

25 H_PECI

R912

8K2R2J-3-GP

1 2

DY

R913

2K2R2J-2-GP

H_PROCHOT#

47 H_PROCHOT#

Q901

AN26

H_THERMTRIP#

25,39 H_THERMTRIP#

AK15

PROCHOT#

THERMTRIP#

3 DY 2 H_CATERR#

MMBT3904-7-F-GP

PEG_CLK

PEG_CLK#

E16

D16

PEG_CLK_R

PEG_CLK#_R

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

A18

A17

38 CPU_CATERR#

BCLK_ITP_P_R

BCLK_ITP_N_R

H_CPURST#

58 H_CPURST#

AP26

AL15

22 H_PM_SYNC

-1.10/0318

PM_SYNC

VCCPW RGOOD

AN14

VCCPWRGOOD_1

VCCPW RGOOD_0

AN27

VCCPWRGOOD_0

22 DRAM_PW ROK

DRAM_PW ROK

AK13

SM_DRAMPWROK

52 H_VTTPW RGD

H_VTTPW RGD

AM15

VTTPWRGOOD

H_PW RGD_XDP

AM26

TAPPWRGOOD

PLT_RST#_R

AL14

RSTIN#

25,58 H_PW RGD

1 R917

2

0R0402-PAD-2-GP

RESET_OBS#

1 R919

2

0R0402-PAD-2-GP

58 H_PW RGD_XDP

RN903

4

3

DY

BCLK_ITP_P 58

BCLK_ITP_N 58

SRN0J-6-GP

PEG_CLK_R 23

PEG_CLK#_R 23

DDR_HVREF_RST_GATE

Q902

F6

SM_DRAMRST#

AL1

AM1

AN1

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

PM_EXT_TS0#

PM_EXT_TS1#

AN15

AP15

PM_EXTTS#_R

PRDY#

PREQ#

AT28

AP27

XDP_PRDY#

XDP_PREQ#

TCK

TMS

TRST#

AN28

AP28

AT27

XDP_TCLK

XDP_TMS

XDP_TRST#

TDI

TDO

TDI_M

TDO_M

AT29

AR27

AR29

AP29

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

DBR#

AN25

H_DBR#_R

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

BPM6#

BPM7#

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

+1.05V_VTT

R914

R918

1

R934

D

2N7002A-7-GP

+1.5V_SUS

2

1KR2J-1-GP

DDR3_DRAMRST#

18,19

R915

DY

1

10KR2J-3-GP

37

C903

SCD047U10V2KX-2GP

1 DY

R936

0R2J-2-GP

C902

SC470P50V2JN-GP

XDP_PRDY# 58

XDP_PREQ# 58

XDP_TCLK 58

XDP_TMS 58

XDP_TRST# 58

DDR3 Compensation Signals

SM_RCOMP_0

1

R909

SM_RCOMP_1

1

R910

SM_RCOMP_2

1

R911

XDP_DBRESET#

0R0402-PAD-2-GP

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

2

2

2

100R2F-L1-GP-U

24D9R2F-L-GP

130R2F-1-GP

XDP_DBRESET# 22,38,58

58

58

58

58

58

58

58

58

+1.05V_VTT

XDP_TMS

R922

1

R921

1K5R2F-2-GP

21,58,80 PLTRST1#

JTAG & BPM

C901

SCD1U10V2KX-4GP

PWR MANAGEMENT

Place near U3801

DY

BCLK_CPU_P_R 25

BCLK_CPU_N_R 25

1

2

CATERR#

+1.05V_VTT

AT15

BCLK_ITP

BCLK_ITP#

AR30

AT30

THERMAL

+3.3V_RUN

AK14

SKTOCC#

BCLK_CPU_P_R

BCLK_CPU_N_R

R907

G16

A16

B16

DY

R905

H_PROCHOT#

49D9R2F-GP

H_COMP1

COMP2

49D9R2F-GP

AT24

BCLK

BCLK#

R908

H_COMP2

20R2F-GP

OF 9

COMP3

100KR2J-1-GP

2

1

DY

H_CATERR#

AT23

CLOCKS

R906

H_COMP3

20R2F-GP

DDR3

MISC

R903

MISC

R904

AUBURNDALE

R902

Processor Pullups

CPU1B

+1.05V_VTT

XDP_TDI_R

R924

750R2F-GP

R923

XDP_PREQ#

R925

XDP_TCLK

R926

DY

DY

DY

DY

51R2J-2-GP

51R2J-2-GP

51R2J-2-GP

51R2J-2-GP

JTAG MAPPING

XDP_TDI_R

R929

XDP_TDO_M

1

R930

DY

XDP_TDI

XDP_TDI

0R0402-PAD-2-GP

XDP_TDO

0R2J-2-GP

58

XDP_TDO 58

+3.3V_ALW _PCH

R941

DY 0R2J-2-GP

U901

SIO_SLP_S3#_C

0R0402-PAD-2-GP

RUNPW ROK_C

0R0402-PAD-2-GP

GND

VCC

Y

R932

0R2J-2-GP

0R0402-PAD-2-GP

XDP_TRST#

5

4

DRAM_PW ROK_R

74LVC1G08GW -1-GP

1

2

R937

1K5R2F-2-GP

DRAM_PW ROK

R939

750R2F-GP

Scan Chain

(Default)

CPU Only

GMCH Only

DY

Stuff --> R901, R929, R932

No Stuff --> R930, R931

R933

51R2J-2-GP

Stuff --> R929, R930

No Stuff --> R901, R931, R932

Stuff --> R931, R932

No Stuff --> R929, R930, R901

1

R927

1

R920

37,38,58 RUNPW ROK

1

R931

XDP_TDO_R

22,35,38,50 SIO_SLP_S3#

XDP_TDI_M

+3.3V_ALW _PCH

R901

0R0402-PAD-2-GP

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU Thermal/Clock/PM (2/7)

Size

A3

Document Number

Date:

Friday, March 19, 2010

Rev

-1

Fonseca 14.1" DIS

Sheet

of

89

SSID = CPU

18 M_A_BS0

18 M_A_BS1

18 M_A_BS2

AC3

AB2

U7

18 M_A_CAS#

18 M_A_RAS#

18 M_A_W E#

AE1

AB3

AE9

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

SA_CK0

SA_CK0#

SA_CKE0

19 M_B_DQ[63..0]

AA6

AA7

P7

M_CLK_DDR0 18

M_CLK_DDR#0 18

M_CKE0 18

SA_CK1

SA_CK1#

SA_CKE1

Y6

Y5

P6

M_CLK_DDR1 18

M_CLK_DDR#1 18

M_CKE1 18

SA_CS0#

SA_CS1#

AE2

AE8

M_CS#0 18

M_CS#1 18

SA_ODT0

SA_ODT1

AD8

AF9

M_ODT0 18

M_ODT1 18

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

B9

D7

H7

M7

AG6

AM7

AN10

AN13

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DM[7..0] 18

M_A_DQS#[7..0] 18

M_A_DQS[7..0] 18

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

C9

F8

J9

N9

AH7

AK9

AP11

AT13

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

C8

F9

H9

M9

AH8

AK10

AN11

AR13

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A[15..0] 18

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

M1

K5

K4

M4

N5

AF3

AG1

AJ3

AK1

AG4

AG3

AJ4

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

AUBURNDALE

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

OF 9

OF 9

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

19 M_B_BS0

19 M_B_BS1

19 M_B_BS2

AB1

W5

R7

SB_BS0

SB_BS1

SB_BS2

19 M_B_CAS#

19 M_B_RAS#

19 M_B_W E#

AC5

Y7

AC6

SB_CAS#

SB_RAS#

SB_WE#

SB_CK0

SB_CK0#

SB_CKE0

W8

W9

M3

M_CLK_DDR2 19

M_CLK_DDR#2 19

M_CKE2 19

SB_CK1

SB_CK1#

SB_CKE1

V7

V6

M2

M_CLK_DDR3 19

M_CLK_DDR#3 19

M_CKE3 19

SB_CS0#

SB_CS1#

AB8

AD6

M_CS#2 19

M_CS#3 19

SB_ODT0

SB_ODT1

AC7

AD1

M_ODT2 19

M_ODT3 19

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

D4

E1

H3

K1

AH1

AL2

AR4

AT8

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

D5

F4

J4

L4

AH2

AL4

AR5

AR8

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

C5

E3

H4

M5

AG2

AL5

AP5

AR7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DM[7..0] 19

M_B_DQS#[7..0] 19

M_B_DQS[7..0] 19

DDR SYSTEM MEMORY - B

A10

C10

C7

A7

B10

D10

E10

A8

D8

F10

E6

F7

E9

B7

E7

C6

H10

G8

K7

J8

G7

G10

J7

J10

L7

M6

M8

L9

L6

K8

N8

P9

AH5

AF5

AK6

AK7

AF6

AG5

AJ7

AJ6

AJ10

AJ9

AL10

AK12

AK8

AL7

AK11

AL8

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AUBURNDALE

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DDR SYSTEM MEMORY A

18 M_A_DQ[63..0]

CPU1D

3

CPU1C

M_B_A[15..0] 19

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU - DDR (3/7)

Size

A3

Document Number

Date:

Friday, March 19, 2010

Rev

-1

Fonseca 14.1" DIS

Sheet

1

10

of

89

SSID = CPU

CPU1E

TP1116

TP1117

1

1

SA_DIMM_VREF#

SB_DIMM_VREF#

CFG0

PCI-Express Configuration Select

TP1101

TP1102

1

1

TP1103

TP1104

1

1

TP1105

TP1106

TP1107

TP1108

TP1109

TP1110

TP1111

TP1112

TP1113

TP1114

1

1

1

1

1

1

1

1

1

1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

H16

RSVD#AP25

RSVD#AL25

RSVD#AL24

RSVD#AL22

RSVD#AJ33

RSVD#AG9

RSVD#M27

RSVD#L28

SA_DIMM_VREF#

SB_DIMM_VREF#

RSVD#G25

RSVD#G17

RSVD#E31

RSVD#E30

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

RSVD_TP#H16

AUBURNDALE

AP25

AL25

AL24

AL22

AJ33

AG9

M27

L28

J17

H17

G25

G17

E31

E30

RSVD#AL26

RSVD_NCTF#AR2

RSVD#AJ26

RSVD#AJ27

RSVD#AL28

RSVD#AL29

RSVD#AP30

RSVD#AP32

RSVD#AL27

RSVD#AT31

RSVD#AT32

RSVD#AP33

RSVD#AR33

RSVD#AR32

RSVD_TP#E15

RSVD_TP#F15

KEY

RSVD#D15

RSVD#C15

RSVD#AJ15

RSVD#AH15

R1102

CFG0

DY 3K01R2F-3-GP

1:Single PEG

0:Bifurcation enabled

B19

A19

For Clarksfield

A20

B20

CFG3

CFG3 - PCI-Express Static Lane Reversal

R1105

3K3R2J-3-GP

U9

T9

CFG3

AC9

AB9

1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

J29

J28

R1109

CFG4

DY 3K01R2F-3-GP

AJ13

AJ12

H_RSVD32

H_RSVD33

1

1

TP1118

TP1119

AH25

AK26

H_RSVD35

TP1120

H_RSVD36

TP1121

AL26

AR2

AJ26

AJ27

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AR32

E15

F15

A2

D15

C15

AJ15

AH15

RSVD#B19

RSVD#A19

RSVD#A20

RSVD#B20

RSVD_TP#AA5

RSVD_TP#AA4

RSVD_TP#R8

RSVD_TP#AD3

RSVD_TP#AD2

RSVD_TP#AA2

RSVD_TP#AA1

RSVD_TP#R9

RSVD_TP#AG7

RSVD_TP#AE3

RSVD#U9

RSVD#T9

RSVD#AC9

RSVD#AB9

RSVD_TP#V4

RSVD_TP#V5

RSVD_TP#N2

RSVD_TP#AD5

RSVD_TP#AD7

RSVD_TP#W3

RSVD_TP#W2

RSVD_TP#N3

RSVD_TP#AE5

RSVD_TP#AD9

CFG4

CFG4 - Display Port Presence

OF 9

RSVD#AH25

RSVD#AK26

RESERVED

SO-DIMM VREFDQ (M3) Circuit

for Clarksfield Processor

RSVD#AJ13

RSVD#AJ12

CPU Piin AJ13 and AJ12:

Core voltage sense line.

Via from PGA pad to the back of the MB

and provide test point.

Do not route any additional trace.

RSVD#J29

RSVD#J28

1:Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

VSS

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS (AP34) can be left NC is

CRB implementation; EDS/DG

recommendation to GND.

RSVD_VSS

R1117

0R0402-PAD-2-GP

CFG7

R1103

DY 3K01R2F-3-GP

A

CFG7(Reserved) - Temporarily used for early

Clarksfield samples.

CFG7

Clarksfield (only for early samples pre-ES1) Connect to GND with 3.01K Ohm/5% resistor.

Note: Only temporary for early CFD sample

(rPGA/BGA) [For details please refer to the

WW33 MoW and sighting report].

For a common M/B design (for AUB and CFD),

the pull-down resistor shouble be used. Does

not impact AUB functionality.

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU - Reserve (4/7)

Size

Document Number

Custom

Date:

5

Rev

-1

Fonseca 14.1" DIS

Friday, March 19, 2010

Sheet

1

11

of

89

CPU1F

AUBURNDALE

1

2

1

2

1

2

1

2

The decoupling capacitors, filter

recommendations and sense resistors on the

CPU/PCH Rails are specific to the CRB

Implementation. Customers need to follow the

recommendations in the Calpella Platform

Design Guide.

C1218

C1219

C1217

1.1V RAIL POWER

DY

C1235

SC22U6D3V5MX-2GP

C1234

SC10U10V5KX-2GP

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

Please note that

The VTT Rail values are

Arrandale for VTT=1.05V

Clarksfield for VTT=1.1V

CPU VIDS

PSI#

POWER

VID0

VID1

VID2

VID3

VID4

VID5

VID6

PROC_DPRSLPVR

VTT_SELECT

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

PSI# 47

H_VID[6..0]

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

47

PM_DPRSLPVR

47

B

G15

H_VTTVID1

TP1201

Arrandale drives this pin High for 1.05V

Clarksfield drives this pin Low for 1.1V

+VCC_CORE

R1203

0R0402-PAD-2-GP

1

2

1

2

R1201

0R0402-PAD-2-GP

1

2

B15

A15

VTT_SENSE_R

TP_VSS_SENSE_VTT 1

R1202

100R2F-L1-GP-U

R1206

0R2J-2-GP

1

DY

TP1202

VCC_SENSE_R

VSS_SENSE_R

39,47

VTT_SENSE 52

DY

DY

VCC_SENSE 47

VSS_SENSE 47

R1204

100R2F-L1-GP-U

AJ34

AJ35

CPU_IMON

VTT_SENSE

VSS_SENSE_VTT

CPU_IMON_R

R1208

27D4R2F-L1-GP

2

VCC_SENSE

VSS_SENSE

AN35

ISENSE

R1205

0R0402-PAD-2-GP

1

2

R1207

27D4R2F-L1-GP

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

C1209

SC10U10V5KX-2GP

C1208

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1207

+1.05V_VTT

SC10U10V5KX-2GP

C1216

SC10U10V5KX-2GP

C1206

SC10U10V5KX-2GP

C1205

SC10U10V5KX-2GP

C1204

SC22U6D3V5MX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5MX-3GP

C1203

SC10U10V5KX-2GP

C1242

C1202

+1.05V_VTT

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

CPU CORE SUPPLY

C1241

C1233

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C1240

C1232

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

SC10U10V5KX-2GP

C1231

+1.05V_VTT

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

SC10U10V5KX-2GP

C1225

SC10U10V5KX-2GP

C1239

C1215

SC22U6D3V5MX-2GP

C1230

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C1238

C1224

SC10U6D3V5KX-1GP

C1229

C1214

SC22U6D3V5MX-2GP

C1223

SC10U6D3V5KX-1GP

C1237

C1213

SC22U6D3V5MX-2GP

C1228

SC10U10V5KX-2GP

DY

C1222

SC22U6D3V5MX-2GP

C1236

SC10U6D3V5MX-3GP

SC22U6D3V5MX-2GP

DY

C1227

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1201

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1226

C1221

C1212

SC22U6D3V5MX-2GP

C1220

C1211

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C1210

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

OF 9

SC10U10V5KX-2GP

48A

+VCC_CORE

D

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

SENSE LINES

+VCC_CORE

PROCESSOR CORE POWER

SSID = CPU

VSS_SENSE_R

47

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU - VCC_CORE (5/7)

Size

Document Number

Custom

Date:

5

Friday, March 19, 2010

Rev

-1

Fonseca 14.1" DIS

Sheet

1

12

of

89

SSID = CPU

C1315

DY

TC1304

SE330U2VDM-L-GP

C1314

C1313

C1312

C1311

C1310

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

J22

J20

J18

H21

H20

H19

VTT1

VTT1

VTT1

VTT1

P10

N10

L10

K10

C1309

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

+1.5V_RUN_CPU

3A

2

1

2

+1.05V_VTT

- 1.5V RAILS

SENSE

LINES

GRAPHICS VIDs

R1301

GFX_IMON_R

1KR2J-1-GP

DDR3

AR25

AT25

AM24

SC22U6D3V5MX-2GP

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

SC10U6D3V5KX-1GP

AM22

AP22

AN22

AP23

AM23

AP24

AN24

SC1U10V2KX-1GP

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

SC1U10V2KX-1GP

VTT1

VTT1

VTT1

AR22

AT22

SC1U6D3V2KX-GP

J24

J23

H25

VAXG_SENSE

VSSAXG_SENSE

SC1U6D3V2KX-GP

C1317

SC10U10V5KX-2GP

FDI

C1316

SC10U10V5KX-2GP

OF 9

SC1U10V2KX-1GP

+1.05V_VTT

GRAPHICS

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

POWER

AUBURNDALE

CPU1G

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

C1318

SC22U6D3V5MX-2GP

C1319

SC10U10V5KX-2GP

1

2

C1325

SC10U10V5KX-2GP

B

C1329

C1328

C1327

C1326

C1330

SC22U6D3V5MX-2GP

DY

SC2D2U10V5KX-2GP

1.35A

SC4D7U6D3V3KX-GP

L26

L27

M26

SC1U25V5KX-1GP

VCCPLL VTT1

VCCPLL VTT1

VCCPLL VTT1

+1.8V_RUN

SC1U25V5KX-1GP

Please note that the VTT Rail Values

Arrandale for VTT=1.05V

Clarksfield for VTT=1.1V

C1324

SC10U10V5KX-2GP

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

1

2

1

2

1

2

C1323

SC22U6D3V5MX-2GP

C1322

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C1321

PEG & DMI

C1320

1.8V

18A

1.1V

+1.05V_VTT

+1.05V_VTT

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU - GFXCORE (6/7)

Size

A3

Document Number

Date:

Friday, March 19, 2010

Rev

-1

Fonseca 14.1" DIS

Sheet

1

13

of

89

SSID = CPU

8

CPU1H

OF 9

9

VSS

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

K27

K9

K6

K3

J32

J30

J21

J19

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

H8

H5

H2

G34

G31

G20

G9

G6

G3

F30

F27

F25

F22

F19

F16

E35

E32

E29

E24

E21

E18

E13

E11

E8

E5

E2

D33

D30

D26

D9

D6

D3

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

B8

B6

B4

A29

A27

A23

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

OF 9

AUBURNDALE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AT35 AR35

AT34

B35 A35

A34

3X

2X

NCTF

CPU1, Board Top View

4X

VSS

NCTF TEST PIN:

A35,AT1,AT35,B1,A3,A33,A34,AP1,AP35,

AR1,AR35,AT2,AT3,AT33,AT34,B35,C1,C35

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AUBURNDALE

CPU1I

AT20

AT17

AR31

AR28

AR26

AR24

AR23

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AL9

AL6

AL3

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AJ8

AJ5

AJ2

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

VSS_NCTF#AR34

VSS_NCTF#B34

VSS_NCTF#B2

AR34

B34

B2

VSS_NCTF#B1

VSS_NCTF#A35

VSS_NCTF#AT1

VSS_NCTF#AT35

RSVD_NCTF#AT33

RSVD_NCTF#AT34

RSVD_NCTF#AP35

RSVD_NCTF#AR35

RSVD_NCTF#AT3

RSVD_NCTF#AR1

RSVD_NCTF#AP1

RSVD_NCTF#AT2

RSVD_NCTF#C1

RSVD_NCTF#A3

RSVD_NCTF#C35

RSVD_NCTF#B35

RSVD_NCTF#A34

RSVD_NCTF#A33

B1

A35

AT1

AT35

AT33

AT34

AP35

AR35

AT3

AR1

AP1

AT2

C1

A3

C35

B35

A34

A33

1X

AT2

AT1 AR1

A3

C1 B1

TP_MCP_VSS_NCTFB1

TP_MCP_VSS_NCTFA35

TP_MCP_VSS_NCTFAT1

TP_MCP_VSS_NCTFAT35

1

1

1

1

TP1401

TP1404

TP1410

TP1407

TP_MCP_VSS_NCTFAT34 1

TP1409

TP_MCP_VSS_NCTFAR35 1

TP1408

TP_MCP_VSS_NCTFAR1

TP1412

TP_MCP_VSS_NCTFAT2

TP_MCP_VSS_NCTFC1

TP_MCP_VSS_NCTFA3

1

1

1

TP1411

TP1402

TP1403

TP_MCP_VSS_NCTFA34

TP1405

All NCTF pins should be Test

Points and should be routed as

trace.

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU - VSS (7/7)

Size

A3

Document Number

Date:

Friday, March 19, 2010

Rev

-1

Fonseca 14.1" DIS

Sheet

1

14

of

89

(Blank)

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Date:

5

Reserve

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

Sheet

1

15

of

89

(Blank)

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Date:

5

Reserve

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

Sheet

1

16

of

89

(Blank)

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Date:

5

Reserve

Rev

-1

Fonseca 14.1" DIS

Thursday, March 18, 2010

Sheet

1

17

of

89

1

2

1

2

1

M_VREF_CA_DIMM1

M_VREF_DQ_DIMM1

126

1

30

9,19 DDR3_DRAMRST#

MA_VTT

203

204

1

2

2

ODT0

ODT1

VREF_CA

VREF_DQ

1

2

C1826

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1825

RESET#

VTT1

VTT2

SA0_DIMM1

SA1_DIMM1

77

122

125

DY

+1.5V_SUS

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

C1802

DY

C1803

If SA0 DIM0 = 1, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA2

SO-DIMMA TS Address is 0x32

C

SODIMM A DECOUPLING

+1.5V_SUS

C1810

DY

DY

2

C1809

C1819

1

2

C1818

C1817

C1801

C1808

C1807

+1.5V_SUS

Near Memory

+1.5V_SUS

Plane

C1827

C1828

C1829

C1830

+1.5V_RUN_CPU

DY2

SCD1U16V2ZY-2GP

DY2

SCD1U16V2ZY-2GP

DY2

SCD1U16V2ZY-2GP

DY2

SCD1U16V2ZY-2GP

Near CPU

+1.5V_RUN

Plane

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

62.10017.N61

DDR3-204P-42-GP

Title

Main:62.10017.N61

DDR III Socket - DM1

Size

Document Number

Custom

2nd:62.10017.F91

Date:

5

C1816

C1815

1

2

C1814

C1806

C1813

C1805

Layout Note:

Place these Caps near

SO-DIMMA.

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

C1804

DY

TC1801

0904 SA

197

201

1

2

1

2

1

2

1

2

1

C1824

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C1823

199

SC10U6D3V3MX-GP

116

120

10 M_ODT0

10 M_ODT1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Note:

If SA0 DIM0 = 0, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA0

SO-DIMMA TS Address is 0x30

SC1U10V2KX-1GP

MA_VTT

12

29

47

64

137

154

171

188

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

PCH_SMBDATA_MEM 19,23,40,58

PCH_SMBCLK_MEM 19,23,40,58

+3.3V_RUN

SC10U6D3V3MX-GP

Place these caps

close to VTT1 and

VTT2.

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

NC#1

NC#2

NC#/TEST

2 0R0402-PAD-2-GP

2 0R0402-PAD-2-GP

SC1U10V2KX-1GP

R1809

0R0603-PAD-2-GP

SA0

SA1

R1804 1

R1805 1

198

SC10U6D3V3MX-GP

C1822

SC10U10V5KX-2GP

10

27

45

62

135

152

169

186

VDDSPD

SODIMM1_1_SMB_DATA_R

SODIMM1_1_SMB_CLK_R

R1801

0R0402-PAD-2-GP

SC1U10V2KX-1GP

+0.75V_DDR_VTT

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

EVENT#

200

202

R1803

0R0402-PAD-2-GP

SC10U6D3V3MX-GP

+0.75V_DDR_VTT

SDA

SCL

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

SC10U6D3V3MX-GP

Place between DM1 and DM2.

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

M_CLK_DDR1 10

M_CLK_DDR#1 10

11

28

46

63

136

153

170

187

SCD1U16V2KX-3GP

C1821

SC2D2U16V3KX-GP

M_CLK_DDR0 10

M_CLK_DDR#0 10

102

104

SC10U6D3V3MX-GP

M_VREF_DQ_DIMM1

SA1_DIMM1

SCD1U16V2KX-3GP

1

2

R1808

0R0603-PAD-2-GP

C1820

SCD1U10V2KX-5GP

101

103

SA0_DIMM1

SCD1U10V2KX-5GP

M_CKE0 10

M_CKE1 10

SCD1U16V2KX-3GP

+V_DDR_MCH_REF

73

74

R1802

DY 10KR2J-3-GP

SC10U6D3V3MX-GP

C1812

SC2D2U16V3KX-GP

M_CS#0 10

M_CS#1 10

10

SC10U6D3V3MX-GP

M_VREF_CA_DIMM1

CK1

CK1#

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

114

121

M_A_A[15..0]

SE330U2VDM-L-GP

1

2

R1807

0R0603-PAD-2-GP

C1811

SCD1U10V2KX-5GP

CK0

CK0#

M_A_RAS# 10

M_A_WE# 10

M_A_CAS# 10

10

SC2D2U16V3KX-GP

+V_DDR_MCH_REF

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

CKE0

CKE1

110

113

115

SCD1U10V2KX-5GP

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

CS0#

CS1#

M_A_DQS[7..0]

10 M_A_DQ[63..0]

RAS#

WE#

CAS#

10

+3.3V_RUN

NP1

NP2

109

108

NP1

NP2

10 M_A_BS0

10 M_A_BS1

A0

A1

A2

A3

A4

A5