Beruflich Dokumente

Kultur Dokumente

DEE6113 - Practical Work2 PDF

Hochgeladen von

FonzBahariOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

DEE6113 - Practical Work2 PDF

Hochgeladen von

FonzBahariCopyright:

Verfügbare Formate

POLITEKNIK SULTAN HAJI AHMAD SHAH KUANTAN

DEPARTMENT OF ELECTRICAL ENGINEERING

DEE6113 CMOS IC DESIGN

Practical Work 2

Layout Design and Simulation of

MOS Transistor

Registration

No.

No

Name

Practical

Work Report

(Cognitive)

Practical Skill

Marks

(Psychomotor)

Total

Marks

1.

/ 30

/ 70

/ 100

2.

/ 30

/ 70

/ 100

CLASS

LECTURER NAME

: PN. NOORFOZILA BINTI BAHARI

DATE SUBMITTED

(Note: Submit this page along with the practical skill rubric after each Practical Work is completed)

Practical Work Report Marks Distribution

Report format:

1.

Title and Outcomes

/4

2.

Result

/ 10

3.

Discussion

/ 12

4.

Conclusion

/4

TOTAL :

/ 30

DEE6113 CMOS IC Design

PRACTICAL WORK 2

2.1 TITLE: Layout Design and Simulation of MOS Transistor

2.2 LEARNING OUTCOMES

At the end of this practical work session, the student should be able to:

1. design NMOS and PMOS transistor layout according to the Design Rules.

2. simulate NMOS and PMOS transistor characteristics.

3. simulate NMOS and PMOS dynamic behaviour.

2.3 EQUIPMENT/TOOLS

PC Set & Microwind 2.6a software.

2.4 PROCEDURE

Part 1 : Designing NMOS transistor layout according to the design rule.

Open the Microwind Editor window.

Select the Foundry file from File menu. Select cmos012.rul file.

Draw the NMOS layout as shown in figure 2.1. (Use NMOS size : W=6, L=2)

Make sure to conform to the design rules (refer to Appendix A).

Polysilicon

Contact N+ diff / Metal1

Metal1

Contact N+ diff / Metal1

Metal1

N+ Diffusion

Figure 2.1: NMOS Layout

Run DRC by selecting:

>Analysis>Design Rule Checker

If your layout is correct, then no messages will appear. If there are some errors, then the

warning messages will appear near the errors. Please modify your layout until no error

messages appear. (refer to the design rules in Appendix A).

Page | 1

DEE6113 CMOS IC Design

View the cross section of the NMOS transistor by selecting:

>Simulate>Process Section in 2D or you can click this icon :

View the the process steps in producing the NMOS by selecting:

>Simulate>Process Steps in 3D or you can click this icon :

Part 2 : Simulating NMOS transistor characteristics.

The Id/Vd characteristics if the NMOS transistor can be obtained by selecting:

>Simulate>MOS Characteristics or you can click this icon :

The NMOS characteristics is shown in Figure 2.2. From the simulation, it is shown that the

NMOS width is 1.8m and the length is 0.6m. A high gate voltage (Vg =5.0) corresponds to

the highest Id/Vd curve. For Vg=0, no current flows. The maximum current is obtained for

Vg=5.0V, Vd=5.0V, with Vs=0.0.

The NMOS parameters shown in Figure 2.2 correspond to SPICE Level 3.

Figure 2.2: NMOS Id/Vd Plot

Part 3 : Simulating NMOS dynamic behaviour

To activate the NMOS, properties must be added to the layout. The most convenient way to

operate the NMOS is to apply a clock to the gate, another to the source and to observe the

drain. The summary of available properties is shown in figure 2.3 below.

Page | 2

DEE6113 CMOS IC Design

VDD Property

VSS Property

Clock Property

Node Visible

Pulse Property

Figure 2.3: Properties to be used in MOS dynamic behaviour simulation

Apply a clock to the drain. Click on the Clock icon, click on the left diffusion. The Clock menu

appears as in figure 2.4. Change the name into drain and click on OK. A default clock with

2 ns period is generated. The Clock property is sent to the node and appears at the right

hand side of the desired location with the name drain .

Figure 2.4: Add clock property to the layout

Apply a clock to the gate. Click on the Clock icon and then, click on the polysilicon gate. The

clock menu appears again. Change the name into gate and click on OK to apply a clock

with 8 ns period.

To watch the output, click on the Visible icon and then, click on the right diffusion. The

window as shown in figure 2.5 appears. Change the name into source. Click OK. The

Visible property is then sent to the node. The wave form of this node will appear at the next

simulation

Page | 3

DEE6113 CMOS IC Design

Figure 2.5: Add a visible property to the layout

All the properties are marked on the layout as shown in figure 2.6.

Figure 2.6: NMOS layout with dynamic properties

Save before Simulation. It is IMPORTANT that you always save your layout BEFORE starting

any simulation !

To simulate the dynamic behaviour, select:

>Simulate>Run Simulation>Voltage vs Time (default) on the main menu. The timing

diagrams of the NMOS appear, as shown in figure 2.7.

Page | 4

DEE6113 CMOS IC Design

Figure 2.7: Timing diagram of NMOS transistor

When the gate is at zero, no channel exists so the node source is disconnected from the

drain. When the gate is on, the source copies the drain. It can be observed that the NMOS

device drives well at zero but poorly at the high voltage. The highest value of source is

around 3.41 Volt, that is VDD minus the threshold voltage. This means that the NMOS device

is bad at passing logic 1 but good at passing logic 0.

Part 4 : Designing and simulating PMOS Layout

Draw the PMOS layout as shown in figure 8. (Use PMOS size : W=12, L=2)

Polysilicon

N Well

Metal1

P+ Diffusion

Figure 8: PMOS Layout

Contact P+ Diff/Metal1

Repeat all the steps in Part 1 until Part 3 for the PMOS transistor layout.

Page | 5

DEE6113 CMOS IC Design

2.5 RESULT

In your report, include the results of the following:

1. NMOS

a. Layout without DRC error

b. Transistor cross section

c. Id - Vd characteristic curves

d. Input / Output timing diagram (dynamic behaviour)

(2 marks)

(1 mark)

(1 mark)

(1 mark)

2. PMOS

c. Layout without DRC error

d. Transistor cross section

c. Id - Vd characteristic curves

d. Input / Output timing diagram (dynamic behaviour)

(2 marks)

(1 mark)

(1 mark)

(1 mark)

2.6 DISCUSSION

1.

2.

Explain why PMOS transistor size is double the size of NMOS transistor.

(2 marks)

Make a compariosn between the Id - Vd characteristic curves between NMOS and PMOS

transistors.

(4 marks)

3.

4.

Does PMOS transistor good at passing logic 1? Explain your answer.

Explain the functions of design rules.

(2 marks)

(4 marks)

2.7 CONCLUSION

Give TWO(2) conclusions for this practical work.

(4 marks)

Page | 6

DEE6113 CMOS IC Design

Appendix A

Design Rules

1.

Nwell Design Rules

r101 Minimum well size : 12

r102 Between wells : 12

r110 Minimum surface : 144 2

2.

Diffusion Design Rules

r201

r202

r203

r204

r205

r206

r210

3.

Minimum N+ and P+ diffusion width : 4

Between two P+ and N+ diffusions : 4

Extra nwell after P+ diffusion : 6

Between N+ diffusion and nwell : 6

Border of well after N+ polarization 2

Distance between Nwell and P+ polarization 6

Minimum surface : 24 2

Polysilicon Design Rules

r301 Polysilicon width : 2

r302 Polysilicon gate on diffusion: 2

r303 Polysilicon gate on diffusion for high

voltage MOS: 4

r304 Between two polysilicon boxes : 3

r305 Polysilicon vs. other diffusion : 2

r306 Diffusion after polysilicon : 4

r307 Extra gate after polysilicium : 3

r310 Minimum surface : 8 2

Page | 7

DEE6113 CMOS IC Design

4.

Contact Design Rules

r401

r402

r403

r404

r405

r406

5.

Appendix A

Contact width : 2

Between two contacts : 5

Extra diffusion over contact: 2

Extra poly over contact: 2

Extra metal over contact: 2

Distance between contact and poly gate: 3

Metal & Via Design Rules

r501 Metal width : 4

r502 Between two metals : 4

r510 Minimum surface : 32 2

r601

r602

r603

r604

r605

Via width : 2

Between two Via: 5

Between Via and contact: 0

Extra metal over via: 2

Extra metal2 over via: 2

When r603=0, stacked via over

contact is allowed

Page | 8

DEE6113 CMOS IC Design

PRACTICAL SKILL ASSESSMENT RUBRIC

DEE6113 CMOS IC DESIGN

PRACTICAL WORK 2

Student Name :

Class :

Student ID# :

Date :

ASPECTS

A.

Technology feature

B.

Design rule

C.

Transistor size

D.

Metal layers

E.

F.

No DRC error

display

Layout Design

input / output /

floorplan

EXCELLENT

4-5

Use correct technology feature

for ALL parts of the layout.

Follow lambda design rule for

minimum width and spacing for

ALL polygons.

Use correct PMOS and NMOS

transistor size.

Use correct number of metal

layers and width.

Able to produce No DRC error

display for ALL layouts.

SCORE DESCRIPTION

MODERATE

2-3

Use correct technology feature

for parts of the layout.

POOR

1

SCALE

Use other technology feature.

x1

Follow lambda design rule for

MANY of the polygons.

Follow lambda design rule for

ONLY a few of the polygons.

x1

Use acceptable PMOS and NMOS

transistor size.

Use correct metal layers but

incorrect width.

Able to produce No DRC error

display for some of the layouts.

Use incorrect PMOS and

NMOS transistor size.

Use incorrect metal layers and

width.

Not able to produce No DRC

error display at ALL.

Produce acceptable floorplan

and input / output layout

design.

Not able to produce any

simulation for ALL of the

layouts.

Produce large layout size (end

product).

Produce good floorplan and

input / output layout design.

Produce appropriate floorplan

and input / output layout design.

Layout simulation

Able to produce the simulation

of ALL layouts correctly.

Able to produce the simulation

for some of the layouts correctly.

H.

Layout size (end

product)

Produce small layout size (end

product).

Produce acceptable layout size

(end product).

TOTAL

SCORE

x2

x2

x2

x2

x2

x2

/ 70

..

Supervisor Name & Signature

Das könnte Ihnen auch gefallen

- Inverter DesignDokument10 SeitenInverter DesignKirthika Vinoth KumarNoch keine Bewertungen

- Practical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11Von EverandPractical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11Noch keine Bewertungen

- MAHINDRA SCORPIO CRDeDokument148 SeitenMAHINDRA SCORPIO CRDeAlex Checa100% (4)

- L Edit Presentation1 PrintableDokument60 SeitenL Edit Presentation1 Printablemamaw231Noch keine Bewertungen

- On-Board Diagnostic (Immobilizer System)Dokument5 SeitenOn-Board Diagnostic (Immobilizer System)pavel35Noch keine Bewertungen

- PT19 1300 SeriesDokument112 SeitenPT19 1300 Seriesbejoythomas100% (1)

- Vlsi Lab Manual (Microwind)Dokument40 SeitenVlsi Lab Manual (Microwind)anon_1360815100% (7)

- Communication Systems: Building Utilities 2Dokument53 SeitenCommunication Systems: Building Utilities 2John Lloyd AgapitoNoch keine Bewertungen

- MOS Integrated Circuit DesignVon EverandMOS Integrated Circuit DesignE. WolfendaleNoch keine Bewertungen

- P544 (87LB 21BU 50BU) Test Report Rev 3Dokument21 SeitenP544 (87LB 21BU 50BU) Test Report Rev 3samiahmedmansourNoch keine Bewertungen

- Labs-VLSI Lab ManualDokument56 SeitenLabs-VLSI Lab ManualAbdul Basit Awan50% (2)

- Complete PCB Design Using OrCAD Capture and PCB EditorVon EverandComplete PCB Design Using OrCAD Capture and PCB EditorBewertung: 5 von 5 Sternen5/5 (1)

- VLSI Backend Lab ManualDokument56 SeitenVLSI Backend Lab ManualAllanki Sanyasi Rao100% (1)

- DX3EVM Mock Examination San Fdo PampDokument11 SeitenDX3EVM Mock Examination San Fdo PampEmmanuel Vallejos100% (1)

- Layout ExamplesDokument13 SeitenLayout Examplesnazibhd786Noch keine Bewertungen

- Practical Work 3 - CMOS + Rubric PDFDokument25 SeitenPractical Work 3 - CMOS + Rubric PDFRiki SmithNoch keine Bewertungen

- Microprocessor System Design: A Practical IntroductionVon EverandMicroprocessor System Design: A Practical IntroductionNoch keine Bewertungen

- Dec50143 PW1Dokument11 SeitenDec50143 PW1imanbatrisyia288Noch keine Bewertungen

- DEE6113 - Practical Work3 PDFDokument8 SeitenDEE6113 - Practical Work3 PDFFonzBahari67% (3)

- DEE6113 - Practical Work1 PDFDokument6 SeitenDEE6113 - Practical Work1 PDFFonzBahariNoch keine Bewertungen

- Dec50143 Pw2 IzzDokument11 SeitenDec50143 Pw2 Izziskandardaniel0063Noch keine Bewertungen

- DEE6113 - Practical Work6 PDFDokument4 SeitenDEE6113 - Practical Work6 PDFFonzBahari0% (1)

- Dec50143 PW2Dokument8 SeitenDec50143 PW2Muhammad JazliNoch keine Bewertungen

- ResultDokument7 SeitenResultZulli KhairiNoch keine Bewertungen

- Practical Work 3Dokument15 SeitenPractical Work 3Kalai ShanNoch keine Bewertungen

- Vlsi Laboratory: List of ExperimentsDokument49 SeitenVlsi Laboratory: List of ExperimentssantoshNoch keine Bewertungen

- Micro WindDokument14 SeitenMicro Windlak_prabNoch keine Bewertungen

- DEE6113 - Practical Work4 PDFDokument10 SeitenDEE6113 - Practical Work4 PDFFonzBahari0% (1)

- DEE6113 - Practical Work5 PDFDokument7 SeitenDEE6113 - Practical Work5 PDFFonzBahariNoch keine Bewertungen

- Dec50143 - PW3 (M.adam F1126)Dokument8 SeitenDec50143 - PW3 (M.adam F1126)iskandardaniel0063Noch keine Bewertungen

- Pw1 Cmos Daniel f1070Dokument9 SeitenPw1 Cmos Daniel f1070iskandardaniel0063Noch keine Bewertungen

- Practical Work Report 1Dokument6 SeitenPractical Work Report 1KimZhiMie100% (1)

- VLSI Lab CompendiumDokument52 SeitenVLSI Lab CompendiumSaad Ali Khan SherwaniNoch keine Bewertungen

- M.Tech Lab Manual-FInal-4.8.2021Dokument28 SeitenM.Tech Lab Manual-FInal-4.8.2021RAMYA VATHSALYA PNoch keine Bewertungen

- IMP MicrowindDokument12 SeitenIMP Microwindrahul_rvm82Noch keine Bewertungen

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Dokument10 SeitenQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNoch keine Bewertungen

- CMOS Design RulesDokument21 SeitenCMOS Design Rulesrakheep123Noch keine Bewertungen

- Vlsi Lab ManualDokument56 SeitenVlsi Lab Manualdilawar sumraNoch keine Bewertungen

- Lamda Rules Layout TutorialDokument15 SeitenLamda Rules Layout TutorialSougata GhoshNoch keine Bewertungen

- Nirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VDokument15 SeitenNirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VPragya jhalaNoch keine Bewertungen

- ch6 97 PDFDokument51 Seitench6 97 PDFRitu SinghNoch keine Bewertungen

- Lecture 5: Microwind/DCSH: CSCI 5330 Digital CMOS VLSI DesignDokument30 SeitenLecture 5: Microwind/DCSH: CSCI 5330 Digital CMOS VLSI DesignDavid ReevesNoch keine Bewertungen

- Microwind TutorialDokument87 SeitenMicrowind Tutorialminajohn86% (7)

- Tanner Lab Manual (S-Edit and L-Edit)Dokument22 SeitenTanner Lab Manual (S-Edit and L-Edit)sandeep_sggsNoch keine Bewertungen

- Basic Physical Design AN: Unit 3Dokument17 SeitenBasic Physical Design AN: Unit 3Shrey MalikNoch keine Bewertungen

- Microwind Tutorial Appendix 1Dokument26 SeitenMicrowind Tutorial Appendix 1mohammadbaig337405Noch keine Bewertungen

- VLSI Design Advanced Lab ManualDokument74 SeitenVLSI Design Advanced Lab ManualShiraz HusainNoch keine Bewertungen

- Industrial Traning Report 3Dokument26 SeitenIndustrial Traning Report 3Sai ChesettiNoch keine Bewertungen

- Vlsi Lab Manual-Microwind PDFDokument54 SeitenVlsi Lab Manual-Microwind PDFyayavaramNoch keine Bewertungen

- Layout Manual - CMOS Inverter - Exp 3Dokument22 SeitenLayout Manual - CMOS Inverter - Exp 3ApoorvaNoch keine Bewertungen

- Lab Title:: Introduction To Microwind and Analysis of CMOS 0.25 MicronDokument7 SeitenLab Title:: Introduction To Microwind and Analysis of CMOS 0.25 MicronWilliam GonzalesNoch keine Bewertungen

- ECE 240 - Project1-CMOS InverterDokument7 SeitenECE 240 - Project1-CMOS InverterAbhishek Sthanik GubbiNoch keine Bewertungen

- 9.1 CFD Module Overview: BenefitsDokument18 Seiten9.1 CFD Module Overview: BenefitsHari PrasadNoch keine Bewertungen

- 2020 IC Design Contest: Full-Custom CategoryDokument6 Seiten2020 IC Design Contest: Full-Custom CategoryE94086018陳寧文Noch keine Bewertungen

- Experiment No. 3: Layout Design of A CMOS Inverter: ECE 4101 Computer and Information Lab III (ECE 4141 VLSI Design Part)Dokument11 SeitenExperiment No. 3: Layout Design of A CMOS Inverter: ECE 4101 Computer and Information Lab III (ECE 4141 VLSI Design Part)Ghanshyam V RaoNoch keine Bewertungen

- VLSI Lab NewDokument19 SeitenVLSI Lab NewRajesh HarikrishnanNoch keine Bewertungen

- Integrated Circuit Layout and Simulation: Prepared by Charles Sumion JKE Politeknik Kota KinabaluDokument16 SeitenIntegrated Circuit Layout and Simulation: Prepared by Charles Sumion JKE Politeknik Kota KinabaluYazid Abdul HamidNoch keine Bewertungen

- Practical Work 5Dokument9 SeitenPractical Work 5Kalai ShanNoch keine Bewertungen

- Practical Work 2 - CMOS + Rubric PDFDokument12 SeitenPractical Work 2 - CMOS + Rubric PDFRiki SmithNoch keine Bewertungen

- Stick Diagrams and LayoutsDokument17 SeitenStick Diagrams and LayoutsPraneetha InumarthiNoch keine Bewertungen

- MINOR2 DfinalocxDokument32 SeitenMINOR2 DfinalocxVenkatesh KumarNoch keine Bewertungen

- TierDokument9 SeitenTierbitMorph3rNoch keine Bewertungen

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionVon EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNoch keine Bewertungen

- DEE6113 - Practical Work4 PDFDokument10 SeitenDEE6113 - Practical Work4 PDFFonzBahari0% (1)

- DEE6113 - Practical Work2 PDFDokument10 SeitenDEE6113 - Practical Work2 PDFFonzBahariNoch keine Bewertungen

- DEE6113 - Practical Work5 PDFDokument7 SeitenDEE6113 - Practical Work5 PDFFonzBahariNoch keine Bewertungen

- DEE6113 - Practical Work4 PDFDokument10 SeitenDEE6113 - Practical Work4 PDFFonzBahari0% (1)

- DEE6113 Course Outline Jun2016Dokument4 SeitenDEE6113 Course Outline Jun2016FonzBahariNoch keine Bewertungen

- High Side Smart Power Solid State Relay: Pentawatt (Vertical) Pentawatt (Horizontal)Dokument11 SeitenHigh Side Smart Power Solid State Relay: Pentawatt (Vertical) Pentawatt (Horizontal)Paulo SilvaNoch keine Bewertungen

- Orange CR20L Manual V16Dokument13 SeitenOrange CR20L Manual V16Jesus ContrerasNoch keine Bewertungen

- In Verter AGILE - ErrorListDokument14 SeitenIn Verter AGILE - ErrorListNapoleon AmbaladaNoch keine Bewertungen

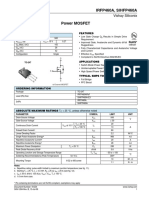

- Vishay IRFP460APBF Datasheet PDFDokument8 SeitenVishay IRFP460APBF Datasheet PDFkamel keddarNoch keine Bewertungen

- QuestHandbook May 2021Dokument22 SeitenQuestHandbook May 2021Pablo FloresNoch keine Bewertungen

- Icepower250A: 250W General Purpose Icepower AmplifierDokument17 SeitenIcepower250A: 250W General Purpose Icepower AmplifierJoão LopesNoch keine Bewertungen

- Beagle Bone SchematicDokument11 SeitenBeagle Bone Schematictemp5556Noch keine Bewertungen

- MTBF Calculation Flatpack2 TEC25Dokument6 SeitenMTBF Calculation Flatpack2 TEC25sumanNoch keine Bewertungen

- Lab1 DiodesDokument4 SeitenLab1 DiodesDavid TandjayaNoch keine Bewertungen

- Cat Switchgear - Eaton Consulting Application GuideDokument58 SeitenCat Switchgear - Eaton Consulting Application GuideFélix VelascoNoch keine Bewertungen

- Design and ASIC Implementation of A 3GPP LTE-Advance Turbo Encoder and Turbo DecoderDokument5 SeitenDesign and ASIC Implementation of A 3GPP LTE-Advance Turbo Encoder and Turbo DecoderghionoiucNoch keine Bewertungen

- FNA Edge Network Appliance: Operations GuideDokument22 SeitenFNA Edge Network Appliance: Operations GuideYosvensa SetiawanNoch keine Bewertungen

- CD4069Dokument5 SeitenCD4069abdullahNoch keine Bewertungen

- View Topic - New VT Plus Series FX Loop - ValvetronixDokument5 SeitenView Topic - New VT Plus Series FX Loop - ValvetronixStaticNoch keine Bewertungen

- Huawei Power Systems Acceptance Manual - Update - 20190621Dokument25 SeitenHuawei Power Systems Acceptance Manual - Update - 20190621wawanNoch keine Bewertungen

- Руководство По Подключению к ПЛК Англ ЯзыкDokument801 SeitenРуководство По Подключению к ПЛК Англ Языкazz zinouNoch keine Bewertungen

- Estimating Maximum Mosfet Switching FrequencyDokument5 SeitenEstimating Maximum Mosfet Switching FrequencyFlavio AlmeidaNoch keine Bewertungen

- DIY EEG and ECG Circuit PDFDokument10 SeitenDIY EEG and ECG Circuit PDFfernandovaras2005Noch keine Bewertungen

- The HD58X Jubilee Is Available Through OnlyDokument20 SeitenThe HD58X Jubilee Is Available Through Only전유신Noch keine Bewertungen

- VSE1 W PX200 Batt EngineDokument1 SeiteVSE1 W PX200 Batt EngineTedy AdhinegoroNoch keine Bewertungen

- How Do Wind Power Plants Work?: How Are Wind Turbines Connected To The Electricity Network ?Dokument3 SeitenHow Do Wind Power Plants Work?: How Are Wind Turbines Connected To The Electricity Network ?Sección Uso CasinoNoch keine Bewertungen

- 2SD863Dokument5 Seiten2SD863FeryBaleaNoch keine Bewertungen

- Synch Panel 3200aDokument11 SeitenSynch Panel 3200aIslam AlazbNoch keine Bewertungen

- 3 Ele Hex HatDokument5 Seiten3 Ele Hex Hatpy8eloNoch keine Bewertungen