Beruflich Dokumente

Kultur Dokumente

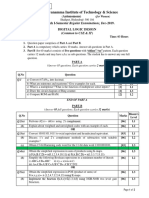

II Mid Examination Answer All The Questions: Quality Analysis of Question Paper

Hochgeladen von

srinu2470 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

44 Ansichten2 SeitenThis document contains the details of a mid-term exam for the second year EEE branch students. It has 3 questions worth a total of 30 marks. Question 1 (10 marks) asks students to implement and design Boolean functions A, B, C, and D using PAL. Question 2 has two parts - part a (3 marks) asks students to construct a JK flip flop using a D flip flop and multiplexer, and part b (7 marks) asks students to draw the schematic of an RS master slave flip flop and provide its truth table. Question 3 also has two parts - part a (3 marks) asks about capabilities and limitations of finite state machines, and part b (7 marks)

Originalbeschreibung:

Switching Theory and Logic Design

Originaltitel

STLD II MID Analysis Sheet

Copyright

© © All Rights Reserved

Verfügbare Formate

DOCX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenThis document contains the details of a mid-term exam for the second year EEE branch students. It has 3 questions worth a total of 30 marks. Question 1 (10 marks) asks students to implement and design Boolean functions A, B, C, and D using PAL. Question 2 has two parts - part a (3 marks) asks students to construct a JK flip flop using a D flip flop and multiplexer, and part b (7 marks) asks students to draw the schematic of an RS master slave flip flop and provide its truth table. Question 3 also has two parts - part a (3 marks) asks about capabilities and limitations of finite state machines, and part b (7 marks)

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

44 Ansichten2 SeitenII Mid Examination Answer All The Questions: Quality Analysis of Question Paper

Hochgeladen von

srinu247This document contains the details of a mid-term exam for the second year EEE branch students. It has 3 questions worth a total of 30 marks. Question 1 (10 marks) asks students to implement and design Boolean functions A, B, C, and D using PAL. Question 2 has two parts - part a (3 marks) asks students to construct a JK flip flop using a D flip flop and multiplexer, and part b (7 marks) asks students to draw the schematic of an RS master slave flip flop and provide its truth table. Question 3 also has two parts - part a (3 marks) asks about capabilities and limitations of finite state machines, and part b (7 marks)

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 2

II B.

Tech II Sem

Date: 12/04/16

1

.

Academic Year: 2015-2016

II Mid Examination

Max.Marks: 30

Branch: EEE

Sub: STLD

Time: 90 Mins.

Answer All the Questions

Implement and Design the following Boolean functions using PAL

[10M][BT L6] [C2222.4]

A(x,y,z) = (1, 2, 4, 6)

B(x,y,z) = (0, 1, 6, 7)

C(x,y,z) = (2,6)

D(x,y,z) = (1, 2, 3, 5, 7)

2

.

a. Construct a JK flip flop using a D flip flop, a 2x1 multiplexer and an inverter. [3M][BT L3] [C2222.5]

b. Draw the schematic circuit of RS master slave flip flop. Give its truth table and justify

the entries in the truth table.

[7M][BT L3] [C2222.5]

3

.

a. Write capabilities and limitations of Finite- State machine

[3M][BT L2] [C2222.6]

b. For the given Moore model machine obtain Mealy reduced state - table and hence draw the state diagram

[7M][BT L3] [C2222.6]

Quality Analysis of Question Paper

Course

STLD

Question

No

1

2.a

2.b

3.a

3.b

Total

L1

L2

L3 L4

L5

L6

1

1

1

1

1

1

3

Remarks by

Subject Expert

Signature of

Faculty

HOD

Das könnte Ihnen auch gefallen

- I Mid Examination Answer All The Questions (4M) (BT L3) (C2222.1) (6M) (BT L3) (C2222.1)Dokument1 SeiteI Mid Examination Answer All The Questions (4M) (BT L3) (C2222.1) (6M) (BT L3) (C2222.1)srinu247Noch keine Bewertungen

- ECE211 Digital ElectronicsDokument3 SeitenECE211 Digital Electronicstejaputta6Noch keine Bewertungen

- R5 210204 Switching Theory & Logic DesignDokument1 SeiteR5 210204 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- 21 - 2010 - Nov - R09 - STLDDokument8 Seiten21 - 2010 - Nov - R09 - STLDvasuvlsiNoch keine Bewertungen

- 3CS3 04 PDFDokument3 Seiten3CS3 04 PDFprashantvlsiNoch keine Bewertungen

- Digital Logic Design (Jntu - Uandistar.org)Dokument4 SeitenDigital Logic Design (Jntu - Uandistar.org)Arepalli SathibabuNoch keine Bewertungen

- DE - KOE 039 - Question BankDokument6 SeitenDE - KOE 039 - Question Bankyash vatsNoch keine Bewertungen

- B.Sc.-Computer Science PDFDokument85 SeitenB.Sc.-Computer Science PDFPiyush AnnadateNoch keine Bewertungen

- R5 210504 Digital Logic DesignDokument1 SeiteR5 210504 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- r05220403 Switching Theory and Logic DesignDokument8 Seitenr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANoch keine Bewertungen

- PGDCMDokument18 SeitenPGDCMMohit ChatapNoch keine Bewertungen

- JanuaryFebruary 2021Dokument1 SeiteJanuaryFebruary 2021vishwatejkachu944Noch keine Bewertungen

- DD&CO QBANK (Vtu23)Dokument3 SeitenDD&CO QBANK (Vtu23)manjufk456Noch keine Bewertungen

- 21 - 2011 - Dec - R09 - STLDDokument8 Seiten21 - 2011 - Dec - R09 - STLDvasuvlsiNoch keine Bewertungen

- STLD 2009 RegularDokument4 SeitenSTLD 2009 RegularrangerNoch keine Bewertungen

- Dlda 2Dokument2 SeitenDlda 2Manoj NaikNoch keine Bewertungen

- Digital Logic 2019 QuestionDokument2 SeitenDigital Logic 2019 QuestionDayan VaradNoch keine Bewertungen

- MCM 1112Dokument82 SeitenMCM 1112Yogesh2323Noch keine Bewertungen

- QBank DPSD cs2202Dokument6 SeitenQBank DPSD cs2202kunarajNoch keine Bewertungen

- BSCCST 203Dokument2 SeitenBSCCST 203api-3782519Noch keine Bewertungen

- R13 Nov 2016Dokument2 SeitenR13 Nov 2016Anil Kumar BNoch keine Bewertungen

- DLDDokument1 SeiteDLDBibah GeeNoch keine Bewertungen

- WWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Dokument2 SeitenWWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Anil Kumar BNoch keine Bewertungen

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Dokument18 SeitenUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNoch keine Bewertungen

- Ddco Question BankDokument3 SeitenDdco Question BankAftab YaragattiNoch keine Bewertungen

- Digital Logic DesignDokument2 SeitenDigital Logic DesignKomal JainNoch keine Bewertungen

- In Semester (Individual) AssignmentDokument10 SeitenIn Semester (Individual) AssignmentmuhammadNoch keine Bewertungen

- Switchinng Theory and Logic Design Feb 2022Dokument2 SeitenSwitchinng Theory and Logic Design Feb 2022panda pavanNoch keine Bewertungen

- Model Paper Kuru III Cs BtechDokument2 SeitenModel Paper Kuru III Cs Btecher_praveshNoch keine Bewertungen

- Digital Electronics June July 2022Dokument8 SeitenDigital Electronics June July 2022RCEE-2020 ONLINE FDPNoch keine Bewertungen

- Nov Dec 2014Dokument4 SeitenNov Dec 2014abdnazar2003Noch keine Bewertungen

- Question Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-ADokument3 SeitenQuestion Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-AmohanaNoch keine Bewertungen

- Roll No:: (An Autonomous Institution, Affiliated To Anna University, Chennai)Dokument1 SeiteRoll No:: (An Autonomous Institution, Affiliated To Anna University, Chennai)Venkatesh TNoch keine Bewertungen

- Digital Design Mid-Sem Question PaperDokument2 SeitenDigital Design Mid-Sem Question PaperAbhinav MishraNoch keine Bewertungen

- B.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015Dokument1 SeiteB.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015jayarami reddy pNoch keine Bewertungen

- Digital Logic DesignDokument4 SeitenDigital Logic DesignrppvchNoch keine Bewertungen

- Switching Theory and Logic DesignDokument6 SeitenSwitching Theory and Logic DesignVijay MNoch keine Bewertungen

- R07 Set No. 2Dokument8 SeitenR07 Set No. 2Samiullah MohammedNoch keine Bewertungen

- DSD Paper (B)Dokument2 SeitenDSD Paper (B)navneetecniecNoch keine Bewertungen

- DE PaperDokument4 SeitenDE Paperbhaveshgupta098Noch keine Bewertungen

- Solution 1 - Csci 343 - Fall 2012Dokument3 SeitenSolution 1 - Csci 343 - Fall 2012adchy7Noch keine Bewertungen

- Question Paper Code:: (10×2 20 Marks)Dokument2 SeitenQuestion Paper Code:: (10×2 20 Marks)kenny kannaNoch keine Bewertungen

- PPS - I Mid Term-SET-1Dokument1 SeitePPS - I Mid Term-SET-1EE ArnavNoch keine Bewertungen

- Mid 221Dokument1 SeiteMid 221prof_ktNoch keine Bewertungen

- WWW - Manaresults.Co - In: (Common To CSE, IT)Dokument2 SeitenWWW - Manaresults.Co - In: (Common To CSE, IT)Sajjad KhanNoch keine Bewertungen

- DLC Series IaDokument1 SeiteDLC Series IaAnusha NatarajanNoch keine Bewertungen

- BCA I I Digital SystemDokument4 SeitenBCA I I Digital SystemAmory Sabri AsmaroNoch keine Bewertungen

- Ec 242 - Digital ElectronicsDokument2 SeitenEc 242 - Digital ElectronicssubhazNoch keine Bewertungen

- DLD GTU Question Bank: Chapter-1 Binary SystemDokument5 SeitenDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Noch keine Bewertungen

- 9A04401 Switching Theory & Logic DesignDokument4 Seiten9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- AllDokument57 SeitenAllKhondoker Razzakul HaqueNoch keine Bewertungen

- Sample Paper Sample Paper Sample Paper Sample PaperDokument12 SeitenSample Paper Sample Paper Sample Paper Sample PaperAnuragGuptaNoch keine Bewertungen

- Term End Examination, 2019: Number of Printed Pages: 4 MCS-031 MCA (Revised)Dokument4 SeitenTerm End Examination, 2019: Number of Printed Pages: 4 MCS-031 MCA (Revised)Sreeganesh MadhavanNoch keine Bewertungen

- Logic Design June 2010 ESDokument2 SeitenLogic Design June 2010 ESPrasad C MNoch keine Bewertungen

- Up and Running with AutoCAD 2020: 2D Drafting and DesignVon EverandUp and Running with AutoCAD 2020: 2D Drafting and DesignNoch keine Bewertungen

- Up and Running with AutoCAD 2014: 2D and 3D Drawing and ModelingVon EverandUp and Running with AutoCAD 2014: 2D and 3D Drawing and ModelingBewertung: 5 von 5 Sternen5/5 (1)

- Linear Programming and Resource Allocation ModelingVon EverandLinear Programming and Resource Allocation ModelingNoch keine Bewertungen

- Up and Running with AutoCAD 2018: 2D Drafting and DesignVon EverandUp and Running with AutoCAD 2018: 2D Drafting and DesignNoch keine Bewertungen

- Upthrust ProblemsDokument3 SeitenUpthrust Problemssrinu24767% (3)

- Reasoning BitsDokument1 SeiteReasoning Bitssrinu247Noch keine Bewertungen

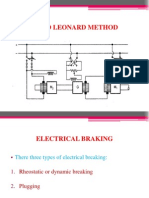

- 3 Phase Induction Motor Question BankDokument2 Seiten3 Phase Induction Motor Question Banksrinu247Noch keine Bewertungen

- Unit VDokument15 SeitenUnit Vsrinu247Noch keine Bewertungen

- Ps-II II MID Question BankDokument3 SeitenPs-II II MID Question Banksrinu247Noch keine Bewertungen

- KWL ChartDokument3 SeitenKWL Chartsrinu247Noch keine Bewertungen

- ct-2 QP SGPDokument1 Seitect-2 QP SGPsrinu247Noch keine Bewertungen

- Air Blast Circuit Breaker 1Dokument13 SeitenAir Blast Circuit Breaker 1srinu247Noch keine Bewertungen

- CS Lab External QPDokument1 SeiteCS Lab External QPsrinu247Noch keine Bewertungen

- Starter MethodsDokument11 SeitenStarter Methodssrinu247Noch keine Bewertungen

- Some Teaching MethodsDokument5 SeitenSome Teaching Methodssrinu247Noch keine Bewertungen

- Control Systems Questions For GATE, IES, PSU and Other Central and State Competitive ExamsDokument11 SeitenControl Systems Questions For GATE, IES, PSU and Other Central and State Competitive Examssrinu247Noch keine Bewertungen

- # Il I, I O': "F::T :#:il$?tr:ffiDokument3 Seiten# Il I, I O': "F::T :#:il$?tr:ffisrinu247Noch keine Bewertungen

- Electrical Circuit Analysis - II 2 Question PapersDokument8 SeitenElectrical Circuit Analysis - II 2 Question Paperssrinu247Noch keine Bewertungen

- Objective Questions On Boolean Algebra SimplificationDokument4 SeitenObjective Questions On Boolean Algebra Simplificationsrinu247Noch keine Bewertungen

- 442 Revised Lab Manual w07Dokument51 Seiten442 Revised Lab Manual w07srinu247Noch keine Bewertungen

- Dual Three-Phase Indirect Matrix Converter With Carrier-Based PWM MethodDokument13 SeitenDual Three-Phase Indirect Matrix Converter With Carrier-Based PWM Methodsrinu247Noch keine Bewertungen

- Basic Electrical LabDokument32 SeitenBasic Electrical Labsrinu247Noch keine Bewertungen

- Eee-Vi-power System Analysis and Stability (10ee61) - NotesDokument119 SeitenEee-Vi-power System Analysis and Stability (10ee61) - Notessrinu24750% (2)

- Applications of Digital Signal ProcessingDokument410 SeitenApplications of Digital Signal ProcessingJoão Claudio..0% (1)

- 13-Chapter 13 - TransistorsDokument28 Seiten13-Chapter 13 - Transistorssrinu247100% (3)

- Bus Bar Protection Scheme 2003Dokument34 SeitenBus Bar Protection Scheme 2003srinu247Noch keine Bewertungen