Beruflich Dokumente

Kultur Dokumente

047ad Compal LA-B211P r1.0 2014

Hochgeladen von

djbessacOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

047ad Compal LA-B211P r1.0 2014

Hochgeladen von

djbessacCopyright:

Verfügbare Formate

A

Model Name : Z5WAL

File Name : LA-B211P

Compal Confidential

2

EA51_BM UMA M/B Schematics Document

Intel Bay Trail M

2014-04-07

REV:1.0

Panelization Information

LA-B211P

Main Board

PWR Board

LS-B161P

USB Board

LS-B162P

BATT Board

LS-B163P

PCB@

ZZZ

PCB Z5WAL LA-B211P LS-B161P/B162P/B163P

Part Number

DAZ15Y00100

Description

PCB Z5WAL LA-B211P LS-B161P/B162P/B163P

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2013/04/12

2014/04/12

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Cover Page

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

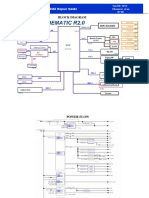

eDP Conn.

HDMI Conn.

204pin DDR3L-SO-DIMM X1

P.13

P.16

P.15

port 0

port 1

Memory BUS

204pin DDR3L-SO-DIMM X1

Dual Channel

P.14

1.35V DDR3L 1066/1333

DDI x2

CRT Conn.

VGA x1

USB2.0 x4

P.17

PCIE II x1

LAN(GbE) / Card Reader

RTL8411B

PCIE II x1

FCBGA 1170 Pin

port 2

USB HUB

GL850G

P.21

USB 3.0

Conn P.21

SOC

P.18,19

port 1

USB3.0 x1

port 0

RJ45 Conn.

VALLEYVIEW-M

port 0

port 3

HD Camera

Conn.

Touch Panel

Conn.

P.15

P.15

HUB port1

MINI CARD

WLAN/BT

port 1

P.19

Card Reader

2 in 1(SD)

SATA II x2

P.20

port 1

HD Audio

P.20

HDA Codec

page 05~12

port 0

LPC BUS

ALC283

P.24

SPI

EC

ENE KB9022

SATA ODD Conn.

RTC CKT.

P.08

Power Circuit DC/DC

P.26~P.34

LED/Power On/Off

P.23

P.23

Universal Jack

P.24

P.24

Int. MIC

P.24

P.08

P.23

Sub Board

Touch Pad

PS2/I2C

LS_B161P PWR

Int.KBD

LS_B162P USB

HUB port2,3

LS_B163P BATT

Fan Control

Speaker

P.22

SATA HDD Conn.

DC/DC Interface CKT.

P.25

SPI ROM

1.8V (8MB)

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

P.20

2013/04/12

2014/04/12

Deciphered Date

Title

Block Diagrams

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

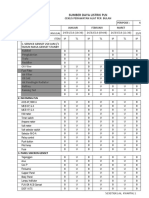

Board ID / SKU ID Table for AD channel

Vcc

Ra/Rc/Re

Board ID

Voltage Rails

Power Plane

1

S0

S3

S4/S5

VIN

19V Adapter power supply

Description

ON

ON

ON

BATT+

12V Battery power supply

ON

ON

ON

B+

AC or battery power rail for power circuit. (19V/12V)

ON

ON

ON

+RTCVCC

RTC Battery Power

ON

ON

ON

+1.0VALW

+1.0v Always power rail

ON

ON

ON

+1.8VALW

+1.8v Always power rail

ON

ON

ON

+3VALW

+3.3v Always power rail

ON

ON

ON

+5VALW

+5.0v Always power rail

ON

ON

ON

+1.35V

+1.35V power rail for DDR3L

ON

ON

OFF

+3V_PTP

+3.3V power rail for PTP

ON

ON

OFF

+SOC_VCC

Core voltage for SOC

ON

OFF

OFF

+SOC_VNN

GFX voltage for SOC

ON

OFF

OFF

+0.675VS

+0.675V power rail for DDR3L Terminator

ON

OFF

OFF

+1.0VS

+1.0v system power rail

ON

OFF

OFF

0

1

2

3

4

5

6

7

8

9

10

11

12

13

3.3V +/- 5%

100K +/- 5%

Rb / Rd / Rf

0

12K +/- 5%

15K +/- 5%

20K +/- 5%

27K +/- 5%

33K +/- 5%

43K +/- 5%

56K +/- 5%

75K +/- 5%

100K +/- 5%

130K +/- 5%

160K +/- 5%

200K +/- 5%

240K +/- 5%

V AD_BID min

0 V

0.347 V

0.423 V

0.541 V

0.691 V

0.807 V

0.978 V

1.169 V

1.398 V

1.634 V

1.849 V

2.015 V

2.185 V

2.316 V

V AD_BID typ

0 V

0.354 V

0.430 V

0.550 V

0.702 V

0.819 V

0.992 V

1.185 V

1.414 V

1.650 V

1.865 V

2.031 V

2.200 V

2.329 V

V AD_BID max

0 V

0.360 V

0.438 V

0.559 V

0.713 V

0.831 V

1.006 V

1.200 V

1.430 V

1.667 V

1.881 V

2.046 V

2.215 V

2.343 V

BOARD ID Table

1

PCB Revision

Board ID

0

1

2

3

4

5

6

EVT

DVT

PVT

Pre-MP

43 level BOM table

+1.05VS

+1.05v system power rail

ON

OFF

OFF

43 Level

+1.35VS

+1.35v system power rail

ON

OFF

OFF

4319SNBOL01

+1.5VS

+1.5v system power rail

ON

OFF

OFF

4319SNBOL02

SMT MB AB211 Z5WAL UMA N2920 HDMI

SMT MB AB211 Z5WAL UMA N3520 HDMI

Description

BOM Structure

+1.8VS

+1.8v system power rail

ON

OFF

OFF

4319SNBOL03

SMT MB AB211 Z5WAL UMA N3530 HDMI

N3520@/9022@/EMC@/PCB@/1DMIC@/NTPM@

N3530@/9022@/EMC@/PCB@/1DMIC@/NTPM@

+3VS

+3.3v system power rail

ON

OFF

OFF

4319SNBOL04

SMT MB AB211 Z5WAL UMA N2930 HDMI

N2930@/9022@/EMC@/PCB@/1DMIC@/NTPM@

+5VS

+5.0v system power rail

ON

OFF

OFF

4319SNBOL05

SMT MB AB211 Z5WAL UMA N2820 HDMI

N2820@/9022@/EMC@/PCB@/1DMIC@/NTPM@

4319SNBOL06

SMT MB AB211 Z5WAL UMA N2830 HDMI

N2830@/9022@/EMC@/PCB@/1DMIC@/NTPM@

N2920@/9022@/EMC@/PCB@/1DMIC@/NTPM@

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

BOM Option Table

2.2K

2.2K

SOC

BH10

PCU_SMB_CLK

BG12

PCU_SMB_DATA

Item

BOM Structure

Unpop

@

Connector

CONN@

EMCrequirement

EMC@

EMCrequirementdepop

@EMC@

KB9012

9012@

KB9022

9022@

TouchScreenI2C

TSI@

KBBL

BL@

DMIC*1

1DMIC@

DMIC*2

2DMIC@

TPM

TPM@

NTPM

NTPM@

DebugSW

DBG@

+1.8VS

BSS138

BSS138

2.2K

2.2K

SCL1

SDA1

77

EC_SMB_CK1

78

EC_SMB_DA1

+3VALW

100 ohm

100 ohm

7

6

BATTERY

CONN

2.2K

2.2K

KBC

SCL2

79

EC_SMB_CK2

SDA2

80

EC_SMB_DA2

2.2K

+3VS

2.2K

BG25

SOC_I2C2_DATA

BJ25

SOC_I2C2_CLK

2.2K

+1.8VS

2.2K

BSS138

200

202

DIMMA

SOC

SMBUS Address [A0h]

2.2K

BH28

BG28

200

202

DIMMB

32

WLAN

SMBUS Address [TBD]

2013/04/12

SOC_I2C5_CLK

Touch Panel

I2C5_SCL_PNL

BSS138

Compal Electronics, Inc.

2014/04/12

Deciphered Date

Title

Notes List

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

+TS_PWR

BSS138

Date:

2.2K

I2C5_SDA_PNL

Compal Secret Data

Security Classification

Issued Date

2.2K

+1.8VS

SOC_I2C5_DATA

SMBUS Address [A2h]

30

Touch Pad

I2C2_SCL_TP

BSS138

2.2K

KB9022

+3V_PTP

I2C2_SDA_TP

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

12000mA

VR_ON

SPOK

ISL95833HRTZ-T

(PU801)

14000mA

SY8208DQNC

(PU601)

325mA

RT8207MZQW

(PU501)

5250mA

+SOC_VNN

+SOC_VCC

+1.0VALWP

SUSP

ME4856-G

(U60)

2750mA

+1.0VS

ADAPTER

SYSON

SUSP#

+1.35VP

SUSP#

TPS22966DPUR

(U59)

420mA

SUSP#

SY8003DFC_DFN8

(PU602)

958mA

SUSP#

APL5930KAI-TRG

(PU701)

1000mA

SPOK

APL5930KAI-TRG

(PU702)

110mA

CHARGER

B+

EC_ON

SY8208BQNC

(PU401)

+3VALWP

BATTERY

+0.675VSP

SUSP#

+1.35VS

2

TPS22966DPUR

(U11)

+1.5VSP

+1.05VSP

TPS22966DPUR

(U59)

+1.8VALWP

JP8

+3VS

+3VS_WLAN

ENVDD

LAN_PWR_EN

G5243AT11U

(U67)

+1.8VS

G5243AT11U

(U8)

+LCDVDD

+3V_LAN

EC_ON

SY8208BQNC

(PU402)

SUSP#

+5VALWP

TPS22966DPUR

(U11)

958mA

+5VS

J1

+VDDA

0 ohm

0 ohm

USB_PWR_EN#

SY6288D10CAC

(U25)

+5VS_HDD

+5VS_ODD

+USB3_VCCA

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2013/04/12

2014/04/12

Deciphered Date

Title

Power Rail

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

DDR_A_D[0..63]

<13>

DDR_A_DQS[0..7]

DDR_A_DQS#[0..7]

DDR_B_D[0..63]

<13>

DDR_B_DQS[0..7]

<13>

DDR_B_DQS#[0..7]

USOC1A

<13>

DDR_A_MA[0..15]

<13>

DDR_A_DM[0..7]

<13>

<13>

<13>

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

<13>

<13>

<13>

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

<13>

DDR_A_CS0#

<13>

DDR_A_CS2#

<13>

DDR_A_CKE0

<13>

DDR_A_CKE2

<13>

DDR_A_ODT0

<13>

DDR_A_ODT2

<13>

<13>

DDR_A_CLK0

DDR_A_CLK0#

<13>

<13>

DDR_A_CLK2

DDR_A_CLK2#

<13>

DDR_A_RST#

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

K45

H47

L41

H44

H50

G53

H49

D50

G52

E52

K48

E51

F47

J51

B49

B50

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

G36

B36

F38

B42

P51

V42

Y50

Y52

M45

M44

H51

K47

K44

D52

P44

P45

C47

D48

F44

E46

T41

P42

M50

M48

P50

P48

P41

AF44

+DDR_SOC_VREF

100K_0402_5% 1

100K_0402_5% 1

2 R960

2 R961

DDR_TERMN0

DDR_TERMN1

AF42

AH42

AD42

AB42

DDR_PWROK

DDR_CORE_PWROK

23.2_0402_1% 1

29.4_0402_1% 1

162_0402_1% 1

2 R962

2 R963

2 R964

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

Follow CRB v2.0

AD44

AF45

AD45

AF40

AF41

AD40

AD41

2

1 DDR_CORE_PWROK

EMC@

C1159

0.047U_0402_25V7K

<14>

<14>

<14>

USOC1B

DRAM0_MA_0

DRAM0_MA_1

DRAM0_MA_2

DRAM0_MA_3

DRAM0_MA_4

DRAM0_MA_5

DRAM0_MA_6

DRAM0_MA_7

DRAM0_MA_8

DRAM0_MA_9

DRAM0_MA_10

DRAM0_MA_11

DRAM0_MA_12

DRAM0_MA_13

DRAM0_MA_14

DRAM0_MA_15

DRAM0_DQ_0

DRAM0_DQ_1

DRAM0_DQ_2

DRAM0_DQ_3

DRAM0_DQ_4

DRAM0_DQ_5

DRAM0_DQ_6

DRAM0_DQ_7

DRAM0_DQ_8

DRAM0_DQ_9

DRAM0_DQ_10

DRAM0_DQ_11

DRAM0_DQ_12

DRAM0_DQ_13

DRAM0_DQ_14

DRAM0_DQ_15

DRAM0_DQ_16

DRAM0_DQ_17

DRAM0_DQ_18

DRAM0_DQ_19

DRAM0_DQ_20

DRAM0_DQ_21

DRAM0_DQ_22

DRAM0_DQ_23

DRAM0_DQ_24

DRAM0_DQ_25

DRAM0_DQ_26

DRAM0_DQ_27

DRAM0_DQ_28

DRAM0_DQ_29

DRAM0_DQ_30

DRAM0_DQ_31

DRAM0_DQ_32

DRAM0_DQ_33

DRAM0_DQ_34

DRAM0_DQ_35

DRAM0_DQ_36

DRAM0_DQ_37

DRAM0_DQ_38

DRAM0_DQ_39

DRAM0_DQ_40

DRAM0_DQ_41

DRAM0_DQ_42

DRAM0_DQ_43

DRAM0_DQ_44

DRAM0_DQ_45

DRAM0_DQ_46

DRAM0_DQ_47

DRAM0_DQ_48

DRAM0_DQ_49

DRAM0_DQ_50

DRAM0_DQ_51

DRAM0_DQ_52

DRAM0_DQ_53

DRAM0_DQ_54

DRAM0_DQ_55

DRAM0_DQ_56

DRAM0_DQ_57

DRAM0_DQ_58

DRAM0_DQ_59

DRAM0_DQ_60

DRAM0_DQ_61

DRAM0_DQ_62

DRAM0_DQ_63

DRAM0_DM_0

DRAM0_DM_1

DRAM0_DM_2

DRAM0_DM_3

DRAM0_DM_4

DRAM0_DM_5

DRAM0_DM_6

DRAM0_DM_7

DRAM0_RAS#

DRAM0_CAS#

DRAM0_WE#

DRAM0_BS_0

DRAM0_BS_1

DRAM0_BS_2

DRAM0_CS_0#

DRAM0_CS_2#

DRAM0_CKE_0

RESERVED_D48

DRAM0_CKE_2

RESERVED_E46

DRAM0_ODT_0

DRAM0_ODT_2

DRAM0_CKP_0

DRAM0_CKN_0

DRAM0_CKP_2

DRAM0_CKN_2

DRAM0_DRAMRST#

0.675V

DRAM_VREF

ICLK_DRAM_TERMN_AF42

ICLK_DRAM_TERMN_AH42

DRAM0_DQSP_0

DRAM0_DQSN_0

DRAM0_DQSP_1

DRAM0_DQSN_1

DRAM0_DQSP_2

DRAM0_DQSN_2

DRAM0_DQSP_3

DRAM0_DQSN_3

DRAM0_DQSP_4

DRAM0_DQSN_4

DRAM0_DQSP_5

DRAM0_DQSN_5

DRAM0_DQSP_6

DRAM0_DQSN_6

DRAM0_DQSP_7

DRAM0_DQSN_7

<30>

<8>

DRAM_VDD_S4_PWROK

DRAM_CORE_PWROK

DRAM_RCOMP_0

DRAM_RCOMP_1

DRAM_RCOMP_2

RESERVED_AF40

RESERVED_AF41

RESERVED_AD40

RESERVED_AD41

M36

J36

P40

M40

P36

N36

K40

K42

B32

C32

C36

A37

C33

A33

C37

B38

F36

G38

F42

J42

G40

C38

G44

D42

A41

C41

A45

B46

C40

B40

B48

B47

K52

K51

T52

T51

L51

L53

R51

R53

T47

T45

Y40

V41

T48

T50

Y42

AB40

V45

V47

AD48

AD50

V48

V50

AB44

Y45

V52

W51

AC53

AC51

W53

Y51

AD52

AD51

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

J38

K38

C35

B34

D40

F40

B44

C43

N53

M52

T42

T44

Y47

Y48

AB52

AA51

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

<14>

<14>

DDR_B_MA[0..15]

AY45

DDR_B_MA0

BB47

DDR_B_MA1

DDR_B_MA2 AW41

BB44

DDR_B_MA3

BB50

DDR_B_MA4

BC53

DDR_B_MA5

BB49

DDR_B_MA6

BF50

DDR_B_MA7

BC52

DDR_B_MA8

BE52

DDR_B_MA9

AY48

DDR_B_MA10

DDR_B_MA11 BE51

DDR_B_MA12 BD47

DDR_B_MA13 BA51

DDR_B_MA14 BH49

DDR_B_MA15 BH50

DDR_B_DM[0..7]

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

AV45

AV44

BB51

<14> DDR_B_RAS#

<14> DDR_B_CAS#

<14> DDR_B_WE#

<14>

<14>

<14>

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

<14>

DDR_B_CS0#

<14>

DDR_B_CS2#

<14>

DDR_B_CKE0

<14>

DDR_B_CKE2

AY47

AY44

BF52

AT44

AT45

BG47

BE46

BD44

BF48

<14>

DDR_B_ODT0

<14>

DDR_B_ODT2

AP41

AT42

AV50

AV48

<14> DDR_B_CLK0

<14> DDR_B_CLK0#

AT50

AT48

<14> DDR_B_CLK2

<14> DDR_B_CLK2#

<14>

BD38

BH36

BC36

BH42

AT51

AM42

AK50

AK52

AT41

DDR_B_RST#

DRAM1_MA_0

DRAM1_MA_1

DRAM1_MA_2

DRAM1_MA_3

DRAM1_MA_4

DRAM1_MA_5

DRAM1_MA_6

DRAM1_MA_7

DRAM1_MA_8

DRAM1_MA_9

DRAM1_MA_10

DRAM1_MA_11

DRAM1_MA_12

DRAM1_MA_13

DRAM1_MA_14

DRAM1_MA_15

DRAM1_DM_0

DRAM1_DM_1

DRAM1_DM_2

DRAM1_DM_3

DRAM1_DM_4

DRAM1_DM_5

DRAM1_DM_6

DRAM1_DM_7

DRAM1_RAS#

DRAM1_CAS#

DRAM1_WE#

DRAM1_BS_0

DRAM1_BS_1

DRAM1_BS_2

DRAM1_CS_0#

DRAM1_CS_2#

DRAM1_CKE_0

RESERVED_BE46

DRAM1_CKE_2

RESERVED_BF48

DRAM1_ODT_0

DRAM1_ODT_2

DRAM1_CKP_0

DRAM1_CKN_0

DRAM1_CKP_2

DRAM1_CKN_2

DRAM1_DRAMRST#

DRAM1_DQSP_0

DRAM1_DQSN_0

DRAM1_DQSP_1

DRAM1_DQSN_1

DRAM1_DQSP_2

DRAM1_DQSN_2

DRAM1_DQSP_3

DRAM1_DQSN_3

DRAM1_DQSP_4

DRAM1_DQSN_4

DRAM1_DQSP_5

DRAM1_DQSN_5

DRAM1_DQSP_6

DRAM1_DQSN_6

DRAM1_DQSP_7

DRAM1_DQSN_7

1 OF 13

FH8065301546401_FCBGA131170

B0@

DRAM1_DQ_0

DRAM1_DQ_1

DRAM1_DQ_2

DRAM1_DQ_3

DRAM1_DQ_4

DRAM1_DQ_5

DRAM1_DQ_6

DRAM1_DQ_7

DRAM1_DQ_8

DRAM1_DQ_9

DRAM1_DQ_10

DRAM1_DQ_11

DRAM1_DQ_12

DRAM1_DQ_13

DRAM1_DQ_14

DRAM1_DQ_15

DRAM1_DQ_16

DRAM1_DQ_17

DRAM1_DQ_18

DRAM1_DQ_19

DRAM1_DQ_20

DRAM1_DQ_21

DRAM1_DQ_22

DRAM1_DQ_23

DRAM1_DQ_24

DRAM1_DQ_25

DRAM1_DQ_26

DRAM1_DQ_27

DRAM1_DQ_28

DRAM1_DQ_29

DRAM1_DQ_30

DRAM1_DQ_31

DRAM1_DQ_32

DRAM1_DQ_33

DRAM1_DQ_34

DRAM1_DQ_35

DRAM1_DQ_36

DRAM1_DQ_37

DRAM1_DQ_38

DRAM1_DQ_39

DRAM1_DQ_40

DRAM1_DQ_41

DRAM1_DQ_42

DRAM1_DQ_43

DRAM1_DQ_44

DRAM1_DQ_45

DRAM1_DQ_46

DRAM1_DQ_47

DRAM1_DQ_48

DRAM1_DQ_49

DRAM1_DQ_50

DRAM1_DQ_51

DRAM1_DQ_52

DRAM1_DQ_53

DRAM1_DQ_54

DRAM1_DQ_55

DRAM1_DQ_56

DRAM1_DQ_57

DRAM1_DQ_58

DRAM1_DQ_59

DRAM1_DQ_60

DRAM1_DQ_61

DRAM1_DQ_62

DRAM1_DQ_63

BG38

BC40

BA42

BD42

BC38

BD36

BF42

BC44

BH32

BG32

BG36

BJ37

BG33

BJ33

BG37

BH38

AU36

AT36

AV40

AT40

BA36

AV36

AY42

AY40

BJ41

BG41

BJ45

BH46

BG40

BH40

BH48

BH47

AY52

AY51

AP52

AP51

AW51

AW53

AR51

AR53

AP47

AP45

AK40

AM41

AP48

AP50

AK42

AH40

AM45

AM47

AF48

AF50

AM48

AM50

AH44

AK45

AM52

AL51

AG53

AG51

AL53

AK51

AF52

AF51

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

BF40

BD40

BG35

BH34

BA38

AY38

BH44

BG43

AU53

AV52

AP42

AP44

AK47

AK48

AH52

AJ51

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

2 OF 13

FH8065301546401_FCBGA131170

B0@

Close To SOC Pin

+1.35V_L

+DDR_SOC_VREF

1

2

R965

4.7K_0402_1%

2

R966

4.7K_0402_1%

C1132

.1U_0402_16V7K

USOC1

N2830@

USOC1

N2930@

USOC1

N3530@

Issued Date

S IC FH8065301729601 SR1UX C0 2.17G ABO!

SA00007QR70

S IC FH8065301729501 SR1UW C0 1.83G ABO!

SA00007RV50

S IC FH8065301728500 SR1UV C0 2.17G ABO!

SA00007QQ50

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2013/04/12

2014/04/12

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

VLV-M SOC Memory DDR3L

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

USOC1C

C26

C28

B28

C27

B26

1 R968

2 DDI0_RCOMPP

402_0402_1% DDI0_RCOMPN

Follow CRB v2.0 0ohm till to GND

AK12

AK13

AM14

AM13

AM3

AM2

DDI1_AUXP

DDI1_AUXN

DDI0_HPD

1.8V

1.8V

DDI1_HPD

DDI0_DDCDATA

DDI0_DDCCLK

1.8V

1.8V

1.8V

1.8V

DDI1_DDCDATA

DDI1_DDCCLK

1.8V

1.8V

1.8V

DDI1_VDDEN

DDI1_BKLTEN

DDI1_BKLTCTL

DDI0_VDDEN

DDI0_BKLTEN

DDI0_BKLTCTL

VSS_AH3

VSS_AH2

DDI0_RCOMP_P

DDI0_RCOMP_N

RESERVED_AM14

RESERVED_AM13

VSS_AM3

VSS_AM2

RESERVED_AH14

RESERVED_AH13

RESERVED_AF14

RESERVED_AF13

VGA_RED

VGA_BLUE

VGA_GREEN

VGA_IREF

VGA_IRTN

+1.8VS

@

R970

10K_0402_5%

T186

GPIO_NC12

RESERVED_T2

RESERVED_T3

RESERVED_AB3

RESERVED_AB2

RESERVED_Y3

RESERVED_Y2

RESERVED_W3

RESERVED_W1

RESERVED_V2

RESERVED_V3

RESERVED_R3

RESERVED_R1

RESERVED_AD6

RESERVED_AD4

RESERVED_AB9

RESERVED_AB7

RESERVED_Y4

RESERVED_Y6

RESERVED_V4

RESERVED_V6

GPIO_S0_NC_13

GPIO_S0_NC14

RESERVED_AB14

GPIO_S0_NC_12

RESERVED_C30

VGA_HSYNC

VGA_VSYNC

3.3V

3.3V

VGA_DDCCLK

VGA_DDCDATA

RESERVED_T7

RESERVED_T9

RESERVED_AB13

RESERVED_AB12

RESERVED_Y12

RESERVED_Y13

RESERVED_V10

RESERVED_V9

RESERVED_T12

RESERVED_T10

RESERVED_V14

RESERVED_V13

RESERVED_T14

RESERVED_T13

RESERVED_T6

RESERVED_T4

RESERVED_P14

GPIO_S0_NC_15

GPIO_S0_NC_16

GPIO_S0_NC_17

GPIO_S0_NC_18

GPIO_S0_NC_19

GPIO_S0_NC_20

GPIO_S0_NC_21

GPIO_S0_NC_22

GPIO_S0_NC_23

GPIO_S0_NC_24

GPIO_S0_NC_25

GPIO_S0_NC_26

@

T187

R971

10K_0402_5%

GPIO_NC13

GPIO_NC14

T2

T3

AB3

AB2

Y3

Y2

W3

W1

V2

V3

R3

R1

AD6

AD4

AB9

AB7

Y4

Y6

V4

V6

A29

C29

AB14

B30

C30

3.3V

3.3V

Follow CRB v2.0

3 OF 10

AG3

AG1

AF3

AF2

AD3

AD2

AC3

AC1

EDP_TXP0 <15>

EDP_TXN0 <15>

EDP_TXP1 <15>

EDP_TXN1 <15>

eDP Panel

AK3

AK2

K30

P30 DDI1_ENABLE R967 1

G30

EDP_AUXP

EDP_AUXN

<15>

<15>

EDP_HPD#

<15>

2 2.2K_0402_5% +1.8VS

N30 DDI1_ENVDD

J30 DDI1_ENBKL

M30 DDI1_PWM

AH3

AH2

Follow CRB v2.0 0ohm till to GND

AH14

AH13

AF14

AF13

BA3

AY2

BA1

AW1

AY3

CRT_R

CRT_B

CRT_G

CRT_IREF 1

R969

CRT_R

CRT_B

CRT_G

2

357_0402_1%

BD2 CRT_HSYNC

BF2 CRT_VSYNC

CRT_HSYNC

CRT_VSYNC

BC1 CRT_DDC_CLK

BC2 CRT_DDC_DATA

T7

T9

AB13

AB12

Y12

Y13

V10

V9

T12

T10

V14

V13

T14

T13

T6

T4

P14

F34

M32

D28

J28

K34

D34

F32

F28

K28

J34

N32

D32

<17>

<17>

CRT

CRT_DDC_CLK <17>

CRT_DDC_DATA <17>

CRT

8

7

6

5

CRT_R

CRT_G

CRT_B

RP43

150_0804_8P4R_1%

1

2

3

4

+1.8VS

eDP

1

DDI1_ENBKL

U61

NC

ENBKL

<22>

+3VS

NL17SZ07DFT2G_SC70-5

SA00004BV00

9012@

R1142 1

1 9012@ 2

ENBKL

4.7K_0402_5%

R1159

RS@ 2 0_0402_5%

+1.8VS

FH8065301546401_FCBGA131170

B0@

GPIO_S0_NC[13]:

Multiplexed with Hardware

<17>

<17>

<17>

HDMI_DDCDATA

HDMI_DDCCLK

1.0V

1.0V

DDI0_AUXP

DDI0_AUXN

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXP_3

DDI1_TXN_3

HDMI_HPD#

<16>

<16>

1.0V

D27

<16>

1.0V

AL3

AL1

DDI0_TXP_0

DDI0_TXN_0

DDI0_TXP_1

DDI0_TXN_1

DDI0_TXP_2

DDI0_TXN_2

DDI0_TXP_3

DDI0_TXN_3

Straps Pin:MDSI_DDCDATA

Y

A

ENVDD

<15>

RP45

2013/04/12

INVT_PWM_SOC

NL17SZ07DFT2G_SC70-5

SA00004BV00

Compal Electronics, Inc.

2014/04/12

Deciphered Date

Title

Date:

1

2

3

4

100K_0804_8P4R_5%

<15>

VLV-M SOC Display

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

8

7

6

5

P

Y

Compal Secret Data

Security Classification

Issued Date

U64

NC

DDI1_ENBKL

DDI1_ENVDD

DDI1_PWM

1

DDI1_PWM

NL17SZ07DFT2G_SC70-5

SA00004BV00

+1.8VS

INVT_PWM_SOC 1

4.7K_0402_5%

R1161

U62

NC

DDI1_ENVDD 2

1

ENVDD

4.7K_0402_5%

R1160

HDMI

AV3

AV2

AT2

AT3

AR3

AR1

AP3

AP2

HDMI_TX2+

HDMI_TX2HDMI_TX1+

HDMI_TX1HDMI_TX0+

HDMI_TX0HDMI_CLK+

HDMI_CLK-

<16>

<16>

<16>

<16>

<16>

<16>

<16>

<16>

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

USOC1D

HDD

ODD

<20>

<20>

SATA_PTX_DRX_P0

SATA_PTX_DRX_N0

<20>

<20>

SATA_PRX_DTX_P0

SATA_PRX_DTX_N0

<20>

<20>

SATA_PTX_DRX_P1

SATA_PTX_DRX_N1

<20>

<20>

SATA_PRX_DTX_P1

SATA_PRX_DTX_N1

BF6

BG7

AU16

AV16

BD10

BF10

AY16

BA16

Follow CRB V2.0 0ohm till to GND

<8>

SOC_SCI#

@ T188

SOC_SCI#

DEVSLP_SOC

1 R972

2 SATA_RCOMPP

402_0402_1% SATA_RCOMPN

BB10

BC10

BA12

AY14

AY12

AU18

AT18

AT22

AV20

AU22

AV22

AT20

AY24

AU26

AT26

AU20

AV26

BA24

AY18

BA18

AY20

BD20

BA20

BD18

BC18

AY26

AT28

BD26

AU28

BA26

BC24

AV28

BF22

BD22

BF26

SATA_TXP_0

SATA_TXN_0

PCIE_TXP_0

PCIE_TXN_0

SATA_RXP_0

SATA_RXN_0

PCIE_RXP_0

PCIE_RXN_0

SATA_TXP_1

SATA_TXN_1

PCIE_TXP_1

PCIE_TXN_1

SATA_RXP_1

SATA_RXN_1

PCIE_RXP_1

PCIE_RXN_1

VSS_BB10

VSS_BC10

PCIE_TXP_2

PCIE_TXN_2

SATA_GP0 / GPIO_S0_SC_0

SATA_GP1 / SATA_DEVSLP_0 / GPIO_S0_SC_1

SATA_LED# / GPIO_S0_SC_2

PCIE_RXP_2

PCIE_RXN_2

PCIE_TXP_3

PCIE_TXN_3

SATA_RCOMP_P

SATA_RCOMP_N

PCIE_RXP_3

PCIE_RXN_3

MMC1_CLK / GPIO_S0_SC_16

VSS_BB7

VSS_BB5

MMC1_D0 / GPIO_S0_SC_17

MMC1_D1 / GPIO_S0_SC_18

MMC1_D2 / GPIO_S0_SC_19

MMC1_D3 / GPIO_S0_SC_20

MMC1_D4 / GPIO_S0_SC_21

MMC1_D5 / GPIO_S0_SC_22

MMC1_D6 / GPIO_S0_SC_23

MMC1_D7 / GPIO_S0_SC_24

PCIE_CLKREQ_0# / GPIO_S0_SC_3

PCIE_CLKREQ_1# / GPIO_S0_SC_4

PCIE_CLKREQ_2# / GPIO_S0_SC_5

PCIE_CLKREQ_3# / GPIO_S0_SC_6

SD3_WP / GPIO_S0_SC_7

MMC1_CMD / GPIO_S0_SC_25

MMC1_RST# / SATA_DEVSLP_0 / GPIO_S0_SC_26

PCIE_RCOMP_P

PCIE_RCOMP_N

RESERVED_BB4

RESERVED_BB3

MMC1_RCOMP

SD2_CLK / GPIO_S0_SC_27

SD2_D0 / GPIO_S0_SC_28

SD2_D1 / GPIO_S0_SC_29

SD2_D2 / GPIO_S0_SC_30

SD2_D3_CD# / GPIO_S0_SC_31

SD2_CMD / GPIO_S0_SC_32

RESERVED_AV10

RESERVED_AV9

HDA_LPE_RCOMP

HDA_RST# / LPE_I2S0_CLK / GPIO_S0_SC_8

HDA_SYNC / LPE_I2S0_FRM / GPIO_S0_SC_9

HDA_CLK / LPE_I2S0_DATAOUT / GPIO_S0_SC_10

HDA_SDO / LPE_I2S0_DATAIN / GPIO_S0_SC_11

HDA_SDI0 / LPE_I2S1_CLK / GPIO_S0_SC_12

HDA_SDI1 / LPE_I2S1_FRM / GPIO_S0_SC_13

SD3_CLK / GPIO_S0_SC_33 HDA_DOCKRST# / LPE_I2S1_DATAOUT / GPIO_S0_SC_14

SD3_D0 / GPIO_S0_SC_34

HDA_DOCKEN# / LPE_I2S1_DATAIN / GPIO_S0_SC_15

SD3_D1 / GPIO_S0_SC_35

SD3_D2 / GPIO_S0_SC_36

LPE_I2S2_CLK / SATA_DEVSLP_1 / GPIO_S0_SC_62

SD3_D3 / GPIO_S0_SC_37

LPE_I2S2_FRM / GPIO_S0_SC_63

SD3_CD# / GPIO_S0_SC_38

LPE_I2S2_DATAIN / GPIO_S0_SC_64

SD3_CMD / GPIO_S0_SC_39

LPE_I2S2_DATAOUT / GPIO_S0_SC_65

SD3_1P8EN / GPIO_S0_SC_40

SD3_PWREN# / GPIO_S0_SC_41

RESERVED_P34

RESERVED_N34

SD3_RCOMP

RESERVED_AK9

RESERVED_AK7

4 OF 10

PROCHOT#

AY7 PCIE_PTX_DRX_P0

AY6 PCIE_PTX_DRX_N0

.1U_0402_16V7K 1

.1U_0402_16V7K 1

2 C1133

2 C1134

AT14 PCIE_PRX_DTX_P0

AT13 PCIE_PRX_DTX_N0

PCIE_PTX_C_DRX_P0

PCIE_PTX_C_DRX_N0

PCIE_PRX_DTX_P0

PCIE_PRX_DTX_N0

AV6 PCIE_PTX_DRX_P1

AV4 PCIE_PTX_DRX_N1

.1U_0402_16V7K 1

.1U_0402_16V7K 1

2 C1135

2 C1000

AT10 PCIE_PRX_DTX_P1

AT9 PCIE_PRX_DTX_N1

PCIE_PTX_C_DRX_P1

PCIE_PTX_C_DRX_N1

PCIE_PRX_DTX_P1

PCIE_PRX_DTX_N1

<18>

<18>

PCIE LAN

<18>

<18>

<19>

<19>

WLAN

<19>

<19>

AT7

AT6

AP12

AP10

AP6

AP4

+1.8VS

AP9

AP7

RP51

BB7

BB5

BG3

BD7

BG5

BE3

BD5

LAN_CLKREQ#

WLAN_CLKREQ#

PCIE_CLKREQ_2#

PCIE_CLKREQ_3#

AP14

AP13

PCIE_RCOMPP

PCIE_RCOMPN

1

2

3

4

LAN_CLKREQ#

WLAN_CLKREQ#

PCIE_CLKREQ_2#

PCIE_CLKREQ_3#

Follow CRB V2.0 0ohm till to GND

LAN_CLKREQ# <18>

WLAN_CLKREQ# <19>

8

7

6

5

10K_0804_8P4R_5%

RP46

8

7

6

5

HDA_SYNC

HDA_SDOUT

HDA_BIT_CLK

HDA_RST#

1 R975

2

402_0402_1%

BB4

BB3

1

2

3

4

HDA_SYNC_AUDIO

<24>

HDA_SDOUT_AUDIO <24>

HDA_BITCLK_AUDIO <24>

HDA_RST_AUDIO# <24>

33_0804_8P4R_5%

EMC@

AV10

AV9

HDA_RCOMP

BF20

BG22

BH20

BJ21

BG20

BG19

BG21

BH18

BG18

BF28

BA30

BD28

BC30

HDA_RCOMP

HDA_RST#

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0

2

1

49.9_0402_1%

2 22P_0402_50V8J

@EMC@

@

T189

@

T190

@

T191

HDA_SDIN0

<24>

Follow CRB v2.0

GPIO_S0_SC_65

P34

N34

R979

73.2_0402_1%

1

2

AK9

AK7

C24

+1.8VS

GPIO_S0_SC_63 R977 2

1 10K_0402_5%

+1.0VS

H_PROCHOT#

Internal PD 2K

GPIO_S0_SC_63:

BIOSBootSelection

0=LPC

1=SPI

GPIO_S0_SC_63

FH8065301546401_FCBGA131170

B0@

R976 1

HDA_BITCLK_AUDIOC1001

<22>

GPIO_S0_SC_65:

SecurityFlashDescriptors

0=Override

1=NormalOperation(InternalPU)

@EMC@

C1002

10P_0402_50V8J

+1.8VS

R978

10K_0402_5%

GPIO_S0_SC_65

EC programing :

"High"for Flash BIOS

D

A

Issued Date

2013/04/12

2014/04/12

Deciphered Date

Title

VLV-M SOC SATA/PCI-E/HDA

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

<22>

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2

TXE_DBG

G

Q62

MESS138W-G_SOT323-3

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

+3VS

3

GND

GND

XTAL_25M_OUT

R984 1

R985 1

ICLK_ICOMP

ICLK_RCOMP

AD10

AD12

C1004

10P_0402_50V8J

2 4.02K_0402_1% ICLK_ICOMP

2 47.5_0402_1% ICLK_RCOMP

RESERVED_AD9

AD14

AD13

ICLK_ICOMP

ICLK_RCOMP

LAN

<18>

<18>

CLK_PCIE_LAN#

CLK_PCIE_LAN

WLAN

<19>

<19>

CLK_PCIE_WLAN#

CLK_PCIE_WLAN

PCIE_CLKN_0

PCIE_CLKP_0

AF9

AF7

PCIE_CLKN_2

PCIE_CLKP_2

AM4

AM6

R989 1

R1026 1

R1024 1

5

6

7

8

XDP_H_TDI

XDP_H_TMS

XDP_H_TCK

XDP_H_TRST#

XDP_H_TCK

XDP_H_TRST#

XDP_H_TMS

XDP_H_TDI

XDP_H_TDO

XDP_H_PRDY#

XDP_H_PREQ_BUF#

51_0804_8P4R_5%

C

@ T193

@T193

SOC_SPI_MISO

SOC_SPI_MOSI

SOC_SPI_CLK

<15> TS_INT_R#

<23> TP_INT#

D14

G12

F14

F12

G16

D18

F16

AT34

SOC_LID_OUT#

SOC_SMI#

PMC_ACIN

D40

2.2K_0402_5%

+1.8VALW

1 RB751V40_SC76-2

ACIN

D26

G24

F18

F22

D22

J20

D20

F26

K26

J26

BG9

F20

J24

G18

SVID_ALERT#

SVID_DATA

SVID_CLK

SIO_PWM_0 / GPIO_S0_SC_94

SIO_PWM_1 / GPIO_S0_SC_95

GPIO_S5_22

GPIO_S5_23

GPIO_S5_24

GPIO_S5_25

GPIO_S5_26

GPIO_S5_27

GPIO_S5_28

GPIO_S5_29

GPIO_S5_30

GPIO_S5_8

GPIO_S5_9

GPIO_S5_10

<18,19,22,23>

NL17SZ07DFT2G_SC70-5

SA00004BV00

PLT_RST#Buffer

+1.8VALW

T192@ 32.768k

PMC_SUSCLK

PMC_SLP_S4#

PMC_SLP_S3#

GPIO_S5_14

PMC_ACIN

PMC_PCIE_WAKE#

PMC_BATLOW#

PMC_PWRBTN#

PMC_RSTBTN#

PMC_PLTRST#

GPIO_S5_17

PMC_SUS_STAT#

output

RP47

1

2

3

4

PMC_PCIE_WAKE#

PMC_BATLOW#

GPIO_S5_14

LS_OE

T209@

PMC_CORE_PWROK EMC@

C1007 1

2 0.047U_0402_25V7K

DDR_CORE_PWROK EMC@

C1158 1

2 0.01U_0402_16V7K

C1006 1

2 .1U_0402_16V7K

T205@

T207@

C11 RTC_TEST#

C12 RTC_RST#

B10

B7

EC_RSMRST#

PMC_CORE_PWROK

C9

A9

B8

P22

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

8

7

6

5

10K_0804_8P4R_5%

PMC_PLTRST#

EC_RSMRST#

EMC@

R990 1

<22>

2 100K_0402_5%

C1155 1

EMC@

1

2

C1008

.1U_0402_16V7K

+RTCVCC

B24 VR_SVID_ALERT#_SOC R1065 1

A25 VR_SVID_DATA_SOC

R1066 1

C25

2 .1U_0402_16V7K

RP55

1

PMC_SLP_S4# 2

SOC_KBRST# 3

SOC_LID_OUT#4

R1064

73.2_0402_1%

2 20_0402_1%

2 16.9_0402_1%

VR_SVID_ALERT# <33>

VR_SVID_DATA <33>

VR_SVID_CLK <33>

K24

N24

M20

J18

M18

K18

K20

M22

M24

SIO_SPI_CS# / GPIO_S0_SC_66

SIO_SPI_MISO / GPIO_S0_SC_67

SIO_SPI_MOSI / GPIO_S0_SC_68

SIO_SPI_CLK / GPIO_S0_SC_69

8

7

6

5

0_0804_8P4R_5%

9022@

+3VALW_EC

9012@

19

VCCA

VCCB

+1.8VALW

1

2

R994

10M_0402_5%

EC_SLP_S4#

EC_KBRST#

EC_LID_OUT#

0_0804_8P4R_5%

9022@

RP56

8

7 EC_SMI#

6 EC_SCI#

5 PBTN_OUT#

1

2

SOC_SMI#

3

SOC_SCI#

PMC_PWRBTN# 4

AU32

AT32

U54

2

PMC_SLP_S3#

PMC_SLP_S4#

SOC_KBRST#

SOC_LID_OUT#

SOC_SERIRQ

SOC_SMI#

SOC_SCI#

PMC_PWRBTN#

32.768KHZ_12.5PF_Q13FC135000040

2

Y8 1

1

5 OF 13

3.3V

PLT_RST_BUF#

1

2

C1174

@EMC@

0.01U_0402_16V7K

PLT_RST_BUF#

ILB_RTC_X1

ILB_RTC_X2

GPIO_RCOMP

<22,28>

BF34

BD34

BD32

BF32

PMC_PLTRST# 2

R983 2

+1.0VS

RTC domain

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

RTC_VCC_P22

PMC_RSMRST#

PMC_CORE_PWROK

GPIO_S5_0

GPIO_S5_1 / PMC_WAKE_PCIE_1

GPIO_S5_2 / PMC_WAKE_PCIE_2

GPIO_S5_3 / PMC_WAKE_PCIE_3

GPIO_S5_4

GPIO_S5_5 / PMU_SUSCLK_1

GPIO_S5_6 / PMU_SUSCLK_2

GPIO_S5_7 / PMU_SUSCLK_3

N26

AU34

AV34

BA34

AY34

EC_RSMRST#

PCU_SPI_CS_0#

PCU_SPI_CS_1# / GPIO_S5_21

PCU_SPI_MISO

PCU_SPI_MOSI

PCU_SPI_CLK

C13

A13

C19

GPIO_RCOMP

ILB_RTC_TEST#

ILB_RTC_RST#

TAP_TCK

TAP_TRST#

TAP_TMS

TAP_TDI

TAP_TDO

TAP_PRDY#

TAP_PREQ#

RESERVED_AT34

B18

B16

C18

A17

C17

C16

B14

C15

SOC_KBRST#

TS_INT#_CPU

TP_INT#_CPU

2 R1016

2 R1015

PMC_PLT_CLK_0 / GPIO_S0_SC_96

PMC_PLT_CLK_1 / GPIO_S0_SC_97

PMC_PLT_CLK_2 / GPIO_S0_SC_98

PMC_PLT_CLK_3 / GPIO_S0_SC_99

PMC_PLT_CLK_4 / GPIO_S0_SC_100

PMC_PLT_CLK_5 / GPIO_S0_SC_101

C23

C21

B22

A21

C22

SOC_SPI_CS0#

0_0402_5%1 TSI@

0_0402_5%1 RS@

RESERVED_AM9

RESERVED_AM10

BH7

BH5

BH4

BH8

BH6

BJ9

RP52

4

3

2

1

PCIE_CLKN_3

PCIE_CLKP_3

AM9

AM10

2 51_0402_5% XDP_H_PRDY#

2 51_0402_5% XDP_H_TDO

2 200_0402_5% XDP_H_PREQ_BUF#

PMC_SUSPWRDNACK / GPIO_S5_11

PMC_SUSCLK_0 / GPIO_S5_12

PMC_SLP_S0IX# / GPIO_S5_13

PMC_SLP_S4#

PMC_SLP_S3#

GPIO_S5_14

PMC_ACPRESENT

PMC_WAKE_PCIE_0# / GPIO_S5_15

PMC_BATLOW#

PMC_PWRBTN# / GPIO_S5_16

PMC_RSTBTN#

PMC_PLTRST#

GPIO_S5_17

PMC_SUS_STAT# / GPIO_S5_18

PCIE_CLKN_1

PCIE_CLKP_1

AK4

AK6

+1.8VALW

SIO_UART2_RXD / GPIO_S0_SC_74

SIO_UART2_TXD / GPIO_S0_SC_75

SIO_UART2_RTS# / GPIO_S0_SC_76

SIO_UART2_CTS# / GPIO_S0_SC_77

RESERVED_AD10

RESERVED_AD12

AF6

AF4

For XDP use

SIO_UART1_RXD / GPIO_S0_SC_70

SIO_UART1_TXD / GPIO_S0_SC_71

SIO_UART1_RTS# / GPIO_S0_SC_72

SIO_UART1_CTS# / GPIO_S0_SC_73

R982

4.7K_0402_5%

U53

NC

AD9

ICLK_OSCIN

ICLK_OSCOUT

C1003

10P_0402_50V8J

1

1

AH12

AH10

XTAL_25M_IN

XTAL_25M_OUT

R981

1M_0402_5%

Y7

25MHZ_10PF_7V25000014

1.8V

USOC1E

XTAL_25M_IN

+1.8VS

1

C1009

18P_0402_50V8J

<9>

C1010

18P_0402_50V8J

SOC_SERIRQ

<7>

SOC_SCI#

AV32

BA28

AY28

AY30

1

3

4

5

6

7

8

9

10

LS_OE

A1

A2

A3

A4

A5

A6

A7

A8

B1

B2

B3

B4

B5

B6

B7

B8

OE

GND

20

18

17

16

15

14

13

12

EC_SLP_S3# <22>

EC_SLP_S4# <22>

EC_KBRST# <22>

EC_LID_OUT# <22>

EC_SERIRQ <22,23>

EC_SMI# <22>

EC_SCI# <22>

PBTN_OUT# <22>

11

TXB0108PWR_TSSOP20

B

R995

49.9_0402_1%

SOC_SERIRQ

R1021 2 NTPM@ 1 0_0402_5%

EC_SERIRQ

PMC_SLP_S3#

R1025 2 NTPM@ 1 0_0402_5%

EC_SLP_S3#

FH8065301546401_FCBGA131170

B0@

+1.8VALW

+3VALW_EC

U71

SOC_SERIRQ

1

2

3

+1.8VALW

EC_SERIRQ

C1013

1 .1U_0402_16V7K

RTC_TEST#

PMC_SLP_S3#

1

2

3

4

8

7

6

5

SPI_CS0#

SPI_MISO

SPI_MOSI

SPI_CLK

SPI_CS0#

SPI_MISO

SPI_WP#

1

2

3

4

CS#

VCC

DO(IO1) HOLD#(IO3)

WP#(IO2)

CLK

GND

DI(IO0)

8

7

6

5

4

3

2

1

5

6

7

8

SPI_CS0#

SPI_MISO

SPI_MOSI

SPI_CLK

22_0804_8P4R_5%

EMC@

+CHGRTC

D22

2

1

SPI_HOLD#

SPI_CLK

SPI_MOSI

W25Q64DWSSIG_SO8

RP48

SOC_SPI_CS0#

SOC_SPI_MISO

SOC_SPI_MOSI

SOC_SPI_CLK

+RTCBATT

C1012

1U_0402_6.3V6K

U56

22_0804_8P4R_5%

EMC@

C1011

1U_0402_6.3V6K

W=20mils

2 RS@

1

RTC_TEST#

0_0402_5%

R1088

2

1

RTC_RST#

@

0_0402_5%

R1089

Clear CMOS

Close to RAM door

CLR_CMOS#

@

JCMOS1

SHORT PADS

CLR_CMOS#

<22>

3

1

C151

.1U_0402_16V7K

3.3V

<22>

PMC_CORE_PWROK

2

1

@EMC@ C1014

10P_0402_50V8J

Issued Date

2013/04/12

2014/04/12

Deciphered Date

Title

NC

Y

A

R993

10K_0402_5%

U55

1.35V

DDR_CORE_PWROK

<5>

NL17SZ07DFT2G_SC70-5

SA00004BV00

VLV-M SOC CLK/PMU/SPI

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Compal Electronics, Inc.

Compal Secret Data

Security Classification

1

2

@EMC@ R1002

33_0402_5%

+1.35VS

+3VALW

Reserve for EMI(Near SPI ROM)

SPI_CLK

EC_SLP_S3#

W=20mils

+RTCVCC

W=10mil

BAS40-04_SOT23-3

EC_SPICS#

EC_MISO

EC_MOSI

EC_SPICLK

+BIOS_SPI

SPI ROM ( 8MByte ) 1.8V

RP53

TPM@ Q83

MESS138W-G_SOT323-3

From EC

(For share ROM)

1

20K_0402_1%

2

1 R997

RTC_RST#

SPI_HOLD#

2 3.3K_0402_5%

R1000 1

R1034

10K_0402_5%

TPM@

R996

20K_0402_1%

2

1

SPI_WP#

1 0_0402_5%

2 3.3K_0402_5%

+RTCVCC

RS@

2

R998

R1001 1

+1.8VALW

SPI_CS0#

2 3.3K_0402_5%

+BIOS_SPI

R999 1

From CPU

6

5

4

VCCB

EO

B4

G2129TL1U_SC70-6

+BIOS_SPI

<22> EC_SPICS#

<22> EC_MISO

<22> EC_MOSI

<22> EC_SPICLK

+1.8VALW

TPM@

VCCA

GND

A4

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

USOC1F

M3

L1

K2

K3

M2

N3

P2

L3

J3

P3

H3

B12

USB3.0 Port

<21>

<21>

USB20_P0

USB20_N0

USB Hub

<21>

<21>

USB20_P1

USB20_N1

Touch Panel

<15>

<15>

USB20_P2

USB20_N2

Camera

+1.8VALW

R1007 1

R1009 1

2 10K_0402_5% USB_OC0#

2 10K_0402_5% USB_OC1#

<15>

<15>

M16

K16

J14

G14

K12

J12

K10

H10

USB20_P3

USB20_N3

1K_0402_1%

1K_0402_1%

1

1

2 R1004 ICLK_USB_TERMP

2 R1005 ICLK_USB_TERMN

D10

F10

USB_OC0#

USB_OC1#

C20

B20

RESERVED_M10

RESERVED_M9

GPIO_S5_32

GPIO_S5_33

GPIO_S5_34

GPIO_S5_35

GPIO_S5_36

GPIO_S5_37

GPIO_S5_38

GPIO_S5_39

RESERVED_P6

RESERVED_P7

RESERVED_M7

USB3_REXT0

RESERVED_P10

RESERVED_P12

RESERVED_M4

RESERVED_M6

GPIO_S5_40

GPIO_S5_41

GPIO_S5_42

GPIO_S5_43

USB3_RXP0

USB3_RXN0

USB3_TXP0

USB3_TXN0

USB_DP0

USB_DN0

M10

M9

D

P6

P7

R1003

M7

1.24K_0402_1%

M12 USB3_REXT0 1

2

P10

P12

M4

M6

D4

E3

PCH_USB3_RX0_P

PCH_USB3_RX0_N

K6

K7

PCH_USB3_TX0_P

PCH_USB3_TX0_N

<21>

<21>

USB3Port0

<21>

<21>

USB_DP1

USB_DN1

BIOS/EFITopSwap

USB_DP2

USB_DN2

USB_DP3

USB_DN3

RESERVED_H8

RESERVED_H7

+1.8VS

H8

H7

ICLK_USB_TERMP

ICLK_USB_TERMN

RESERVED_H4

RESERVED_H5

H4

H5

USB_OC_0# / GPIO_S5_19

USB_OC_1# / GPIO_S5_20

GPIO_S0_SC_56

USB_PLL_MON

M13

B4

B5

E2

D2

NOTE: Ref checklist rev1.2 p.25

USB_HSIC_RCOMP must NOT float if they are not being used.

1

R1012

49.9_0402_1%1

+1.8VS

RP49

5

6

7

8

2

HSIC_RCOMP

45.3_0402_1%

4

3

2

1

PCU_SMB_CLK

PCU_SMB_DATA

PCU_SMB_ALERT#

4.7K_0804_8P4R_5%

+1.8VS

<22,23>

<22,23>

<22,23>

<22,23>

<22,23>

<22>

<23>

<23>

<8>

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_CLK_EC

LPC_CLK_TPM

LPC_CLKRUN#

SOC_SERIRQ

2 R1013 LPC_RCOMP

22_0402_5% 1 EMC@ 2 R1014 LPC_CLK_0

22_0402_5% 1 TPM@ 2 R1017 LPC_CLK_1

A7

BF18

BH16

BJ17

BJ13

BG14

BG17

BG15

BH14

BG16

BG13

USB_RCOMPO

USB_RCOMPI

GPIO_S0_SC_55

GPIO_S0_SC_56

GPIO_S0_SC_57 / PCU_UART_TXD

GPIO_S0_SC_58

GPIO_S0_SC_59

GPIO_S0_SC_60

GPIO_S0_SC_61 / PCU_UART_RXD

USB_PLL_MON

USB_HSIC0_DATA

USB_HSIC0_STROBE

ILB_8254_SPKR / GPIO_S0_SC_54

USB_HSIC1_DATA

USB_HSIC1_STROBE

SIO_I2C0_DATA / GPIO_S0_SC_78

SIO_I2C0_CLK / GPIO_S0_SC_79

BD12

BC12

BD14

BC14

BF14

BD16

BC16

BH12

GPIO_S0_SC_56

DBG_UART_TXD

T203@

DBG_UART_RXD

T204@

SOC_SPKR

SOC_SPKR

GPIO_S0_SC_56:TopSwap(A16Override)

0=Topaddressbitisunchanged

1=Topaddressbitisinverted

ReferenceEDS2.0Page51

<24>

BH22

BG23

USB_HSIC_RCOMP

SIO_I2C1_DATA / GPIO_S0_SC_80

SIO_I2C1_CLK / GPIO_S0_SC_81

LPC_RCOMP / VGA_RCOMP

ILB_LPC_AD_0 / GPIO_S0_SC_42

ILB_LPC_AD_1 / GPIO_S0_SC_43

ILB_LPC_AD_2 / GPIO_S0_SC_44

ILB_LPC_AD_3 / GPIO_S0_SC_45

ILB_LPC_FRAME# / GPIO_S0_SC_46

ILB_LPC_CLK_0 / GPIO_S0_SC_47

ILB_LPC_CLK_1 / GPIO_S0_SC_48

ILB_LPC_CLKRUN# / GPIO_S0_SC_49

ILB_LPC_SERIRQ / GPIO_S0_SC_50

ForTouchScreen

BG24

BH24

+1.8VS

SOC_I2C5_DATA R1143 1

SIO_I2C2_DATA / GPIO_S0_SC_82

SIO_I2C2_CLK / GPIO_S0_SC_83

@

R1011

10K_0402_5%

BG25

BJ25

SOC_I2C2_DATA

SOC_I2C2_CLK

SOC_I2C5_CLK

TSI@ 2 2.2K_0402_5%

R1144 1

TSI@ 2 2.2K_0402_5%

+1.8VS

SIO_I2C3_DATA / GPIO_S0_SC_84

SIO_I2C3_CLK / GPIO_S0_SC_85

BG26

BH26

5

D6

C7

BF27

BG27

TSI@

3

SOC_I2C5_DATA 4

Q80A

DMN63D8LDW_SOT363-6

I2C5_SDA_PNL

<15>

I2C5_SCL_PNL

<15>

BG12

PCU_SMB_DATA

BH10

PCU_SMB_CLK

PCU_SMB_ALERT# BG11

4 PCU_SMB_CLK

Q79A

DMN63D8LDW_SOT363-6

PCU_SMB_DATA / GPIO_S0_SC_51

PCU_SMB_CLK / GPIO_S0_SC_52

PCU_SMB_ALERT# / GPIO_S0_SC_53

SIO_I2C6_DATA / GPIO_S0_SC_90

SIO_I2C6_CLK / GPIO_S0_SC_91 / SD3_WP

PCU_SMB_DATA

EC_SMB_DA2

<13,14,19,22>

Q79B

DMN63D8LDW_SOT363-6

SIO_I2C5_DATA / GPIO_S0_SC_88

SIO_I2C5_CLK / GPIO_S0_SC_89

ILB_LPC_CLK_0 : Output

Need Check with EC

of

25MHz,

6 OF 13

ILB_LPC_CLK_1 is for CLK_0 feedback.(Input)

Set to Output for Normal Usage

GPIO_S0_SC_092

GPIO_S0_SC_093

SOC_I2C5_DATA

SOC_I2C5_CLK

BH28

BG28

TSI@

6

1

Q80B

DMN63D8LDW_SOT363-6

SOC_I2C5_CLK

EC_SMB_CK2

<13,14,19,22>

Pull High at EC side

SIO_I2C4_DATA / GPIO_S0_SC_86

SIO_I2C4_CLK / GPIO_S0_SC_87

R1010 1

@

0_0402_5%

USB_RCOMP

C1015

@EMC@

2

1 10P_0402_50V8J LPC_CLK_0

R1008 1

45.3_0402_1%

@

R1006

10K_0402_5%

<21>

GPIO_S5_31

G2

BJ29

BG29

BH30

BG30

GPIO_S0_SC_92

GPIO_S0_SC_93

T201@

T202@

ForTouchPad

+1.8VS

SOC_I2C2_DATA R1153 1

FH8065301546401_FCBGA131170

B0@

SOC_I2C2_CLK

2 2.2K_0402_5%

R1152 1

2 2.2K_0402_5%

+1.8VS

I2C2_SDA_TP

<23>

I2C2_SCL_TP

<23>

3

SOC_I2C2_DATA 4

Q81A

DMN63D8LDW_SOT363-6

1

6

Q81B

DMN63D8LDW_SOT363-6

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2013/04/12

SOC_I2C2_CLK

2014/04/12

Deciphered Date

Title

VLV-M SOC USB/LPC/SMBus

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

of

Rev

1.0

39

+1.35V_SOC

+SOC_VCC

USOC1G

AA27

AA29

AA30

AC27

AC29

AC30

AD27

AD29

AD30

AF27

AF29

AG27

AG29

AG30

P26

P27

U27

U29

V27

V29

V30

Y27

Y29

Y30

T194

AA22

TP2_CORE_VCC_S0iX

DRAM_VDD_S4_AD38

DRAM_VDD_S4_AF38

DRAM_VDD_S4_A48

DRAM_VDD_S4_AK38

DRAM_VDD_S4_AM38

DRAM_VDD_S4_AV41

DRAM_VDD_S4_AV42

DRAM_VDD_S4_BB46

DRAM_VDD_S4_BD49

DRAM_VDD_S4_BD52

DRAM_VDD_S4_BD53

DRAM_VDD_S4_BF44

DRAM_VDD_S4_BG51

DRAM_VDD_S4_BJ48

DRAM_VDD_S4_C51

DRAM_VDD_S4_D44

DRAM_VDD_S4_F49

DRAM_VDD_S4_F52

DRAM_VDD_S4_F53

DRAM_VDD_S4_H46

DRAM_VDD_S4_M41

DRAM_VDD_S4_M42

DRAM_VDD_S4_V38

DRAM_VDD_S4_Y38

CORE_VCC_S0IX_AD27

CORE_VCC_S0IX_AD29

CORE_VCC_S0IX_AD30

CORE_VCC_S0IX_AF27

CORE_VCC_S0IX_AF29

CORE_VCC_S0IX_AG27

CORE_VCC_S0IX_AG29

CORE_VCC_S0IX_AG30

CORE_VCC_S0IX_P26

CORE_VCC_S0IX_P27

CORE_VCC_S0IX_U27

CORE_VCC_S0IX_U29

CORE_VCC_S0IX_V27

CORE_VCC_S0IX_V29

CORE_VCC_S0IX_V30

CORE_VCC_S0IX_Y27

CORE_VCC_S0IX_Y29

CORE_VCC_S0IX_Y30

AD38

AF38

A48

AK38

AM38

AV41

AV42

BB46

BD49

BD52

BD53

BF44

BG51

BJ48

C51

D44

F49

F52

F53

H46

M41

M42

V38

Y38

BB8

P28

N28

VGFX_VSNS

VCORE_VSNS

VCORE_GSNS

1250mA

C1019 2

C1020 2

C1021 2

C1022 2

1

1

1

1

C1147 1

C1148 1

2 10U_0603_6.3V6M

2 10U_0603_6.3V6M

JUMP_43X118

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

0715 Add for CRT flicker

ICLK_V1P35_S3_F2_AG18

ICLK_V1P35_S3_F1_AJ19

VGA_V1P35_S3_F1_BD1

AG18

AJ19

VGA_V1P35_S3_F1

DRAM_V1P35_S0IX_F1_AD36

UNCORE_V1P35_S0IX_F2_AG32

UNCORE_V1P35_S0IX_F3_V36

UNCORE_V1P35_S0IX_F4_U36

UNCORE_V1P35_S0IX_F5_AA25

VGA_V1P35_S3_F1

C1023 1

R1084

8.06K_0402_1%

2 10U_0603_6.3V6M

AD36

AG32

V36

U36

OUT

IN

BYP

SHDN

1

2

3

2

G916T1UF_SOT23-5

C1179

1U_0402_6.3V6K

R1085

100K_0402_1%

B

AA25

<22,25,30,31,32>

UNCORE_V1P35_S0IX_F6_AF19

UNCORE_VNN_SENSE

UNCORE_V1P35_S0IX_F1_AG19

CORE_VCC_SENSE_P28 7 OF 13

CORE_VSS_SENSE_N28

GND

BD1

UNCORE_VNN_S3_AM22

UNCORE_VNN_S3_AK32

UNCORE_VNN_S3_AK30

UNCORE_VNN_S3_AK29

UNCORE_VNN_S3_AK27

UNCORE_VNN_S3_AK25

UNCORE_VNN_S3_AK24

UNCORE_VNN_S3_AK22

UNCORE_VNN_S3_AJ24

UNCORE_VNN_S3_AJ22

UNCORE_VNN_S3_AG24

UNCORE_VNN_S3_AG22

UNCORE_VNN_S3_AF24

UNCORE_VNN_S3_AF22

UNCORE_VNN_S3_AD22

UNCORE_VNN_S3_AC24

UNCORE_VNN_S3_AC22

UNCORE_VNN_S3_AA24

UNCORE_VNN_S3_AD24

+3VALW

U65

420mA

AF19

AG19

C1024 1

C1025 1

C1026 1

C1027 1

C1028 1

C1029 1

C1030 1

C1031 1

C1032 1

C1033 1

FH8065301546401_FCBGA131170

R1020

100_0402_1%

@EMC@ L63

2

1

HCB2012KF-121T50_2P

JP3 JP@

<33>

<33>

<33>

R1019

100_0402_1%

2

R1018

100_0402_1%

@EMC@ L62

2

1

HCB2012KF-121T50_2P

+1.35VS

AM22

AK32

AK30

AK29

AK27

AK25

AK24

AK22

AJ24

AJ22

AG24

AG22

AF24

AF22

AD22

AC24

AC22

AA24

AD24

+SOC_VCC

2 1U_0402_6.3V6K

2 .1U_0402_16V7K

TP2_CORE_VCC_S0IX

14A +SOC_VNN

+SOC_VNN

C1017 1

C1018 1

CORE_VCC_S0IX_AA27

CORE_VCC_S0IX_AA29

CORE_VCC_S0IX_AA30

CORE_VCC_S0IX_AC27

CORE_VCC_S0IX_AC29

CORE_VCC_S0IX_AC30

+1.35V_L

@EMC@ L61

2

1

HCB2012KF-121T50_2P

20mil

12A

B0@

2

2

2

2

@2

2

2

2

2

2

22U_0805_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

VOUT

2

1

R1087

36K_0402_5%

SUSP#

= 1.25 (1 + R1/R2).

C1181

.1U_0402_16V7K

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2013/04/12

2014/04/12

Deciphered Date

Title

VLV-M SOC Power

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

10

of

Rev

1.0

39

USOC1H

+1.0VALW

UNCORE_V1P0_G3 1uF*4

USB3_V1P0_G3 0.01uF*1

C1034

C1035

C1036

C1037

1

1

1

1

2

2

2

2

C1039

2 0.01U_0402_16V7K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

+1.0VS

C

DRAM_V1P0_S0iX 1uF*4

C1043

C1044

C1046

C1047

1

1

1

1

2

2

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

DDI_V1P0_S0iX 1uF*4

C1048

C1049

C1050

C1052

1

1

1

1

2

2

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

UNCORE_V1P0_S0iX 22uF*3

1uF*2

PCIE_SATA_V1P0_S3 1uF*1

UNCORE_V1P0_S3 1uF*1

PCIE_V1P0_S3 1uF*1

VGA_V1P0_S3 1uF*1

USB_V1P0_S3 0.1uF*1

USB3DEV_V1P0_S3 0.01uF*1

GPIO_V1P0_S3 1uF*1

SVID_V1P0_S3 1uF*1

C1056 1

C1057 1

C1059 1

C1060 1

C1061 1

2

2

2

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

C1062 1

C1064 1

C1066 1

C1068 1

C1069 1

C1070 1

C1071 1

C1072 1

2

2

2

2

2

2

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

.1U_0402_16V7K

0.01U_0402_16V7K

1U_0402_6.3V6K

1U_0402_6.3V6K

U22

V22

C5

B6

Y19

C3

V32

BJ6

AD35

AF35

AF36

AA36

AJ36

AK35

AK36

Y35

Y36

AK19

AK21

AJ18

AM16

AN29

AN30

V24

Y22

Y24

AF16

AF18

Y18

G1

AK18

AM18

AM21

AN21

AN18

AN19

AF21

AG21

M14

U18

U19

AN25

Follow CRBv1.15

325mA

UNCORE_V1P0_G3_U22

UNCORE_V1P0_G3_V22

UNCORE_V1P0_G3_C5

UNCORE_V1P0_G3_B6

1000mA

CORE_V1P0_S3_AC32

CORE_V1P0_S3_Y32

USB3_V1P0_G3_Y19

USB3_V1P0_G3_C3

2750mA

SVID_V1P0_S3_V32

VGA_V1P0_S3_BJ6

DRAM_V1P0_S0IX_AD35

DRAM_V1P0_S0IX_AF35

DRAM_V1P0_S0IX_AF36

DRAM_V1P0_S0IX_AA36

DRAM_V1P0_S0IX_AJ36

DRAM_V1P0_S0IX_AK35

DRAM_V1P0_S0IX_AK36

DRAM_V1P0_S0IX_Y35

DRAM_V1P0_S0IX_Y36

DDI_V1P0_S0IX_AK19

DDI_V1P0_S0IX_AK21

DDI_V1P0_S0IX_AJ18

DDI_V1P0_S0IX_AM16

VIS_V1P0_S0IX_AN29

VIS_V1P0_S0IX_AN30

VIS_V1P0_S0IX_V24

VIS_V1P0_S0IX_Y22

VIS_V1P0_S0IX_Y24

UNCORE_V1P0_S3_AF16

UNCORE_V1P0_S3_AF18

UNCORE_V1P0_S3_Y18

UNCORE_V1P0_S3_G1

PCIE_V1P0_S3_AK18

PCIE_V1P0_S3_AM18

PCIE_V1P0_S3_AM21

PCIE_V1P0_S3_AN21

PCIE_SATA_V1P0_S3_AN18

SATA_V1P0_S3_AN19

UNCORE_V1P0_S0IX_AF21

UNCORE_V1P0_S0IX_AG21

USB_V1P0_S3_M14

USB_V1P0_S3_U18

USB_V1P0_S3_U19

GPIO_V1P0_S3_AN25

CORE_V1P05_S3_AA33

CORE_V1P05_S3_AF33

CORE_V1P05_S3_AG33

CORE_V1P05_S3_AG35

CORE_V1P05_S3_U33

CORE_V1P05_S3_U35

CORE_V1P05_S3_V33

F1

TP_CORE_V1P05_S4

AF30

AA33

AF33

AG33

AG35

U33

U35

V33

C1038 1

2 0.47U_0402_6.3V6K

C1040 1

C1041 1

C1042 1

2 1U_0402_6.3V6K

2 1U_0402_6.3V6K

2 1U_0402_6.3V6K

CORE_V1P05_S3 1uF*3

+1.8VALW

C

UNCORE_V1P8_G3_U24

PCU_V1P8_G3_V25

USB_V1P8_G3_N20

65mA PMU_V1P8_G3_U25

UNCORE_V1P8_G3_AA18

U24

V25

N20

U25

AA18

C1045 1

PMC_V1P8_G3 1uF*1

2 1U_0402_6.3V6K

+1.8VS

10mA

UNCORE_V1P8_S3_AM30

UNCORE_V1P8_S3_AN32

UNCORE_V1P8_S3_U38

58mA

HDA_V1P5_S3_AM32

50mA PCU_V3P3_G3_N22

USB_V3P3_G3_N18

USB_V3P3_G3_P18

33mA

VGA_V3P3_S3_AN24

SD3_V1P8V3P3_S3_AN27

LPC_V1P8V3P3_S3_AM27

35mA

USB_HSIC_V1P2_G3_V18

T195

@

+1.05VS

AC32

Y32

RESERVED_F1

VSS_AD16

VSS_AD18

AM30

AN32

U38

C1051 1

C1053 1

C1054 1

C1055 1

2

2

2

@2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

UNCORE_V1P8_S3 1uF*4

+1.5VS

AM32

C1058 1

2 1U_0402_6.3V6K

+3VALW

N22 +3VALW_SOC

2 RS@

1

R1022

0_0402_5%

2 .1U_0402_16V7K

C1063 1

2 1U_0402_6.3V6K

C1065 1

2 1U_0402_6.3V6K

C1067 1

USB_V3P3_G3 0.1uF*1

USB_ULPI_V1P8_S3 1uF*1

PCU_V3P3_G3 1uF*1

N18

P18

AN24

+3VS

2 RS@

1

R1023

0_0402_5%

1

2

C1073

1U_0402_6.3V6K

AM27 +1.8VS_3.3VS LPC 2 TPM@ 1

R1031

0_0402_5%

2 NTPM@ 1

R1032

0_0402_5%

V18

1

2

C1075

1U_0402_6.3V6K

+3VS_SOC

AN27

AD16

AD18

TP_CORE_V1P05_S4_AF30

C1074 1

HDA_LPE_V1P5V1P8_S3 1uF*1

+3VS

VGA_V3P3_S3 1uF*1

+1.8VS

B

+1.0VALW

USB_HSIC_V1P2_G3 1uF*1

Disable HSIC

If the USB HSIC is not used, pin V18 can be connected

to either +V1P2A or +V1P0A.

2 1U_0402_6.3V6K

@

Pop when use +1.2VALW

8 OF 13

FH8065301546401_FCBGA131170

B0@

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2013/04/12

2014/04/12

Deciphered Date

Title

VLV-M SOC Power

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Z5WAL_BayTrailM_LAB211P

Sheet

Monday, April 07, 2014

11

of

Rev

1.0

39

USOC1I

A11

A15

A19

A23

A27

A31

A35

A39

A43

A47

AA1

AA16

AA19

AA21

AA3

AA32

AA35

AA38

AA53

AB10

AB4

AB41

AB45

AB47

AB48

AB50

AB51

AB6

AC16

AC18

AC19

AC21

AC25

AC33

AC35

B2

A6

A52

A51

A5

A49

A3

BH53

BH52

BH2

BH1

BG53

E53

U16

AN16

VSS_A11

VSS_AC36

VSS_A15

VSS_AC38

VSS_A19

VSS_AD19

VSS_A23

VSS_AD21

VSS_A27

VSS_AD25

VSS_A31

VSS_AD32

VSS_A35

VSS_AD33

VSS_A39

VSS_AD47

VSS_A43

VSS_AD7

VSS_A47

VSS_AE1

VSS_AA1

VSS_AE11

VSS_AA16

VSS_AE12

VSS_AA19

VSS_AE14

VSS_AA21

VSS_AE3

VSS_AA3

VSS_AE4

VSS_AA32

VSS_AE40

VSS_AA35

VSS_AE42

VSS_AA38

VSS_AE43

VSS_AA53

VSS_AE45

VSS_AB10

VSS_AE46

VSS_AB4

VSS_AE48

VSS_AB41

VSS_AE50

VSS_AB45

VSS_AE51

VSS_AB47

VSS_AE53

VSS_AB48

VSS_AE6

VSS_AB50

VSS_AE8

VSS_AB51

VSS_AE9

VSS_AB6

VSS_AF10

VSS_AC16

VSS_AF12

VSS_AC18

VSS_AF25

VSS_AC19

VSS_AF32

VSS_AC21

VSS_AF47

VSS_AC25

VSS_AG16

VSS_AC33

VSS_AG25

VSS_AC35 9 OF 13VSS_AG36

VSS_B2

VSS_B52

VSS_A6

VSS_B53

VSS_A52

VSS_BE1

VSS_A51

VSS_BE53

VSS_A5

VSS_BG1

VSS_A49

VSS_BJ2

VSS_A3

VSS_BJ3

VSS_BH53

VSS_BJ5

VSS_BH52

VSS_BJ49

VSS_BH2

VSS_BJ51

VSS_BH1

VSS_BJ52

VSS_BG53

VSS_C1

VSS_E53

VSS_C53

VSS_E1

USOC1J

AC36

AC38

AD19

AD21

AD25

AD32

AD33

AD47

AD7

AE1

AE11

AE12

AE14

AE3

AE4

AE40

AE42

AE43

AE45

AE46

AE48

AE50

AE51

AE53

AE6

AE8

AE9

AF10

AF12

AF25

AF32

AF47

AG16

AG25

AG36

B52

B53

BE1

BE53

BG1

BJ2

BJ3

BJ5

BJ49

BJ51

BJ52

C1

C53

E1

AG38

AH4

AH41

AH45

AH7

AH9

AJ1

AJ16

AJ21

AJ25

AJ27

AJ29

AJ3

AJ30

AJ32

AJ33

AJ35

AJ38

AJ53

AK10

AK14

AK16

AK33

AK41

AK44

AM12

AM19

AM24

AM25

AM29

AM33

AM35

AM36

AM40

M28

VSS_AG38

VSS_AH47

VSS_AH4

VSS_AH48

VSS_AH41

VSS_AH50

VSS_AH45

VSS_AH51

VSS_AH7

VSS_AH6

VSS_AH9

VSS_AM44

VSS_AJ1

VSS_AM51

VSS_AJ16

VSS_AM7

VSS_AJ21

VSS_AN1

VSS_AJ25

VSS_AN11

VSS_AJ27

VSS_AN12

VSS_AJ29

VSS_AN14

VSS_AJ3

VSS_AN22

VSS_AJ30

VSS_AN3

VSS_AJ32

VSS_AN33

VSS_AJ33

VSS_AN35

VSS_AJ35

VSS_AN36

VSS_AJ38

VSS_AN38

VSS_AJ53

VSS_AN40

VSS_AK10

VSS_AN42

VSS_AK14

VSS_AN43

VSS_AK16

VSS_AN45

VSS_AK33

VSS_AN46

VSS_AK41

VSS_AN48

VSS_AK44

VSS_AN49

VSS_AM12

VSS_AN5

VSS_AM19

VSS_AN51

VSS_AM24

VSS_AN53

VSS_AM25

VSS_AN6

VSS_AM29

VSS_AN8

VSS_AM33

VSS_AN9

VSS_AM35

VSS_AP40

VSS_AM36

VSS_AT12

VSS_AM40

VSS_AT16

VSS_M28 10 OF 13 VSS_AT19

USOC1K

AH47

AH48

AH50

AH51

AH6

AM44

AM51

AM7

AN1

AN11

AN12

AN14

AN22

AN3

AN33

AN35

AN36

AN38

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN5

AN51

AN53

AN6

AN8

AN9

AP40

AT12

AT16

AT19

AT24

AT27

AT30

AT35

AT38

AT4

AT47

AT52

AU1

AU24

AU3

AU30

AU38

AU51

AV12

AV13

AV14

AV18

AV19

AV24

AV27

AV30

AV35

AV38

AV47

AV51

AV7

AW13

AW19

AW27

AW3

AW35

AY10

AY22

AY32

USOC1L

VSS_AT24

VSS_AY36

VSS_AT27

VSS_AY4

VSS_AT30

VSS_AY50

VSS_AT35

VSS_AY9

VSS_AT38

VSS_BA14

VSS_AT4

VSS_BA19

VSS_AT47

VSS_BA22

VSS_AT52

VSS_BA27

VSS_AU1

VSS_BA32

VSS_AU24

VSS_BA35

VSS_AU3

VSS_BA40

VSS_AU30

VSS_BA53

VSS_AU38

VSS_BB19

VSS_AU51

VSS_BB27

VSS_AV12

VSS_BB35

VSS_AV13

VSS_BC20

VSS_AV14

VSS_BC22

VSS_AV18

VSS_BC26

VSS_AV19

VSS_BC28

VSS_AV24

VSS_BC32

VSS_AV27

VSS_BC34

VSS_AV30

VSS_BC42

VSS_AV35

VSS_BD19

VSS_AV38

VSS_BD24

VSS_AV47

VSS_BD27

VSS_AV51

VSS_BD30

VSS_AV7

VSS_BD35

VSS_AW13

VSS_BE19

VSS_AW19

VSS_BE2

VSS_AW27

VSS_BE35

VSS_AW3

VSS_BE8

VSS_AW35

VSS_BF12

VSS_AY10

VSS_BF16

VSS_AY22

VSS_BF24

VSS_AY32 11 OF 13

VSS_BF38

AY36

AY4

AY50

AY9

BA14

BA19

BA22

BA27

BA32

BA35

BA40

BA53

BB19

BB27

BB35

BC20

BC22

BC26

BC28

BC32

BC34

BC42

BD19

BD24

BD27

BD30

BD35

BE19

BE2

BE35

BE8

BF12

BF16

BF24

BF38

BF30

BF36

BF4

BG31

BG34

BG39

BG42

BG45

BG49

BJ11

BJ15

BJ19

BJ23

BJ27

BJ31

BJ35

BJ39

BJ43

BJ47

BJ7

C14

C31

C34

C39

C42

C45

C49

D12

D16

D24

D30

D36

D38

E19

E35

VSS_BF30

VSS_BF36

VSS_BF4

VSS_BG31

VSS_BG34

VSS_BG39

VSS_BG42

VSS_BG45

VSS_BG49

VSS_BJ11

VSS_BJ15

VSS_BJ19

VSS_BJ23

VSS_BJ27

VSS_BJ31

VSS_BJ35

VSS_BJ39

VSS_BJ43

VSS_BJ47

VSS_BJ7

VSS_C14

VSS_C31

VSS_C34

VSS_C39

VSS_C42