Beruflich Dokumente

Kultur Dokumente

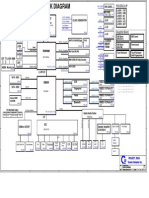

Smp8654 Dev Board: 922Reva3A

Hochgeladen von

Михаил ГудковOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Smp8654 Dev Board: 922Reva3A

Hochgeladen von

Михаил ГудковCopyright:

Verfügbare Formate

A

Ethernet

RJ45

PHY

RTL8201

RJ45

PHY

RTL8201

10/100

MINIPCI

10/100

NETWORK

0

25M

Ethernet

NETWORK

1

USB

Host

Controller

USB 2.0

Wireless Card

802.11b/g/n

MII or PCI

25M

Digital

VIDEO

JTAG

HDMI 1.3

up to 1080P60

UART

12bit Deep color

Analog

AUDIO

2Vrms

Right

Stereo

DAC

Left

Digital

AUDIO

Optical

I2S

Coax.

S/PDIF

Component

32

PWR:

3.3V/2.5/1.8/1.0V

Y

up to 1080P

Pr

DDR0

SPI

Pb

IR

CS1#

NAND FLASH

up to 8GBits

CS0#

POWER

+12V 3A

DC IN

SmartCard

SATA-2

27M

32

DDR2 SDRAM

32Mx16 333MHz

DC-DC

DDR2 SDRAM

32Mx16 333MHz

Lin.

DDR2 SDRAM

32Mx16 333MHz

I.R.

1

1

1

1

1

SATA

T29

Audio

5V

0.1A

DC-DC 5V

3A

2

120M

Video DACs

Lin.

0.2A est.

3.3V

1.5A

3.3V

120M

SATA

T30

3.0A

1.8V

T31

Smart

Card

T32

T33

TDA8024

3.0A

1.0V

T34

to HDD

1A

5V 3A

DDR2 SDRAM

32Mx16 333MHz

1

1A

DDR1

Video

DACs

HDTV OUT

PB

SMP8654

S-Video

PAL/NTSC

656 Jtag UART

IN

Composite

TV OUT

PCI

HDMI GMII GMII USB

NAND FLASH

up to 8GBits

H7

MTG125

Smart

Card

TDA8024

SMP8654 Dev

Board

H5

MTG125

922revA3a

B

SIGMA DESIGNS CONFIDENTIAL

Title

Sigma Designs

SMP8654 Dev Board

1778 McCarthy Blvd Size

B

Milpitas CA 95035

Date:

0.5A est.

1.5A max

Include (2x) USB

ports at 0.5A ea.

Document Number

Rev

53-000922-01

Monday, January 19, 2009

A3a

Sheet

E

of

15

C547

10uF Cer

C8

1

2

C552

10uF Cer

1

2

C551

10uF Cer

C16

C550

10uF Cer

C15

1000pF

J72

J3

1 0.01uF

3300pF

C558

27K

R688

1

2

R687

10.0K

D38

RT8272

26.1K

C29

R686

10uF Cer

C28

SYNC

FB

GND

PAD

COMP

Vcc3V3

L62

4.7uH

10uF Cer

SW

8

4

9

C555

C27

EN

10uF Cer

BS

B330A

Vcc5V

R664

3

MTH157

R256

1

2

3

-10%

+10%

R679

30K

Vcc3V3

00

R683

xx

R684 1

N-MOS

Q20

100K

1

2

3

200K

R685

J62

SIGMA DESIGNS CONFIDENTIAL

Title

Sigma Designs

R257

SMP8654 Dev Board

1778 McCarthy Blvd Size

B

Milpitas CA 95035

B

Split planes for I/O

power

HDR1x2 Measurement

J51

Date:

A

Vcc1V8

J86

-10%

+10%

HDR1x3

HDR1x3

200K

R681

1

2

R682

3

1M

Vcc1V8

TESTING ONLY

C546

Vcc5V

1.8V 3A

1

2

R678

C544

10.0K

J5

HDR1x2

10uF Cer

18

C543

TAB

10uF Cer

C545

C542

R677

22pF

C541

12.4K

10

10uF Cer

GND

PGND

TAB

TAB

TAB

TAB

TAB

TAB

TAB

2

5

FB

COMP

C540

SHDN/RT

3

4

10uF Cer

LX

LX

10uF Cer

VDD

PVDD

PVDD

R680

332K

TESTING ONLY

100K

C539

C538

10uF Cer

1

2

C527

C32

C525

R22

10uF Cer

10.0K

10uF Cer

R667

30K

C524

18

10uF Cer

TAB

C386

10uF Cer

22pF

C31

10

R296

xx

R295 1

N-MOS

Q18

COMP

R20

Vcc1V8

00

3.32K

Vcc1V0

8

7

6

For current measurement purpose only.

MUST BE REMOVED for standard operation

SR-0805 size

L61

2.2uH

R663

332K

1M

GND

PGND

TAB

TAB

TAB

TAB

TAB

TAB

TAB

2

5

FB

10uF Cer

SHDN/RT

3

4

C526

LX

LX

1000pF

VDD

PVDD

PVDD

11

12

13

14

15

16

17

C523

C30

10uF Cer

10uF Cer

8

7

6

SR-0805 size

L6

2.2uH

10uF Cer

1.05V

3A

U95

RT8015A

1000pF

160

U6

RT8015A

9

9

9

IN

11

12

13

14

15

16

17

80

J6

Vcc5V

MTH157

8

7

6

5

Split planes for I/O

power

HDR1x2 Measurement

usec

0

HDR1x2

8

7

6

5

H4

1

2

3

4

R9

1.0V

HOSTMODE

Power sequencing: 3.3V-->1.8V-->1.0V

MTH157

10.0K

HDR1x2

Vcc5V

8

7

6

5

1

2

3

4

18 R10

30K

TAB

Vcc3V3

BSS138

MTH157

H3

C553

1.8V

10K

Vcc3V3

8

7

6

5

H6

GND

PGND

R19

0.1uF C557

C556

Sequencing:

4.7uF 35V

3.3V

1

2

3

4

R7

22pF

U96

For single Stereo DAC only (25mA),

use RT9161-50GV in SOT23-3 !

MTH157

H9

C14

P12V

3A_30R300

8

7

6

5

1

2

3

4

2

5

R8

332K

2

2

30.9K

10

10uF Cer

C22

10uF Cer

0.1uF

FB

COMP

C5

C21

SHDN/RT

C13

0.1uF

10uF Cer

C20

Q1

H8

Vcc3V3

10uF Cer

0.1uF

1

MBRS320T3

D5

B330A

1

2

3

4

5V 3A

HDR1x2

L3 SR-0805 size

2.2uH

3

4

C19

Vcc12V

2

Jack_DCIN

MBRS320T3

3.3V 3A

LX

LX

11

12

13

14

15

16

17

10uF Cer

VDD

PVDD

PVDD

TAB

TAB

TAB

TAB

TAB

TAB

TAB

10uF Cer

C18

8

7

6

D4

2

J2

For current measurement purpose only.

MUST BE REMOVED for standard operation

U3

RT8015A

GND

OUT

100uF/16V

VIN

2

Z1

4.7uF 35V

C17

C549

Audio = 75mA

(25mA x3)

330uF/25V

NC

AUDVAA

10uF Cer

SOT223

RT9161A-50GG

C26

R2

SOIC8

2

P12V

3

2

D2

OUTPUT set to 5.3V to compensate

loss over D1

Nominal for 5.0V: R1=44.2K

Power Input

12V DC

Do not use when using as PCI device

(Power is derived from PCI slot)

1

47.5K

R4

10.0K

B330A

MOLEX 015244449

Vcc5V

F1

C9

27K

RT8272

B330A

Vcc12V

J4

R1

3300pF

C488

10uF Cer

SYNC

FB

GND

PAD

COMP

C7

SW

8

4

9

Vcc5V

D1

2

10uF Cer

EN

C6

C2

CDRH5D28

SR-0805 size

L1

4.7uH

C1

R662

SOIC8

1 0.01uF

C554

27K

BS

10uF Cer

R5

J1

IN

10uF Cer

10.0K

D3

5V

GND

GND

12V

4

3

2

1

0.1uF C4

C522

C520

6 3300pF

RT8272

C519

SYNC

FB

GND

PAD

COMP

R3

10uF Cer

44.2K

10uF Cer

C3

C12

EN

0.01uF

C518

SW

C11

U1

2

VCC12V

10uF Cer

0.1uF C521

4.7uF 35V

8

4

9

BS

IN

C10

HDD5V

10uF Cer

U2

2

SR-0805 size

L2

4.7uH

10uF Cer

Vcc12V

Protection Diode required because of dual power source (5V from PCI in

device mode). MUST BE REMOVED for standard operation

P12V

5V 3A

SATA Power

4.7uF 35V

Document Number

Rev

53-000922-01

Monday, January 19, 2009

A3a

Sheet

E

of

15

CLK27M_IN

U7A

Vcc3V3

RCLK0_IN

UART1_CTS/TMS

UART1_DCD/TCK

UART1_DSR/TRST#

UART1_DTR/TDI

UART1_RTS/TDO

UART1_RX

UART1_TX

xx

xx

00

00

WDO

RESET#

R303

R304

R305

R306

F2

G6

F5

G5

RCLK0_OUT

RCLK1_OUT

B28

G23

F24

E25

C27

D26

A29

J55

A27

F23

E24

D25

B27

C26

A28

SCARD1_CLK

SCARD1_5V

SCARD1_CMD

SCARD1_OFF

SCARD1_FCB

SCARD1_IO

SCARD1_RST

J56

JTAG1_TMS

JTAG1_TCK

JTAG1_TRST#

JTAG1_TDI

JTAG1_TDO

T35

1

T8

1

B30

H4

J4

Vcc3V3

WDO

RESET#

n.c.

n.c.

n.c.

Vcc3V3

SCARD0_CLK

SCARD0_CTL0

SCARD0_CTL1

SCARD0_CTL2

SCARD0_FC#

SCARD0_IO

SCARD0_RST

SCARD1_CLK

SCARD1_CTL0

SCARD1_CTL1

SCARD1_CTL2

SCARD1_FC#

SCARD1_IO

SCARD1_RST

GPIO0/SCL

GPIO1/SDA

GPIO2/FIP_DIN

GPIO3/FIP_DOUT

GPIO4/FIP_STB

GPIO5/FIP_CLK

GPIO6/SCL-S

GPIO7/SDA-S

GPIO8/INTA

GPIO9/INTB

GPIO10/INTC

GPIO11/INTD

GPIO12/IR

GPIO13/CEC

GPIO14/PWM1

GPIO15/PWM0

D5

E6

F7

G8

A3

B4

C5

D6

E7

F8

A4

B5

C6

D7

E8

F9

R301

R302

7

3

2

5

6

1

HOLD#

WP#

SO

SI

SCK

CS#

PCI_INT#

USB-OC#

USB-ENABLE

IR

HDMI_CEC

00

R39

14

1

MR

2

1

22

RESET#

R40

RESET#

GND

Vcc3V3

U9B

AAT3526-3.08

U0_TXD

JTAG_RESET#

U0_RXD

JTAG1_TCK

JTAG_ENAB

JTAG1_TMS

JTAG1_TDI

JTAG1_TDO

JTAG1_TRST#

Vcc3V3

3

4

10K

PC-PCI_RST#

R41

Vcc3V3

10K

RESET FROM PCI

(DEVICE ONLY)

14

SW1

EVQPA

Manual

Reset

R240

74LCX08

13

11

PIO_RESET#

22

R241

AUX_RESET#

12

14 7

Vcc3V3

74LCX08

10

8

9

7

U9D

GND

R31

U51

13

12

11

10

9

8

7

6

5

4

3

2

1

16

Vcc5V

Vcc5V

VDD

Vcc3V3

V2MON

Q17

18.2K

R285

V3MON

Vcc1V0

4.99K

R287

V4MON

HDD5V

68.0K

R288

V5MON GND

Failure Threshold:

4.64V

3.09V

1.70V

0.90V

4.68V

MR

Vcc1V8

8 1K

RST

R286 1

2N3906

ISL88031IU8HFZ

D24

3

1 POWER FAIL

- 2

LED RED

D15

3

D16

Q11

Vcc3V3

14

D17

3

- 2

LED GREEN

RN1903

D18

3

Q12

Vcc1V8

470

D19

Q13

R259

120

R243

120

R244

120

R245

POWER 1V0

1

- 2

LED GREEN

2N3904

15

Vcc5V

R242

POWER 1V8

1

- 2

LED GREEN

R258 1

2N3904

Vcc1V0

470

120

IDE/SATA POWER

1

14

R292

POWER 3V3

1

- 2

LED GREEN

HDD5V

120

POWER 5V

1

- 2

LED GREEN

15

120

R246

D20

3

- 2

LED RED

SIGMA DESIGNS CONFIDENTIAL

Vcc3V3

Title

120

R247

Sigma Designs

SMP8654 Dev Board

1778 McCarthy Blvd Size

B

Milpitas CA 95035

RESET

Date:

5

33

I.R.

TSOP4838

1

2

3

PLEASE KEEP

FOR SIGMA

SUPPORT

U9C

13

12

11

10

9

8

7

6

5

4

3

2

1

16

R29

IR1

J69

FPC12

HDR1x8

74LCX08

R28

33

TESTING ONLY

HDR1x8

1

2

U9A

RESET

10K

1

2

3

4

5

6

7

8

HDMI_CEC

1

2

3

4

5

6

7

8

Vcc3V3

VCC

Vcc5V

Vcc3V3

VCC

J13

TESTING ONLY

U8

4

RESERVED FOR

SIGMA USE ONLY

IR

TESTING ONLY

14

WDO

JTAG_RESET#

Vcc3V3

74LCX08

Vcc3V3

PIO_RESET#

Vcc3V3

Vcc3V3

I2C_SCL

I2C_SDA

R38

GND

SPI Flash

150mil SOIC8

XTAL_DISC

TEST

SMP8654

10K

U19

10K

10K

J14

J57

VCC

HDR2x10

SPI Flash

200mil SOIC8

RCLK3_OUT

J54

SCARD0_CLK

SCARD0_5V

SCARD0_CMD

SCARD0_OFF

SCARD0_FCB

SCARD0_IO

SCARD0_RST

H24

F26

G25

C29

D28

C30

E27

HOLD#

WP#

SO

SI

SCK

CS#

2

4

6

8

10

12

14

16

18

20

H2

Vcc3V3

7

3

2

5

6

1

U0_RXD

U0_TXD

F27

D29

1

3

5

7

9

11

13

15

17

19

JTAG1

UART0_RX

UART0_TX

Vcc3V3

U19A

XTAL_BUF

R30

G3

H1

HDR1x2

G2

JTAG_ENAB

E26

JTAG1_TDO

RP4

F4

JTAG_UART1#

J70

10K

R300

JTAG1_TDI

JTAG1_TMS

JTAG1_TCK

HDR2x7

5 4x10K 4

6

3

7

2

8

1

XTAL_OUT

2

4

6

8

10

12

14

22

XTAL_IN

G1

Enable

JTAG1

1

2

R289

R290

R291

R26

RCLK0_IN

HDR1x5

1

3

5

7

9

11

13

10.0K

10.0K

10.0K

1

2

3

4

5

U0_TXD

JTAG1_TRST#

JTAG1_TDI

JTAG1_TDO

JTAG1_TMS

JTAG1_TCK

JTAG_RESET#

RP3

8 4x10K 1

7

2

6

3

5

4

22

F1

R35

R36

PCI clock

RCLK0_33M

x_470K

C34

SATA

Clock

2

4

6

8

10

1K

1K

J53

J10

J15

J7

HDR2x5-005

1

x_49.9

x_27pF

UART

1

3

5

7

9

U0_RXD

Vcc3V3

C33

x_27MHz

X1

T1

J11

R337

R24

x_27pF

R260

J52

Vcc5V

xx

TESTING ONLY

Document Number

Rev

53-000922-01

Monday, January 19, 2009

A3a

Sheet

1

of

15

CONFIDENTIAL

U7B

DRAM1_DM0

DRAM1_DM1

DRAM1_DM2

DRAM1_DM3

R12

xx

R11

xx

R14

xx

R32

U12

DRAM1_A0

DRAM1_A1

DRAM1_A2

DRAM1_A3

DRAM1_A4

DRAM1_A5

DRAM1_A6

DRAM1_A7

DRAM1_A8

DRAM1_A9

DRAM1_A10

DRAM1_A11

DRAM1_A12

DRAM1_A13

Testing only

Vcc1V8

1K

R45

Vref1

VRef0

1K

R46

DRAM1_BA0

DRAM1_BA1

DRAM1_BA2

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10(AP)

A11

A12

A13

rfu

rfu

BA0

BA1

BA2

DRAM1_WE#

DRAM1_CS#

DRAM1_RAS#

DRAM1_CAS#

DRAM1_CLK

DRAM1_CLK#

DRAM1_CLKE

K3

L8

K7

L7

J8

K8

K2

WE

CS

RAS

CAS

CLK

CLK

CKE

DRAM1_ODT

K9

J2

ODT

Vref

VrefDDR1

C62

C63

C64

C65

C66

0.1uF

0.1uF

0.1uF

Vss

Vss

Vss

Vss

Vss

DDR 0

VddL

J7

VssDL

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

F2

B8

D8

E7

D2

B2

H8

H2

A7

F8

Vss

Vss

Vss

Vss

Vss

J1

C7

G1

G7

C9

A9

G3

C3

C1

E9

G9

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

A1

J9

E1

M9

R1

Vdd

Vdd

Vdd

Vdd

Vdd

J1

C7

G1

G7

C9

A9

G3

C3

C1

E9

G9

LDQS

LDQS#

LDM

F7

E8

F3

1K

R48

VrefDDR0

UDQS

UDQS#

UDM

B7

A8

B3

nc

nc

E2

A2

R272

DRAM1_D8

DRAM1_D9

DRAM1_D10

DRAM1_D11

DRAM1_D12

DRAM1_D13

DRAM1_D14

DRAM1_D15

DRAM1_DQS1

DRAM1_DQS1#

DRAM1_DM1

DRAM1_A0

DRAM1_A1

DRAM1_A2

DRAM1_A3

DRAM1_A4H

DRAM1_A5H

DRAM1_A6

DRAM1_A7

DRAM1_A8

DRAM1_A9

DRAM1_A10

DRAM1_A11

DRAM1_A12

DRAM1_A13

DRAM1_BA0

DRAM1_BA1

DRAM1_BA2

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10(AP)

A11

A12

A13

rfu

rfu

BA0

BA1

BA2

DRAM1_WE#

DRAM1_CS#

DRAM1_RAS#

DRAM1_CAS#

DRAM1_CLK

DRAM1_CLK#

DRAM1_CLKE

K3

L8

K7

L7

J8

K8

K2

WE

CS

RAS

CAS

CLK

CLK

CKE

DRAM1_ODT

K9

J2

ODT

Vref

VrefDDR1

300

FBGA84

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

G8

G2

H7

H3

H1

H9

F1

F9

LDQS

LDQS#

LDM

F7

E8

F3

DRAM1_DQS2

DRAM1_DQS2#

DRAM1_DM2

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

C8

C2

D7

D3

D1

D9

B1

B9

DRAM1_D24

DRAM1_D25

DRAM1_D26

DRAM1_D27

DRAM1_D28

DRAM1_D29

DRAM1_D30

DRAM1_D31

UDQS

UDQS#

UDM

B7

A8

B3

DRAM1_DQS3

DRAM1_DQS3#

DRAM1_DM3

nc

nc

E2

A2

32Mx16 DDR2 266MHz

DRAM1_CLK

DRAM1_CLK#

R273

DRAM1_D16

DRAM1_D17

DRAM1_D18

DRAM1_D19

DRAM1_D20

DRAM1_D21

DRAM1_D22

DRAM1_D23

300

Bottom

1K

R49

C1_CLK

C1_CLK#

VRefDDR1

C46

C47

C48

0.1uF

C45

0.1uF

C44

1K

R52

10uF Cer

C43

C84

0.1uF

0.1uF

C83

0.1uF

0.1uF

C42

C41

C40

C39

1K

R51

10uF Cer

C82

0.1uF

C8

C2

D7

D3

D1

D9

B1

B9

DRAM1_DQS0

DRAM1_DQS0#

DRAM1_DM0

Vcc1V8

0.1uF

C81

0.1uF

0.1uF

C80

0.1uF

0.1uF

C79

0.1uF

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DRAM1_D0

DRAM1_D1

DRAM1_D2

DRAM1_D3

DRAM1_D4

DRAM1_D5

DRAM1_D6

DRAM1_D7

C1_CS#

C1_RAS#

C1_A0

C1_CAS#

8

1 DRAM1_CS#

7 RP25 2 DRAM1_RAS#

6 4x22 3 DRAM1_A0

5

4 DRAM1_CAS#

1

8 DRAM1_A1

2 RP28 7 DRAM1_A4

3 4x22 6 DRAM1_A10

4

5 DRAM1_BA0

C1_A4H

C1_A6

C1_A8

C1_A13

8

1 DRAM1_A4H

7 RP29 2 DRAM1_A6

6 4x22 3 DRAM1_A8

5

4 DRAM1_A13

1

8 DRAM1_BA1

2 RP32 7 DRAM1_BA2

3 4x22 6 DRAM1_CLKE

4

5 DRAM1_WE#

C1_A2

C1_A11

C1_A5H

C1_A5

8

1 DRAM1_A2

7 RP33 2 DRAM1_A11

6 4x22 3 DRAM1_A5H

5

4 DRAM1_A5

C1_A12

C1_A9

C1_A7

C1_A3

8

1 DRAM1_A12

7 RP36 2 DRAM1_A9

6 4x22 3 DRAM1_A7

5

4 DRAM1_A3

Top

10uF Cer

C78

C75

0.1uF

0.1uF

C74

0.1uF

C77

C73

0.1uF

C76

C72

0.1uF

U13

DDR 1

Vcc1V8

1K

R50

0.1uF

C71

0.1uF

Vcc1V8

FBGA84

1K

R47

10uF Cer

C70

300

Vcc1V8

0402 size

0.1uF

R271

DRAM0_CLK

DRAM0_CLK#

G8

G2

H7

H3

H1

H9

F1

F9

32Mx16 DDR2 266MHz

A3

J3

N1

E3

P9

0.1uF

0.1uF

0.1uF

10uF Cer

C61

0.1uF

C57

0.1uF

0.1uF

C56

0.1uF

C60

C55

0.1uF

0.1uF

C54

0.1uF

C59

C53

0.1uF

0.1uF

C52

0.1uF

C58

C51

0.1uF

300

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DRAM1_CLK

DRAM1_CLK#

Tango3

Vcc1V8

C69

A1

J9

E1

M9

R1

Vdd

Vdd

Vdd

Vdd

Vdd

R282

C1_ODT

VRef1

0.1uF

R270

J1

xx

Tango3

0.1uF

C50

0.1uF

E2

A2

VddL

R13

Testing only

10uF Cer

C49

10uF Cer

nc

nc

R281

Vcc1V8

C68

DRAM0_DQS3

DRAM0_DQS3#

DRAM0_DM3

VssDL

xx

Connected 1.8V split planes.

Common 1.8V must be used for customer

layout

0402 size

C67

B7

A8

B3

J63

xx

0402 size

0.1uF

UDQS

UDQS#

UDM

C7

G1

G7

C9

A9

G3

C3

C1

E9

G9

R33

J64

Vcc1V8

10uF Cer

DRAM0_D24

DRAM0_D25

DRAM0_D26

DRAM0_D27

DRAM0_D28

DRAM0_D29

DRAM0_D30

DRAM0_D31

Vcc1V8

xx

0402 size

C1_A1

C1_A4

C1_A10

C1_BA0

C1_BA1

C1_BA2

C1_CLKE

C1_WE#

C1_ODT

R53

R54

R55

22

22

22

DRAM1_CLK

DRAM1_CLK#

DRAM1_ODT

0402 size

0402 size

Vcc1V8

0.1uF C191

0.1uF C186

0.1uF C183

0.1uF C148

0.1uF C129

C24

0.1uF

0.1uF C193

0.1uF C188

0.1uF C185

0.1uF C139

C25

0.1uF C138

0.1uF

0.1uF C190

0.1uF C187

C23

0.1uF

0.1uF C184

C390

10uF Cer

0.1uF C146

C389

10uF Cer

0.1uF C130

C388

10uF Cer

0.1uF C127

C387

10uF Cer

0.1uF C192

C394

10uF Cer

0.1uF C189

C393

10uF Cer

0.1uF C149

C392

10uF Cer

0.1uF C140

C391

0.1uF C128

Vcc1V8

Vcc1V8

10uF Cer

C8

C2

D7

D3

D1

D9

B1

B9

Vcc1V8

xx

SMP8654

Vcc1V8

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

J7

A12

D23

G19

G16

G13

D9

DRAM0_DQS2

DRAM0_DQS2#

DRAM0_DM2

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

DRAM1_ODT

DRAM1_VREF0

DRAM1_VREF1

DRAM1_VREF2

DRAM1_VREF3

DRAM1_VREF4

ODT

Vref

F7

E8

F3

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

E21

B24

C12

C10

K9

J2

LDQS

LDQS#

LDM

DRAM0_D16

DRAM0_D17

DRAM0_D18

DRAM0_D19

DRAM0_D20

DRAM0_D21

DRAM0_D22

DRAM0_D23

DRAM0_CLK

DRAM0_CLK#

Vcc1V8

A14 C1_CLK

A13 C1_CLK#

DRAM1_DM0

DRAM1_DM1

DRAM1_DM2

DRAM1_DM3

DRAM0_ODT

VrefDDR0

G8

G2

H7

H3

H1

H9

F1

F9

F2

B8

D8

E7

D2

B2

H8

H2

A7

F8

DRAM1_CK

DRAM1_CK#

8

1 DRAM0_A12

7 RP22 2 DRAM0_A9

6 4x22 3 DRAM0_A7

5

4 DRAM0_A3

C0_A12

C0_A9

C0_A7

C0_A3

E2

A2

WE

CS

RAS

CAS

CLK

CLK

CKE

A3

J3

N1

E3

P9

C1_WE#

C1_CAS#

C1_RAS#

C1_CS#

C1_CLKE

Vref0

nc

nc

K3

L8

K7

L7

J8

K8

K2

A1

J9

E1

M9

R1

B19

C14

C13

D13

A18

ODT

Vref

DRAM0_WE#

DRAM0_CS#

DRAM0_RAS#

DRAM0_CAS#

DRAM0_CLK

DRAM0_CLK#

DRAM0_CLKE

FBGA84

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

32Mx16 DDR2 266MHz

Vdd

Vdd

Vdd

Vdd

Vdd

DRAM1_WE#

DRAM1_CAS#

DRAM1_RAS#

DRAM1_CS#

DRAM1_CKE

K9

J2

B7

A8

B3

DRAM0_DQS1

DRAM0_DQS1#

DRAM0_DM1

DRAM0_BA0

DRAM0_BA1

DRAM0_BA2

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10(AP)

A11

A12

A13

rfu

rfu

BA0

BA1

BA2

Vss

Vss

Vss

Vss

Vss

C1_BA0

C1_BA1

C1_BA2

DRAM0_ODT

VrefDDR0

UDQS

UDQS#

UDM

DRAM0_D8

DRAM0_D9

DRAM0_D10

DRAM0_D11

DRAM0_D12

DRAM0_D13

DRAM0_D14

DRAM0_D15

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

A3

J3

N1

E3

P9

C17

A17

B17

WE

CS

RAS

CAS

CLK

CLK

CKE

VddL

DRAM1_BA0

DRAM1_BA1

DRAM1_BA2

8

1 DRAM0_A11

7 RP21 2 DRAM0_A2

6 4x22 3 DRAM0_A5H

5

4 DRAM0_A5

K3

L8

K7

L7

J8

K8

K2

C8

C2

D7

D3

D1

D9

B1

B9

DRAM0_DQS0

DRAM0_DQS0#

DRAM0_DM0

VssDL

C1_A0

C1_A1

C1_A2

C1_A3

C1_A4

C1_A5

C1_A4H

C1_A5H

C1_A6

C1_A7

C1_A8

C1_A9

C1_A10

C1_A11

C1_A12

C1_A13

C0_A11

C0_A2

C0_A5H

C0_A5

DRAM0_WE#

DRAM0_CS#

DRAM0_RAS#

DRAM0_CAS#

DRAM0_CLK

DRAM0_CLK#

DRAM0_CLKE

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DRAM0_D0

DRAM0_D1

DRAM0_D2

DRAM0_D3

DRAM0_D4

DRAM0_D5

DRAM0_D6

DRAM0_D7

J7

D14

A15

E16

F18

B15

E17

F14

F16

C15

D18

E15

C18

B16

C16

F17

F15

8

1 DRAM0_A4H

7 RP19 2 DRAM0_A6

6 4x22 3 DRAM0_A8

5

4 DRAM0_A13

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

DRAM1_A0

DRAM1_A1

DRAM1_A2

DRAM1_A3

DRAM1_A4

DRAM1_A5

DRAM1_A4H

DRAM1_A5H

DRAM1_A6

DRAM1_A7

DRAM1_A8

DRAM1_A9

DRAM1_A10

DRAM1_A11

DRAM1_A12

DRAM1_A13

C0_A4H

C0_A6

C0_A8

C0_A13

DRAM0_BA0

DRAM0_BA1

DRAM0_BA2

F7

E8

F3

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

C0_ODT

8

1 DRAM0_CS#

7 RP17 2 DRAM0_RAS#

6 4x22 3 DRAM0_A0

5

4 DRAM0_CAS#

LDQS

LDQS#

LDM

32Mx16 DDR2 266MHz

F2

B8

D8

E7

D2

B2

H8

H2

A7

F8

K30

AA27

U24

P24

L24

G27

Bottom

C0_CS#

C0_RAS#

C0_A0

C0_CAS#

G8

G2

H7

H3

H1

H9

F1

F9

DRAM0_A0

DRAM0_A1

DRAM0_A2

DRAM0_A3

DRAM0_A4H

DRAM0_A5H

DRAM0_A6

DRAM0_A7

DRAM0_A8

DRAM0_A9

DRAM0_A10

DRAM0_A11

DRAM0_A12

DRAM0_A13

J1

DRAM0_ODT

DRAM0_VREF0

DRAM0_VREF1

DRAM0_VREF2

DRAM0_VREF3

DRAM0_VREF4

DRAM0_DM0

DRAM0_DM1

DRAM0_DM2

DRAM0_DM3

DRAM0_ODT

FBGA84

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

VddL

W26

AB29

K28

H28

22

U11

VssDL

DRAM0_DM0

DRAM0_DM1

DRAM0_DM2

DRAM0_DM3

R44

Vcc1V8

J7

M30 C0_CLK

L30 C0_CLK#

C0_ODT

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10(AP)

A11

A12

A13

rfu

rfu

BA0

BA1

BA2

Vss

Vss

Vss

Vss

Vss

DRAM0_CK

DRAM0_CK#

1

8 DRAM0_BA2

2 RP20 7 DRAM0_BA1

3 4x22 6 DRAM0_CLKE

4

5 DRAM0_WE#

C0_BA2

C0_BA1

C0_CLKE

C0_WE#

M8

M3

M7

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

A3

J3

N1

E3

P9

C0_WE#

C0_CAS#

C0_RAS#

C0_CS#

C0_CLKE

1

8 DRAM0_A4

2 RP18 7 DRAM0_A1

3 4x22 6 DRAM0_A10

4

5 DRAM0_BA0

C0_A4

C0_A1

C0_A10

C0_BA0

C7

G1

G7

C9

A9

G3

C3

C1

E9

G9

U29

M28

L28

L27

T30

DRAM0_A0

DRAM0_A1

DRAM0_A2

DRAM0_A3

DRAM0_A4

DRAM0_A5

DRAM0_A6

DRAM0_A7

DRAM0_A8

DRAM0_A9

DRAM0_A10

DRAM0_A11

DRAM0_A12

DRAM0_A13

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

VddQ

DRAM0_WE#

DRAM0_CAS#

DRAM0_RAS#

DRAM0_CS#

DRAM0_CKE

DRAM0_CLK

DRAM0_CLK#

A1

J9

E1

M9

R1

C0_BA0

C0_BA1

C0_BA2

22

22

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

VssQ

DRAM1_DQS0

DRAM1_DQS0#

DRAM1_DQS1

DRAM1_DQS1#

DRAM1_DQS2

DRAM1_DQS2#

DRAM1_DQS3

DRAM1_DQS3#

R28

R30

R29

U10

Top

R42

R43

C0_CLK

C0_CLK#

0.1uF C194

C20

B20

B23

A23

D11

E11

A8

B8

DRAM0_BA0

DRAM0_BA1

DRAM0_BA2

Vcc1V8

F2

B8

D8

E7

D2

B2

H8

H2

A7

F8

DRAM1_DQS0

DRAM1_DQS0#

DRAM1_DQS1

DRAM1_DQS1#

DRAM1_DQS2

DRAM1_DQS2#

DRAM1_DQS3

DRAM1_DQS3#

DRAM1_DQ0

DRAM1_DQ1

DRAM1_DQ2

DRAM1_DQ3

DRAM1_DQ4

DRAM1_DQ5

DRAM1_DQ6

DRAM1_DQ7

DRAM1_DQ8

DRAM1_DQ9

DRAM1_DQ10

DRAM1_DQ11

DRAM1_DQ12

DRAM1_DQ13

DRAM1_DQ14

DRAM1_DQ15

DRAM1_DQ16

DRAM1_DQ17

DRAM1_DQ18

DRAM1_DQ19

DRAM1_DQ20

DRAM1_DQ21

DRAM1_DQ22

DRAM1_DQ23

DRAM1_DQ24

DRAM1_DQ25

DRAM1_DQ26

DRAM1_DQ27

DRAM1_DQ28

DRAM1_DQ29

DRAM1_DQ30

DRAM1_DQ31

C0_A0

C0_A1

C0_A2

C0_A3

C0_A4

C0_A5

C0_A4H

C0_A5H

C0_A6

C0_A7

C0_A8

C0_A9

C0_A10

C0_A11

C0_A12

C0_A13

Vdd

Vdd

Vdd

Vdd

Vdd

F19

E22

E20

D21

C22

E19

F21

D19

C21

B25

C23

A24

A26

A21

C24

B22

D10

F13

F12

E12

E13

E10

B12

F11

B7

C11

B9

A9

A11

A6

B10

C8

M27

N30

P26

T25

N29

R26

M25

P25

N28

T27

N26

T28

P29

P28

R25

N25

C38

DRAM1_D0

DRAM1_D1

DRAM1_D2

DRAM1_D3

DRAM1_D4

DRAM1_D5

DRAM1_D6

DRAM1_D7

DRAM1_D8

DRAM1_D9

DRAM1_D10

DRAM1_D11

DRAM1_D12

DRAM1_D13

DRAM1_D14

DRAM1_D15

DRAM1_D16

DRAM1_D17

DRAM1_D18

DRAM1_D19

DRAM1_D20

DRAM1_D21

DRAM1_D22

DRAM1_D23

DRAM1_D24

DRAM1_D25

DRAM1_D26

DRAM1_D27

DRAM1_D28

DRAM1_D29

DRAM1_D30

DRAM1_D31

DRAM0_DQS0

DRAM0_DQS0#

DRAM0_DQS1

DRAM0_DQS1#

DRAM0_DQS2

DRAM0_DQS2#

DRAM0_DQS3

DRAM0_DQS3#

DRAM0_A0

DRAM0_A1

DRAM0_A2

DRAM0_A3

DRAM0_A4

DRAM0_A5

DRAM0_A4H

DRAM0_A5H

DRAM0_A6

DRAM0_A7

DRAM0_A8

DRAM0_A9

DRAM0_A10

DRAM0_A11

DRAM0_A12

DRAM0_A13

C37

DRAM0_DQS0

V28

DRAM0_DQS0# V29

DRAM0_DQS1 AA29

DRAM0_DQS1# AA30

DRAM0_DQS2

J27

DRAM0_DQS2# J26

DRAM0_DQS3

F30

DRAM0_DQS3# F29

DRAM0_DQ0

DRAM0_DQ1

DRAM0_DQ2

DRAM0_DQ3

DRAM0_DQ4

DRAM0_DQ5

DRAM0_DQ6

DRAM0_DQ7

DRAM0_DQ8

DRAM0_DQ9

DRAM0_DQ10

DRAM0_DQ11

DRAM0_DQ12

DRAM0_DQ13

DRAM0_DQ14

DRAM0_DQ15

DRAM0_DQ16

DRAM0_DQ17

DRAM0_DQ18

DRAM0_DQ19

DRAM0_DQ20

DRAM0_DQ21

DRAM0_DQ22

DRAM0_DQ23

DRAM0_DQ24

DRAM0_DQ25

DRAM0_DQ26

DRAM0_DQ27

DRAM0_DQ28

DRAM0_DQ29

DRAM0_DQ30

DRAM0_DQ31

C36

U25

Y26

V26

W27

Y28

U26

W25

U27

W28

AC29

AA28

AB30

AD30

W30

AB28

Y29

H27

L25

K25

K26

L26

H26

K29

J25

E29

J28

G29

G30

J30

D30

H29

F28

C35

DRAM0_D0

DRAM0_D1

DRAM0_D2

DRAM0_D3

DRAM0_D4

DRAM0_D5

DRAM0_D6

DRAM0_D7

DRAM0_D8

DRAM0_D9

DRAM0_D10

DRAM0_D11

DRAM0_D12

DRAM0_D13

DRAM0_D14

DRAM0_D15

DRAM0_D16

DRAM0_D17

DRAM0_D18

DRAM0_D19

DRAM0_D20

DRAM0_D21

DRAM0_D22

DRAM0_D23

DRAM0_D24

DRAM0_D25

DRAM0_D26

DRAM0_D27

DRAM0_D28

DRAM0_D29

DRAM0_D30

DRAM0_D31

SIGMA DESIGNS CONFIDENTIAL

Title

Sigma Designs

SMP8654 Dev Board

1778 McCarthy Blvd Size

C

Milpitas CA 95035

Date:

Document Number

Rev

53-000922-01

Monday, January 19, 2009

Sheet

E

A3a

4

of

15

NAND #0

Flash

NAND #1

Flash

U7E

Vcc3V3

Vcc3V3

NAND SLC

PB_D7

PB_D6

PB_D5

PB_D4

PB_D3

PB_D2

PB_D1

PB_D0

AF30

AF29

AF27

AE29

AE28

AE27

AE26

AD28

PB_D7

PB_D6

PB_D5

PB_D4

PB_D3

PB_D2

PB_D1

PB_D0

PB_D7

PB_D6

PB_D5

PB_D4

PB_D3

PB_D2

PB_D1

PB_D0

44

43

42

41

32

31

30

29

I/O7

I/O6

I/O5

I/O4

I/O3

I/O2

I/O1

I/O0

PB_CLE

PB_ALE

PB_WR#

AC25

AB25

AC27

PB_CLE

PB_ALE

PB_WR#

PB_CLE

PB_ALE

PB_WR#

PB_IORDY

PB_RD#

PB_CS0#

PB_CS1#

AC26

AD25

AD26

AD27

PB_IORDY

PB_RD#

PB_CS0#

PB_CS1#

16

17

18

19

7

8

9

CLE

ALE

WE

WP

R/B

RE

CE

Vcc3V3

NAND_RDY

PB_RD#

NAND0_CS#

SMP8654

00

PB_CS1#

NAND0_CS#

R307

xx_10K

R309

SPI0_CS#

xx_10K

R310

00

R311

NAND1_CS#

xx_10K

R312

xx

R313

SPI1_CS#

xx_10K

R314

Vcc3V3

36

13

VSS

VSS

44

43

42

41

32

31

30

29

I/O7

I/O6

I/O5

I/O4

I/O3

I/O2

I/O1

I/O0

PB_CLE

PB_ALE

PB_WR#

16

17

18

19

7

8

9

CLE

ALE

WE

WP

R/B

RE

CE

NAND_RDY

PB_RD#

NAND1_CS#

TSOP48

TSOP48

7

3

2

5

6

1

HOLD#

WP#

SO

SI

SCK

CS#

VCC

Vcc3V3

GND

PB_IORDY

00

R59

PB_D3

PB_D2

PB_D1

PB_D0

PB_RD#

SPI0_CS#

NAND_RDY

TESTING ONLY

J16

PB_D0

PB_D1

PB_D2

PB_D3

PB_D4

PB_D5

PB_D6

PB_D7

PB_CLE

PB_ALE

NAND_RDY

1

3

5

7

9

11

13

15

17

19

21

2

4

6

8

10

12

14

16

18

20

22

PB_WR#

PB_RD#

PB_CS0#

PB_CS1#

7

3

2

5

6

1

HOLD#

WP#

SO

SI

SCK

CS#

VSS

VSS

36

13

7

3

2

5

6

1

VCC

GND

SPI Flash

200mil SOIC8

Vcc3V3

HOLD#

WP#

SO

SI

SCK

CS#

VCC

GND

SPI Flash

150mil SOIC8

Vcc3V3

U52A

10K

12

37

U53

PB_D3

PB_D2

PB_D1

PB_D0

PB_RD#

SPI1_CS#

SPI Flash

150mil SOIC8

R57

VCC

VCC

Vcc3V3

U52

PB_D3

PB_D2

PB_D1

PB_D0

PB_RD#

SPI0_CS#

PB_D7

PB_D6

PB_D5

PB_D4

PB_D3

PB_D2

PB_D1

PB_D0

U15

R308

xx

NAND SLC

12

37

VCC

VCC

U14

Vcc3V3

PB_CS0#

Vcc3V3

U53A

PB_D3

PB_D2

PB_D1

PB_D0

PB_RD#

SPI1_CS#

7

3

2

5

6

1

HOLD#

WP#

SO

SI

SCK

CS#

VCC

8

2

GND

SPI Flash

200mil SOIC8

RESERVED FOR FUTURE USE

HDR2x11

SIGMA DESIGNS CONFIDENTIAL

Title

Sigma Designs

SMP8654 Dev Board

1778 McCarthy Blvd Size

B

Milpitas CA 95035

Date:

A

Document Number

Rev

53-000922-01

Monday, January 19, 2009

A3a

Sheet

E

of

15

PCI HOST/Device

CONTROLER

PCI_AD[0..31]

T9

PCI_CLK

PCI_FRAME#

PCI_TRDY#

PCI_IRDY#

PCI_STOP#

PCI_DEVSEL#

AE23

AF23

AH23

AJ24

AJ23

PCI_FRAME#

PCI_TRDY#

PCI_IRDY#

PCI_STOP#

PCI_DEVSEL#

PCI_IDSEL0

PCI_IDSEL1

PCI_IDSEL2

AE20

AE21

AF21

PCI_IDSEL0

PCI_IDSEL1

PCI_IDSEL2

AK18

AJ18

AH18

PCI_GNT#0

PCI_GNT#1

PCI_GNT#2

PCI_GNT#0

1

PCI_PAR

AK17

PCI_REQ#0

PCI_REQ#1

PCI_REQ#2

PCI_REQ#0

T3

PCI_CLK

PCI_CBE0#

PCI_CBE1#

PCI_CBE2#

PCI_CBE3#

AF17

AF18

AE18

PCI_PAR

AH24

PCI_CBE0#

PCI_CBE1#

PCI_CBE2#

PCI_CBE3#

AJ27

AK24

AG23

AK20

PCI_INTA#

AG17

PCI_REQ0#

PCI_REQ1#

PCI_REQ2#

PCI_GNT0#

PCI_GNT1#

PCI_GNT2#

PCI_PAR

PCI_CBE0#

PCI_CBE1#

PCI_CBE2#

PCI_CBE3#

PCI_INTA#

Vcc5V

R61

00

R62

x_0

PC-PCI_CLK

PCI_GNT#0

PCI_AD[31:0]

PCI_AD31

PCI_AD29

PCI_AD27

PCI_AD25

PCI_CBE3#

PCI_AD23

PCI_AD21

PCI_AD19

PCI_AD17

PCI_CBE2#

8 RP42 1

7

2

6

3

5

4

4x10K

PCI_IRDY#

PCI_INTA#

PCI_INT#

PCI_DEVSEL#

PCI_FRAME#

PCI_IRDY#

PCI_TRDY#

PCI_STOP#

PCI_DEVSEL#

8 RP44 1

7

2

6

3

5

4

4x10K

PCI_REQ#0

PCI_REQ#1

PCI_REQ#2

U47D

PCI_CBE1#

PCI_AD14

8

74LCX04

PCI_AD12

PCI_AD10

U47E

11

10

74LCX04

14

7

8 RP43 1

7

2

6

3

5

4

4x10K

PCI_AD8

PCI_AD7

U47F

12

74LCX04

PCI_AD5

PCI_AD3

13

PCI_AD1

Used for PCI Device only.

2

74LCX04

14 7

RCLK0_33M

HOSTMODE

U47B

4

74LCX04

14

7

-12V

TCK

GND

TDO

+5V

+5V

INTB

INTD

PRSNT1

RESERVED

PRSNT2

KEYWAY

KEYWAY

RESERVED

GND

CLK

GND

REQ

Vio

AD31

AD29

GND

AD27

AD25

+3.3V

C/BE3

AD23

GND

AD21

AD19

+3.3V

AD17

C/BE2

GND

IRDY

+3.3V

DEVSEL

GND

LOCK

PERR

+3.3V

SERR

+3.3V

C/BE1

AD14

GND

AD12

AD10

M66EN/GND

KEYWAY

KEYWAY

AD8

AD7

+3.3V

AD5

AD3

GND

AD1

Vio

ACK64

+5V

+5V

TRST

+12V

TMS

TDI

+5V

INTA

INTC

+5V

RESERVED

Vio

RESERVED

KEYWAY

KEYWAY

RESERVED

RST

Vio

GNT

GND

RESERVED

AD30

+3.3V

AD28

AD26

GND

AD24

IDSEL

+3.3V

AD22

AD20

GND

AD18

AD16

+3.3V

FRAME

GND

TRDY

GND

STOP

+3.3V

SDONE

SBO

GND

PAR

AD15

+3.3V

AD13

AD11

GND

AD9

KEYWAY

KEYWAY

C/BE0

+3.3V

AD6

AD4

GND

AD2

AD0

Vio

REQ64

+5V

+5V

H2

PI3B3257

1

2

3

5

6

11

10

14

13

S

1A

1B

2A

2B

3A

3B

4A

4B

VDD

15

EN

VSS

H1

16

1Y

2Y

3Y

4Y

12

22

R70

PCI_CLK

22

R71

PCI_CLK1

To PCI slot

22

R315

PCI_CLK0

To MiniPCI

slot

H2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

PCI_INT#

PCI_INT#

Vcc5V

Vcc12V

PCI_INTA#

PCI_CLK1

PCI_REQ#1

PCI_AD31

PCI_AD29

PC-PCI_RST#

33

R63

C86

PCI_AD27

PCI_AD25

10pF

PCI_REQ#0

PCI_AD30

PCI_CBE3#

PCI_AD23

PCI_AD[31:0]

PCI_AD28

PCI_AD26

PCI_AD21

PCI_AD19

PCI_AD24

PCI_IDSEL0

PCI_AD17

PCI_CBE2#

PCI_AD22

PCI_AD20

PCI_IRDY#

Vcc3V3

PCI_AD18

PCI_AD16

PCI_DEVSEL#

R64

R65

10K

10K

R66

10K

PCI_LOCK#

PCI_PERR#

PCI_FRAME#

PCI_SERR#

PCI_TRDY#

PCI_CBE1#

PCI_AD14

PCI_STOP#

Vcc3V3

PCI_AD12

PCI_AD10

R67 10K

PCI_PAR

PCI_AD15

PCI_AD8

PCI_AD7

PCI_AD13

PCI_AD11

PCI_AD5

PCI_AD3

PCI_AD9

Vcc3V3

PCI_AD1

PCI_CBE0#

R68

10K

PCI_AD6

PCI_AD4

Vcc3V3

-12V

TRST

TCK

+12V

GND1

TMS

TDO

TDI

+5V1

+5V7

+5V2

INTA

INTC

INTB

INTD

+5V8

PRSNT1

RSV3

RSV1

+5V9

PRSNT2

RSV4

GND2

GND13

GND3

GND14

RSV2

RSV5

GND4

RST

+5V10

CLK

GNT

GND5

GND15

REQ

+5V3

RSV6

AD31

AD30

AD29

+3.3V7

GND6

AD28

AD27

AD26

AD25

GND16

+3.3V1

AD24

CBE3

IDSEL

AD23

+3.3V8

GND7

AD22

AD21

AD20

AD19

GND17

+3.3V2

AD18

AD17

AD16

CBE2

+3.3V9

GND8

FRAME

GND18

IRDY

+3.3V3

TRDY

GND19

DEVSEL

GND9

STOP

+3.3V10

LOCK

PERR

SDONE

+3.3V4

SBO

GND20

SERR

+3.3V5

PAR

CBE1

AD15

AD14

+3.3V11

GND10

AD13

AD12

AD11

AD10

GND21

GND11/M66EN AD09

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

AD08

AD07

+3.3V6

AD05

AD03

GND12

AD01

+5V4

ACK64

+5V5

+5V6

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

CBEO

+3.3V12

AD06

AD04

GND22

AD02

AD00

+5V11

REQ64

+5V12

+5V13

Vcc12V

Vcc5V

PCI_INT#

D

AUX_RESET#

PCI_GNT#1

PCI_AD30

PCI_AD28

PCI_AD26

PCI_AD24

PCI_IDSEL1

PCI_AD22

PCI_AD20

PCI_AD18

PCI_AD16

PCI_FRAME#

PCI_TRDY#

PCI_STOP#

PCI_PAR

PCI_AD15

PCI_AD13

PCI_AD11

PCI_AD9

PCI_CBE0#

PCI_AD6

PCI_AD4

B

PCI_AD2

PCI_AD0

Vcc3V3

PCI_REQ64#

10K

R69

PCI_AD2

PCI_AD0

PCI slot (Host)

PCI_SERR#

PCI_PERR#

PCI_SERR#

PCI_PERR#

SIGMA DESIGNS CONFIDENTIAL

Title

Sigma Designs

U17

6

74LCX04

SMP8654 Dev Board

1778 McCarthy Blvd Size

B

Milpitas CA 95035

Date:

PCI BUS

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

To Tango3

U47C

PC-PCI_CLK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

PCI-A

H1

Vcc3V3

14

Vcc3V3

U47A

J18

Vcc5V

PCI-B

SMP8654

Vcc3V3

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

AG30

AH30

AH29

AJ29

AJ28

AK28

AH27

AK27

AK26

AH26

AJ26

AF25

AH25

AG25

AJ25

AF24

AH22

AK22

AF22

AJ22

AE22

AJ21

AG21

AH21

AF20

AJ20

AH20

AJ19

AF19

AH19

AE19

AG19

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

14

PCI_IDSEL0

Vcc3V3

32bit 5V/3V3 PCI board edge

14

7

PCI_AD[0..31]

U7C

PCI_FRAME#

PCI_TRDY#

PCI_IRDY#

PCI_STOP#

PCI_DEVSEL#

Document Number

Rev

53-000922-01

Monday, January 19, 2009

A3a

Sheet

1

of

15

PCI_AD[0..31]

Use for Ralink b/g/n

MII card only

or MiniPCI

Wireless card

U7J

ETH0_TXCLK

ETH0_TX_EN

ETH0_TX_ER

ETH0_TXD3

ETH0_TXD2

ETH0_TXD1

ETH0_TXD0

AG1

AJ3

AJ1

AH2

AH1

AG3

AG2

ETH0_RXCLK

ETH0_RX_DV

ETH0_RX_ER

ETH0_RXD3

ETH0_RXD2

ETH0_RXD1

ETH0_RXD0

AF4

AE4

AE2

AF3

AF2

AF1

AE5

ETH0_CRS

ETH0_COL

ETH0_MDC

ETH0_MDIO

ETH0_MDINT#

AE3

AK2

AE1

AD6

AD5

ETH1_TXCLK

ETH1_TX_EN

ETH1_TX_ER

ETH1_TXD3

ETH1_TXD2

ETH1_TXD1

ETH1_TXD0

AG6

AF7

AG7

AH7

AJ7

AK7

AF6

ETH1_RXCLK

ETH1_RX_DV

ETH1_RX_ER

ETH1_RXD3

ETH1_RXD2

ETH1_RXD1

ETH1_RXD0

AH6

AJ5

AH4

AJ6

AK6

AG5

AH5

ETH1_CRS

ETH1_COL

ETH1_MDC

ETH1_MDIO

ETH1_MDINT#

AK5

AE7

AJ4

AK4

AK3

SMP8654

22

R72

1

RP64 2

4x22 3

4

8

7

6

5

E0_TXC

E0_TXEN

E0_TXER

E0_TXD3

E0_TXD2

E0_TXD1

E0_TXD0

J19

E0_RXD3

E0_RXD2

E0_RXD0

E0_RXER

E0_TXC

E0_TXD0

E0_TXD2

E0_MDIO

E0_MDINT#

E0_TXD[3:0]

E0_RXC

E0_RXDV

E0_RXER

E0_RXD3

E0_RXD2

E0_RXD1

E0_RXD0

E0_MDINT#

PCI_FRAME#

PCI_TRDY#

PCI_IRDY#

PCI_STOP#

PCI_DEVSEL#

TESTING ONLY

1

3

5

7

9

11

13

15

17

19

E0_RXD[3:0]

E0_CRS

E0_COL

E0_MDC

E0_MDIO

E0_COL

E0_CRS

E0_RXD1

E0_RXDV

E0_RXC

E0_TXER

E0_TXEN

E0_TXD1

E0_TXD3

E0_MDC

2

4

6

8

10

12

14

16

18

20

R73

1K

R74

22

1

RP65 2

4x22 3

4

E1_TXC

E1_TXER

E1_TXEN

E1_RXC

E1_RXDV

E1_CRS

E1_COL

E1_MDC

E1_MDIO

E1_MDINT#

Vcc3V3

R75

E1_TXC

E1_TXEN

E1_TXER

8 E1_TXD3

7 E1_TXD2

6 E1_TXD1

5 E1_TXD0

1

3

5

7

9

11

13

15

17

19

PCI_AD31

PCI_AD29

E1_TXD3

E1_TXD2

E1_TXD1

E1_TXD0

E1_RXER

E1_RXD3

E1_RXD2

E1_RXD1

E1_RXD0

2

4

6

8

10

12

14

16

18

20

PCI_AD27

PCI_AD25

E1_MDC

PCI_CBE3#

PCI_AD23

PCI_AD21

PCI_AD19

HDR2x10

PCI_AD17

PCI_CBE2#

PCI_IRDY#

E1_TXD[3:0]

E1_RXC

E1_RXDV

E1_RXD3

E1_RXD2

E1_RXD1

E1_RXD0

10K

R297

E1_RXER

E1_RXD[3:0]

E1_CRS

E1_COL

E1_MDINT#

10K

R76

1K

R77

PCI_SERR#

PCI_PERR#

10K

10K

PCI_CLK0

PCI_REQ#0

J21

R298

R299

PCI_SERR#

PCI_PERR#

PCI_CBE1#

PCI_AD14

PCI_AD12

PCI_AD10

E1_MDC

E1_MDIO

PCI_AD8

PCI_AD7

Vcc3V3

PCI_AD5

E1_MDIO

PCI_AD3

Vcc3V3

TESTING ONLY

PCI_AD1

SEG-A

4

RN1903

E1_TXEN

E1_RXDV

E1_TXD0

E1_TXD1

E1_TXD2

SEG-B

Q2

E1_TXD3

1

SEG-F

E1_TXC

E1_TXEN

E1_TXD0

E1_TXD1

1

2

3

4

E1_TXD2

E1_TXD3

E1_MDC

E1_MDIO

1

2

3

4

8

7 RP45

6 4x00

5

SEG-A

SEG-B

SEG-C

SEG-D

8

7 RP46

6 4x00

5

SEG-E

SEG-F

SEG-G

SEG-DP

4

RN1903

SEG-C

SEG-G

Q3

SEG-E

SEG-D

1

2

3

4

1

2

3

4

8

7

6

5

8

7

6

5

10

9

2

3

8

RP48

4

4x100 5

7

RP47

4x100

A

B

F

G

C F

E

D E

DP

E1_TXC

1

6

VDD

VDD

TIP

RING

KEY

KEY

RD+

TD+

RDTDRJ45Tmn7

RJ45Tmn4

RJ45Tmn8

RJ45Tmn5

LED1_GRNP

LED2_YELP

LED1_GRNN

LED2_YELN

CHSGND

RESERVED5

INTB#

5V2

3.3V1

INTA#

RESERVED1

RESERVED6

GND1

3.3VAUX1

CLK

RST#

GND2

3.3V5

REQ#

GNT#

3.3V2

GND10

AD[31]

PME#

AD[29]

RESERVED7

GND3

AD[30]

AD[27]

3.3V6

AD[25]

AD[28]

RESERVED2

AD[26]

C/BE[3]#

AD[24]

AD[23]

IDSEL

GND4

GND11

AD[21]

AD[22]

MINI-PCI CONN

AD[19]

AD[20]

GND5

PAR

TYPE III

AD[17]

AD[18]

C/BE[2]#

AD[16]

(2 X 62)

IRDY#

GND12

3.3V3

FRAME#

CLKRUN#

TRDY#

SERR#

STOP#

GND6

3.3V7

PERR#

DEVSEL#

C/BE[1]#

GND13

AD[14]

AD[15]

GND7

AD[13]

AD[12]

AD[11]

AD[10]

GND14

GND8

AD[09]

AD[08]

C/BE[0]#

AD[07]

3.3V8

3.3V4

AD[06]

AD[05]

AD[04]

RESERVED3

AD[02]

AD[03]

AD[00]

5V1

RESERVED_WIP1

AD[01]

RESERVED_WIP2

GND9

GND15

AC_SYNC

M66EN

AC_SDADA_IN

AC_SDATA_OUT

AC_BIT_CLK

AC_CODEC_ID0#

AC_CODEC_ID1#

AC_RESET#

MOD_AUDIO_MON

RESERVED8

AUDIO_GND1

GND16

SYS_AUDIO_OUT

SYS_AUDIO_IN

SYS_AUDIO_OUT_GND

SYS_AUDIO_IN_GND

AUDIO_GND2

AUDIO_GND3

RESERVED4

MPCIACT#

VCC5VA

3.3VAUX2

AMP 440145-1

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

RESET#

RESET#

PCI_INT#

00

R316

AUX_RESET#2

PCI_GNT#0

PCI_AD30

PCI_AD28

PCI_AD26

PCI_AD24

PCI_IDSEL0

PCI_AD22

PCI_AD20

PCI_PAR

PCI_AD18

PCI_AD16

PCI_FRAME#

PCI_TRDY#

PCI_STOP#

PCI_DEVSEL#

PCI_AD15

PCI_AD13

PCI_AD11

PCI_AD9

PCI_CBE0#

PCI_AD6

PCI_AD4

PCI_AD2

PCI_AD0

E1_RXD0

E1_RXD1

E1_RXD2

E1_RXD3

E1_RXC

Vcc3V3

1K

1K

R279

R280

B

C

DP

A

SIGMA DESIGNS CONFIDENTIAL

SEG-DP

Title

Sigma Designs

SMP8654 Dev Board

1778 McCarthy Blvd Size

B

Milpitas CA 95035

Q5

Date:

5

Q4

RN1903

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

A

G

Vcc3V3

LDS-A324RI

RN1903

Vcc5V

J22

Vcc5V

J20

PCI_INT#

PCI_CLK0

Vcc3V3

Vcc3V3

PCI_CBE0#

PCI_CBE1#

PCI_CBE2#

PCI_CBE3#

TESTING ONLY

10K

Vcc5V

PCI_IDSEL0

PCI_REQ#0

PCI_GNT#0

PCI_PAR

HDR2x10

PCI_AD[0..31]

127 TAB

128 TAB

Document Number

Rev

53-000922-01

Monday, January 19, 2009

A3a

Sheet

1

of

15

J85

FPC12

Vcc12V

RESET#

AUDVAA

1

HDD5V

Vcc5V

Vcc3V3

Vcc1V8

Vcc1V0

13

12

11

10

9

8

7

6

5

4

3

2

1

16

13

12

11

10

9

8

7

6

5

4

3

2

1

16

14

15

14

Vcc3V3

VSS_PLL1

VSS_PLL2

H6

H5

Vcc3V3

AE17

AE24

AE30

AE9

AF26

AF5

AG18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG22

AG26

AG28

AH10

AH11

AH12

AH17

AH28

AH3

AH9

AK19

AK23

AK8

B14

B2

B21

B6

C19

C25

C28

C9

D12

D16

D22

D8

E23

E30

F10

F20

F22

F3

F6

G10

G15

G17

G22

G24

G28

H10

H12

H14

H16

H18

H21

H22

H23

H25

H3

H8

Vcc3V3

0.1uF C339

0.1uF C338

0.1uF C337

0.1uF C336

0.1uF C335

0.1uF C334

0.1uF C333

0.1uF C332

L8

BEAD

0.1uF C348

0.1uF C347

Vcc3V3

VccPLL12

0402 size

0.1uF C346

SMP8654

0.1uF C345

C85

0.1uF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

0402 size

Vcc1V8

No

connection

to VSS !

SIGMA DESIGNS CONFIDENTIAL

Title

Sigma Designs

15

SMP8654 Dev Board

Date:

AD19

AD20

AD21

AD24

AD7

AE10

AE12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1778 McCarthy Blvd Size

B

Milpitas CA 95035

A

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SMP8654

J5

J6

SMP8654

A19

A25

A7

AA11

AA12

AA15

AA16

AA19

AA20

AA23

AA24

AA26

AA6

AA7

AB1

AB2

AB23

AB5

AB6

AB8

AC13

AC14

AC17

AC18

AC22

AC23

AC28

AC30

AC8

AC9

AD10

AD11

AD12

SMP8654

0.1uF C344

VDD_PLL2_3V3

VDD_PLL1_3V3

L8

M8

R8

T8

U7

V5

V7

W5

W8

Y8

AE25

AG27

AJ2

AJ8

AJ17

AJ30

P27

P8

R10

R13

R14

R17

R18

R21

R24

R7

T10

T13

T14

T17

T18

T21

T23

T26

T6

T7

U11

U12

U15

U16

U19

U20

U28

U30

U6

U8

V11

V12

V15

V16

V19

V20

V23

V25

V4

V6

V8

W10

W13

W14

W17

W18

W21

W24

W29

W4

W6

W7

Y10

0.1uF C343

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

0.1uF C342

For Sigma use only

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

0.1uF C341

H7

L7

BEAD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

0.1uF C340

HDR1x2

VSS_PLL0

H9

J23

J29

J8

K11

K12

K15

K16

K19

K20

K23

K7

L7

L10

L13

L14

L17

L18

L21

M10

M13

M14

M17

M18

M21

M23

M26

M29

M7

N11

N12

N15

N16

N19

N20

N24

N8

P11

P12

P15

P16

P19

P20

P23

Y13

Y14

Y17

Y18

Y21

Y23

Y27

Y6

Y7

U7I

0.1uF C354

VccPLL0

1

2

J7

0.1uF C117

J58

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_PLL0_1V0

A10

A16

A20

A22

A5

AB27

AD29

B11

B13

B18

B26

C7

D15

D17

D20

D24

E14

E18

E28

E9

G11

G12

G14

G18

G20

G21

G26

H11

H13

H15

H17

H19

H20

H30

J24

K24

K27

L23

L29

M24

N23

N27

P30

R23

R27

T24

T29

U23

V24

V27

V30

W23

Y24

Y25

Y30

0.1uF C353

0.1uF C106

0.1uF C116

For current measurement

purpose only

AA25

AA8

AB24

AB26

AB3

AB4

AB7

AC10

AC11

AC12

AC15

AC16

AC19

AC20

AC21

AC24

AC7

AD17

AD18

AD22

AD23

AD8

AD9

AE6

AF28

AG20

AG24

AG29

AG4

AK21

AK25

AK29

B29

D27

D4

F25

G4

G7

G9

K8

Vcc1V0

VccPLL0

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

VDD_1V8

0.1uF C352

C96

0.1uF

0.1uF C105

0.1uF C115

0.1uF C114

0.1uF C113

0.1uF C112

0.1uF C111

0.1uF C110

0.1uF C109

0.1uF C108

0.1uF C107

Vcc3V3

R11

R12

R15

R16

R19

R20

T11

T12

T15

T16

T19

T20

U10

U13

U14

U17

U18

U21

V10

V13

V14

V17

V18

V21

W11

W12

W15

W16

W19

W20

Y11

Y12

Y15

Y16

Y19

Y20

0.1uF C351

C95

0.1uF

0.1uF C104

0.1uF C103

0.1uF C102

0.1uF C101

0.1uF C100

C99

0.1uF

C98

C97

0.1uF

0.1uF

0402 size

Vcc1V8

0402 size

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

0.1uF C350

C94

0.1uF

0402 size

Vcc3V3

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

VDD_1V0

U7K

Vcc1V8

C410

C93

0.1uF

AA10

AA13

AA14

AA17

AA18

AA21

K10

K13

K14

K17

K18

K21

L11

L12

L15

L16

L19

L20

M11

M12

M15

M16

M19

M20

N10

N13

N14

N17

N18

N21

P10

P13

P14

P17

P18

P21

U7L

Vcc1V0

0.1uF C118

C92

0.1uF

0.1uF C182

C91

0.1uF

0.1uF C181

C90

0.1uF

0.1uF C180

C89

0.1uF

0.1uF C179

C88

0.1uF

0.1uF C349

C87

0.1uF

Vcc1V0

U7H

Vcc1V0

10uF Cer

Document Number

Rev

53-000922-01

Monday, January 19, 2009

A3a

Sheet

E

of

15

J24

U7F

SHELL3

SHELL1

D2+

D2 Shield

D2D1+

D1 Shield

D1D0+

D0 Shield

D0CK+

CK Shield

CKCE Remote

NC

DDC CLK

DDC DATA

GND

+5V

HP DET

SHELL2

SHELL4

D36

L37

P7

N7

HDMI_AVDD_1V0

HDMI_AVDD_1V0

HDMI_TX1_P

HDMI_TX1_N

P1

P2

U5

V3

U3

T3

Y5

AA3

Y3

W3

VO1_AVDD

VO1_AVDD_U

VO1_AVDD_V

VO1_AVDD_Y

VO2_AVDD

VO2_AVDD_U

VO2_AVDD_V

VO2_AVDD_Y

T5

V2

U2

T2

VO1_AVSS

VO1_AVSS_U

VO1_AVSS_V

VO1_AVSS_Y

C395

CEC isolation at power off

L9

BEAD

L11

BEAD

47K

VO2_Y

VO2_U

VO2_V

W1

AA1

Y1

Vcc5V

F2

U4

0.1uF

C144

VO2_VREF

Y4

0.1uF

C145

VO1_RSET

T4

140

R108

VO2_RSET

AA4

0.1uF

C147

VO2_AVSS

VO2_AVSS_U

VO2_AVSS_V

VO2_AVSS_Y

AA5

AA2

Y2

W2

140

R111

0.1uF

C150

- Do not add any VIA on TMDS lines

- Traces should have 100ohm differential impedance for each pair.

- All 8 Traces must be equal length within 10 mils of each other

- Route traces over the GND plane

- Each pairs should have minimum 15 mils clearance between each other

and any copper plane

J25

RCA+DIN4 stacked

SVid-C

SVid-Y

S-Video

B

D30

Dual

D29

Dual

D28

Dual

75

22pF

3

4

L17

BEAD

Vcc3V3

L16

BEAD

SVid-C

Composite

L15

BEAD

CVBS

J26

L2

R2

Pb

1

3

L1

R1

Pr

S/PDIF

.

.

5

6

C151

22pF

L41

BEAD

C366

BEAD

C365

Pb

2

3

R117

C363

75

22pF

R115