Beruflich Dokumente

Kultur Dokumente

Lesson Plan-COMPUTER Architecture

Hochgeladen von

Debabala SwainOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lesson Plan-COMPUTER Architecture

Hochgeladen von

Debabala SwainCopyright:

Verfügbare Formate

SRM UNIVERSITY FACULTY OF ENGINEERING AND TECHNOLOGY SCHOOL OF COMPUTING DEPARTMENT OF CSE COURSE PLAN Course Code Course

Title Semester Course Time Location : : : : :

CS0207

Computer Organization and Architecture III July Nov 2009 S.R.M.E.C Tech Park

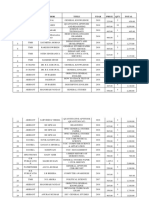

SECTION C Hour Timing 9.2010.10 a.m 1.302.20 p.m 8.309.20 a.m 10.2011.10 am Hour 6

Day Hour Monday 2

A Timing 9.2010.10 a.m 11.1012.00 noon 1.302.20 p.m 11.1012.00 noon Hour 2

B Timing 9.2010.10 a.m 9.2010.10 a.m 1.302.20 p.m 11.1012.00 noon

D Timing 2.203.10 1.302.10 8.309.20 8.309.20 Hour -

E Timing -

Tuesday

9.20-10.10 9.2010.10,2.203.10 1.30-2.20

Wednesday

2,6

Thursday

Friday

Faculty Details Sec. A B C D E Name C.Malathy K.Annapoorani Panaiyappan C.Lakshmi PRAVEEN.N Akilandeswari. Office Tech Park Tech Park Tech Park Tech Park Tech Park Office hour Tuesday-2nd hour & 4th hourWednesday-5th hour,Friday-4th hour Monday-2nd hour,Tuesday-2nd hour,Wednesday-5th hour,Friday-4th hour Tuesday-2nd hour Wednesday5th hour,Thursday-1 st hour,Friday-4th hour Monday - Friday Monday - Friday Mail id malathyc@cse.srmuniv.ac.in annapoorani@cse.srmuniv.ac.in lakshmi@cse.srmuniv.ac.in praveen@cse.srmuniv.ac.in akilandeswari@cse.srmuniv.ac.in

Required Text Books:

1. Carl Hamacher,Computer Organization,Fifth Edition,McGrawHill International Edition, 2002 2. P.Pal Chaudhuri, "Computer Organization and Design" , 2nd Edition, PHI 2003 3. William Stallings , Computer Organization and Architecture Designing for Performance, PHI, 2004. 4. John P.Hayes, "Computer Architecture and Organization", III Edition, McGraw Hill International Editions,1998.

Web resources

www.amazon.com www.freebookcentre.com

Prerequisite Objectives : CS0102 Digital computer fundamentals

1. Gives a knowledge of various architectures 2. CPU, Control unit, I/O Processing 3. Memory and its types 4. Design of the above components

Assessment Details

Cycle Test I Surprise Test I Cycle Test II Surprise Test II Model Exam Test Schedule S.No. 1 2 3 Outcomes DATE

: : : : :

10 Marks 7 Marks 10 Marks 8 Marks 15 Marks

TEST Cycle Test - I Cycle Test - II Model Exam

TOPICS Unit I & II Unit III & IV All 5 units

DURATION 2 periods 2 periods 3 Hrs

Students who have successfully completed this course will have full understanding of the following concepts Course outcome To learn The basic functional units, operational concepts and Program outcome An ability to understand the basic functioning of computer. To understand the concepts of addressing modes a

The basic memory operations, addressing modes. Basic ALU functions (operations) Control unit design and memory and its types Input and output processing bus interface I/O interface Detailed Session Plan

To solve various ALU operations. To implement booth algorithm To understand various types of memory concepts I/O processing.

UNIT-I INTRODUCTION Evolution of Computer Systems-Computer Types-Functional units-Basic operational concepts-Bus structures-Memory location and addresses-memory operations- Addressing modes-Design of a computer system-Instruction and instruction sequencing, RISC versus CISC Sessi Time Teaching on Topics to be covered Ref Testing Method (min) Method No. Evolution of Computer Systems Group discussion 1 50 1,2 PPT Quiz Computer Types Objective type test 2 50 1,2 PPT Quiz 3 Functional units 50 1 PPT Quiz Basic operational concepts, Bus structures Quiz 4 50 1 PPT 5 6 7 8 9 RISC versus CISC Memory location and addresses-memory operations Addressing modes Design of a computer system Instruction and instruction sequencing 50 50 50 50 50 1,3 1,3 2 1,3 1,3 PPT PPT PPT PPT PPT Quiz Quiz Objective type test Quiz, Assignment Group discussion Group discussion

UNIT-II CENTRAL PROCESSING UNIT Introduction-Arithmetic Logic Unit - Fixed point arithmetic, floating point arithmetic-Execution of a complete instruction-Basic concepts of pipelining Introduction-Arithmetic Logic Unit Quiz 10 50 1,2 PPT Fixed point arithmetic Quiz 11 50 1,2 PPT Brain storming Fixed point arithmetic Quiz 12 50 1,2 PPT Surprise Test Floating point arithmetic Group discussion 13 50 1,2 PPT Quiz Floating point arithmetic Group discussion, Quiz 14 50 1,2 PPT Floating point arithmetic Quiz, Assignment 15 50 1,2 PPT Execution of a complete Quiz 16 50 1,2 PPT instruction 17 Basic concepts of pipelining 50 1,2 PPT Quiz

18 Basic concepts of pipelining 50 1,2 PPT Quiz UNIT-III CONTROL UNIT DESIGN Introduction-Control Transfer-Fetch cycle - Instruction Interpretation & Execution - Hardwired control Microprogrammed control

Introduction-Control Transfer 19 20 21 22 23 24 25 26 27 Fetch cycle Fetch cycle Instruction Interpretation & Execution Instruction Interpretation & Execution Hardwired control Hardwired control Microprogrammed control Microprogrammed control 50 50 50 50 50 50 50 50 50 2 2 2 1,2 1,2 1,2 1,2 1,2 1,2,3 BB,PPT BB,PPT BB,PPT BB,PPT BB,PPT BB,PPT BB,PPT BB,PPT BB,PPT

Quiz Group discussion Objective type test Quiz Group discussion Quiz Quiz Surprise Test Quiz Group discussion Quiz Quiz Group discussion Quiz Quiz Brain storming

UNIT-IV MEMORIES AND SUBSYSTEMS Semiconductor memory - Static and Dynamic -Associative memory- Cache memory- Virtual memorySecondary memories-Optical magnetic tape & magnetic disks & controllers Semiconductor memory- Static and Group discussion 28 50 1,2,3 BB Dynamic memory Assignment Static and Dynamic memory Group discussion 29 50 1,2,3 BB Quiz Associative memory Group discussion 30 50 1,2,3 BB Assignment Associative memory Group discussion 31 50 1,2,3 BB Assignment Cache memory Objective type test 32 50 1,2,3 BB Quiz Group discussion Virtual memory Quiz 33 50 1,2,3 BB Group discussion 34 35 36 Secondary memories-Optical magnetic tape Magnetic disks & controllers Magnetic disks & controllers 50 50 50 1,2,3 1,2,3 1,2,3 BB BB BB Objective type test Objective type test Quiz Group discussion

UNIT-V I/O PROCESSING Introduction-Data transfer techniques- Bus Interface- I/O Channel-I/O Processor, I/O devices -Direct memory access. 37 38 39 40 41 Introduction-Data transfer techniques Bus Interface I/O Channel I/O Processor I/O Processor 50 50 50 50 50 1,2 1,2 1,2 1,2 2,3 BB BB BB BB BB Group discussion Objective type test Brain storming Brain storming Surprise test

42 43 44 45

I/O devices I/O devices Direct memory access. Direct memory access. BB Black Board PP Power Point

50 50 50 50

2,3 2,3 1,2 1,2

BB BB BB BB

Quiz Assignment Assignment Brain storming Brain storming

Das könnte Ihnen auch gefallen

- COBOL Programming Interview Questions: COBOL Job Interview PreparationVon EverandCOBOL Programming Interview Questions: COBOL Job Interview PreparationBewertung: 4.5 von 5 Sternen4.5/5 (2)

- Computer-Controlled Systems: Theory and Design, Third EditionVon EverandComputer-Controlled Systems: Theory and Design, Third EditionBewertung: 3 von 5 Sternen3/5 (4)

- Modeling Embedded Systems and SoC's: Concurrency and Time in Models of ComputationVon EverandModeling Embedded Systems and SoC's: Concurrency and Time in Models of ComputationNoch keine Bewertungen

- UVCE CSE SyllabusDokument55 SeitenUVCE CSE Syllabusaryan171100% (2)

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationVon EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNoch keine Bewertungen

- Managing the Testing Process: Practical Tools and Techniques for Managing Hardware and Software TestingVon EverandManaging the Testing Process: Practical Tools and Techniques for Managing Hardware and Software TestingBewertung: 4 von 5 Sternen4/5 (8)

- A History of Microwave Filter Research, Design, and DevelopmentDokument15 SeitenA History of Microwave Filter Research, Design, and Developmentsanjeevsoni64Noch keine Bewertungen

- Cs0207 Computer Organization and Architecture 2013Dokument4 SeitenCs0207 Computer Organization and Architecture 2013Sharath Kumar KRNoch keine Bewertungen

- Vlsi Design ECE5014Dokument5 SeitenVlsi Design ECE5014SriramNoch keine Bewertungen

- Syllabus MecveDokument44 SeitenSyllabus MecveronpeterpNoch keine Bewertungen

- B.tech MDU Syllabus (CSE) 3yr "F" SchemeDokument24 SeitenB.tech MDU Syllabus (CSE) 3yr "F" SchemebtechkarloNoch keine Bewertungen

- 4.61 Computer EnggDokument54 Seiten4.61 Computer EnggChandani ShahNoch keine Bewertungen

- CS0207-COMPUTER ArchitectureDokument4 SeitenCS0207-COMPUTER ArchitectureRama Krishna BadiguntlaNoch keine Bewertungen

- BCADokument23 SeitenBCAsudhir_kmr1Noch keine Bewertungen

- SPPU TBSC CS Syllabus 2021 22 PDFDokument60 SeitenSPPU TBSC CS Syllabus 2021 22 PDFSHWETA GANGURDENoch keine Bewertungen

- Mtech Electronics Syllabus VTUDokument48 SeitenMtech Electronics Syllabus VTUmuqeetmmaNoch keine Bewertungen

- SCHEME - G Fifth Semester (CO)Dokument42 SeitenSCHEME - G Fifth Semester (CO)RazeenKhanNoch keine Bewertungen

- Savitribai Phule University T.Y.B.Sc. Computer Science SyllabusDokument46 SeitenSavitribai Phule University T.Y.B.Sc. Computer Science SyllabusDhiraj GawhaneNoch keine Bewertungen

- BTECH CSE 5th 6th Sem 2020 21Dokument29 SeitenBTECH CSE 5th 6th Sem 2020 21Rahul GoyalNoch keine Bewertungen

- Adikavi Nannaya University MCA Syllabus 2008-11Dokument66 SeitenAdikavi Nannaya University MCA Syllabus 2008-11Rachakonda Deepika100% (1)

- Calicut University ECE Scheme and Syllabus 2009Dokument132 SeitenCalicut University ECE Scheme and Syllabus 2009Akhil Paul VNoch keine Bewertungen

- CSE-S4-Syllabus-2K9-Calicut UniversityDokument21 SeitenCSE-S4-Syllabus-2K9-Calicut UniversityfazilfazNoch keine Bewertungen

- Proposed Syllabus by Zubair Khan Garhmukteshwar Bachelors of Computer Application Semester - Wise Breakup of CourseDokument47 SeitenProposed Syllabus by Zubair Khan Garhmukteshwar Bachelors of Computer Application Semester - Wise Breakup of Coursemominkhan7764Noch keine Bewertungen

- Me Eee Es R13Dokument42 SeitenMe Eee Es R13Revathy VijayanNoch keine Bewertungen

- B.tech (Computer Sci & Engg) 5th & 6th Sem Session 2009-10Dokument19 SeitenB.tech (Computer Sci & Engg) 5th & 6th Sem Session 2009-10Akhil ManglaNoch keine Bewertungen

- M.E Cse PDFDokument51 SeitenM.E Cse PDFLatha MugunthanNoch keine Bewertungen

- Btech Cse r2007 2008 SyllabusDokument106 SeitenBtech Cse r2007 2008 SyllabusSurya TejaNoch keine Bewertungen

- OS SyllabusDokument10 SeitenOS Syllabusneena joiceNoch keine Bewertungen

- BCADokument47 SeitenBCANitin Kumar VatsNoch keine Bewertungen

- Computer SC PDFDokument155 SeitenComputer SC PDFVipeesh ParameswaranNoch keine Bewertungen

- Computer Organization and ArchitectureDokument12 SeitenComputer Organization and ArchitectureYaseen 777Noch keine Bewertungen

- Cs1253-Operating Systems: Continuous Internal Assessment - IDokument1 SeiteCs1253-Operating Systems: Continuous Internal Assessment - IShanmugapriyaVinodkumarNoch keine Bewertungen

- Course Outline CSC 201 Computer Architecture AUG - DEC 2015Dokument3 SeitenCourse Outline CSC 201 Computer Architecture AUG - DEC 2015church123Noch keine Bewertungen

- SyllabusDokument44 SeitenSyllabusRekha ThomasNoch keine Bewertungen

- Lesson Plan: EE 2253 Control SystemsDokument6 SeitenLesson Plan: EE 2253 Control Systemsm_duraiNoch keine Bewertungen

- SE Syllabus DTUDokument152 SeitenSE Syllabus DTUMayukh MaitraNoch keine Bewertungen

- Production EngineeringDokument39 SeitenProduction EngineeringkeepingbusyNoch keine Bewertungen

- 4 CoeDokument46 Seiten4 Coe27296621Noch keine Bewertungen

- Handout of EEE F 313 (Analog Digital VLSI Design)Dokument3 SeitenHandout of EEE F 313 (Analog Digital VLSI Design)bits_who_am_iNoch keine Bewertungen

- Te CseDokument20 SeitenTe Csepritamalde3595Noch keine Bewertungen

- Visvesvaraya Technological University, Belgaum: Teaching Hours/weekDokument34 SeitenVisvesvaraya Technological University, Belgaum: Teaching Hours/weekpreethipreethiNoch keine Bewertungen

- Computer OrganisationDokument12 SeitenComputer OrganisationSachuNoch keine Bewertungen

- 2013 Regulation Syllabus ITDokument108 Seiten2013 Regulation Syllabus ITNagendra KumarNoch keine Bewertungen

- Introduction to Algorithms & Data Structures 3: Learn Linear Data Structures with Videos & Interview QuestionsVon EverandIntroduction to Algorithms & Data Structures 3: Learn Linear Data Structures with Videos & Interview QuestionsBewertung: 5 von 5 Sternen5/5 (1)

- Foundation Course for Advanced Computer StudiesVon EverandFoundation Course for Advanced Computer StudiesNoch keine Bewertungen

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsVon EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsNoch keine Bewertungen

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionVon EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionBewertung: 5 von 5 Sternen5/5 (4)

- Fundamentals of Computer Organization and ArchitectureVon EverandFundamentals of Computer Organization and ArchitectureBewertung: 5 von 5 Sternen5/5 (1)

- Real-Time UML Workshop for Embedded SystemsVon EverandReal-Time UML Workshop for Embedded SystemsBewertung: 3.5 von 5 Sternen3.5/5 (2)

- Product Performance Evaluation using CAD/CAE: The Computer Aided Engineering Design SeriesVon EverandProduct Performance Evaluation using CAD/CAE: The Computer Aided Engineering Design SeriesNoch keine Bewertungen

- Engineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconVon EverandEngineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconBewertung: 1 von 5 Sternen1/5 (1)

- CH 8Dokument41 SeitenCH 8tasmia abedinNoch keine Bewertungen

- SL - No Publisher Author Title Year Price QTY TotalDokument5 SeitenSL - No Publisher Author Title Year Price QTY TotalDebabala SwainNoch keine Bewertungen

- File Concept Access Methods Directory Structure File System Mounting File Sharing ProtectionDokument30 SeitenFile Concept Access Methods Directory Structure File System Mounting File Sharing ProtectionDebabala SwainNoch keine Bewertungen

- Chapter 6: CPU Scheduling: Cycle of CPU Execution and I/O WaitDokument17 SeitenChapter 6: CPU Scheduling: Cycle of CPU Execution and I/O Waityo5208Noch keine Bewertungen

- Chapter1 Regression IntroductionDokument19 SeitenChapter1 Regression IntroductionDebabala SwainNoch keine Bewertungen

- Chapter1 Regression IntroductionDokument19 SeitenChapter1 Regression IntroductionDebabala SwainNoch keine Bewertungen

- Computer System Operation I/O Structure Storage Structure Storage Hierarchy Hardware Protection General System ArchitectureDokument29 SeitenComputer System Operation I/O Structure Storage Structure Storage Hierarchy Hardware Protection General System ArchitectureDebabala SwainNoch keine Bewertungen

- OS Concepts Chapter 5 ThreadsDokument20 SeitenOS Concepts Chapter 5 ThreadsDebabala SwainNoch keine Bewertungen

- OS Processes ChapterDokument38 SeitenOS Processes ChapterDebabala SwainNoch keine Bewertungen

- Computer Applications in Pharmacy Databases & SoftwareDokument1 SeiteComputer Applications in Pharmacy Databases & SoftwareDebabala SwainNoch keine Bewertungen

- CH 1Dokument23 SeitenCH 1Ashok KumarNoch keine Bewertungen

- Digital Circuit and Computer OrganizationDokument13 SeitenDigital Circuit and Computer OrganizationDebabala SwainNoch keine Bewertungen

- AdminDokument1 SeiteAdminDebabala SwainNoch keine Bewertungen

- CD Lab ManualDokument101 SeitenCD Lab ManualmainakNoch keine Bewertungen

- Chapter1 Regression Introduction PDFDokument8 SeitenChapter1 Regression Introduction PDFDebabala SwainNoch keine Bewertungen

- Data Structures and Algorithms (CS-2001Dokument120 SeitenData Structures and Algorithms (CS-2001Debabala SwainNoch keine Bewertungen

- CENTURION UNIVERSITY EXAM SCHEDULEDokument13 SeitenCENTURION UNIVERSITY EXAM SCHEDULEDebabala SwainNoch keine Bewertungen

- Chapter4 ArithmeticDokument74 SeitenChapter4 ArithmeticDebabala SwainNoch keine Bewertungen

- WILLINGNESS PROFORMA FOR SHORT-TERM TRAININGDokument1 SeiteWILLINGNESS PROFORMA FOR SHORT-TERM TRAININGDebabala SwainNoch keine Bewertungen

- Computer Graphics BCA Iii Sem Multiple Choice Questions: Ans: Picture ElementDokument20 SeitenComputer Graphics BCA Iii Sem Multiple Choice Questions: Ans: Picture ElementRoel PalmairaNoch keine Bewertungen

- CLSPDokument1 SeiteCLSPDebabala SwainNoch keine Bewertungen

- CENTURION UNIVERSITY COMPUTER ORGANIZATION SYLLABUSDokument1 SeiteCENTURION UNIVERSITY COMPUTER ORGANIZATION SYLLABUSDebabala SwainNoch keine Bewertungen

- 6th Semester - Time TableDokument6 Seiten6th Semester - Time TableDebabala SwainNoch keine Bewertungen

- 2 ExamDokument27 Seiten2 ExamEyyEychNoch keine Bewertungen

- BDD 5500Dokument49 SeitenBDD 5500LilianitaRizoNoch keine Bewertungen

- BGY888 Philips PDFDokument12 SeitenBGY888 Philips PDFPoso TvNoch keine Bewertungen

- HBR4HF Transciever ManualDokument7 SeitenHBR4HF Transciever ManualPetrika Janeku100% (1)

- Rjp30h1dpp MoDokument6 SeitenRjp30h1dpp MoAnonymous JIvcJUNoch keine Bewertungen

- Kirchhoff's Current Law (KCL) :: Kirchhoff's First & Second Laws With Solved ExampleDokument20 SeitenKirchhoff's Current Law (KCL) :: Kirchhoff's First & Second Laws With Solved Examplenobody126Noch keine Bewertungen

- ECE 270: Embedded Logic Design Byte-Wide WriteDokument34 SeitenECE 270: Embedded Logic Design Byte-Wide WriteMath CalculatorNoch keine Bewertungen

- AIWA 4ZG-1 (Chipset SONY) SvcMnlsDokument18 SeitenAIWA 4ZG-1 (Chipset SONY) SvcMnlsavrelecNoch keine Bewertungen

- Practical BIOS Editing PDFDokument294 SeitenPractical BIOS Editing PDFrazvan_nNoch keine Bewertungen

- Satlink2 User Manual 2Dokument165 SeitenSatlink2 User Manual 2javierth Enrique AraucoNoch keine Bewertungen

- Electrical Machines LabDokument8 SeitenElectrical Machines LabrabbystarNoch keine Bewertungen

- ICT1012 - Inner Workings of the CPUDokument80 SeitenICT1012 - Inner Workings of the CPUchaturakaNoch keine Bewertungen

- Contemporary Device TreeDokument25 SeitenContemporary Device TreeChairil AnwarNoch keine Bewertungen

- DSL Repair Dis Cas Codes 2013Dokument6 SeitenDSL Repair Dis Cas Codes 2013Adrian EladNoch keine Bewertungen

- REM615Dokument2 SeitenREM615anksyete50% (2)

- FCC Compliant RF Smart Repeater Installation GuideDokument1 SeiteFCC Compliant RF Smart Repeater Installation Guiderrr44Noch keine Bewertungen

- Microprocessors and Applications GuideDokument3 SeitenMicroprocessors and Applications GuideImmanuel VinothNoch keine Bewertungen

- CPS GRCP-User Manual-Oct 2008Dokument18 SeitenCPS GRCP-User Manual-Oct 2008Nur DiphylleiaNoch keine Bewertungen

- 555 Oscilador Datasheet PDFDokument6 Seiten555 Oscilador Datasheet PDFArlés GómezNoch keine Bewertungen

- Blade Center S - Battery Unit ReplacementDokument3 SeitenBlade Center S - Battery Unit ReplacementJorge Duran HerasNoch keine Bewertungen

- Test Bank For Modern Electronic Communication 9th Edition Jeff Beasley DownloadDokument3 SeitenTest Bank For Modern Electronic Communication 9th Edition Jeff Beasley Downloadkendrataylorygwedrfzcn100% (23)

- EE3403 -MEASUREMENTS AND INSTRUMENTATION --Question Bank-1- refer CAT 1Dokument8 SeitenEE3403 -MEASUREMENTS AND INSTRUMENTATION --Question Bank-1- refer CAT 1Pandyselvi BalasubramanianNoch keine Bewertungen

- JRC ErrorcodeDokument98 SeitenJRC ErrorcodeNguyen Minh Giap100% (1)

- Vlsi Design Automation Course Notes The Principles of Vlsi DesignDokument17 SeitenVlsi Design Automation Course Notes The Principles of Vlsi DesignChinni BabuNoch keine Bewertungen

- Rane Sound System InterconnectionDokument8 SeitenRane Sound System InterconnectionkennkkiNoch keine Bewertungen

- Altai A8n Catalog Eng 160810Dokument2 SeitenAltai A8n Catalog Eng 160810Mahmoud Ben RahalNoch keine Bewertungen

- LM35 Temperature Sensor Interfacing with ArduinoDokument14 SeitenLM35 Temperature Sensor Interfacing with ArduinoAjay kumarNoch keine Bewertungen

- CBS Power Products User Guide Manual For Epoxy Molded Vacuum RecloserDokument163 SeitenCBS Power Products User Guide Manual For Epoxy Molded Vacuum RecloserMohammad Alshikh100% (1)

- KLV S23a10 PDFDokument109 SeitenKLV S23a10 PDFmg139Noch keine Bewertungen