Beruflich Dokumente

Kultur Dokumente

EVMAM1810 Schematics RevC

Hochgeladen von

quoctoan_3tCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

EVMAM1810 Schematics RevC

Hochgeladen von

quoctoan_3tCopyright:

Verfügbare Formate

5

REV

SCHEMATIC CONTENTS

SHEET01

SHEET02

SHEET03

SHEET04

SHEET05

SHEET06

SHEET07

SHEET08

SHEET09

SHEET10

SHEET11

SHEET12

SHEET13

SHEET14

SHEET15

SHEET16

SHEET17

SHEET18

SHEET19

SHEET20

SHEET21

SHEET22

SHEET23

SHEET24

SHEET25

SHEET26

SHEET27

SHEET28

SHEET29

SHEET30

SHEET31

SHEET32

SHEET33

SHEET34

SHEET36

SHEET36

SHEET37

SHEET38

TITLE PAGE

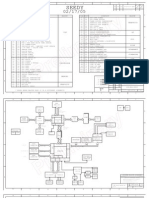

AM1810 McASP

AM1810 SATA INTERFACE

AM1810 SERIAL I/O

I2C EEPROM

SPI FLASH

AM1810 VIDEO PORT OUT

AM1810 VIDEO PORT IN

AM1810 USB 2.0 PORT

AM1810 USB 1.0 PORT

AM1810 EMIF A

AM1810 DDR2 EMIF

AM1810 JTAG/CLOCKS

AM1810 POWER PINS

AM1810 I/O POWER PINS

AM1810 GROUND PINS

DDR2 MEMORY

MII ETHERNET PHY

ETHERNET CONNECTOR

AUDIO CODEC

RS232 CONNECTOR

MMC/SD CONNECTOR

BIT MAPPED LCD INTERFACE CONNECTOR

USB CONNECTORS

USER LEDS/SWITCHES

BOOT SWITCHES

JTAG EMULATION CONNECTORS

XDS100v2 EMULATION

XDS100v2 EMULATION BUFFERS

PERIPHERAL EXPANSION CONNECTOR

PMDC CONNECTOR

EMIF EXPANSION CONNECTOR

AUDIO EXPANSION CONNECTOR

TPS65070 PMIC

RTC POWER

POWER MONITORS AND POWER ROUTER

BATTERY POWER

POWER

DESCRIPTION

DATE

Initial schematic for layout

APPROVED

03/01/2010

RRP

I2C ADDRESS MAP

BASE( HEX)

BASE BINARY

I2C ADDRESS TABLE

SHEET

0X50

101 0000W

I2C EEPROM

0X48

100 1000W

TPS65070 PMIC

0X18

001 1000W

TLV320AIC3106

0X21

010 0001W

TCA6416 - U34 - User Switches

POWER MEASUREMENT - NOT ON AM1810 CPU BUS

100 0000W

INA219 - 5V INPUT

100 0001W

INA219 - PMIC 3V3

100 0010W

INA219 - PMIC I/O VOLTAGE ( 1V8/3V3 )

100 0011W

INA219 - PMIC 1V2

100 0100W

INA219 - PMIC 1V2 LDO

100 0101W

INA219 - PMIC 1V8 LDO

100 0110W

INA219 - RTC 1V2 LDO EXTERNAL

UI BOARD ADDRESSES FOR REFERENCE

010 1010W

ADV7343

101 1101W

TVP5147 COMPOSITE VIDEO ( SW SEL )

101 1100W

TVP5147 S-VIDEO ( SW SEL )

SPECIFIC CHIP

CAMERA IMAGER ( SW SEL - NEG BIT

OF TVP5147'S SEL )

010 0000W

PCF8575 IO EXPANDER

110 0101W

CDCE913 CLOCK CHIP

REVISION STATUS OF SHEETS

REV

SH

31

32

33

34

35

36

37

38

DWN

R.R.P.

CHK

REV

SH

21

22

23

24

25

26

27

28

29

30

REV

T.W.K.

ENGR

R.R.P.

ENGR-MGR

R.R.P.

QA

SH

11

12

13

14

15

16

17

18

19

20

REV

SH

10

C.M.D.

MFG

NEXT ASSY

USED ON

R.R.P.

RLSE

APPLICATION

R.R.P.

4

DATE

03/01/2010

DATE

03/01/2010

DATE

03/01/2010

DATE

03/01/2010

DATE

03/01/2010

DATE

03/01/2010

DATE

03/01/2010

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

TITLE PAGE

Size:B

DWG NO

Date:

3

AM1810 EVM

Revision:

B

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

U23-1

A3

CPU_AHCLKX

R206

22

AHCLKX/USB_REFCLKIN/UART1_CTS/GP0[10]

AHCLKX/USB_REFCLKIN/UART1_CTS/GP0[10] 20

ACLKX/GP0[14]

AFSX/GP0[12]

AXR11/FSX1/GP0[3]

AXR12/FSR1/GP0[4]

B1

B2

C5

C4

CPU_ACLKX

R193

22

ACLKX/GP0[14]

AFSX/GP0[12]

AXR11/FSX1/GP0[3]

AXR12/FSR1/GP0[4]

ACLKX/GP0[14] 20

AFSX/GP0[12] 20

AXR11/FSX1/GP0[3] 20

AXR12/FSR1/GP0[4] 20

ACLKR/GP0[15]

AHCLKR/UART1_RTSn/GP0[11]

AFSR/GP0[13]

AMUTE/UART2_RTSn/GP0[9]

A1

A2

C2

D5

CPU_ACLKR

CPU_AHCLKR

R192

R208

22

22

ACLKR/GP0[15]

AHCLKR/UART1_RTSn/GP0[11]

AFSR/GP0[13]

AMUTE/UART2_RTSn/GP0[9]

ACLKR/GP0[15] 33

AHCLKR/UART1_RTSn/GP0[11] 22,33

AFSR/GP0[13] 33

AMUTE/UART2_RTSn/GP0[9] 21,33

AXR0/ECAP0_APWM0/GP8[7]/MII_TXD[0]/CLKS0

AXR1/DX0/GP1[9]/MII_TXD[1]

AXR2/DR0/GP1[10]/MII_TXD[2]

AXR3/FSX0/GP1[11]/MII_TXD[3]

F3

E1

E2

E3

CPU_AXR[0]

AXR0/ECAP0_APWM0/GP8[7]/MII_TXD[0]/CLKS0

AXR1/DRX0/GP1[9]/MII_TXD[1]

AXR2/DR0/GP1[10]/MII_TXD[2]

AXR3/FSX0/GP1[11]/MII_TXD[3]

AXR0/ECAP0_APWM0/GP8[7]/MII_TXD[0]/CLKS0 18,33

AXR1/DX0/GP1[9]/MII_TXD[1] 18,33

AXR2/DR0/GP1[10]/MII_TXD[2] 18,33

AXR3/FSX0/GP1[11]/MII_TXD[3] 18,33

AXR4/FSR0/GP1[12]/MII_COL

AXR5/CLKX0/GP1[13]/MII_TXCLK

AXR6/CLKR0/GP1[14]/MII_TXEN

AXR7/EPWM1TZ[0]/GP1[15]

D1

D3

C1

D2

CPU_AXR[4]

CPU_AXR[5]

AXR8/CLKS1/ECAP1/APWM1/GP0[0]

AXR9/DX1/GP0[1]

AXR10/DR1/GP0[2]

E4

C3

D4

AXR13/CLKX1/GP0[5]

AXR14/CLKR1/GP0[6]

AXR15/EPWM0TZ[0]/ECAP2_APWM2/GP0[7]

B3

B4

A4

AHCLKX/USB_REFCLKIN/UART1_CTSn/GP0[10]

R205

22

CPU_AXR[13]

CPU_AXR[14]

R210

R191

R207

R204

22

22

22

22

AXR4/FSR0/GP1[12]/MII_COL

AXR5/CLKX0/GP1[13]/MII_TXCLK

AXR6/CLKR0/GP1[14]/MII_TXEN

AXR7/EPWM1TZ[0]/GP1[15]

AXR4/FSR0/GP1[12]/MII_COL 18,33

AXR5/CLKX0/GP1[13]/MII_TXCLK 18,33

AXR6/CLKR0/GP1[14]/MII_TXEN 18,33

AXR7/EPWM1TZ[0]/GP1[15] 33

AXR8/CLKS1/ECAP1_APWM1/GP0[0]

AXR9/DX1/GP0[1]

AXR10/DR1/GP0[2]

AXR8/CLKS1/ECAP1_APWM1/GP0[0] 33

AXR9/DX1/GP0[1] 33

AXR10/DR1/GP0[2] 33

AXR13/CLKX1/GP0[5]

AXR14/CLKR1/GP0[6]

AXR15/EPWM0TZ[0]/ECAP2_APWM2/GP0[7]

AXR13/CLKX1/GP0[5] 33

AXR14/CLKR1/GP0[6] 33

AXR15/EPWM0TZ[0]/ECAP2_APWM2/GP0[7] 33

POWER GROUP A

AM1810

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

McASP/MII Ethernet MAC

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

DSK_3V3

L4

Ferrite Chip

C40

C190

C189

C42

1.0uF

0.01uF

560pF

0.1uF

DIFFERENTIAL PAIR

100 OHM DIFFERENTIAL

IMPEDANCE

SHORT AND STRAIGHT AS

POSSIBLE,

MINIMUM NUMBER OF VIAS

DSK_3V3

R255

10K

U27

0 = ON,

1 = OFF

Q11

BSS138

VoD-

SATA_CLKN

VoD+

GND NC

SATA_CLKP

DIFFERENTIAL PAIR

100 OHM DIFFERENTIAL

IMPEDANCE

SHORT AND STRAIGHT AS

POSSIBLE,

MINIMUM NUMBER OF VIAS

6,11,18,34 BUFF_ENn

E/D VCC

CCLD-033-50-100.00

VCC_1V2_LDO

U23-15

E2

NFM21PC474R1C3D

3

1

C50

C55

0.001uF

C56

0.1uF

C57

0.01uF

C58

1uF

M2

N4

P1

P2

SATA_VDD.1

SATA_VDD.2

SATA_VDD.3

SATA_VDD.4

SATA_REFCLKP

N2

SATA_REFP

SATA_REFCLKN

N1

SATA_REFN

.1uF

R79

NO-POP

C45

.1uF

VCC_1V8_LDO

J3

E4

NFM21PC474R1C3D

3

1

P3

C69

0.001uF

C70

0.1uF

C71

0.01uF

SATA_TXP

J1

SATA_TXP

.1uF

CON_SATA_TXP

CON_SATA_TXN

SATA_TXN

J2

SATA_TXN

.1uF

SATA_RXN

L2

SATA_RXN

.1uF

C173

SATA_RXP

L1

SATA_RXP

.1uF

C179

NC.M3

M3

C162

SATA_VDDR

C72

1uF

1

2

3

4

5

6

7

CON_SATA_RXN

CON_SATA_RXP

C165

1 MH1

2

3

4

5

6

7 MH9

SATA HEADER 7

N3

SATA_REG

C187

0.1uF

H1

H2

K1

K2

L3

M1

SATA_VSS.1

SATA_VSS.2

SATA_VSS.3

SATA_VSS.4

SATA_VSS.5

SATA_VSS.6

Pin # Function

1 Ground

2 A+ (Transmit)

3 A- (Transmit)

4 Ground

5 B- (Receive)

6 B+ (Receive)

7 Ground

- coding notch

A 7-pin Serial ATA data cable

SPECTRUM DIGITAL INCORPORATED

AM1810

Title:

Page Contents:

SATA INTERFACE

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

U23-6

F4

RSVD/RTC_ALARM]/UART2_CTSn/GP0[8]/DEEPSLEEPn

SPI1_SCS[0]/EPWM1B/GP2[14]/TM64P3_IN12

SPI1_SCS[1]/EPWM1A/GP2[15]/TM64P2_IN12

SPI1_SCS[2]/UART1_TXD/SATA_CP_POD/GP1[0]

SPI1_SCS[3]/UART1_RXD/SATA_LED/GP1[1]

E19

F18

F19

E18

SPI1_SCS[0]/EPWM1B/GP2[14]/TM64P3_IN12

SPI1_SCS[1]/EPWM1A/GP2[15]/TM64P2_IN12

SPI1_SCS[2]/UART1_TXD/SATA_CP_POD/GP1[0]

SPI1_SCS[3]/UART1_RXD/SATA_LED/GP1[1]

SPI1_SCS[4]/UART2_TXD/I2C1_SDA/GP1[2]

SPI1_SCS[5]/UART2_RXD/I2C1_SCL/GP1[3]

SPI1_SCS[6]/I2C0_SDA/TM64P3_OUT12/GP1[4]

SPI1_SCS[7]/I2C0_SCL/TM64P2_OUT12/GP1[5]

F16

F17

G18

G16

SPI1_SCS[4]/UART2_TXD/I2C1_SDA/GP1[2]

SPI1_SCS[5]/UART2_RXD/I2C1_SCL/GP1[3]

I2C0_SDA

I2C0_SCL

SPI1_ENAn/GP2[12]

SPI1_CLK/GP2[13]

SPI1_SIMO/GP2[10]

SPI1_SOMI/GP2[11]

H16

G19

G17

H17

SPI1_ENAn/GP2[12]

CPU_SPI1_CLK/GP2[13]

SPI1_SIMO/GP2[10]

SPI1_SOMI/GP2[11]

SPI0_SCS[0]/TM64P1_OUT12/GP1[6]/MDIO_D/TM64P1_IN12

SPI0_SCS[1]/TM64P0_OUT12/GP1[7]/MDIO_CLK/TM64P0_IN12

D17

E16

SPI0_SCS[0]/TM64P1_OUT12/GP1[6]/MDIO_D/TM64P1_IN12

SPI0_SCS[1]/TM64P0_OUT12/GP1[7]/MDIO_CLK/TM64P0_IN12

SPI0_SCS[2]/UART0_RTSn/GP8[1]/MII_RXD[0]/SATA_CP_DET

SPI0_SCS[3]/UART0_CTSn/GP8[2]/MII_RXD[1]/SATA_MP_SWITCH

SPI0_SCS[4]/UART0_TXD/GP8[3]/MII_RXD[2]

SPI0_SCS[5]/UART0_RXD/GP8[4]/MII_RXD[3]

D16

E17

D18

C19

SPI0_SCS[2]/UART0_RTSn/GP8[1]/MII_RXD[0]/SATA_CP_DET

SPI0_SCS[3]/UART0_CTSn/GP9[2]/MII_RXD[1]/SATA_MP_SWITCH

SPI0_SCS[4]/UART0_TXD/GP8[3]/MII_RXD[2]

SPI0_SCS[5]/UART0_RXD/GP8[4]/MII_RXD[3]

SPI0_ENAn/EPWM0B/MII_RXDV

SPI0_CLK/EPWM0A/GP1[8]/MII_RXCLK

SPI0_SOMI/EPWMSYNCI/GP8[6]/MII_RXER

SPI0_SIMO/EPWMSYNC0/GP8[5]/MII_CRS

C17

D19

C16

C18

SPI0_ENAn/WPWM0B/MII_RXDV

CPU_SPI0_CLK/EPWM0A/GP1[8[/MII_RXCLK

SPI0_SOMI/EPWMSYNCI/GP8[6]/MII_RXER

SPI0_SIMO/EPWMSYNCO/GP8[5]/MII_CRS

RSVD/RTC_ALARM/UART2_CTSn/GP0[8]/DEEPSLEEPn

RSVD/RTC_ALARM]/UART2_CTSn/GP0[8]/DEEPSLEEPn 5,21,31

SPI1_SCS[0]/EPWM1B/GP2[14]/TM64P3_IN12 6,23,33

SPI1_SCS[1]/EPWM1A/GP2[15]/TM64P2_IN12 23,33

SPI1_SCS[2]/UART1_TXD/SATA_CP_POD/GP1[0] 33

SPI1_SCS[3]/UART1_RXD/SATA_LED/GP1[1] 33

SPI1_SCS[4]/UART2_TXD/I2C1_SDA/GP1[2] 21,33

SPI1_SCS[5]/UART2_RXD/I2C1_SCL/GP1[3] 21,33

I2C0_SDA 5,20,25,30,31,32,33,34

I2C0_SCL 5,20,25,30,31,32,33,34

R225

22

SPI1_ENAn/GP2[12]

SPI1_CLK/GP2[13]

SPI1_SIMO/GP2[10]

SPI1_SOMI/GP2[11]

SPI1_ENAn/GP2[12] 6,33

SPI1_CLK/GP2[13] 6,33

SPI1_SIMO/GP2[10] 6,33

SPI1_SOMI/GP2[11] 6,33

SPI0_SCS[0]/TM64P1_OUT12/GP1[6]/MDIO_D/TM64P1_IN12 18,30

SPI0_SCS[1]/TM64P0_OUT12/GP1[7]/MDIO_CLK/TM64P0_IN12 18,30

SPI0_SCS[2]/UART0_RTSn/GP8[1]/MII_RXD[0]/SATA_CP_DET 18,32

SPI0_SCS[3]/UART0_CTSn/GP9[2]/MII_RXD[1]/SATA_MP_SWITCH 18,32

SPI0_SCS[4]/UART0_TXD/GP8[3]/MII_RXD[2] 18,32

SPI0_SCS[5]/UART0_RXD/GP8[4]/MII_RXD[3] 18,32

R219

22

SPI0_ENAn/EPWM0B/MII_RXDV 18,31,32

SPI0_CLK/EPWM0A/GP1[8]/MII_RXCLK 18,31,32

SPI0_SOMI/EPWMSYNCI/GP8[6]/MII_RXER 18,31,32

SPI0_SIMO/EPWMSYNCO/GP8[5]/MII_CRS 18,31,32

SPI0_CLK/EPWM0A/GP1[8[/MII_RXCLK

POWER GROUP A

AM1810

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

AM1808 SERIAL I/O

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

DSK_VIO

DSK_VIO

C101

.1uF

R148

NO-POP

R149

NO-POP

R150

NO-POP

U2

D

8

7

6

5

I2C0_SCL

I2C0_SDA

4,20,25,30,31,32,33,34 I2C0_SCL

4,20,25,30,31,32,33,34 I2C0_SDA

VCC

WP

SCL

SDA

A0

A1

NC

VSS

24WC256

1

2

3

4

R159

NO-POP

R160

0

R161

0

DO NOT POPULATE

DSK_3V3

DSK_VIO

R12

2K

1%

DSK_3V3

R11

2K

1%

R5

NO-POP(4.7k)

5%

3

4

6 PIDCLK

4,21,31 RSVD/RTC_ALARM]/UART2_CTSn/GP0[8]/DEEPSLEEPn

VREF1

SCL1

SDA1

R7

NO-POP(2K)

1%

DSK_3V3

C100

NO-POP(.1uF)

U4

R6

NO-POP(2K)

1%

VREF2

EN

SCL2

SDA2

6

5

GND

R145

NO-POP

R146

NO-POP

R147

NO-POP

R163

NO-POP(0)

R164

NO-POP(0)

U3

8

7

6

5

VCC

WP

SCL

SDA

A0

A1

NC

VSS

1

2

3

4

NO-POP(24WC256)

R162

NO-POP

NO-POP(PCA9306)

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

I2C EEPROM / PARAMETER I2C EEPROM

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

LEVEL TRANSLATORS

OE

L

L

DIR

L

H

FUNCTION

B->A

A->B

DSK_3V3

DSK_VIO

DSK_3V3

DSK_VIO

DSK_3V3

R156

10K

R154

10K

R153

10K

R152

10K

R151

10K

C109

.1uF

1

2

15

4

5

4,33 SPI1_SIMO/GP2[10]

4,33 SPI1_CLK/GP2[13]

6

7

4,23,33 SPI1_SCS[0]/EPWM1B/GP2[14]/TM64P3_IN12

4,33 SPI1_ENAn/GP2[12]

3

14

3,11,18,34 BUFF_ENn

R4

C102

.1uF

U5

NO-POP

VCCA VCCB

R155

10K

R157

10K

R137

10K

DSK_3V3

U1

16

SPI_HOLD

1DIR

1OEn

1A1

1A2

2A1

2A2

1B1

1B2

2B1

2B2

13

12

T3V3_SPI1_SIMO

T3V3_SPI1_CLK

11

10

T3V3_SPI1_SCS[0]

SCLK

16

T3V3_SPI1_CLK

VCC

DIO

15

T3V3_SPI1_SIMO

NC.3

NC.14

14

NC.4

NC.13

13

NC.5

NC.12

12

NC.6

NC.11

11

CS

GND

10

DO

WP

1

2

C115

0.1uF

2DIR

2OEn

GNDA GNDB

R136

10K

T3V3_SPI1_SCS[0]

T3V3_SPI1_SOMI

74AVC4T245PW

HOLD

DSK_3V3

SPI_WP

10K

R135

W25X64VSFIG

R3

10K

PIDCLK

PIDCLK

OR M25P64-VMF6TP

DSK_VIO

C108

.1uF

4,33 SPI1_SOMI/GP2[11]

U40

SN74LVC1G125

T3V3_SPI1_SOMI

3

1

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

SPI ROM

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

23,30 LCD_AC_ENB_CSn/GP6[0]

LCD_AC_ENB_CSn/GP6[0]

R269

RN9

26

26

26

26

26

26

26

26

BOOTMODE[7]

BOOTMODE[6]

BOOTMODE[5]

BOOTMODE[4]

BOOTMODE[3]

BOOTMODE[2]

BOOTMODE[1]

BOOTMODE[0]

22

RPACK8-10

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

U23-5

R5

LCD_AC_ENB_CSn/GP6[0]

23,30 VP_DOUT[15]/LCD_D[15]/UPP_XD[7]/GP7[7]

23,30 VP_DOUT[14]/LCD_D[14]/UPP_XD[6]/GP7[6]

23,30 VP_DOUT[13]/LCD_D[13]/UPP_XD[5]/GP7[5]

23,30 VP_DOUT[12]/LCD_D[12]/UPP_XD[4]/GP7[4]

23,30 VP_DOUT[11]/LCD_D[11]/UPP_XD[3]/GP7[3]

23,30 VP_DOUT[10]/LCD_D[10]/UPP_XD[2]/GP7[2]

23,30 VP_DOUT[9]/LCD_D[9]/UPP_XD[1]/GP7[1]

23,30 VP_DOUT[8]/LCD_D[8]/UPP_XD[0]/GP7[0]

P4

R3

R2

R1

T3

T2

T1

U3

VP_DOUT[15]/LCD_D[15]/UPP_XD[7]/GP7[7]/BOOT[7]

VP_DOUT[14]/LCD_D[14]/UPP_XD[6]/GP7[6]/BOOT[6]

VP_DOUT[13]/LCD_D[13]/UPP_XD[5]/GP7[5]/BOOT[5]

VP_DOUT[12]/LCD_D[12]/UPP_XD[4]/GP7[4]/BOOT[4]

VP_DOUT[11]/LCD_D[11]/UPP_XD[3]/GP7[3]/BOOT[3]

VP_DOUT[10]/LCD_D[10]/UPP_XD[2]/GP7[2]/BOOT[2]

VP_DOUT[9]/LCD_D[9]/UPP_XD[1]/GP7[1]/BOOT[1]

VP_DOUT[8]/LCD_D[8]/UPP_XD[0]/GP7[0]/BOOT[0]

23,30

23,30

23,30

23,30

23,30

23,30

23,30

23,30

U2

U1

V3

V2

V1

W3

W2

W1

VP_DOUT[7]/LCD_D[7]/UPP_XD[15]/GP7[15]

VP_DOUT[6]/LCD_D[6]/UPP_XD[14]/GP7[14]

VP_DOUT[5]/LCD_D[5]/UPP_XD[13]/GP7[13]

VP_DOUT[4]/LCD_D[4]/UPP_XD[12]/GP7[12]

VP_DOUT[3]/LCD_D[3]/UPP_XD[11]/GP7[11]

VP_DOUT[2]/LCD_D[2]/UPP_XD[10]/GP7[10]

VP_DOUT[1]/LCD_D[1]/UPP_XD[9]/GP7[9]

VP_DOUT[0]/LCD_D[0]/UPP_XD8/GPIO7[8]

VP_DOUT[7]/LCD_D[7]/UPP_XD[15]/GP7[15]

VP_DOUT[6]/LCD_D[6]/UPP_XD[14]/GP7[14]

VP_DOUT[5]/LCD_D[5]/UPP_XD[13]/GP7[13]

VP_DOUT[4]/LCD_D[4]/UPP_XD[12]/GP7[12]

VP_DOUT[3]/LCD_D[3]/UPP_XD[11]/GP7[11]

VP_DOUT[2]/LCD_D[2]/UPP_XD[10]/GP7[10]

VP_DOUT[1]/LCD_D[1]/UPP_XD[9]/GP7[9]

VP_DOUT[0]/LCD_D[0]/UPP_XD[8]/GP7[8]

R221

R218

R234

R203

22

22

22

22

F1

F2

H4

G4

MMCSD1_DAT[7]/LCD_PCLK/GP8[11]

MMCSD1_DAT[6]/LCD_MCLK/GP8[10]

MMCSD1_DAT[5]/LCD_HSYNC/GP8[9]

MMCSD1_DAT[4]/LCD_VSYNC/GP8[8]

30 VP_CLKIN2/MMCSD1_DAT[3]/GP6[4]

30 VP_CLKO2/MMCSD1_DAT[2]/GP6[3]

30 VP_CLKIN3/MMCSD1_DAT[1]/GP6[2]

30 MMCSD1_DAT[0]/UPP_CHB_CLK/GP8[15]

R237

R245

R239

R230

22

22

22

22

H3

K3

J3

G1

VP_CLKIN2/MMCSD1_DAT[3]/GP6[4]

VP_CLKOUT2/MMCSD1_DAT[2]/GP6[3]

VP_CLKIN3/MMCSD1_DAT[1]/GP6[2]

MMCSD1_DAT[0]/UPP_CHB_CLK/GP8[15]

30 MMCSD1_CLK/UPP_CHB_START/GP8[14]

30 MMCSD1_CMD/UPP_CHB_ENABLE/GP8[13]

R228

R241

22

22

G2

J4

MMCSD1_CLK/UPP_CHB_START/GP8[14]

MMCSD1_CMD/UPP_CHB_ENABLE/GP8[13]

R247

22

K4

VP_CLKOUT3/GP6[1]

G3

UPP_CHB_WAIT/GP8[12]

23,30

30

23,30

23,30

MMCSD1_DAT[7]/LCD_PCLK/GP8[11]

MMCSD1_DAT[6]/LCD_MCLK/GP8[10]

MMCSD1_DAT[5]/LCD_HSYNC/GP8[9]

MMCSD1_DAT[4]/LCD_VSYNC/GP8[8]

30 VP_CLKO3/GP6[1]

30 UPP_CHB_WAIT/GP8[12]

POWER GROUP C

AM1810

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

Video Port

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

U23-4

30 VP_DIN[15]_VSYNC/UHPI_HD[7]/UPP_CHA_D[7]

30 VP_DIN[14]_HSYNC/UHPI_HD[6]/UPP_CHA_D[6]

30 VP_DIN[13]_FIELD/UHPI_HD[5]/UPP_CHA_D[5]

30 VP_DIN[12]/UHPI_HD[4]/UPP_CHA_D[4]

30 VP_DIN[11]/UHPI_HD[3]/UPP_CHA_D[3]

30 VP_DIN[10]/UHPI_HD[2]/UPP_CHA_D[2]

30 VP_DIN[9]/UHPI_HD[1]/UPP_CHA_D[1]

30 VP_DIN[8]/UHPI_HD[0]/UPP_CHA_D[0]/GP6[5]

30 VP_DIN[7]/UHPI_HD[15]/UPP_CHA_D[15]/RMII_TXD[1]

30 VP_DIN[6]/UHPI_HD[14]/UPP_CHA_D[14]/RMII_TXD[0]

30 VP_DIN[5]/UHPI_HD[13]/UPP_CHA_D[13]/RMII_TXEN

30 VP_DIN[4]/UHPI_HD[12]/UPP_CHA_D[12]/RMII_RXD[1]

30 VP_DIN[3]/UHPI_HD[11]/UPP_CHA_D[11]/RMII_RXD[0]

30 VP_DIN[2]/UHPI_HD[10]/UPP_CHA_D[10]/RMII_RXER

30 VP_DIN[1]/UHPI_HD[9]/UPP_CHA_D[9]/RMII_MHZ_50_CLK

30 VP_DIN[0]/UHPI_HD[8]/UPP_CHA_D[8]/RMII_CRS_DV

VP_DIN[15]_VSYNC/UHPI_HD[7]/UPP_CHA_D[7]

VP_DIN[14]_HSYNC/UHPI_HD[6]/UPP_CHA_D[6]

VP_DIN[13]_FIELD/UHPI_HD[5]/UPP_CHA_D[5]

VP_DIN[12]/UHPI_HD[4]/UPP_CHA_D[4]

VP_DIN[11]/UHPI_HD[3]/UPP_CHA_D[3]

VP_DIN[10]/UHPI_HD[2]/UPP_CHA_D[2]

VP_DIN[9]/UHPI_HD[1]/UPP_CHA_D[1]

VP_DIN[8]/UHPI_HD[0]/UPP_CHA_D[0]/GP6[5]

V18

V19

U19

T16

R18

R19

R15

P17

VP_DIN[15]_VSYNC/UHPI_HD[7]/UPP_CHA_D[7]

VP_DIN[14]_HSYNC/UHPI_HD[6]/UPP_CHA_D[6]

VP_DIN[13]_FIELD/UHPI_HD[5]/UPP_CHA_D[5]

VP_DIN[12]/UHPI_HD[4]/UPP_CHA_D[4]

VP_DIN[11]/UHPI_HD[3]/UPP_CHA_D[3]

VP_DIN[10]/UHPI_HD[2]/UPP_CHA_D[2]

VP_DIN[9]/UHPI_HD[1]/UPP_CHA_D[1]

VP_DIN[8]/UHPI_HD[0]/UPP_CHA_D[0]/GP6[5]

VP_DIN[7]/UHPI_HD[15]/UPP_CHA_D[15]/RMII_TXD[1]

VP_DIN[6]/UHPI_HD[14]/UPP_CHA_D[14]/RMII_TXD[0]

VP_DIN[5]/UHPI_HD[13]/UPP_CHA_D[13]/RMII_TXEN

VP_DIN[4]/UHPI_HD[12]/UPP_CHA_D[12]/RMII_RXD[1]

VP_DIN[3]/UHPI_HD[11]/UPP_CHA_D[11]/RMII_RXD[0]

VP_DIN[2]/UHPI_HD[10]/UPP_CHA_D[10]/RMII_RXER

VP_DIN[1]/UHPI_HD[9]/UPP_CHA_D[9]/RMII_MHZ_50_CLK

VP_DIN[0]/UHPI_HD[8]/UPP_CHA_D[8]/RMII_CRS_DV

U18

V16

R14

W16

V17

W17

W18

W19

VP_DIN[7]/UHPI_HD[15]/UPP_CHA_D[15]/RMII_TXD[1]

VP_DIN[6]/UHPI_HD[14]/UPP_CHA_D[14]/RMII_TXD[0]

VP_DIN[5]/UHPI_HD[13]/UPP_CHA_D[13]/RMII_TXEN

VP_DIN[4]/UHPI_HD[12]/UPP_CHA_D[12]/RMII_RXD[1]

VP_DIN[3]/UHPI_HD[11]/UPP_CHA_D[11]/RMII_RXD[0]

VP_DIN[2]/UHPI_HD[10]/UPP_CHA_D[10]/RMII_RXER

VP_DIN[1]/UHPI_HD[9]/UPP_CHA_D[9]/RMII_MHZ_50_CLK

VP_DIN[0]/UHPI_HD[8]/UPP_CHA_D[8]/RMII_CRS_DV

30 VP_CLKIN1/UHPI_HDS1n/GP6[6]

30 VP_CLKIN0/UHPI_HCSn/GP6[7]/UPP_2XTXCLK

30 UHPI_HCNTL0/UPP_CHA_CLK/GP6[11]

30 UHPI_HCNTL1/UPP_CHA_START/GP6[10]

30 UHPI_HRWn/UPP_CHA_WAIT/GP6[8]

30 UHPI_HHWIL/UPP_CHA_ENABLE/GP6[9]

25,30 UHPI_HINTn/GP6[12]

24,30 UHPI_HRDY/GP6[13]

31 CLKOUT/UHPI_HDS2n/GP6[14]

VP_CLKIN1/UHPI_HDS1n/GP6[6]

R76

V15

VP_CLKIN1/UHPI_HDS1n/GP6[6]

VP_CLKIN0/UHPI_HCSn/GP6[7]/UPP_2XTXCLK

R264

W14

VP_CLKIN0/UHPI_HCSn/GP6[7]/UPP_2xTXCLK

U17

W15

T15

U16

UHPI_HCNTL0/UPP_CHA_CLK/GP6[11]

UHPI_HCNTL1/UPP_CHA_START/GP6[10]

UHPI_HRWn/UPP_CHA_WAIT/GP6[8]

UHPI_HHWIL/UPP_CHA_ENABLE/GP6[9]

R16

R17

T18

UHPI_HINTn/GP6[12]

UHPI_HRDYn/GP6[13]

CLKOUT/UHPI_HDS2n/GP6[14]

T17

RESETOUTn/UHPI_HASn/GP6[15]

UHPI_HCNTL0/UPP_CHA_CLK/GP6[11]

UHPI_HCNTL1/UPP_CHA_START/GP6[10]

UHPI_HRWn/UPP_CHA_WAIT/GP6[8]

UHPI_HHWIL/UPP_CHA_ENABLE/GP6[9]

UHPI_HINTn/GP6[12]

UHPI_HRDY/GP6[13]

CLKOUT/UHPI_HDS2n/GP6[14]

R262

R73

DSK_VIO

R259

10K

POWER GROUP C

AM1810

18,20,30,31,32,33 RESETOUTn

RESETOUTn

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

Video Port Input

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

DSK_3V3

E3

NFM21PC474R1C3D

1

C68

0.001uF

C67

0.1uF

C66

0.01uF

C65

1uF

90 ohm differential pairs

Differential Pair

U23-10

VCC_1V8_LDO

E6

NFM21PC474R1C3D

1

C84

0.001uF

C83

0.1uF

C82

0.01uF

C180

NO-POP

C81

1uF

C158

.22uF

N18

USB0_VDDA33

N16

NC.N16

N14

PWR

GROUP

B

USB0_DRVVBUS

K18

USB0_DRV_VBUS

USB0_VBUS

N19

FB_USB0_VBUS

USB0_DM

M18

USB0_DM

USB0_DM 24

USB0_DP

M19

USB0_DP

USB0_DP 24

USB0_ID

P16

USB0_VDDA18

M14

NC.M14

N17

USB0_VDDA12

PWR

GROUP

B

USB0_DRV_VBUS 24

FB_USB0_VBUS 24

USB0_ID

USB0_ID

24

AM1810

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

USB 2.0 INTERFACE

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

of

38

Differential Route 90 ohms

DSK_3V3

E5

NFM21PC474R1C3D

3

1

R70

15K

U23-9

C78

0.001uF

C77

0.1uF

C76

0.01uF

C75

1uF

P15

USB1_VDD33

P14

USB1_VDD18

USB1_DM

USB1_DP

P18

P19

CPU_USB1_DM

CPU_USB1_DP

R253

R250

24.9 1%

24.9 1%

USB1_DM

USB1_DP

USB1_DM 24

USB1_DP 24

VCC_1V8_LDO

E7

NFM21PC474R1C3D

3

1

C95

0.001uF

C94

0.1uF

C93

0.01uF

R68

15K

AM1810

C92

1uF

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

USB 1.0 HOST INTERFACE

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

10 o f

38

R182

10K

U23-2

DSK_VIO

R196

10K

EMA_A[23]/MMCSD0_CLK/GP4[7]

EMA_A[22]/MMCSD0_CMD/GP4[6]

EMA_A[21]/MMCSD0_DAT[0]/GP4[5]

EMA_A[20]/MMCSD0_DAT[1]/GP4[4]

EMA_A[19]/MMCSD0_DAT[2]/GP4[3]

EMA_A[18]/MMCSD0_DAT[3]/GP4[2]

EMA_A[17]/MMCSD0_DAT[4]/GP4[1]

EMA_A[16]/MMCSD0_DAT[5]/GP4[0]

E9

A10

B10

A11

C10

E11

B11

E12

R188

22

SD0_CLK 22

SD0_CMD 22

SD0_DATA0 22

SD0_DATA1 22

SD0_DATA2 22

SD0_DATA3 22

SD_WP

22

SD_INS

22

32 EMA_WAIT[0]/GP3[8]

EMA_WAIT[0]/GP3[8]

B18

EMA_WAIT[0]/GP3[8]

32 EMA_WAIT[1]/GP2[1]

EMA_WAIT[1]/GP2[1]

B19

EMA_WAIT[1]/GP2[1]

32 EMA_D[15]/GP3[7]

32 EMA_D[14]/GP3[6]

32 EMA_D[13]/GP3[5]

32 EMA_D[12]/GP3[4]

32 EMA_D[11]/GP3[3]

32 EMA_D[10]/GP3[2]

32 EMA_D[9]/GP3[1]

32 EMA_D[8]/GP3[0]

EMA_D[15]/GP3[7]

EMA_D[14]/GP3[6]

EMA_D[13]/GP3[5]

EMA_D[12]/GP3[4]

EMA_D[11]/GP3[3]

EMA_D[10]/GP3[2]

EMA_D[9]/GP3[1]

EMA_D[8]/GP3[0]

E6

C7

B6

A6

D6

A7

D9

E10

EMA_D[15]/GP3[7]

EMA_D[14]/GP3[6]

EMA_D[13]/GP3[5]

EMA_D[12]/GP3[4]

EMA_D[11]/GP3[3]

EMA_D[10]/GP3[2]

EMA_D[9]/GP3[1]

EMA_D[8]/GP3[0]

EMA_A[15]/MMCSD0_DAT[6]/GP5[15]

EMA_A[14]/MMCSD0_DAT[7]/GP5[14]

EMA_A[13]/GP5[13]

EMA_A[12]/GP5[12]

EMA_A[11]/GP5[11]

EMA_A[10]/GPIO5[10]

EMA_A[9]/GP5[9]

EMA_A[8]/GP5[8]

C11

A12

D11

D13

B12

C12

D12

A13

EMA_A[15]/MMCSD0_DAT[6]/GP5[15] 32

EMA_A[14]/MMCSD0_DAT[7]/GP5[14] 32

EMA_A[13]/GP5[13] 32

EMA_A[12] GP5[12] 32

EMA_A[11]/GP5[11] 32

EMA_A[10]/GP5[10] 32

EMA_A[9]/GP5[9] 32

EMA_A[8]/GP5[8] 32

32 EMA_D[7]/GP4[15]

32 EMA_D[6]/GP4[14]

32 EMA_D[5]/GP4[13]

32 EMA_D[4]/GP4[12]

32 EMA_D[3]/GP4[11]

32 EMA_D[2]/GP4[10]

32 EMA_D[1]/GP4[9]

32 EMA_D[0]/GP4[8]

EMA_D[7]/GP4[15]

EMA_D[6]/GP4[14]

EMA_D[5]/GP4[13]

EMA_D[4]/GP4[12]

EMA_D[3]/GP4[11]

EMA_D[2]/GP4[10]

EMA_D[1]/GP4[9]

EMA_D[0]/GP4[8]

D7

C6

E7

B5

E8

B8

A8

C9

EMA_D[7]/GP4[15]

EMA_D[6]/GP4[14]

EMA_D[5]/GP4[13]

EMA_D[4]/GP4[12]

EMA_D[3]/GP4[11]

EMA_D[2]/GP4[10]

EMA_D[1]/GP4[9]

EMA_D[0]/GP4[8]

EMA_A[7]/GP5[7]

EMA_A[6]/GP5[6]

EMA_A[5]/GP5[5]

EMA_A[4]/GP5[4]

EMA_A[3]/GP5[3]

EMA_A[2]/GP5[2]

EMA_A[1]/GP5[1]

EMA_A[0]/GP5[0]

B13

E13

C13

A14

D14

B14

D15

C14

EMA_A[7]/GP5[7]

EMA_A[6]/GP5[6]

EMA_A[5]/GP5[5]

EMA_A[4]/GP5[4]

EMA_A[3]/GP5[3]

EMA_A[2]/GP5[2]

EMA_A[1]/GP5[1]

EMA_A[0]/GP5[0]

EMA_BA[1]/GP2[9]

EMA_BA[0]/GP2[8]

A15

C15

EMA_CLK/GP2[7]

B7

EMA_SDCKE/GP2[6]

D8

EMA_CASn/GP2[4]

A9

EMA_RASn/GP2[5]

A16

32

32

32

32

32

32

32

32

EMA_BA[1]/GP2[9] 32

EMA_BA[0]/GP2[8] 23,32

R190

22

EMA_CLK/GP2[7] 32

BUFF_ENn 3,6,18,34

USB1_PWR_EN 24

R199

22

TPS65070_PB_OUT 34

DSK_VIO

R189

2K

R197

10K

R183

10K

R184

10K

R187

10K

R198

10K

EMA_CS[0]n/GP2[0]

A18

EMA_CS[0]/GP2[0] 32

EMA_CS[2]n/GP3[15]

B17

EMA_CS[2]/GP3[15] 22,32

EMA_CS[3]n/GP3[14]

A17

EMA_CS[3]/GP3[14] 32

EMA_CS[4]n/GP3[13]

F9

EMA_CS[4]/GP3[13] 32

EMA_CS[5]n/GP3[12]

B16

EMA_CS[5]/GP3[12] 32

DSK_VIO

R185

10K

POWER GROUP B

R186

10K

EMA_OEn/GP3[10]

B15

R200

22

EMA_WEn/GP3[11]

B9

R201

22

R209

EMA_WE_DQM[0]n/GP2[3]

C8

EMA_WEn/GP3[11] 32

TOUCH_INT 34

BATT_HDQ 37

EMA_WE_DQM[1]n/GP2[2]

A5

TPS65070_PWR_ON 34

D10

EMA_RNW/GP3[9] 32

EMA_A_RWn/GP3[9]

EMA_OEn/GP3[10] 32

0

SPECTRUM DIGITAL INCORPORATED

AM1810

AM1810 EVM

Title:

Page Contents:

EMIFA Interface

Size:B

DWG NO

Date:

5

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

11 o f

38

DDR_A[13]

D

R84

22

T_DDR_A[13]

U23-3

17 DDR_D[15]

17 DDR_D[14]

17 DDR_D[13]

17 DDR_D[12]

17 DDR_D[11]

17 DDR_D[10]

17 DDR_D[9]

17 DDR_D[8]

17

17

17

17

17

17

17

17

DDR_D[7]

DDR_D[6]

DDR_D[5]

DDR_D[4]

DDR_D[3]

DDR_D[2]

DDR_D[1]

DDR_D[0]

DDR_D[15]

DDR_D[14]

DDR_D[13]

DDR_D[12]

DDR_D[11]

DDR_D[10]

DDR_D[9]

DDR_D[8]

W10

U11

V10

U10

T12

T10

T11

T13

DDR_D[15]

DDR_D[14]

DDR_D[13]

DDR_D[12]

DDR_D[11]

DDR_D[10]

DDR_D[9]

DDR_D[8]

DDR_A[13]

DDR_A[12]

DDR_A[11]

EMB_A[10]

DDR_A[9]

DDR_A[8]

T5

V4

T4

W4

T6

U4

DDR_A[13]

DDR_A[12]

DDR_A[11]

DDR_A[10]

DDR_A[9]

DDR_A[8]

DDR_D[7]

DDR_D[6]

DDR_D[5]

DDR_D[4]

DDR_D[3]

DDR_D[2]

DDR_D[1]

DDR_D[0]

W11

W12

V12

V13

U13

V14

U14

U15

DDR_D[7]

DDR_D[6]

DDR_D[5]

DDR_D[4]

DDR_D[3]

DDR_D[2]

DDR_D[1]

DDR_D[0]

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

DDR_A[3]

DDR_A[2]

DDR_A[1]

DDR_A[0]

U6

W5

V5

U5

V6

W6

T7

U7

DDR_A[7]

DDR_A[6]

DDR_A[5]

DDR_A[4]

DDR_A[3]

DDR_A[2]

DDR_A[1]

DDR_A[0]

DDR_BA[2]

DDR_BA[1]

DDR_BA[0]

U8

T9

V8

DDR_BA[2]

DDR_BA[1]

DDR_BA[0]

RPACK8-22

9

10

11

12

13

14

15

16

DDR_A[12]

DDR_A[11]

DDR_A[10]

DDR_A[9]

DDR_A[8]

DDR_A[7]

DDR_A[6]

DDR_A[5]

RPACK8-22

DDR_A[4]

DDR_A[3]

DDR_A[2]

DDR_A[1]

DDR_A[0]

DDR_BA[2]

DDR_BA[1]

DDR_BA[0]

RN8

8

7

6

5

4

3

2

1

T_DDR_A[12]

T_DDR_A[11]

T_DDR_A[10]

T_DDR_A[9]

T_DDR_A[8]

T_DDR_A[7]

T_DDR_A[6]

T_DDR_A[5]

T_DDR_A[13] 17

T_DDR_A[12] 17

T_DDR_A[11] 17

T_DDR_A[10] 17

T_DDR_A[9] 17

T_DDR_A[8] 17

T_DDR_A[7] 17

T_DDR_A[6] 17

T_DDR_A[5] 17

RN7

9

10

11

12

13

14

15

16

8

7

6

5

4

3

2

1

T_DDR_A[4]

T_DDR_A[3]

T_DDR_A[2]

T_DDR_A[1]

T_DDR_A[0]

T_DDR_BA[2]

T_DDR_BA[1]

T_DDR_BA[0]

T_DDR_A[4] 17

T_DDR_A[3] 17

T_DDR_A[2] 17

T_DDR_A[1] 17

T_DDR_A[0] 17

T_DDR_BA[2] 17

T_DDR_BA[1] 17

T_DDR_BA[0] 17

17 DDR_DQS[0]

DDR_DQS[0]

T14

DDR_DQS[0]

DDR_CLKP

W8

DDR_CLKP

R93

10

T_DDR_CLKP

T_DDR_CLKP 17

17 DDR_DQS[1]

DDR_DQS[1]

V11

DDR_DQS[1]

DDR_CLKN

W7

DDR_CLKN

R90

10

T_DDR_CLKN

T_DDR_CLKN 17

22

T_DDR_CSn

DDR_DQM[0]

W13

T_DDR_CSn 17

17 T_DDR_DQM[0]

R110

V9

R88

22

DDR_CSn

DDR_CSn

T_DDR_DQM[0]

22

T_DDR_CKE

DDR_DQM[1]

R10

T_DDR_CKE 17

17 T_DDR_DQM[1]

R105

V7

R85

22

DDR_CKE

DDR_CKE

T_DDR_DQM[1]

DDR_RASn

W9

DDR_RASn

R89

22

T_DDR_RASn

T_DDR_RASn 17

DDR_CASn

U9

DDR_CASn

R87

22

T_DDR_CASn

T_DDR_CASn 17

DDR_WEn

T8

DDR_WEn

R86

22

T_DDR_WEn

T_DDR_WEn 17

R6

DDR_VREF

17 T_DDR_DQGATE0

T_DDR_DQGATE0

R282

10

DDR_DQGATE0

DDR_DQGATE1

17 DDR_DQGATE1

R11

R12

DDR_DQM[0]

DDR_DQM[1]

DDR_DQGATE0

DDR_DQGATE1

DDR_VREF

DDR_ZP

U12

DDR_VREF 17

DDR_ZP

C206

0.1UF

R270

49.9 1%

AM1810

DIFF PAIR

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

DDR2 INTERFACE

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

12 o f

38

DSK_VIO

R62

10K

27,34,38 MSTR_nRST_3.3_1.8

D

DSK_VIO

R242

NO-POP

U23-8

R231

10K

30,34 NMIn

OSCIN

K14

RESETn

J17

NMIn

PWR

GROUP

B

TRSTn

TRSTn

L17

TRSTn

TMS

TMS

L16

TMS

27

TDI

TDI

M16

TDI

27

TDO

TDO

J18

TDO

27

JTAG_TCK

TCK

OSCOUT

K19

OSCVSS

L18

RTC_XI

J19

33pF

C46

18 pF

C33

27

27

C29

Y5

24MHz

R61

100

J15

TCK

K17

RTCK/GP8[0]

J16

EMU0

K16

EMU1

3

2

Y4

32.768KHz

33pF

L19

RTC_XO

H19

VSS_RTC

H18

18 pF

C31

DSK_VIO

C37

AM1810

22pF

R235

10K

27 EMU0

27 EMU1

R229

10K

EMU0

EMU1

R238

27 RTCK

33

RTCK/GP8[0]

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

JTAG/CLOCKS

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

13 o f

38

VCC_1V2

VCC_1V2

U23-12

E15

G7

G8

G13

H6

H7

H10

H11

H12

C48

33uF

C152

0.1uF

c402-25

C178

0.1uF

c402-25

C166

0.1uF

c402-25

C174

0.1uF

c402-25

CVDD.1

CVDD.2

CVDD.3

CVDD.4

CVDD.5

CVDD.6

CVDD.7

CVDD.8

CVDD.9

CVDD.10

CVDD.11

CVDD.12

CVDD.13

CVDD.14

CVDD.15

CVDD.16

CVDD.17

CVDD.18

H13

J6

J12

K6

K12

L12

M8

M9

N8

+

C148

0.1uF

c402-25

C172

0.1uF

c402-25

C176

C163

0.1uF

0.1uF

c402-25 c402-25

C22

33uF

AM1810

U23-14

VCC_1V8_LDO

C52

33uF

C181

0.1uF

c402-25

C184

0.1uF

c402-25

N6

N9

N10

P7

P8

C183

0.1uF

c402-25

DDR_DVDD18.1

DDR_DVDD18.2

DDR_DVDD18.3

DDR_DVDD18.4

DDR_DVDD18.5

VCC_1V8_LDO

DDR_DVDD18.6

DDR_DVDD18.7

DDR_DVDD18.8

DDR_DVDD18.9

DDR_DVDD18.10

P9

P10

R7

R8

R9

C202

0.1uF

C204

0.1uF

C205

0.1uF

C53

33uF

AM1810

VCC_1V2_LDO

U23-16

E1

NFM21PC474R1C3D

1

C35

0.1uF

C38

0.01uF

L15

PLL0_VDDA12

N15

PLL1_VDDA12

M17

PLL0_VSSA12

M15

PLL1_VSSA12

1V2_RTC

RTC_CVDD

L14

C170

0.1uF

L2

BLMG1P500SPT

AM1810

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

AM1810 POWER PINS

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

C

513302-0031

Monday, December 20, 2010

Sheet

1

14 o f

38

DSK_VIO

CPU_VIO_A

R214

0

CPU_VIO_C

U23-7

D

C25

33uF

DSK_VIO

D

C151

0.1uF

c402-25

C154

0.1uF

c402-25

C160

0.1uF

c402-25

C182

0.1uF

c402-25

F5

G5

H5

F15

G14

G15

DVDD3318_A.1

DVDD3318_A.2

DVDD3318_A.3

DVDD3318_A.4

DVDD3318_A.5

DVDD3318_A.6

J5

K13

L4

L13

M13

N13

P5

P6

P12

R4

DVDD3318_C.1

DVDD3318_C.2

DVDD3318_C.3

DVDD3318_C.4

DVDD3318_C.5

DVDD3318_C.6

DVDD3318_C.7

DVDD3318_C.8

DVDD3318_C.9

DVDD3318_C.10

CPU_VIO_B

DSK_VIO

R81

DVDD3318_B.1

DVDD3318_B.2

DVDD3318_B.3

DVDD3318_B.4

DVDD3318_B.5

DVDD3318_B.6

DVDD3318_B.7

DVDD3318_B.8

DVDD3318_B.9

DVDD3318_B.10

DVDD3318_B.11

R194

E14

F6

F7

F8

F10

F11

F12

F13

G9

J14

K15

C21

33uF

C186

0.1uF

c402-25

C164

0.1uF

c402-25

C146

0.1uF

c402-25

C161

0.1uF

c402-25

C147

0.1uF

c402-25

C149

0.1uF

c402-25

C212

33uF

C195

0.1uF

c402-25

C201

0.1uF

c402-25

C192

0.1uF

c402-25

C207

0.1uF

c402-25

C175

0.1uF

c402-25

C188

0.1uF

c402-25

AM1810

VCC_1V2_LDO

U23-13

C168

0.1uF

c402-25

VCC_1V8_LDO

B

C23

33uF

C194

0.1uF

c402-25

C171

0.1uF

c402-25

C203

0.1uF

c402-25

C167

0.1uF

c402-25

C150

0.1uF

c402-25

F14

G6

G10

G11

G12

J13

K5

L6

P13

R13

C155

0.1uF

c402-25

DVDD18.1

DVDD18.2

DVDD18.3

DVDD18.4

DVDD18.5

DVDD18.6

DVDD18.7

DVDD18.8

DVDD18.9

DVDD18.10

RVDD.1

RVDD.2

RVDD.3

E5

H14

N7

USB_CVDD

M12

RSV2(VPP)

T19

C153

0.1uF

c402-25

C177

0.1uF

c402-25

C193

0.1uF

c402-25

TP5

TEST POINT

AM1810

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

AM1810 I/O POWER PINS

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

15 o f

38

U23-11

A19

H8

H9

H15

J7

J8

J9

J10

J11

K7

K8

K9

K10

K11

L5

VSS.1

VSS.2

VSS.3

VSS.4

VSS.5

VSS.6

VSS.7

VSS.8

VSS.9

VSS.10

VSS.11

VSS.12

VSS.13

VSS.14

VSS.15

VSS.16

VSS.17

VSS.18

VSS.19

VSS.20

VSS.21

VSS.22

VSS.23

VSS.24

VSS.25

VSS.26

VSS.27

VSS.28

VSS.29

VSS.30

L7

L8

L9

L10

L11

M4

M5

M6

M7

M10

M11

N5

N11

N12

P11

AM1810

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

AM1810 GROUND PINS

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

16 o f

38

VCC_1V8_LDO

C228

0.1UF

U35

12 T_DDR_A[13]

12 T_DDR_A[12]

12 T_DDR_A[11]

12 T_DDR_A[10]

12 T_DDR_A[9]

12 T_DDR_A[8]

12 T_DDR_A[7]

12 T_DDR_A[6]

12 T_DDR_A[5]

T_DDR_A[13]

T_DDR_A[12]

T_DDR_A[11]

T_DDR_A[10]

T_DDR_A[9]

T_DDR_A[8]

T_DDR_A[7]

T_DDR_A[6]

T_DDR_A[5]

V8

V2

U7

R2

U3

U8

U2

T7

T3

NC/A13

A12

A11

A10

A9

A8

A7

A6

A5

12 T_DDR_A[4]

12 T_DDR_A[3]

12 T_DDR_A[2]

12 T_DDR_A[1]

12 T_DDR_A[0]

12 T_DDR_BA[2]

12 T_DDR_BA[1]

12 T_DDR_BA[0]

T_DDR_A[4]

T_DDR_A[3]

T_DDR_A[2]

T_DDR_A[1]

T_DDR_A[0]

T_DDR_BA[2]

T_DDR_BA[1]

T_DDR_BA[0]

T8

T2

R7

R3

R8

P1

P3

P2

A4

A3

A2

A1

A0

BA2

BA1

BA0

AA9

AA8

AA2

AA1

D2

NC1

NC2

NC3

NC4

NC5

VCC_1V8_LDO

R292

NO-POP

DDR_ODT

R291

0

A9

A8

A2

A1

H2

V3

V7

N9

NC7

NC8

NC9

NC10

NC11

RFU.1

RFU.2

ODT

12 T_DDR_CSn

12 T_DDR_CASn

12 T_DDR_RASn

12 T_DDR_WEn

12 T_DDR_CKE

T_DDR_CSn

T_DDR_CASn

T_DDR_RASn

T_DDR_WEn

T_DDR_CKE

P8

P7

N7

N3

N2

CS#

CAS#

RAS#

WE#

CKE

12 T_DDR_CLKP

12 T_DDR_CLKN

T_DDR_CLKP

T_DDR_CLKN

M8

N8

CK

CK#

D8

E7

H8

J7

UDQS#/NU

UDQS

LDQS#/NU

LDQS

E3

J3

UDM

LDM

12 DDR_DQS[1]

DDR_DQS[1]

R119

22

T_DDR_DQS[1]

12 DDR_DQS[0]

DDR_DQS[0]

R123

22

T_DDR_DQS[0]

12 T_DDR_DQM[1]

12 T_DDR_DQM[0]

T_DDR_DQM[1]

T_DDR_DQM[0]

VDD.1

VDD.2

VDD.3

VDD.4

VDD.5

VDDQ.1

VDDQ.2

VDDQ.3

VDDQ.4

VDDQ.5

VDDQ.6

VDDQ.7

VDDQ.8

VDDQ.9

VDDQ.10

M9

H1

R9

D1

V1

F3

F7

K1

K3

K7

K9

D9

F1

F9

H9

VDDL

M1

VREF

M2

DQ15

DQ14

DQ13

DQ12

E9

E1

G9

G1

T_DDR_D[15]

T_DDR_D[14]

T_DDR_D[13]

T_DDR_D[12]

DQ11

DQ10

DQ9

DQ8

G3

G7

F2

F8

T_DDR_D[11]

T_DDR_D[10]

T_DDR_D[9]

T_DDR_D[8]

DQ7

DQ6

DQ5

DQ4

J9

J1

L9

L1

T_DDR_D[7]

T_DDR_D[6]

T_DDR_D[5]

T_DDR_D[4]

DQ3

DQ2

DQ1

DQ0

L3

L7

K2

K8

T_DDR_D[3]

T_DDR_D[2]

T_DDR_D[1]

T_DDR_D[0]

VSS.1

VSS.2

VSS.3

VSS.4

VSS.5

VSSQ.1

VSSQ.2

VSSQ.3

VSSQ.4

VSSQ.5

VSSQ.6

VSSQ.7

VSSQ.8

VSSQ.9

VSSQ.10

VSSDL

U9

T1

H3

D3

M3

G8

J8

D7

J2

E2

L8

L2

E8

H7

G2

M7

C234

0.1UF

C233

0.1UF

C239

0.1UF

+

C235

10UF

VCC_1V8_LDO

D

C240

560PF

C238

560PF

C236

560PF

C229

560PF

R285

1K 1%

C227

0.1UF

DDR_VREF

R284

1K 1%

RN10

T_DDR_D[14]

T_DDR_D[9]

T_DDR_D[11]

T_DDR_D[12]

5

6

7

8

RN12

T_DDR_D[15]

T_DDR_D[8]

T_DDR_D[10]

T_DDR_D[13]

RPACK4-22

4

3

2

1

DDR_D[14]

DDR_D[9]

DDR_D[11]

DDR_D[12]

DDR_D[14] 12

DDR_D[9] 12

DDR_D[11] 12

DDR_D[12] 12

RPACK4-22

1

2

3

4

DDR_D[15]

DDR_D[8]

DDR_D[10]

DDR_D[13]

DDR_D[15] 12

DDR_D[8] 12

DDR_D[10] 12

DDR_D[13] 12

5

6

7

8

RPACK4-22

4

3

2

1

DDR_D[6]

DDR_D[1]

DDR_D[4]

DDR_D[3]

DDR_D[6]

DDR_D[1]

DDR_D[4]

DDR_D[3]

12

12

12

12

5

6

7

8

RPACK4-22

4

3

2

1

DDR_D[2]

DDR_D[5]

DDR_D[7]

DDR_D[0]

DDR_D[2]

DDR_D[5]

DDR_D[7]

DDR_D[0]

12

12

12

12

RN13

T_DDR_D[2]

T_DDR_D[5]

T_DDR_D[7]

T_DDR_D[0]

C226

0.1UF

8

7

6

5

RN11

T_DDR_D[6]

T_DDR_D[1]

T_DDR_D[4]

T_DDR_D[3]

DDR_VREF 12

MT47H64M16HR-3:G

12 T_DDR_DQGATE0

T_DDR_DQGATE0

R283

0

SPECTRUM DIGITAL INCORPORATED

12 DDR_DQGATE1

DDR_DQGATE1

Title:

Page Contents:

DDR2 - EMIF B

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

17 o f

38

ENET_VDDIO

VCC_1V2

ENET_VDDCR

2

2

C141

BLM21PG221SN1D

C30

C144

C140

0.1uF

R181

2.2K

0

4,30 SPI0_SCS[0]/TM64P1_OUT12/GP1[6]/MDIO_D/TM64P1_IN12

17

MDC

16

MDIO

0.1uF

MII_TXP1

28

MII_TXM1

RX+

31

RX-

30

25

24

23

22

TXD3

TXD2

TXD1

TXD0

20

TX_CLK

LED2/INTSELn

49.9

49.9

15

14

COL/CRS_DV/MODE2

CRS

LED1/REGOFF

MII_RXP1

MII_TXP1

19

MII_TXM1

19

MII_RXP1 19

MII_RXM1

MII_RXM1 19

XTAL1/CLKIN

MII_SPEED_LED

MII_LINK_LED

33pF

R55

R57

R51

R42

49.9

49.9

49.9

49.9

8

9

10

11

RXD3/PHYAD2

RXD2/RMIISEL

RXD1/MODE1

RXD0/MODE0

R40

R53

R36

49.9

49.9

49.9

13

7

26

RX_ER/RXD4/PHYAD0

RX_CLK/PHYAD1

RX_DV

18

INT/TX_ER/TXD4

XTAL2

19

RESETn

RBIAS

32

MII_SPEED_LED 19

MII_LINK_LED 19

C28

ENET_VDDA

Y3

25.0000MHz

R44

1K

Internal Regulator Disable

8,20,30,31,32,33 RESETOUTn

GND1

1

2

4,31,32 SPI0_SOMI/EPWMSYNCI/GP8[6]/MII_RXER

4,31,32 SPI0_CLK/EPWM0A/GP1[8]/MII_RXCLK

4,31,32 SPI0_ENAn/EPWM0B/MII_RXDV

R329

49.9

3

4

4,32 SPI0_SCS[5]/UART0_RXD/GP8[4]/MII_RXD[3]

4,32 SPI0_SCS[4]/UART0_TXD/GP8[3]/MII_RXD[2]

4,32 SPI0_SCS[3]/UART0_CTSn/GP9[2]/MII_RXD[1]/SATA_MP_SWITCH

4,32 SPI0_SCS[2]/UART0_RTSn/GP8[1]/MII_RXD[0]/SATA_CP_DET

R260

49.9

TX-

2,33 AXR3/FSX0/GP1[11]/MII_TXD[3]

2,33 AXR2/DR0/GP1[10]/MII_TXD[2]

2,33 AXR1/DX0/GP1[9]/MII_TXD[1]

2,33 AXR0/ECAP0_APWM0/GP8[7]/MII_TXD[0]/CLKS0

R30

R33

R94

49.9

Differential Pair

TX_EN

2,33 AXR4/FSR0/GP1[12]/MII_COL

4,31,32 SPI0_SIMO/EPWMSYNCO/GP8[5]/MII_CRS

R330

49.9

10uF

29

21

R29

0.1uF

C24

TX+

2,33 AXR6/CLKR0/GP1[14]/MII_TXEN

2,33 AXR5/CLKX0/GP1[13]/MII_TXCLK

C145

1

27

VDD2A

VDD1A

U20

12

R32

10K

VDDIO

1

3

DSK_VIO

3,6,11,34 BUFF_ENn

BLM21PG221SN1D

ENET_VDDA

R26

10uF

0.1uF

4,30 SPI0_SCS[1]/TM64P0_OUT12/GP1[7]/MDIO_CLK/TM64P0_IN12

10uF

U44

NO-POP(SN74LVC1G125)

L10

C17

NO-POP(.1uF)

VDDCR

BLM21PG221SN1D

C19

C143

0.1uF

DSK_VIO

DSK_3V3

L9

L11

Do NOT populate when using PHY

Internal Regulator

DSK_VIO

R41

NO-POP

33

DSK_VIO

R54

NO-POP

R56

NO-POP

R58

NO-POP

R43

2K

R52

2K

33pF

R39

C27

12.1K

LAN8710A-EZK

R174

2K

TP1

ENET_INT

SPECTRUM DIGITAL INCORPORATED

Title:

R195

2K

R224

2K

R226

2K

R223

2K

R212

NO-POP

R216

NO-POP

R31

NO-POP

Page Contents:

ETHERNET PHY

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

B

513302-0031

Monday, December 20, 2010

Sheet

1

18 o f

38

DSK_3V3

R220

NO-POP

DSK_3V3

R227

NO-POP

R211

10

R236

10

DSK_3V3

DSK_3V3

R232

330

R217

330

Differential Pair 100 ohm

C

J31

18 MII_TXP1

18 MII_TXM1

18 MII_RXP1

18 MII_RXM1

R213

NO-POP

Differential Pair 100 ohm

R233

NO-POP

C157

0.1uF

C159

0.1uF

18 MII_SPEED_LED

18 MII_LINK_LED

1

4

2

TX+

TXCT

TX-

3

5

6

RX+

RXCT

RX-

11

C_YLW

12

A_YLW

10

C_GRN

A_GRN

7

8

NC

CHS_GND1

CHS_GND3CHS_GND2

Yellow LED

Green LED

13

14

J0011D01BNL

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

ETHERNET MII CONNECTOR

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

B

513302-0031

Monday, December 20, 2010

Sheet

1

19 o f

38

DSK_VIO

DSK_3V3

VDD

GND

OUT

.1uF

.1uF

24.576MHz

3V3_XTAL_24.576

DSK_3V3

DSK_VIO

Line In

C9

0.1uF

C7

0.1uF

U9

VCCA

DIR

A

GND

VCCB

C3

0.47uF

3

XTAL_24.576

R8

10K

5

6

1

5

3

2

J11

1

2

4

R1

10K

C2

0.47uF

SN74AVC1T45

DIR=H : A to B

DIR=L : B to A

DSK_3V3

C246

.1uF

25

U12

LINE1LM / MIC1LM

HPLOUT

18

LINE1LP / MIC1LP

HPLCOM

19

LINE1RM / MIC1RM

HPROUT

23

LINE1RP / MIC1RP

HPRCOM

22

LINE2LM / MIC2LM

MONO_LOP

27

LINE2LP / MIC2LP

MONO_LOM

28

10

LINE2RM / MIC2RM

LEFT_LOP

29

LINE2RP / MIC2RP

LEFT_LOM

30

RIGHT_LOP

31

RIGHT_LOM

32

MIC3L

14

MIC3R

13

MICBIAS

12

MICDET

C249

.1uF

C250

4.7uF

D

11

C248

.1uF

C247

4.7uF

AVDD_DAC

OE

C254

C253

4.7uF

DRVDD.1

DRVDD.2

DRVDD.3

C252

C251

4.7uF

36

44

C15

0.1uF

Y2

D

DVDD

IOVDD

DSK_3V3

16

17

24

VCC_1V8_LDO

C5

0.47uF

C

C1

0.47uF

J12

XTAL_24.576

MCLK

BCLK

WCLK

DIN

DOUT

48

47

46

45

43

2

1

MFP3 / SPI_MOSI / GPI

MFP2 / SPI_MISO / GPIO

MFP1 / SPI_SCK / GPI / I2C_A1

MFP0 / SPI_CSn / GPI / I2C_A0

SELECT

SDA / GPIO

SCL / GPIO

34

35

GPIO2

GPIO1

33

RESET

3

R2

20K

R20

2.2K

EXP_ACLKX/GP0[14] 33

EXP_AFSX/GP0[12] 33

EXP_AXR11/FSX1/GP0[3] 33

EXP_AXR12/FSR1/GP0[4] 33

EXP_AHCLKX/USB_REFCLKIN/UART1_CTS/GP0[10] 33

R10

20K

AVSS_DAC

R21

2.2K

TP6

.

TP7

.

26

AIC_MCLK

AVSS_ADC

AIC_DIN

AIC_DOUT

DRVSS.1

DRVSS.2

S0

S1

S2

VCC

1

56

55

AIC_WCLK

8

19

38

49

R215

10K

37

38

39

40

41

AIC_BCLK

54

53

52

51

50

48

47

46

45

44

43

42

41

40

39

37

36

35

34

33

32

31

30

29

Line Out

1

2

4

15

26,33 AUDIO_EXP_SEL

22

22

22

22

22

DVSS.1

DVSS.2

2 AHCLKX/USB_REFCLKIN/UART1_CTS/GP0[10]

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

5B1

5B2

6B1

6B2

7B1

7B2

8B1

8B2

9B1

9B2

10B1

10B2

11B1

11B2

12B1

12B2

R15

R16

R17

R18

R19

21

20

2 AXR12/FSR1/GP0[4]

B

1A1

1A2

2A1

2A2

3A1

3A2

4A1

4A2

5A1

5A2

6A1

6A2

7A1

7A2

8A1

8A2

9A1

9A2

10A1

10A2

11A1

11A2

12A1

12A2

22

49

42

2 AFSX/GP0[12]

2 AXR11/FSX1/GP0[3]

2

3

4

5

6

7

9

10

11

12

13

14

15

16

18

20

21

22

23

24

25

26

27

28

GND.1

GND.2

GND.3

GND.4

2 ACLKX/GP0[14]

17

C32

0.1uF

U21

SN74CBTLV16212

R13

6

5

AIC_MCLK

AIC_BCLK

AIC_WCLK

AIC_DIN

AIC_DOUT

TLV320AIC3106IRGZ

SPECTRUM DIGITAL INCORPORATED

DSK_3V3

Title:

4,5,25,30,31,32,33,34 I2C0_SDA

4,5,25,30,31,32,33,34 I2C0_SCL

8,18,30,31,32,33 RESETOUTn

5

Page Contents:

AUDIO CODEC

Size:B

DWG NO

Date:

3

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

20 o f

38

DSK_3V3

D

C107

0.1uF

DSK_VIO

U7

TRS3386ECPWR

R142

0

C10

0.1uF

C13

0.1uF

R144

NO-POP

4,33 SPI1_SCS[4]/UART2_TXD/I2C1_SDA/GP1[2]

2,33 AMUTE/UART2_RTSn/GP0[9]

4,33 SPI1_SCS[5]/UART2_RXD/I2C1_SCL/GP1[3]

C1+

C1-

C2+

VCC

DSK_VIO

19

V+

C12

0.1uF

V-

C11

0.1uF

GND

18

VL

12

DIN1

DOUT1

17

RSA_TXD

DIN2

DOUT2

16

RSA_RTS

DIN3

DOUT3

15

C2-

7

8

9

C106

0.1uF

P1

1

6

2

7

3

8

4

9

5

RSA_RXD

RSA_RTS

RSA_TXD

RSA_CTS

20

PWRDOWN

11

ROUT1

RIN1

14

RSA_RXD

10

ROUT2

RIN2

13

RSA_CTS

10

11

DB-9

DSK_VIO

U8

VCC

OE

DEEPSLEEP_nEN 25

4,5,31 RSVD/RTC_ALARM]/UART2_CTSn/GP0[8]/DEEPSLEEPn

GND

SN74LVC1G125DCKR

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

RS232 CONNECTOR

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

21 o f

38

DSK_VIO

DSK_3V3

R336

0

DSK_3V3

R337

NO-POP

DSK_VIO

C138

22uF

C256

.1uF

R176

51K

U45

16

4

11 SD0_DATA2

11 SD0_DATA1

VCC

1A

2A

11 SD0_DATA0

3A

11 SD0_DATA3

12

4A

GND

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

2

3

5

6

11

10

14

13

S

OE

1

15

EXP_SD0_DATA1 32

ONBD_SD0_DATA1

EXP_SD0_DATA0 32

ONBD_SD0_DATA0

R179

51K

R180

51K

R175

51K

R173

51K

SD_MMC_SEL

ONBD_SD_WP

WP

WP

ONBD_SD_INS

CD

CARD_DETECT

9

8

7

6

5

4

3

2

1

ONBD_SD0_CLK

ONBD_SD0_CMD

ONBD_SD0_DATA3

SN74CBTLV3257PW

DSK_3V3

L -- EXPANSION ACCESS

H -- SD CARD ACCESS

C257

.1uF

C139

0.1uF

R133

51K

ONBD_SD0_DATA2

ONBD_SD0_DATA1

ONBD_SD0_DATA0

EXP_SD0_DATA3 32

ONBD_SD0_DATA3

R178

51K

J10

EXP_SD0_DATA2 32

ONBD_SD0_DATA2

R177

51K

COM

CO

DAT2

DAT1

DAT0

VSS2

CLK

VDD

VSS1

CMD

DAT3

C

MMC/SD_CARD

SEL IS 0 = A, 1 =B

U46

16

11

SD_WP

VCC

1A

SD_INS

2A

11 SD0_CLK

3A

11

12

11 SD0_CMD

4A

GND

1B1

1B2

2B1

2B2

3B1

3B2

4B1

4B2

2

3

5

6

11

10

14

13

S

OE

1

15

EXP_SD_WP 32

ONBD_SD_WP

EXP_SD_INS 32

ONBD_SD_INS

EXP_SD0_CLK 32

ONBD_SD0_CLK

EXP_SD0_CMD 32

ONBD_SD0_CMD

SD_MMC_SEL

SN74CBTLV3257PW

DSK_3V3

DSK_VIO

DSK_VIO

DSK_VIO

R339

10K

R338

C258

0.1uF

U48

U47

C259

.1uF

NO-POP

1

4

2

32 UI_PRESENTn

L IS PRESENT

H IS NOT PRESENT

74LVC1G02DCK

2

1

4

SN74LVC1G04

11,32 EMA_CS[2]/GP3[15]

R343

2,33 AHCLKR/UART1_RTSn/GP0[11]

R342

NO-POP

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

SD/MMC CONNECTOR

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

W ednesday, March 30, 2011

Sheet

1

22 o f

38

DSK_VIO

DSK_3V3

U29

C241

0.1uF

5V

C232

1000pF

DSK_3V3

31

42

VCCA.1

VCCA.2

VCCB.1

VCCB.2

C217

1000pF

18

7

C218

0.1uF

C209

22uF

J15

26 LCD_EXP_EN

R261

10K

H = A->B

7,30 LCD_AC_ENB_CSn/GP6[0]

7,30 MMCSD1_DAT[7]/LCD_PCLK/GP8[11]

7,30 MMCSD1_DAT[4]/LCD_VSYNC/GP8[8]

7,30 MMCSD1_DAT[5]/LCD_HSYNC/GP8[9]

4,33 SPI1_SCS[1]/EPWM1A/GP2[15]/TM64P2_IN12

R64

11,32 EMA_BA[0]/GP2[8]

4,6,33 SPI1_SCS[0]/EPWM1B/GP2[14]/TM64P3_IN12

DSK_VIO

R69

NO-POP

25

48

2OE

1OE

24

1

2DIR

1DIR

26

27

29

30

32

33

35

36

2A7

2A6

2A5

2A4

2A3

2A2

2A1

2A0

2B7

2B6

2B5

2B4

2B3

2B2

2B1

2B0

23

22

20

19

17

16

14

13

37

38

40

41

43

44

46

47

1A7

1A6

1A5

1A4

1A3

1A2

1A1

1A0

1B7

1B6

1B5

1B4

1B3

1B2

1B1

1B0

12

11

9

8

6

5

3

2

28

34

39

45

GND.1

GND.2

GND.3

GND.4

GND.5

GND.6

GND.7

GND.8

4

10

15

21

RN2

RPACK4-22

M_LCD_MDISP

1

2

3

4

1

2

3

4

M_LCD_DCLK

M_LCD_VSYNC

M_LCD_HSYNC

M_LCD_BACKLIGHT_PWR

M_LCD_PANEL_PWR

R_LCD_MDISP

R_LCD_DCLK

R_LCD_VSYNC

R_LCD_HSYNC

R_LCD_BACKLIGHT_PWR

R_LCD_PANEL_PWR

R_LCD_PWM0

8

7

6

5

8

7

6

5

RN1

RPACK4-22

M_LCD_PWM0

R_LCD_PANEL_PWR

R_LCD_BACKLIGHT_PWR

R_LCD_MDISP

R_LCD_DCLK

R_LCD_HSYNC

R_LCD_PWM0

R_LCD_VSYNC

R_LCD_B5

R_LCD_B4

SN74AVC16T245DGG

U36

DSK_VIO

R67

10K

C196

1000pF

DSK_3V3

31

42

C219

0.1uF

26 LCD_EXP_EN

H = A->B

VCCA.1

VCCA.2

25

48

2OE

1OE

24

1

2DIR

1DIR

7,30 VP_DOUT[4]/LCD_D[4]/UPP_XD[12]/GP7[12]

7,30 VP_DOUT[3]/LCD_D[3]/UPP_XD[11]/GP7[11]

7,30 VP_DOUT[2]/LCD_D[2]/UPP_XD[10]/GP7[10]

7,30 VP_DOUT[1]/LCD_D[1]/UPP_XD[9]/GP7[9]

7,30 VP_DOUT[0]/LCD_D[0]/UPP_XD[8]/GP7[8]

7,30 VP_DOUT[10]/LCD_D[10]/UPP_XD[2]/GP7[2]

7,30 VP_DOUT[9]/LCD_D[9]/UPP_XD[1]/GP7[1]

7,30 VP_DOUT[8]/LCD_D[8]/UPP_XD[0]/GP7[0]

26

27

29

30

32

33

35

36

2A7

2A6

2A5

2A4

2A3

2A2

2A1

2A0

7,30

7,30

7,30

7,30

7,30

7,30

7,30

7,30

37

38

40

41

43

44

46

47

1A7

1A6

1A5

1A4

1A3

1A2

1A1

1A0

28

34

39

45

GND.1

GND.2

GND.3

GND.4

VP_DOUT[7]/LCD_D[7]/UPP_XD[15]/GP7[15]

VP_DOUT[6]/LCD_D[6]/UPP_XD[14]/GP7[14]

VP_DOUT[5]/LCD_D[5]/UPP_XD[13]/GP7[13]

VP_DOUT[15]/LCD_D[15]/UPP_XD[7]/GP7[7]

VP_DOUT[14]/LCD_D[14]/UPP_XD[6]/GP7[6]

VP_DOUT[13]/LCD_D[13]/UPP_XD[5]/GP7[5]

VP_DOUT[12]/LCD_D[12]/UPP_XD[4]/GP7[4]

VP_DOUT[11]/LCD_D[11]/UPP_XD[3]/GP7[3]

VCCB.1

VCCB.2

18

7

C230

0.1uF

R_LCD_B3

R_LCD_B2

R_LCD_B1

R_LCD_B5

C231

1000pF

LCD_B0_B

R_LCD_G5

R_LCD_G4

R_LCD_G3

R_LCD_G2

2B7

2B6

2B5

2B4

2B3

2B2

2B1

2B0

23

22

20

19

17

16

14

13

M_LCD_B5

M_LCD_B4

M_LCD_B3

M_LCD_B2

M_LCD_B1

M_LCD_G5

M_LCD_G4

M_LCD_G3

1B7

1B6

1B5

1B4

1B3

1B2

1B1

1B0

12

11

9

8

6

5

3

2

M_LCD_G2

M_LCD_G1

M_LCD_G0

M_LCD_R5

M_LCD_R4

M_LCD_R3

M_LCD_R2

M_LCD_R1

GND.5

GND.6

GND.7

GND.8

4

10

15

21

1

2

3

4

8

7

6

5

RN3

RPACK4-22

R_LCD_B5

R_LCD_B4

R_LCD_B3

R_LCD_B2

1

2

3

4

8

7

6

5

RN4

RPACK4-22

R_LCD_B1

R_LCD_G5

R_LCD_G4

R_LCD_G3

1

2

3

4

8

7

6

5

RN5

RPACK4-22

R_LCD_G2

R_LCD_G1

R_LCD_G0

R_LCD_R5

1

2

3

4

8

7

6

5

RN6

RPACK4-22

R_LCD_R4

R_LCD_R3

R_LCD_R2

R_LCD_R1

R_LCD_G1

R_LCD_G0

R_LCD_R5

R_LCD_R4

R_LCD_R3

R_LCD_R2

R_LCD_R1

R_LCD_R5

LCD_R0_B

SPECTRUM DIGITAL INCORPORATED

AM1810 EVM

Page Contents:

BIT MAPPED LCD TOUCH INTERFACE

Size:B

DWG NO

Date:

4

MH2

Title:

HEADER 30X2

MH1

SN74AVC16T245DGG

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

34 TSY1_TOP

34 TSX2_LEFT

34 TSY2_BOTTOM

34 TSX1_RIGHT

RGB565 to RGB666

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

23 o f

38

VCC_5V

U42

IO2

NC2

5

2

IO1 GND

Vcc

USB0_VBUS

TPD2E001DRLRG4

USB0_VBUS 34

J6C

D

1A

SHIELD3

VBUS-A

2A

3A

DD+

4A

GND

SHIELD4

R328

9 FB_USB0_VBUS

USB-micro/A/B connector

FULL SIZE A CONNECTOR

J6B

VCC_5V VCC_5V

R143

10K

DSK_VIO

R158

10K

C110

0.1uF

USB0_VBUS

R140

10K

1B

ATTACH

2B

3B

DD+

4B

GND

SHIELD1

SHIELD2

USB-micro/A/B connector

FULL SIZE B CONNECTOR

J6A

R9

Q8

BSS138

G

S

9 USB0_DRV_VBUS

10K

2

4

3

IN

EN2

EN1

1

9

GND.1

GND.2

OUT2

OUT1

6

7

OC2

OC1

5

8

R141

0R139

0

C6

150uF

C118

4.7uF

C99

0.1uF

TPS2042BDGN

For OTG mode

or device mode

pull ID line high

VBUS

USB0_DM

2AB

D-

USB0_DP

3AB

D+

DSK_3V3

4AB

ID

5AB

GND

R134

10K

USB0_ID

1AB

9

SHIELD5

SHIELD6

SHIELD7

SHIELD8

MH1

MH2

U41

R202

11 USB1_PWR_EN

10K

For host only,

pull ID line low

Q9

BSS138

MICRO A-B CONNECTOR

USB-micro/A/B connector

90 ohm differential pairs

R138

NO-POP

5

6

7

8

9

10

VCC_5V

J27

usb1_vbus

C16

150uF

C134

0.1uF

10 USB1_DM

10 USB1_DP

VCC_5V

U43

1

3

S1

1

2

3

4

VBUS

DD+

GND

5

IO2

NC2

5

2

IO1 GND

Vcc

S2

USB-A connector

TPD2E001DRLRG4

UHPI_HRDY/GP6[13] 8,30

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

USB INTERFACE CONNECTORS

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

24 o f

38

USER DIP SWITCHES

IO EXPANDER

DSK_3V3

DSK_3V3

DSK_VIO

R317 R318 R319 R320 R321 R322 R323

R324

10K

10K

DSK_3V3

R128

0

10K

10K

10K

10K

10K

10K

C87

0.1uF

C79

0.1uF

S2

R124

NO-POP

User_SW_1

User_SW_2

User_SW_3

User_SW_4

User_SW_5

User_SW_6

User_SW_7

User_SW_8

U34

4,5,20,30,31,32,33,34 I2C0_SCL

4,5,20,30,31,32,33,34 I2C0_SDA

VCCI

R125

22

SCL

R117

23

SDA

DSK_VIO

R108

4.7k

INT

RESET

12

GND

VCCP

24

ADDR

21

P17

P16

P15

P14

P13

P12

P11

P10

20

19

18

17

16

15

14

13

User_SW_8

User_SW_7

User_SW_6

User_SW_5

User_SW_4

User_SW_3

User_SW_2

User_SW_1

P07

P06

P05

P04

P03

P02

P01

P00

11

10

9

8

7

6

5

4

User_LED_1

User_LED_2

1

2

3

4

5

6

7

8

R109

R301

R300

R299

R298

R297

R296

R295

R294

1K

1K

1K

1K

1K

1K

1K1K

8 SPST

DSK_3V3

R304

330

D2

Green

.

.

.

TP10

TP8

TP9

R303

330

D3

TCA6416PW

8,30 UHPI_HINTn/GP6[12]

16

15

14

13

12

11

10

9

Green

R302

330

D4

Green

DSK_3V3

R103

10K

DSK_3V3

R104

10K

USER_PB_1 38

SW_RST

JIRA:

TIFREON-98

38

DSK_VIO

R106

10K

DEEPSLEEP_nEN 21

R97

DEEPSLEEP_EN

Q6

BSS138

SPECTRUM DIGITAL INCORPORATED

1K

R98

10K

Title:

Page Contents:

USER SWITCH & LEDS

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Monday, December 20, 2010

Sheet

1

25 o f

38

PROBE GND CONNECTOR

J8

DSK_VIO

D

1

2

R312

1K

R313

1K

R314

1K

HEADER2

R315

1K

J2

1

2

HEADER2

DSK_3V3

DSK_VIO

J9

C

8

7

6

5

4

3

2

1

1

2

HEADER2

S7

8 SPST

9

10

11

12

13

14

15

16

BOOT MODE

Distribute 2 pin headers

around outside edges of the board

7 BOOTMODE[4]

LCD_EXP_EN 23

7 BOOTMODE[3]

AUDIO_EXP_SEL

7 BOOTMODE[2]

AUDIO_EXP_SEL 20,33

R306

7 BOOTMODE[1]

SELECT_VIO 34

0

B

R331

4.7K

DSK_VIO

R111

NO-POP

R112

NO-POP

R113

NO-POP

R114

NO-POP

R290

1K

R289

1K

R288

1K

R287

1K

R332

4.7K

R333

4.7K

R334

4.7K

R305

NO-POP

7 BOOTMODE[7]

7 BOOTMODE[6]

7 BOOTMODE[5]

7 BOOTMODE[0]

A

SPECTRUM DIGITAL INCORPORATED

Title:

Page Contents:

BOOT SWITCH

Size:B

DWG NO

Date:

5

AM1810 EVM

Revision:

A

513302-0031

Tuesday, March 29, 2011

Sheet

1

26 o f

38

EMU0

29

T_EMU0

R78

13

DSK_VIO

DSK_3V3

D

R240

10K

C85

EMU1

DSK_VIO

13

R83

10K

0.1uF

29

J7

R63

T_EMU1

C41

TRSTn

EMU_STS

2

4

6

8

10

12

14

EMU_STS

C59

0.1uF

EMU1

TMS

TDI

1

3

5

7

9

11

13

U24

EMU_STS

TDO

RTCK

JTAG_TCK

EMU0

OE

FTDI_3.3V

GND

0.1uF

R65

33

TCK

SN74LVC1G125DCKR

TI 14 PIN JTAG

R82

10K

VCC

13

TRSTn

TRSTn

13

DSK_VIO

EMBED_EMU_SELn 29

FTDI_3.3V

EMBED_EMU_SELn

C51

0.1 uF

Q4

BSS138

29 T_TRST_N

29

T_TMS

U30

VCCA

4

5

1A1

1A2

C47

0.1 uF

VCCB

16

1B1

1B2

13

12

R274

R266

33

33

11

10

R265

R273

33

33

TMS

TMS

13

TDI

13

TDI

29

29

DSK_VIO

EMU_STS

J4

2

4

6

8

10

12

14

16

18

20

DSK_VIO

1

3

5

7

9

11

13

15

17

19

TRSTn

TDI

TMS

JTAG_TCK

RTCK

TDO

R278

6

7

T_TDI

T_TCK

FTDI_3.3V

R281

10K

EMBED_EMU_SELn

2A1

2A2

2

15

1DIR

1OEn

3

14

2DIR

2OEn

2B1

2B2

DIR AND OEn ARE ON A POWER DOMAIN

GND.1

GND.2

8

9

OEn

L

L

DIR

L

H

FUNCTION

B->A

B<-A

B

SN74AVC4T245PWRE4

DSK_VIO

FTDI_3.3V

HEADER 10X2

C43

0.1 uF

ARM JTAG

U25

VCCA

VCCB

16

4

5

1A1

1A2

1B1

1B2

13

12

6

7

2A1

2A2

2B1

2B2

11

10

C36

0.1 uF

RTCK

29

29

T_RTCK

T_TDO

2

15

1DIR

1OEn

3

14

2DIR

2OEn

13

13