Beruflich Dokumente

Kultur Dokumente

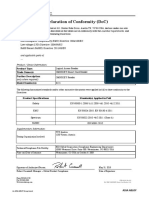

Dell Inspiron 1440 - Wistron Alba Discrete - Rev SB Sec

Hochgeladen von

053530Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Dell Inspiron 1440 - Wistron Alba Discrete - Rev SB Sec

Hochgeladen von

053530Copyright:

Verfügbare Formate

5

Alba Discrete ATI M92-LP gDDR2 Schematics

uFCPGA Mobile Penryn

Intel Cantiga-PM + ICH9M

C

2009-03-23

REV : SA

B

DY : Nopop Component

GM : Pop when Cantiga is GM

PM : Pop when Cantiga is PM

G/P : BOM control if Cantiga is PM

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Date:

5

Monday, March 23, 2009

Cover Page

Rev

SB

Alba Discrete

Sheet

1

of

60

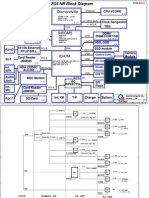

ALBA Discrete Block Diagram

D

PCB LAYER

L1:

L2:

L3:

L4:

L5:

L6:

L7:

L8:

Top

GND

Signal

Signal

VCC

Signal

GND

Bottom

CRT

42

Clock Generator

SLG8SP513VTR

Intel Mobile CPU

Penryn

Socket P

LCD

41

8,9

91.4BK01.001

48.4BK13.0SA

09207

SA

34,35

INPUTS

OUTPUTS

+PWR_SRC

+VCC_CORE

SYSTEM DC/DC

36

TPS51117

INPUTS

OUTPUTS

+PWR_SRC

+1.05V_VCCP

RGB CRT

INPUTS

DDRII

800

DDRII 800 Channel A

DDR Memory I/F

53,54,55,56

OUTPUTS

+15V_ALW

+3.3V_RTC_LDO

+5V_ALW

+3.3V_ALW

+PWR_SRC

Slot 0

LDO

16

DDR II 800 Channel B

DDRII

800

External Graphics

TPS2231RGP

Slot 1

37

L6935TR

Power SW

AGTL+ CPU I/F

PCIe x 16

33

TPS51125

FSB

800/1066MHz

Intel

Cantiga-GM

LVDS(Dual Channel)

:

:

:

:

ISL6266A

SYSTEM DC/DC

VRAM(gDDR2)

32Mbx16x4 (512MB)457,58

ATI M92-LP

C

Project code

Part Number

PCB P/N

Revision

CPU DC/DC

50

INPUTS

OUTPUTS

+1.8V_SUS

+1.5V_RUN

17

10,11,12,13,14,15

New Card

PCIE x 1 & USB 2.0 x 1

(On Express Card board)

DMIx4

CONTROL-LINK

PCIE x 1

10/100 LOM

(7 in 1)SD/MMC

MS/MS Pro/xD

USB2.0

Realtek

RTS5159

ICH9-M

802.11a/b/g/n

High Definition Audio

ACPI 1.1

AZALIA

Azalia

CODEC

USB 2.0 x 1

Bluetooth

45

USB 2.0 x 1

Right Side:

USB x 1

OUTPUTS

+PWR_SRC

+VCC_GFX_CORE

INPUTS

OUTPUTS

+DC_IN

+PBATT

+PWR_SRC

38

TPS51100

51

INPUTS

OUTPUTS

+1.8V_SUS

22

32

LDO

LPC Bus

18,19,20,21

+V_DDR_MCH_REF

+0.9V_DDR_VTT

KBC

SATA

HP OUT

(On Express Card board)

INPUTS

PCI/PCI BRIDGE

SATA

IDT

92HD81

39

MAX8731A

47

OP AMP

MIC IN

+1.8V_SUS

TPS51117

LPC I/F

44

+PWR_SRC

43

CAMERA

(Option)

USB 2.0 x 1

USB 2.0

SATA ports (4)

Internal Mic

OUTPUTS

CHARGER

PCI Express ports (6)

Digital Mic Array

47

(Option)

INPUTS

SYSTEM DC/DC

Mini-Card

PCIE x 1

38

42

USB 2.0/1.1 ports (12)

50

(On Express Card board)

PCIE

SYSTEM DC/DC

TPS51117

Left Side:

USB x 2 46

USB 2.0 x 2

Intel

CardReader

RJ45

CONN

25

RTL8103EL

50

LDO

WINBOND

SPI

WPCE773L

26

37

L6935TR

INPUTS

OUTPUTS

+1.8V_SUS

+1.1V_RUN

<Core Design>

2CH SPEAKER

HDD

44

44

ODD

44

Flash ROM

2MB

47

Touch

PAD

45

Int.

KB

Thermal

& Fan

45

EMC2102

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

28,44

Title

Size

Document Number

Custom

Date:

Block Diagram

Monday, March 23, 2009

Rev

Alba Discrete

Sheet

1

SB

of

60

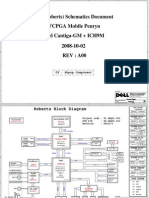

+PWR_SRC

Adapter

TPS51117

ISL6266A

32

TPS51117

36

+1.8V_SUS

39

Charger

MAX8731A

Battery

TPS51117

34,35

SI4835BDY

38

+PBATT

+VCC_CORE

+1.05V_VCCP

+VCC_GFX_CORE

32

TPS51100

TPS51125

L6935TR

38

L6935TR

37

+1.1V_RUN

+5V_ALW2

3D3V_AUX_S5

+15V_ALW

+3.3V_RTC_LDO

37

33

+5V_ALW

+V_DDR_MCH_REF

+3.3V_ALW

+1.5V_RUN

+0.9V_DDR_VTT

TPS2231RGP

TPS2062AD

AO4468

46

+5V_USB1

TPS2062AD

30

+5V_RUN

AO3403

51

+5V_USB2

TPS2231RGP

25

+3.3V_LAN

50

+3.3V_CARDAUX

RTL8103EL

30

+1.5V_CARD

+3.3V_RUN

TPS2034DR

25

50

AO4468

TPS2231RGP

41

50

SI2301

30

+DVDD12

+LCDVDD

+3.3V_CARD

+3.3V_DELAY

Power Shape

Regulator

LDO

Switch

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Power Block Diagram

Size

Document Number

Custom

Date: Monday, March 23, 2009

5

Rev

SB

Alba Discrete

Sheet

1

of

59

ICH9M SMBus Block Diagram

KBC SMBus Block Diagram

+5V_RUN

SRN10KJ-5-GP

1

+3.3V_ALW

+3.3V_RUN

PSDAT1

TPDATA

PSCLK1

TPCLK

ICH9M

SMBCLK

SMB_CLK

SMBDATA

SMB_DATA

TPDATA

TPCLK

TPCLK

45

SRN2K2J-1-GP

DIMM 1

ICH_SMBCLK

ICH_SMBDATA

SCL

SDA

SRN4K7J-8-GP

16

SMBus Address:A0

20

TPDATA

+3.3V_RTC_LDO

+3.3V_RUN

SRN2K2J-1-GP

SCL1

BAT_SCL

SDA1

BAT_SDA

2N7002SPT

DIMM 2

ICH_SMBCLK

ICH_SMBDATA

SDA

Battery Conn.

SRN100J-3-GP

PBAT_SMBCLK1

CLK_SMB

PBAT_SMBDAT1

DAT_SMB

KBC

SCL

17

SMBus Address:A4

2

SMB_CLK

SMB_DATA

SMB_CLK

SMB_DATA

50

ICH_SMBCLK

ICH_SMBDATA

MAX8731

WPC773L

SCL

Clock

Generator

SMBus address:12

09

+3.3V_RTC_LDO

SMBus address:D2

SMB_CLK

SMB_DATA

+3.3V_RUN

Minicard

WLAN

SRN4K7J-8-GP

SMB_CLK

SMB_DATA

32

+3.3V_RUN

SCLK

SDATA

SMBus address:16

31

SDA

Express

Card

TouchPad Conn.

GPIO73/SCL2

KBC_SCL1

GPIO74/SDA2

KBC_SDA1

43

SRN4K7J-8-GP

Thermal

THERM_SCL

SCL

THERM_SDA

SDA

SMBus address:7A

28

2N7002DW-1-GP

26

+3.3V_RUN

SRN2K2J-1-GP

DDC1CLK

LDDC_CLK

DDC1DATA

LDDC_DATA

LCD Conn.

41

+3.3V_DELAY

VGA

+5V_CRT_RUN

SRN2K2J-1-GP

DDC2CLK

M92CRT_DDCCLK

M92CRT_DDCDATA

DDC2DATA

4

+3.3V_DELAY

SRN2K2J-1-GP

DDC_CLK_CON

DDC_DATA_CON

CRT CONN

42

2N7002DW-1-GP

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

54

SMBUS Block Diagram

Size

C

Document Number

Date:

Monday, March 23, 2009

Rev

SB

Alba Discrete

Sheet

E

of

59

Thermal Block Diagram

Audio Block Diagram

0R3-0-U-GP

SPKR_PORT_D_L+

AUD_SPK_L1

AUD_SPK_L1_R

SPKR_PORT_D_L-

AUD_SPK_L2

AUD_SPK_L2_R

SPKR_PORT_D_R-

AUD_SPK_R2

AUD_SPK_R2_R

SPKR_PORT_D_R+

AUD_SPK_R1

SPEAKER

AUD_SPK_R1_R

0R3-0-U-V-GP

DP1

H_THERMDA

DN1

H_THERMDC

CPU

Thermal

EMC2102

VGA_THERMDA

HP

OUT

50

HP0_PORT_A_L

AUD_EXT_MIC_L

HP0_PORT_A_R

AUD_EXT_MIC_R

VREFOUT_A_OR_F

AUD_VREFOUT_B

VGA_THERMDC

MIC

IN

DPLUS

GPU

SC470P50V3JN-2GP

DN2

AUD_HP1_JACK_R

Codec

92HD81

THRMDC

DP2

AUD_HP1_JACK_L

HP1_PORT_B_R

THRMDA

SC470P50V3JN-2GP

2

HP1_PORT_B_L

44

DMINUS

50

54

33R2J-2-GP

DMIC_CLK/GPIO1

AUD_DMIC_CLK

AUD_DMIC_CLK_G_R

DMIC0/GPIO2

AUD_DMIC_IN0

33R2J-2-GP

AUD_DMIC_IN0_R

Digital

MIC

Array

47

DP3

CPU_THERMDA

DN3

CPU_THERMDC

MMBT3904-3-GP

SC1U10V3KX-3GP

SC470P50V3JN-2GP

AUD_INT_MIC_L

INT_MIC_L_R

PORT_C_L

HW T8 sensor

Internal

MIC

AUD_INT_MIC_R

PORT_C_R

28

VREFOUT_C

22

AUD_VREFOUT_C

4K7R2J-2-GP

44

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Thermal/Audio Block Diagram

Size

Document Number

Custom

Date:

A

Monday, March 23, 2009

Rev

SB

Alba Discrete

Sheet

E

of

59

ICH9M Functional Strap Definitions

Usage/When Sampled

HDA_SDOUT

XOR Chain Entrance/

Allows entrance to XOR Chain testing when TP3

PCIE Port Config1 bit1, pulled low. When TP3 not pulled low at rising edge

Rising Edge of PWROK.

of PWROK, sets bit1 of RPC.PC (Cofig Registers:

offset 224h). This signal has weak internal

pull-down.

HDA_SYNC

PCIE config1 bit0,

Rising Edge of PWROK.

This signal has a weak internal pull-down.

Sets bit0 of PRC.PC (Config Registers: Offset

224h).

GNT2#/

GPIO53

PCIE config2 bit2,

Rising Edge of PWROK.

This signal has a weak internal pull-up.

Sets bit2 of PRC.PC2 (Config Registers: Offset

224h).

GPIO20

Reserved.

This signal should not be pulled high.

GNT1#/

GPIO51

ESI Strap (Server Only) ESI compatible mode is for server platforms only.

Rising Edge of PWROK.

This signal should not be pulled low for desktop

and mobile.

GNT3#/

GPIO55

Top-Block Swap

override. Rising Edge

of PWROK.

Sampled low: Top-Block Swap mode (inverts A16 for

all cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

GNT0#:

SPI_CS1#/

GPIO58

Boot BIOS Destination

Selection 0:1.

Rising Edge of PWROK.

Controllable via Boot BIOS Destination bit

(Config Registers: Offset 3410h:bit 11:10).

GNT0# is MSB, 01-SPI, 10-PCI, 11-LPC

SPI_MOSI

GPIO49

SATALED#

SPKR

TP3

GPIO33/

HDA_DOCK

_EN#

ICH9 EDS 642879

PULL-UP 20K

CFG[2:0]

CL_DATA[1:0]

PULL-UP 20K

FSB Frequency Select 000 = FSB1067

011 = FSB667

010 = FSB800

others = Reserved

CL_RST0#

PULL-UP 20K

DPRSLPVR/GPIO16

PULL-DOWN 20K

ENERGY_DETECT

PULL-UP 20K

CFG[4:3]

Reserved

CFG8

CFG[15:14]

CFG[18:17]

HDA_BIT_CLK

PULL-DOWN 20K

CFG5

DMI x2 Select

HDA_DOCK_EN#/GPIO33

PULL-UP 20K

0 = DMI x2

1 = DMI x4 (Default)

CFG6

iTPM Host Interface

HDA_RST#

PULL-DOWN 20K

0 = The iTPM Host Interface is enabled (Note 2)

1 = The iTPM Host Interface is disabled (default)

HDA_SDIN[3:0]

PULL-DOWN 20K

CFG7

HDA_SDOUT

PULL-DOWN 20K

Intel Management

engine crypto strap

0 = Transport Layer Security (TLS) cipher

suite with no confidentiality

1 = TLS cipher suite with confidentiality(Default)

0 = Reserved Lanes, 15->0, 14->1 ect..

1 = Normal operation (Default): Lane Numbered in

Order

PULL-DOWN 20K

CFG9

PCIE Graphics Lane

The pull-up or pull-down

active when configured

for native GLAN_DOCK#

functionality and determined

by LAN controller.

CFG10

PCIE Loopback enable 0 = Enable (Note 3)

1 = Disable (Default)

LDA[3:0]#/FHW[3:0]#

PULL-UP 20K

Integrated TPM Enable, Sample low: the Integrated TPM will be disable.

Rising Edge of CLPWROK. Sample high: the MCH TPM enable strap is sampled

low and the TPM Disable bit is clear, the

Integrated TPM will be enable.

LAN_RXD[2:0]

PULL-UP 20K

LDRQ[0]

PULL-UP 20K

LDRQ[1]/GPIO23

PULL-UP 20K

DMI Termination

Voltage. Rising Edge

of CLPWROK.

PME#

PULL-UP 20K

PWRBTN#

PULL-UP 20K

SATALED#

PULL-UP 15K

SPI_CS1#/GPIO58/CLGPIO6

PULL-UP 20K

PCI Express Lane

Reversal. Rising Edge

of PWROK.

Signal has weak internal pull-up. Sets bit 27

of MPC.LR (Device 28: Function 0:Offset D8).

SPI_MOSI

PULL-DOWN 20K

No Reboot.

Rising Edge of PWROK.

If sampled high, the system is strapped to the

"No Reboot" mode (ICH9 will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.

SPI_MISO

PULL-UP 20K

SPKR

PULL-DOWN 20K

TACH_[3:0]

PULL-UP 20K

XOR Chain Entrance.

Rising Edge of PWROK.

Flash Descriptor

Security Override

Strap. Rising Edge of

PWROK.

This signal should not be pull low unless using

XOR Chain testing.

Sampled low: the Flash Descriptor Security will be

overridden. If high, the security measures will be

in effect. This should only be enabled in

manufacturing environments using an external

pull-up resister.

TP[3]

PULL-UP 20K

USB[11:0][P,N]

PULL-DOWN 15K

LANE5

New Card

GLAN_DOCK#

PULL-UP 20K

LAN

Configuration

HDA_SYNC

PULL-DOWN 20K

LANE3

Montevina Platform Design guide 22339 Rev.0.5

CL_CLK[1:0]

GPIO49

MiniCard WLAN

Rev.1.5

Strap Description

PULL-UP 20K

LANE2

Pin Name

GPIO20

The signal is required to be low for desktop

applications and required to be high for mobile

applications.

Cantiga chipset and ICH9M I/O controller

Hub strapping configuration

Resistor Type/Value

SIGNAL

GNT[3:0]#/GPIO[55,53,51]

PCIE Routing

Rev.1.5

Signal

ICH9 EDS 642879

Comment

ICH9 Integrated pull-up

and pull-down Resistors

CFG[13:12] XOR/ALL

00

10

01

11

CFG16

FSB Dynamic ODT

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled (Default)

CFG19

DMI Lane Reversal

0 = Normal operation (Default): Lane Numbered in

Order

1 = Reverse Lanes

DMI x4 mode [MCH->ICH]: (3->0, 2->1, 1->2 and 0->3)

DMI x2 mode [MCH->ICH]: (3->0, 2->1)

CFG20

Digital Display Port 0 = Only Digital Display Port or PCIE is

operational (Default)

(SDVO/DP/iHDMI)

display Port and PCIe are operating

Concurrent with PCIe 1 = Digital

simulataneously via the PEG port

SDVO

SDVO Present

_CTRLDATA

L_DDC_DATA Local Flat Panel

(LFP) Present

=

=

=

=

Reserve

XOR mode Enabled

ALLZ mode Enable (Note 3)

Disabled (Default)

0 = No SDVO Card Present (Default)

1 = SDVO Card Present

0 = LFP Disabled (Default)

1 = LFP Card Present; PCIE disabled

NOTE:

1. All strap signals are sampled with respect to the leading edge of the (G)MCH

Power OK (PWROK) signal.

2. iTPM can be disabled by a 'Soft-Strap' option in the Flash-decriptor section of

the Firmware. This 'Soft-Strap' is activated only after enabling iTPM via CFG6.

Only one of the CFG10/CFG12/CFG13 straps can be enabled at any time.

USB Table

USB

Pair

0

1

2

3

4

5

6

7

8

9

10

11

Device

USB1

USB2

USB3

RESERVED

MINI CARD

RESERVED

BLUETOOTH

NEW CARD

RESERVED

RESERVED

Card Reader

CAMERA

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Table of Content

Date: Monday, March 23, 2009

Rev

SB

Alba Discrete

Sheet

of

59

R705 1

19

27

43

52

33

56

RN701

1

2

4

3

SRN0J-6-GP

CLK_CPU_BCLK 8

CLK_CPU_BCLK# 8

CPUT1_F

CPUC1_F

58

57

CLK_MCH_BCLK1

CLK_MCH_BCLK1#

RN702

1

2

4

3

SRN0J-6-GP

CLK_MCH_BCLK 10

CLK_MCH_BCLK# 10

CPUT2_ITP/SRCT8

CPUC2_ITP/SRCC8

54

53

CLK_CPU_ITP1

CLK_CPU_ITP1#

RN703

1

2

4

3

SRN0J-6-GP

CLK_CPU_ITP 43

CLK_CPU_ITP# 43

SRCT7/CR#_F

SRCC7/CR#_E

51

50

CLK_PCIE_LAN1

CLK_PCIE_LAN1#

RN704

1

2

4

3

SRN0J-6-GP

CLK_PCIE_LAN 25

CLK_PCIE_LAN# 25

RN712

1

2

4

3

SRN0J-6-GP

CLK_PCIE_VGA 53

CLK_PCIE_VGA# 53

2

1

3

4

SRN0J-6-GP

CLK_PCIE_NEW 50

CLK_PCIE_NEW# 50

CLK_PCIE_MINI1 43

CLK_PCIE_MINI1# 43

FSB

FSC

64

5

FSLB/TEST_MODE

REF0/FSLC/TEST_SEL

55

NC#55

GND48

GNDPCI

GNDREF

18

15

1

Main source: 71.08513.003 (SLG8SP513VTR)

Second source: 71.00875.C03 (RTM875N-606-VD-GRT)

SRCT6

SRCC6

47

CLK_PCIE_VGA1

CLK_PCIE_VGA1#

SRCT10

SRCC10

41

42

CLK_PCIE_NEW1

CLK_PCIE_NEW1#

RN705

SRCT11 SRCT11/CR#_H

SRCC11 SRCC11/CR#_G

40

39

RN706

NEWCARD_CLKREQ#

MINI1_CLKREQ# 43

50

SRCT9

SRCC9

37

38

CLK_PCIE_MINI1_1

CLK_PCIE_MINI1_1#

2

1

3

4

SRN0J-6-GP

SRCT4

SRCC4

34

35

CLK_MCH_3GPLL1

CLK_MCH_3GPLL1#

RN707

2

1

3

4

SRN0J-6-GP

CLK_MCH_3GPLL 11

CLK_MCH_3GPLL# 11

SRCT3/CR#_C

SRCC3/CR#_D

31

32

CLK_PCIE_ICH1

CLK_PCIE_ICH1#

RN708

2

1

3

4

SRN0J-6-GP

CLK_PCIE_ICH 19

CLK_PCIE_ICH# 19

SRCT2/SATAT

SRCC2/SATAC

28

29

CLK_PCIE_SATA1

CLK_PCIE_SATA1#

RN709

2

1

3

4

SRN0J-6-GP

CLK_PCIE_SATA 18

CLK_PCIE_SATA# 18

27MHZ_NONSS/SRCT1/SE1

27MHZ_SS/SRCC1/SE2

24

25

MCH_SSCDREFCLK1 RN711

MCH_SSCDREFCLK1#

2

1

GM

3

4

SRN0J-6-GP

MCH_SSCDREFCLK 11

MCH_SSCDREFCLK# 11

SRCT0/DOTT_96

SRCC0/DOTC_96

20

21

CLK_MCH_DREFCLK1 RN710

CLK_MCH_DREFCLK1#

2

1

GM

3

4

SRN0J-6-GP

CLK_MCH_DREFCLK 11

CLK_MCH_DREFCLK# 11

GND

27_SEL

ITP_EN

PCI0/CR#_A

PCI1/CR#_B

PCI2/TME

PCI3

PCI4/27_SELECT

PCI_F5/ITP_EN

DY

2

VDD96_IO

VDDPLL3_IO

VDDSRC_IO

VDDSRC_IO

VDDSRC_IO

VDDCPU_IO

CK_PW RGD/PD#

8

10

11

12

13

14

C723

SC4D7P50V2CN-1GP

CLKSATAREQ#

CLKREQ#_1

PCI2_TME

CLK_CPU_BCLK1

CLK_CPU_BCLK1#

GM 20090310

65

2 33R2J-2-GP

DY

2 475R2F-L1-GP

2 33R2J-2-GP

SCLK

SDATA

61

60

GM 20090310

48

GND

GNDSRC

GNDSRC

GNDSRC

GNDCPU

GND

20 CLK_14M_ICH

R711 1

2 33R2J-2-GP

2 33R2J-2-GP

R709 1

R710 1

C722

SC4D7P50V2CN-1GP

26 PCLK_KBC

19 CLK_PCI_ICH

C721

SC4D7P50V2CN-1GP

PCI_STOP#

CPU_STOP#

63

R708 1

R707 1

45

44

7

6

20 CLKSATAREQ#

11 CLKREQ#_B

43 PCLK_FWH

USB_48MHZ/FSLA

DY 2SC4D7P50V2CN-1GP

20 CK_PWRGD

DY

17

16,17,20,43 ICH_SMBCLK

16,17,20,43 ICH_SMBDATA

DY

4

16

9

46

62

23

VDDREF

VDD48

VDDPCI

VDDSRC

VDDCPU

VDDPLL3

FSA

DY

CPUT0

CPUC0

X1

X2

22

30

36

49

59

26

R706 2

22R2J-2-GP

ALBA X00

3

2

20 H_STP_PCI#

20 H_STP_CPU#

C713

SCD1U16V2KX-3GP

DY

2

1

2

C720

SCD1U16V2KX-3GP

1

2

C712

SCD1U16V2KX-3GP

C719

SCD1U16V2KX-3GP

1

2

C718

SCD1U16V2KX-3GP

C717

SCD1U16V2KX-3GP

0R3-0-U-GP

C716

SC10U6D3V5MX-3GP

C714

1

2

C715

SC1U10V3KX-3GP

R704

DY

U701

ICS9LPRS355BKLFT-GP-U

2 22R2J-2-GP

1

20 CLK_48M_ICH

3D3V_S0_CK505

CLK_XTAL_OUT

C711

SC12P50V2JN-3GP

50 CLK_48M_CARD

+3.3V_RUN

X-14D31818M-50GP

C724

SCD1U16V2KX-3GP

C708

SC12P50V2JN-3GP

DY

2

1

2

C707

SCD1U16V2KX-3GP

1

2

C706

SCD1U16V2KX-3GP

C705

SCD1U16V2KX-3GP

1

2

C704

SCD1U16V2KX-3GP

C703

SCD1U16V2KX-3GP

DY

X701

0R3-0-U-GP

C702

SC10U6D3V5MX-3GP

CLK_XTAL_IN

ALBA X00

1

2

C701

SC1U10V3KX-3GP

NEWCARD_CLKREQ#

CLK_PCIE_NEW

CLK_PCIE_NEW#

3D3V_S0_CK505_IO

+3.3V_RUN

3D3V_S0_CK505_IO

R703

+3.3V_RUN

2 10KR2J-3-GP

2 10KR2J-3-GP

3D3V_S0_CK505

R702 1

R701 1

EC701

SC22P50V2JN-4GP

NEWCARD_CLKREQ#

MINI1_CLKREQ#

SSID = CLOCK

C710

SC4D7P50V2CN-1GP

C709

SC4D7P50V2CN-1GP

GM 20090311

MCH_SSCDREFCLK1

R712 1

PM

2 0R2J-2-GP

CLK_VGA_27M_NSS 54

3D3V_S0_CK505

B

PCI2_TME

2

1

R716

10KR2J-3-GP

GM

R717

10KR2J-3-GP

Overclocking of CPU and SRC allowed

Overclocking of CPU and SRC not allowed

1

EC702

SC47P50V2JN-3GP

DY

EC703

SC47P50V2JN-3GP

27_SEL

PIN 20

PIN 21

DOT96T

DOT96C

SRCT0

SRCC0

UMA

DY

Output

PCI2_TME

R715

10KR2J-3-GP

MCH_SSCDREFCLK1#

SRC8

CPU_ITP

DY

R714

10KR2J-3-GP

0

1

ITP_EN

Output

MCH_SSCDREFCLK1

ITP_EN

R713

10KR2J-3-GP

DY

27_SEL

PM

3D3V_S0_CK505

3D3V_S0_CK505

R724

10KR2J-3-GP

SEL2 SEL1 SEL0

FSC FSB FSA

1

0

0

0

0

0

0

1

1

0

CPU

100M

133M

166M

200M

266M

1

1

1

0

0

FSB

X

533M

667M

800M

1067M

8 CPU_BSEL2

R718 1

2 10KR2J-3-GP

FSC

8 CPU_BSEL1

R719 1

2 0R2J-2-GP

FSB

8 CPU_BSEL0

R720 1

2 2K2R2J-2-GP

FSA

R721 1

2 1KR2J-1-GP

MCH_CLKSEL0 11

R722 1

2 1KR2J-1-GP

MCH_CLKSEL1 11

R723 1

2 1KR2J-1-GP

MCH_CLKSEL2 11

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Clock Generator SLG8SP513VTR

Size

Document Number

Custom

Date:

Discrete

Monday, March 23, 2009

Rev

Alba Discrete

Sheet

1

SB

of

59

SSID = CPU

TP807

TP808

TP802

TP804

TP803

TP805

TP813

TP810

TP806

TP809

TP801

RSVD_CPU_1

RSVD_CPU_2

RSVD_CPU_3

RSVD_CPU_4

RSVD_CPU_5

RSVD_CPU_6

RSVD_CPU_7

RSVD_CPU_8

RSVD_CPU_9

RSVD_CPU_10

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

RSVD_CPU_11

B1

LOCK#

H4

RESET#

RS0#

RS1#

RS2#

TRDY#

C1

F3

F4

G3

G2

HIT#

HITM#

G6

E4

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

PROCHOT#

THRMDA

THRMDC

STPCLK#

LINT0

LINT1

SMI#

THERMTRIP#

RSVD#M4

RSVD#N5

RSVD#T2

RSVD#V3

RSVD#B2

RSVD#C3 TEST7

RSVD#D2

RSVD#D22

RSVD#D3

RSVD#F6

BCLK0

BCLK1

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_DBRESET#

DY

2 0R2J-2-GP

2 56R2J-4-GP

H_THERMDA

H_THERMDC

H_DSTBP#[3..0]

H_D#[63..0]

10

H_DSTBP#[3..0]

10

H_D#[63..0]

10

CPU1B 2 OF 4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

CPU_PROCHOT#

34

+1.05V_VCCP

H_THRMTRIP#

DY

10

H_DSTBN#[3..0]

10

10 H_DSTBN#0

10 H_DSTBP#0

10 H_DINV#0

H_THERMDA 28

H_THERMDC 28

2 56R2J-4-GP

H_DINV#[3..0]

H_DSTBN#[3..0]

ITP_BPM#0 43

ITP_BPM#1 43

ITP_BPM#2 43

ITP_BPM#3 43

ITP_BPM#4 43

ITP_BPM#5 43

ITP_TCK 43

ITP_TDI 43

ITP_TDO 43

ITP_TMS 43

ITP_TRST# 43

ITP_DBRESET# 20,43

C7

A22

A21

+1.05V_VCCP

H_LOCK# 10

H_CPURST# 10,43

H_RS#[2..0] 10

H_TRDY#

R806 1

D21

A24

B25

H_DINV#[3..0]

2 56R2J-4-GP

H_INIT# 18

H_HIT# 10

H_HITM# 10

R810 1

HCLK

R804 1

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

R805 1

THERMAL

A20M#

FERR#

IGNNE#

H_BREQ#0 10

D20 CPU_IERR#

B3

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

11,18,26,30,54

H_THRMTRIP# should connect to

ICH9 and MCH without T-ing.

+1.05V_VCCP

CLK_CPU_BCLK 7

CLK_CPU_BCLK# 7

+1.05V_VCCP

R814

1KR2F-3-GP

KEY_NC

BGA479-SKT6-GPU7

62.10040.221

CPU_GTLREF0

C802

SC1KP50V2KX-1GP

R807 1

R809 1

R808 1

R801 1

R813

2KR2F-3-GP

10 H_DSTBN#1

10 H_DSTBP#1

10 H_DINV#1

X01 20090112

DY

DY

DY

DY

7 CPU_BSEL0

7 CPU_BSEL1

7 CPU_BSEL2

Layout notes

Z= 55 Ohm 0.5" MAX for CPU_GTLREF0

2 1KR2J-1-GP

2 1KR2J-1-GP

2 1KR2J-1-GP

TEST1

TEST2

CPU_TEST3

2 1KR2J-1-GP

CPU_TEST5

E22

F24

E26

G22

F23

G25

E25

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

AD26

C23

D25

C24

AF26

AF1

A26

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

B22

B23

C21

DATA GRP1

D5

C6

B4

A3

18 H_STPCLK#

18 H_INTR

18 H_NMI

18 H_SMI#

F1

DATA GRP2

A6

A5

C4

H_DEFER# 10

H_DRDY# 10

H_DBSY# 10

DATA GRP0

18 H_A20M#

18 H_FERR#

18 H_IGNNE#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

ADSTB1#

ICH

10 H_ADSTB#1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

AA4

AB2

AA3

V1

ADDR GROUP 1

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H5

F21

E1

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

BR0#

IERR#

INIT#

H_ADS# 10

H_BNR# 10

H_BPRI# 10

K3

H2

K2

J3

L1

CONTROL

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

DEFER#

DRDY#

DBSY#

H1

E2

G5

10 H_ADSTB#0

10 H_REQ#[4..0]

ADS#

BNR#

BPRI#

XDP/ITP SIGNALS

H_A#[35..3]

TP814

RESERVED

10 H_A#[35..3]

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

ADSTB0#

ADDR GROUP 0

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

DATA GRP3

CPU1A 1 OF 4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

MISC

BSEL0

BSEL1

BSEL2

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W 22

Y23

W 24

W 25

AA23

AA24

AB25

Y26

AA26

U22

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

R26

U26

AA1

Y1

COMP0

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPW R#

PW RGOOD

SLP#

PSI#

E5

B5

D24

D6

D7

AE6

H_DSTBN#2 10

H_DSTBP#2 10

H_DINV#2 10

H_DSTBN#3 10

H_DSTBP#3 10

H_DINV#3 10

R812

R811

R803

R802

1

1

1

1

2

2

2

2

27D4R2F-L1-GP

54D9R2F-L1-GP

27D4R2F-L1-GP

54D9R2F-L1-GP

H_DPRSTP# 11,18,34

H_DPSLP# 18

H_DPWR# 10

H_PWRGOOD 18,30

H_CPUSLP# 10

PSI# 34

BGA479-SKT6-GPU7

62.10040.221

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5".

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5".

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

Document Number

Custom

Date: Monday, March 23, 2009

CPU-FSB(1/2)

Rev

SB

Alba Discrete

Sheet

of

59

SSID = CPU

CPU1D

A4

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3

1

2

1

2

DY

C935

SC22U6D3V5MX-2GP

C934

SC22U6D3V5MX-2GP

C901

SC22U6D3V5MX-2GP

C903

SC22U6D3V5MX-2GP

DY

2

C902

SC22U6D3V5MX-2GP

DY

2

DY

2

1

2

1

2

DY

C938

SC22U6D3V5MX-2GP

+VCC_CORE

DY

C908

SC22U6D3V5MX-2GP

+VCC_CORE

C919

SC22U6D3V5MX-2GP

DY

2

DY

C922

SC22U6D3V5MX-2GP

C915

SC22U6D3V5MX-2GP

+VCC_CORE

C907

SC22U6D3V5MX-2GP

X01 20090106

CPU1C3 OF 4

1

2

1

2

C933

SC22U6D3V5MX-2GP

1

2

DY

C932

SC22U6D3V5MX-2GP

C910

SC22U6D3V5MX-2GP

C936

SC22U6D3V5MX-2GP

DY

2

C927

SC22U6D3V5MX-2GP

C921

SC22U6D3V5MX-2GP

DY

2

C916

SC22U6D3V5MX-2GP

1

2

C931

SC22U6D3V5MX-2GP

C912

SC22U6D3V5MX-2GP

C914

SC22U6D3V5MX-2GP

1

2

1

2

C937

SC22U6D3V5MX-2GP

C930

SC22U6D3V5MX-2GP

C929

SC22U6D3V5MX-2GP

DY

2

C928

SC22U6D3V5MX-2GP

C917

SC22U6D3V5MX-2GP

C918

SC22U6D3V5MX-2GP

C920

SC22U6D3V5MX-2GP

1

2

C913

SC22U6D3V5MX-2GP

1

2

C909

SC22U6D3V5MX-2GP

+1.5V_VCCA

C926

SC22U6D3V5MX-2GP

C905

SCD1U16V2KX-3GP

C904

SC1U6D3V2KX-GP

C906

SCD1U10V2KX-4GP

C925

SCD1U16V2KX-3GP

layout note: "+1.5V_VCCA"

as short as possible

+1.5V_RUN

R903

C939

SCD01U16V2KX-3GP

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

0R3-0-U-GP

34

CPU_VID[6..0]

C940

SC10U6D3V5MX-3GP

Layout Note:

Place as close as possible

to the CPU VCCA pin.

PG901

R902 1

2

1

2

100R2F-L1-GP-U

GAP-CLOSE-PWR-3-GP

+VCC_CORE

VCC_SENSE 34

VSS_SENSE 34

VCC_SENSE and VSS_SENSE lines

should be of equal length.

PG902

BGA479-SKT6-GPU7

62.10040.221

VSSSENSE

AE7

AF7

DY

C924

SCD1U16V2KX-3GP

VCCSENSE

AD6

AF5

AE5

AF4

AE3

AF3

AE2

DY

VID0

VID1

VID2

VID3

VID4

VID5

VID6

DY

+1.05V_VCCP

C923

SCD1U16V2KX-3GP

B26

C26

DY

X01 20090106

VCCA

VCCA

DY

+VCC_CORE

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W 21

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

C911

SC22U6D3V5MX-2GP

+VCC_CORE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

TC901

ST220U2D5VBM-LGP

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

R901 1

100R2F-L1-GP-U

4 OF 4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W 23

W 26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

NCTF

PIN

CPU_GND1

TP902

B

CPU_GND2

CPU_GND3

TP901

TP903

CPU_GND4

TP904

BGA479-SKT6-GPU7

GAP-CLOSE-PWR-3-GP

62.10040.221

X01 20090106

A

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

CPU-Power(2/2)

Size

Document Number

Custom

Date:

5

Monday, March 23, 2009

Rev

SB

Alba Discrete

Sheet

1

of

59

SSID = MCH

+1.05V_VCCP

H_SWING routing Trace width and

Spacing use 10 / 20 mil

R1003

221R2F-2-GP

H_SWING Resistors and

Capacitors close MCH

500 mil ( MAX )

R1002

100R2F-L1-GP-U

H_SWING

C1001

SCD1U10V2KX-4GP

H_RCOMP routing Trace width and

Spacing use 10 / 20 mil

1

R1001

2 H_RCOMP

24D9R2F-L-GP

Place R1001 near to the chip ( < 0.5")

H_SWING

H_RCOMP

C5

E3

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SW ING

H_RCOMP

+1.05V_VCCP

F2

G8

F8

E6

G2

H6

H2

F6

D4

H3

M9

M11

J1

J2

N12

J6

P2

L2

R2

N9

L6

M5

J3

N2

R1

N5

N6

P13

N8

L7

N10

M3

Y3

AD14

Y6

Y10

Y12

Y14

Y7

W2

AA8

Y9

AA13

AA9

AA11

AD11

AD10

AD13

AE12

AE9

AA2

AD8

AA3

AD3

AD7

AE14

AF3

AC1

AE3

AC3

AE11

AE8

AG2

AD6

HOST

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_D#[63..0]

8 H_D#[63..0]

R1004

1KR2F-3-GP

C12

E11

8,43 H_CPURST#

8 H_CPUSLP#

A11

B11

H_AVREF

H_DVREF

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPW R#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

J8

L3

Y13

Y1

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

L10

M7

AA5

AE6

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

L9

M8

AA6

AE5

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

B15

K13

F13

B13

B14

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#_0

H_RS#_1

H_RS#_2

B6

F12

C8

H_RS#0

H_RS#1

H_RS#2

C

H_ADS# 8

H_ADSTB#0 8

H_ADSTB#1 8

H_BNR# 8

H_BPRI# 8

H_BREQ#0 8

H_DEFER# 8

H_DBSY# 8

CLK_MCH_BCLK 7

CLK_MCH_BCLK# 7

H_DPWR# 8

H_DRDY# 8

H_HIT# 8

H_HITM# 8

H_LOCK# 8

H_TRDY# 8

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

B

H_DSTBP#[3..0]

H_REQ#[4..0]

H_REQ#[4..0]

H_RS#[2..0]

H_RS#[2..0]

CANTIGA-GM-GP-U-NF

DY

H_CPURST#

H_CPUSLP#

H_A#[35..3]

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

C1002

SCD1U16V2KX-3GP

R1005

2KR2F-3-GP

H_AVREF

H_A#[35..3]

1 OF 10

U1001A

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Cantiga-HOST(1/6)

Size

Document Number

Custom

Date: Monday, March 23, 2009

Rev

SB

Alba Discrete

Sheet

10

of

59

16

16

17

17

SM_RCOMP

SM_RCOMP#

BG22

BH21

M_RCOMPP

M_RCOMPN

SM_RCOMP_VOH

SM_RCOMP_VOL

BF28

BH28

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PW ROK

SM_REXT

SM_DRAMRST#

AV42

AR36

BF17

BC36

CANTIGA_SM_VREF

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

B38

A38

E41

F41

CLK_MCH_DREFCLK

CLK_MCH_DREFCLK#

MCH_SSCDREFCLK

MCH_SSCDREFCLK#

PEG_CLK

PEG_CLK#

F43

E43

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

AE41

AE37

AE47

AH39

DMI_ITXN0_MRXN0

DMI_ITXN1_MRXN1

DMI_ITXN2_MRXN2

DMI_ITXN3_MRXN3

DMI_ITXN0_MRXN0

DMI_ITXN1_MRXN1

DMI_ITXN2_MRXN2

DMI_ITXN3_MRXN3

19

19

19

19

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

AE40

AE38

AE48

AH40

DMI_ITXP0_MRXP0

DMI_ITXP1_MRXP1

DMI_ITXP2_MRXP2

DMI_ITXP3_MRXP3

DMI_ITXP0_MRXP0

DMI_ITXP1_MRXP1

DMI_ITXP2_MRXP2

DMI_ITXP3_MRXP3

19

19

19

19

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

AE35

AE43

AE46

AH42

DMI_IRXN0_MTXN0

DMI_IRXN1_MTXN1

DMI_IRXN2_MTXN2

DMI_IRXN3_MTXN3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

AD35

AE44

AF46

AH43

DMI_IRXP0_MTXP0

DMI_IRXP1_MTXP1

DMI_IRXP2_MTXP2

DMI_IRXP3_MTXP3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

B33

B32

G33

F33

E33

GFX_VR_EN

C34

2 4K02R2F-GP

7 MCH_CLKSEL0

7 MCH_CLKSEL1

7 MCH_CLKSEL2

CFG20

RN1101

4

3

1

2

PM_EXTTS#0

PM_EXTTS#1

SRN10KJ-5-GP

R1128 1

R1108 1

R1107 1

R1103 1

R1127 1

R1124 1

R1102 1

R1106 1

R1104 1

DY

DY

DY

DY

DY

DY

DY

DY

DY

2 2K21R2F-GP

CFG5

2 2K21R2F-GP CFG6

2 2K21R2F-GP CFG7

TP1101

TP1102

2 2K21R2F-GP CFG8

TP1104

2 4K02R2F-GP CFG9

2 2K21R2F-GP CFG10

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

CFG

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

TP1103

TP1105

T25

R25

P25

P20

P24

C25

N24

M24

E21

C23

C24

N21

P21

T21

R20

M20

L21

H21

P29

R28

T28

DMI

FSB setting

2 4K02R2F-GP CFG19

2 2K21R2F-GP CFG12

2 2K21R2F-GP CFG13

2 2K21R2F-GP CFG16

PWROK_R

RSTIN#

R1118

20,26,28 PM_PWROK

0R2J-2-GP

1

R1101

100R2J-2-GP

C1101

SC100P50V2JN-3GP

DY

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

A47

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PW ROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC#BG48

NC#BF48

NC#BD48

NC#BC48

NC#BH47

NC#BG47

NC#BE47

NC#BH46

NC#BF46

NC#BG45

NC#BH44

NC#BH43

NC#BH6

NC#BH5

NC#BG4

NC#BH3

NC#BF3

NC#BH2

NC#BG2

NC#BE2

NC#BG1

NC#BF1

NC#BD1

NC#BC1

NC#F1

NC#A47

CANTIGA-GM-GP-U-NF

2

1

1

2

C1103

SCD01U16V2KX-3GP

AH37

AH36

AN36

AJ35

AH34

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

N28

M28

G36

E36

K36

H36

1

1

+1.8V_SUS

+V_DDR_MCH_REF

1

1

2

R1123

499R2F-2-GP

DY

CLK_MCH_DREFCLK 7

CLK_MCH_DREFCLK# 7

MCH_SSCDREFCLK 7

MCH_SSCDREFCLK# 7

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

DMI_IRXN0_MTXN0

DMI_IRXN1_MTXN1

DMI_IRXN2_MTXN2

DMI_IRXN3_MTXN3

19

19

19

19

DMI_IRXP0_MTXP0

DMI_IRXP1_MTXP1

DMI_IRXP2_MTXP2

DMI_IRXP3_MTXP3

19

19

19

19

R1139

0R3-0-U-GP

R1129

DY10KR2F-2-GP

DY

GM 20090310

TSATN#

B12

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

B28

B30

B29

C29

A28

SM_REXT

RN1102

CLK_MCH_DREFCLK

CLK_MCH_DREFCLK#

2

1

PM

3

4

SRN0J-6-GP

RN1103

MCH_SSCDREFCLK

MCH_SSCDREFCLK#

2

1

PM

3

4

SRN0J-6-GP

GM 20090310

+3.3V_RUN

R1121

56R2J-4-GP

DY

R1122

10KR2J-3-GP

TSATN#_KBC

+1.05V_VCCP

MCH_CLVREF

TSATN#

R1114

1KR2F-3-GP

CL_CLK0 20

CL_DATA0 20

M_PWROK 20

CL_RST#0 20

TP1106

CLKREQ#_B 7

MCH_ICH_SYNC#

TSATN#

R1111

1KR2F-3-GP

C1102

SC2D2U10V3KX-1GP

+1.05V_VCCP

CL_CLK

CL_DATA

CL_PW ROK

CL_RST#

CL_VREF

1

2

2

1

SM_RCOMP_VOL

R1119

DY10KR2F-2-GP

MCH_CLVREF ~= 0.35V

NC

8,18,26,30,54 H_THRMTRIP#

20,34 DPRSLPVR

PLT_RST#

19,25,26,43,50

R29

B7

N33

P32

AT40

AT11

T20

R32

PM

20 PM_SYNC#

8,18,34 H_DPRSTP#

16 PM_EXTTS#0

17 PM_EXTTS#1

GRAPHICS VID

R1112 1

2 2K21R2F-GP CFG18

ME

R1110 1

2 2K21R2F-GP CFG11

MISC

R1115 1

DY

DY

DY

DY

2

M_ODT0

M_ODT1

M_ODT2

M_ODT3

HDA

R1105 1

BD17

AY17

BF15

AY13

R1125

80D6R2F-L-GP

+3.3V_RUN

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

CLK

16

16

17

17

DDPC_CTRLDATA

M_CS0#

M_CS1#

M_CS2#

M_CS3#

TSATN#_KBC 26

L_DDC_DATA

BA17

AY16

AV16

AR13

R1109

3K01R2F-3-GP

DY

Q1101

MMBT3904WT1G-GP

SDVO_CTRLDATA

DMI lanes

* Reverse

PCIE and SDVO are

Only PCIE or SDVO

simultaneously

* operatiing

is operational

via the PEG port

enable

SDVO interface disable

* SDVOLFPinterface

LFP disable

card present

*

SDVO/iHDMI/DP

SDVO/iHDMI/DP

interface disabled *

interface enabled

Normal operation

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

C1105

SCD01U16V2KX-3GP

C1104

SC2D2U10V3KX-1GP

CFG 19

DMI Lane Reserved

CFG 20

SDVO concurrent

with PCIE

FSB Dynamic ODT enable

RESERVED#BG23

RESERVED#BF23

RESERVED#BH18

RESERVED#BF18

16

16

17

17

FSB dynamic ODT disable

CFG 16

BG23

BF23

BH18

BF18

RESERVED#AY21

M_CKE0

M_CKE1

M_CKE2

M_CKE3

SM_RCOMP_VOH

XOR mode enable

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

BC28

AY28

AY36

BB36

R1126

80D6R2F-L-GP

ALLZ mode enable

CFG 13

16

16

17

17

C1143

SCD1U10V2KX-4GP

CFG 12

AY21

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

PCIE loopback enable

RESERVED#B31

RESERVED#B2

RESERVED#M1

AR24

AR21

AU24

AV20

CFG 10

B31

B2

M1

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

R1113

1KR2F-3-GP

+1.8V_SUS

C1144

SCD1U10V2KX-4GP

PCIE GFX lane reversed

16

16

17

17

CFG 9

RSVD

CFG 7

TLS cipher suite with

no confidentiality

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

AP24

AT21

AV24

AU20

ITPM enable

CFG 6

*

ITPM disable

*

TLS cipher suite with

*

confidentiality

PCIE GFX lane

numbered in oder *

PCIE loopback disable

*

ALLZ mode disable

*

XOR mode disable

*

*

+1.8V_SUS

High

DMI X 4

+3.3V_RUN

R1116

499R2F-2-GP

R1117

CLKREQ#_B

Low

DMI X 2

CFG 5

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

CFG Strap

RESERVED#M36

RESERVED#N36

RESERVED#R33

RESERVED#T33

RESERVED#AH9

RESERVED#AH10

RESERVED#AH12

RESERVED#AH13

RESERVED#K12

RESERVED#AL34

RESERVED#AK34

RESERVED#AN35

RESERVED#AM35

RESERVED#T24

C1106

SCD1U10V2KX-4GP

* is current setting

M36

N36

R33

T33

AH9

AH10

AH12

AH13

K12

AL34

AK34

AN35

AM35

T24

DDR CLK/ CONTROL/COMPENSATION

SSID = MCH

2 OF 10

U1001B

10KR2J-3-GP

20

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Cantiga-DMI/CFG(2/6)

Size

Document Number

Custom

Date: Monday, March 23, 2009

Rev

SB

Alba Discrete

Sheet

11

of

59

SSID = MCH

CANTIGA-GM-GP-U-NF

M_A_BS#0 16

M_A_BS#1 16

M_A_BS#2 16

SA_RAS#

SA_CAS#

SA_W E#

BB20

BD20

AY20

M_A_RAS# 16

M_A_CAS# 16

M_A_WE# 16

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

AM37

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

AJ44

AT44

BA43

BC37

AW 12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW 24

BC21

BG26

BH26

BH17

AY25

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_DQS[7..0]

M_A_DQS#[7..0]

M_A_A[14..0]

M_A_DM[7..0]

16

M_A_DQS[7..0]

16

M_A_DQS#[7..0]

M_A_A[14..0]

16

16

M_B_DQ[63..0]

5 OF 10

U1001E

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AK47

AH46

AP47

AP46

AJ46

AJ48

AM48

AP48

AU47

AU46

BA48

AY48

AT47

AR47

BA47

BC47

BC46

BC44

BG43

BF43

BE45

BC41

BF40

BF41

BG38

BF38

BH35

BG35

BH40

BG39

BG34

BH34

BH14

BG12

BH11

BG8

BH12

BF11

BF8

BG7

BC5

BC6

AY3

AY1

BF6

BF5

BA1

BD3

AV2

AU3

AR3

AN2

AY2

AV1

AP3

AR1

AL1

AL2

AJ1

AH1

AM2

AM3

AH3

AJ3

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

SB_BS_0

SB_BS_1

SB_BS_2

BC16

BB17

BB33

M_B_BS#0 17

M_B_BS#1 17

M_B_BS#2 17

SB_RAS#

SB_CAS#

SB_W E#

AU17

BG16

BF14

M_B_RAS# 17

M_B_CAS# 17

M_B_WE# 17

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

AM47

AY47

BD40

BF35

BG11

BA3

AP1

AK2

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

AL47

AV48

BG41

BG37

BH9

BB2

AU1

AN6

AL46

AV47

BH41

BH37

BG9

BC2

AT2

AN5

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

AV17

BA25

BC25

AU25

AW 25

BB28

AU28

AW 28

AT33

BD33

BB16

AW 33

AY33

BH15

AU33

M_B_DM[7..0]

BD21

BG18

AT25

MEMORY

17 M_B_DQ[63..0]

SA_BS_0

SA_BS_1

SA_BS_2

M_A_DM[7..0]

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

MEMORY

AJ38

AJ41

AN38

AM38

AJ36

AJ40

AM44

AM42

AN43

AN44

AU40

AT38

AN41

AN39

AU44

AU42

AV39

AY44

BA40

BD43

AV41

AY43

BB41

BC40

AY37

BD38

AV37

AT36

AY38

BB38

AV36

AW 36

BD13

AU11

BC11

BA12

AU13

AV13

BD12

BC12

BB9

BA9

AU10

AV9

BA11

BD9

AY8

BA6

AV5

AV7

AT9

AN8

AU5

AU6

AT5

AN10

AM11

AM5

AJ9

AJ8

AN12

AM13

AJ11

AJ12

SYSTEM

4 OF 10

U1001D

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DDR

M_A_DQ[63..0]

SYSTEM

16 M_A_DQ[63..0]

DDR

M_B_DM[7..0]

M_B_DQS[7..0]

17

M_B_DQS[7..0]

M_B_DQS#[7..0]

17

M_B_DQS#[7..0]

17

M_B_A[14..0]

M_B_A[14..0]

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

17

CANTIGA-GM-GP-U-NF

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Cantiga-DDR(3/6)

Size

Document Number

Custom

Date: Monday, March 23, 2009

Rev

SB

Alba Discrete

Sheet

12

of

59

NC#E1

NC#D2

NC#C3

NC#B4

NC#A5

NC#A6

NC#A43

NC#A44

NC#B45

NC#C46

NC#D47

NC#B47

NC#A46

NC#F48

NC#E48

NC#C48

NC#B48

2

M33

K33

J33

PEG_COMPI

PEG_COMPO

A41

H38

G37

J37

B42

G38

F37

K37

F25

H25

K25

H24

C31

E32

AF32

AB32

V32

AJ30

AM29

AF29

AB29

U26

U23

AL20

V20

AC19

AL17

AJ17

AA17

U17

E28

G28

J28

G29

CRT_DDC_CLK

CRT_DDC_DATA

TP1303

TP1302

TP1304

TP1301

NCTF

PIN

R1304

0R2J-2-GP

GMCH_GND1

GMCH_GND2

GMCH_GND3

GMCH_GND4

CRT_TVO_IREF

H32

J32

J29

E29

L29

L_VDD_EN

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSB_CLK#

LVDSB_CLK

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

LVDSA_DATA#_3

LVDSA_DATA_0

LVDSA_DATA_1

LVDSA_DATA_2

LVDSA_DATA_3

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

LVDSB_DATA#_3

LVDSB_DATA_0

LVDSB_DATA_1

LVDSB_DATA_2

LVDSB_DATA_3

TVA_DAC

TVB_DAC

TVC_DAC

TV_RTN

TV_DCONSEL_0

TV_DCONSEL_1

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_IRTN

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_TVO_IREF

CRT_VSYNC

T37

T36

PEG_CMP

H44

J46

L44

L40

N41

P48

N44

T43

U43

Y43

Y48

Y36

AA43

AD37

AC47

AD39

PCIE_MRX_GTX_N0

PCIE_MRX_GTX_N1

PCIE_MRX_GTX_N2

PCIE_MRX_GTX_N3

PCIE_MRX_GTX_N4

PCIE_MRX_GTX_N5

PCIE_MRX_GTX_N6

PCIE_MRX_GTX_N7

PCIE_MRX_GTX_N8

PCIE_MRX_GTX_N9

PCIE_MRX_GTX_N10

PCIE_MRX_GTX_N11

PCIE_MRX_GTX_N12

PCIE_MRX_GTX_N13

PCIE_MRX_GTX_N14

PCIE_MRX_GTX_N15

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

PCIE_MRX_GTX_P0

PCIE_MRX_GTX_P1

PCIE_MRX_GTX_P2

PCIE_MRX_GTX_P3

PCIE_MRX_GTX_P4

PCIE_MRX_GTX_P5

PCIE_MRX_GTX_P6

PCIE_MRX_GTX_P7

PCIE_MRX_GTX_P8

PCIE_MRX_GTX_P9

PCIE_MRX_GTX_P10

PCIE_MRX_GTX_P11

PCIE_MRX_GTX_P12

PCIE_MRX_GTX_P13

PCIE_MRX_GTX_P14

PCIE_MRX_GTX_P15

J41

M46

M47

M40

M42

R48

N38

T40

U37

U40

Y40

AA46

AA37

AA40

AD43

AC46

PCIE_MTX_GRX_C_N0

PCIE_MTX_GRX_C_N1

PCIE_MTX_GRX_C_N2

PCIE_MTX_GRX_C_N3

PCIE_MTX_GRX_C_N4

PCIE_MTX_GRX_C_N5

PCIE_MTX_GRX_C_N6

PCIE_MTX_GRX_C_N7

PCIE_MTX_GRX_C_N8

PCIE_MTX_GRX_C_N9

PCIE_MTX_GRX_C_N10

PCIE_MTX_GRX_C_N11

PCIE_MTX_GRX_C_N12

PCIE_MTX_GRX_C_N13

PCIE_MTX_GRX_C_N14

PCIE_MTX_GRX_C_N15

C1302

C1305

C1307

C1301

C1310

C1313

C1314

C1315

C1317

C1330

C1311

C1312

C1316

C1327

C1329

C1332

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

PCIE_MTX_GRX_N0

PCIE_MTX_GRX_N1

PCIE_MTX_GRX_N2

PCIE_MTX_GRX_N3

PCIE_MTX_GRX_N4

PCIE_MTX_GRX_N5

PCIE_MTX_GRX_N6

PCIE_MTX_GRX_N7

PCIE_MTX_GRX_N8

PCIE_MTX_GRX_N9

PCIE_MTX_GRX_N10

PCIE_MTX_GRX_N11

PCIE_MTX_GRX_N12

PCIE_MTX_GRX_N13

PCIE_MTX_GRX_N14

PCIE_MTX_GRX_N15

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

PCIE_MTX_GRX_C_P0

PCIE_MTX_GRX_C_P1

PCIE_MTX_GRX_C_P2

PCIE_MTX_GRX_C_P3

PCIE_MTX_GRX_C_P4

PCIE_MTX_GRX_C_P5

PCIE_MTX_GRX_C_P6

PCIE_MTX_GRX_C_P7

PCIE_MTX_GRX_C_P8

PCIE_MTX_GRX_C_P9

PCIE_MTX_GRX_C_P10

PCIE_MTX_GRX_C_P11

PCIE_MTX_GRX_C_P12

PCIE_MTX_GRX_C_P13

PCIE_MTX_GRX_C_P14

PCIE_MTX_GRX_C_P15

C1303

C1306

C1309

C1304

C1308

C1328

C1324

C1323

C1325

C1326

C1331

C1318

C1319

C1320

C1321

C1322

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP