Beruflich Dokumente

Kultur Dokumente

qp2011

Hochgeladen von

kcshah20120 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

19 Ansichten2 SeitenOriginaltitel

361102 - qp2011

Copyright

© Attribution Non-Commercial (BY-NC)

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

19 Ansichten2 Seitenqp2011

Hochgeladen von

kcshah2012Copyright:

Attribution Non-Commercial (BY-NC)

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 2

1

Seat No.: _____ Enrolment No.______

GUJARAT TECHNOLOGICAL UNIVERSITY

DIPLOMA VI- EXAMINATION MAY-2011

Subject code: 361102 Subject Name: VLSI Technology

Date:19/05/2011 Time: 02:30 pm to 05:00 pm

Total Marks: 70

Instructions:

1. Attempt all questions.

2. Make suitable assumptions wherever necessary.

3. Figures to the right indicate full marks.

4. English version is Authentic

Q.1 (a) Draw general FPGA architecture diagram and explain CLB

(Configurable Logic Block) in detail using simple diagram.

07

(b) Describe VLSI design flow in detail. 07

Q.2 (a) With the help of figures explain the behavior of MOS system under

external bias.

07

(b) Describe three-stage CMOS ring oscillator circuit with diagram. 07

OR

(b) Explain CMOS Inverter circuit in detail. 07

Q.3 (a) Implement full CMOS circuit of XOR function. Also explain pseudo

nMOS gate.

07

(b) Explain two input depletion load NAND gate in detail. 07

OR

Q.3 (a)

Implement the logic function G = C AB + using CMOS. Also explain

OAI gate.

07

(b) Draw two input NOR gate using CMOS and explain its operation by

pMOS network and nMOS network. .

07

Q.4 (a) Explain behavior of bistable circuit in detail. 07

(b) Draw truth table and gate level schematic of SR latch. Also draw and

explain SR latch using CMOS.

07

OR

Q. 4 (a) Explain switching power dissipation of CMOS inverter. 07

(b) Explain clocked JK latch circuit in detail. 07

Q.5 (a) Draw circuit of 4:1 multiplexer and write a VHDL program of it. 07

(b) Write definition of Entity declaration and Architecture body. Write

VHDL programs (i) XOR gate (ii) AND gate.

07

OR

Q.5 (a) Write a VHDL program which generates output X = (AB)+(CD) using

structural method, where A,B,C and D are inputs.

07

(b) Draw circuit of 2-to-4 decoder and write VHDL program of that circuit. 07

************

2

+ --+ + --+ + --+ + --+ ~ ~-- FPGA ~.-|.-- .+.-.+ .-. ~- CLB (-.-.|-+- .~- .-) .|

~.-- .-| ~--~.- +~.~..

07

VLSI |..- .. ~--~.- ~~.. 07

+ --- + --- + --- + --- ~ ~.---| +| MOS '.+- -+~c.- . .+ c- +~.~.. 07

|.~ CMOS -|- ~.|.- ~.-- .-| ~--~.- +~.~.. 07

~~. ~~. ~~. ~~.

CMOS -~.- -|. ~--~.- +~.~.. 07

+ -- + -- + -- + --

~ CMOS -|. ..-. +_ XOR .-.- ~~. ~- pseudo nMOS -. +~.~.. 07

. -+. |+u- . NAND -. ~--~.- +~.~.. 07

~~. ~~. ~~. ~~.

+ -- + -- + -- + -- ~

CMOS ..-. .~- .-.- G = C AB +

~~. ~- OAI -. +~.~..

07

CMOS ..-. . -+. NOR -. .-. ~- -- ~.+-u- pMOS -.~- ~-

nMOS -.~- ..-. +~.~..

07

+ -- + -- + -- + -- ~ .+. -|.- -+~c.- ~--~.- +~.~.. 07

~ ~.- - ._ . ~--. ~ -+.|- .-.. CMOS ..-. ~ ~.- .-|-

+~.~..

07

~~. ~~. ~~. ~~.

+ -- + -- + -- + -- ~ CMOS -~.--. ~|'- +.~- ||+u- +~.~.. 07

-.- ~- -|. ~--~.- +~.~.. 07

+ --+ + --+ + --+ + --+ ~ 4:1 +-.|.--| -|. .-. ~- --. VHDL +.-.+ .. 07

~'-..| |--u- ~- ~.-|.-- .|-| -+.+. .. (i) XOR -. (ii) AND

-.-. VHDL +.-.+ ..

07

~~. ~~. ~~. ~~.

+ --+ + --+ + --+ + --+ ~ VHDL +.-.+ .-- ++'- ~ . - ~ ~...+. X = (AB)+(CD) ~--. --|

u-. ~+. A,B,C ~- D -+. :.

07

2-to-4 |-.- -|. .-. ~- --. VHDL +.-.+ .. 07

************

Das könnte Ihnen auch gefallen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Oxygen Sensor Simulator - JumperDokument7 SeitenOxygen Sensor Simulator - JumperBrianssrt4100% (2)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- 108 PDFDokument28 Seiten108 PDFcoulibalyoumarNoch keine Bewertungen

- Ceramics PPT CEMDokument37 SeitenCeramics PPT CEMskhanveNoch keine Bewertungen

- Pha MGW Rfman 10Dokument81 SeitenPha MGW Rfman 10BogdanNoch keine Bewertungen

- ES PaperDokument22 SeitenES PaperRaghu Nath SinghNoch keine Bewertungen

- Metal Semiconductor FET MESFETDokument26 SeitenMetal Semiconductor FET MESFETsrinathNoch keine Bewertungen

- Samsung Chassis Ksca PDFDokument27 SeitenSamsung Chassis Ksca PDFKornaek SaelimNoch keine Bewertungen

- TCAD - Silvaco DetailedDokument30 SeitenTCAD - Silvaco Detailedraghcharash100% (1)

- Kamranmahar O3O4 1797633: 15. Which Type of Computers Uses The 8-Bit Code Called Ebcdic?Dokument26 SeitenKamranmahar O3O4 1797633: 15. Which Type of Computers Uses The 8-Bit Code Called Ebcdic?AmirSaeedNoch keine Bewertungen

- Vincotech - V23990 P589 A41 PM - FD Rev - 06Dokument29 SeitenVincotech - V23990 P589 A41 PM - FD Rev - 06Gaurav NandaNoch keine Bewertungen

- Okidata - Pacemark 3410 Service ManualDokument249 SeitenOkidata - Pacemark 3410 Service Manual19jayster84Noch keine Bewertungen

- Electric Trains and Japanese Technology: Breakthrough in Japanese Railways 4Dokument9 SeitenElectric Trains and Japanese Technology: Breakthrough in Japanese Railways 4Aee TrDNoch keine Bewertungen

- Coaxial Capacitor Displacement CurrentDokument2 SeitenCoaxial Capacitor Displacement CurrentGopi Srikanth VegiNoch keine Bewertungen

- HDB3 ReportDokument98 SeitenHDB3 ReportCornel CaceamacNoch keine Bewertungen

- A Stable Radio Microphone With Loop AntennaDokument6 SeitenA Stable Radio Microphone With Loop AntennaAdi FadillahNoch keine Bewertungen

- NE700 Valve PositionerDokument9 SeitenNE700 Valve Positionersteve@air-innovations.co.zaNoch keine Bewertungen

- GTAW2Dokument37 SeitenGTAW2JithuJohnNoch keine Bewertungen

- Cascode Amplifiers and Cascode Current MirrorsDokument17 SeitenCascode Amplifiers and Cascode Current MirrorsJohn ErhinyoNoch keine Bewertungen

- Study of Sensors: SensorDokument4 SeitenStudy of Sensors: SensorDavidNoch keine Bewertungen

- Chemistry Corrected Material Unit 12-17Dokument55 SeitenChemistry Corrected Material Unit 12-17Pandu RockingNoch keine Bewertungen

- Afcap ManualDokument39 SeitenAfcap ManualNarendra Bhole0% (1)

- Microelectronic PillsDokument24 SeitenMicroelectronic PillsVenkata KarthikNoch keine Bewertungen

- SK9822-2020 LED DatasheetDokument16 SeitenSK9822-2020 LED DatasheetDaisyNoch keine Bewertungen

- 13 Electro IIIDokument212 Seiten13 Electro IIIReynald Jezreel RamirezNoch keine Bewertungen

- Physics ProjectDokument13 SeitenPhysics ProjectAadi AthreyaNoch keine Bewertungen

- Analog Applications Journal TI Slyt486Dokument38 SeitenAnalog Applications Journal TI Slyt486thietdaucongNoch keine Bewertungen

- FR151 - FR157: FeaturesDokument3 SeitenFR151 - FR157: FeatureselsubberNoch keine Bewertungen

- UNIT 1: Principles of Power ElectronicsDokument15 SeitenUNIT 1: Principles of Power ElectronicsIntekhab AlamNoch keine Bewertungen

- Samsung Pg17n, Pg19n Service ManualDokument85 SeitenSamsung Pg17n, Pg19n Service ManualAZAD MATUBBERNoch keine Bewertungen

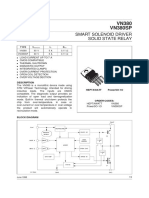

- VN380 Smart Solenoid Driver SpecificationsDokument10 SeitenVN380 Smart Solenoid Driver SpecificationsAdan Pérez EchevarríaNoch keine Bewertungen