Beruflich Dokumente

Kultur Dokumente

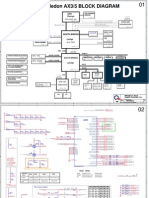

Ts 7500 Schematic

Hochgeladen von

imransiddiquiatvxtCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ts 7500 Schematic

Hochgeladen von

imransiddiquiatvxtCopyright:

Verfügbare Formate

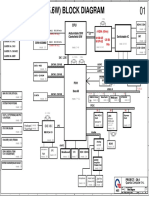

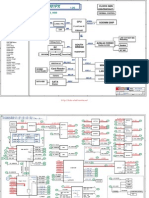

U2 2 39 103

3.3V FB8

USB_HOST0_DP USB_HOST0_DM USB_HOST1_DP USB_HOST1_DM R38 510

11 12 19 18

VDD_33 USB0_DP USB0_DM USB1_DP VCCA_U2O_33 USB1_DM DEV_AN_33 VDD_AN_POW_33 HOST_USB_RES VDD_HOST_AN33 VDD_AN_ETH33 VDD_AN_ETH33 VDD_33 VDD_33

3.3V

C77 128 123 33 13 .1 uF

C78 .1 uF

16

FB7 23 29 64 75 15 38 1.8V 20 32 47 82 98 109 121 2.5V C75 .1 uF C76 .1 uF PHY_GND 3.3V

USB_DEV_DP USB_DEV_DM R45 12.0K

127 126

DEV_USB_DP VDD_RAM_25 DEV_USB_DM VDD_RAM_25 HOST_PLL_18 DEV_USB_RES SYS_PLL_18 VDD_CORE_18

125

CPU_UART_TXD CPU_UART_RXD

107 108

UART_TXD0 UART_RXD0 Res. PU

VDD_CORE_18 VDD_CORE_18 VDD_CORE_18 VDD_CORE_18 VDD_CORE_18 VDD_CORE_18

10/100 Ethernet

J5 4 RX+ RXR14 100 C104

GPIO_A28 GPIO_A29 SPI_CLK SPI_MOSI SPI_MISO

118 119 117 116 115

SPI_CS0# SPI_CS1# SPI_CLK SPI_MOSI SPI_MISO

GPIO_A28 GPIO_A29 GPIO_A27

RX+ RXGPIO_A26 TX+

27 28

24 25 22 R32 11.5K

SCL SDA

7 6

TXSCL/GPIO_A14 SDA/GPIO_A13 REF_RES

6 10 nF

RX_CT ALIGN ALIGN

17 18

INT28 GPIO_A0 GPIO_A1 JTAG_CLK GPIO_A3 GPIO_A15 GPIO_A16 GPIO_A17

5 111 112 113 114 8 9 10

PHY_GND INT28/USB_INT INT29/GPIO_A0 INT30/GPIO_A1 UART0/GPIO_A2 I2SDR/GPIO_A3 I2SSD/GPIO_A15 I2SWS/GPIO_A16 I2SCK/GPIO_A17 RAM_D8 RAM_D9 RAM_D10 RAM_D11 RAM_D12 RAM_D13 LED1/GPIO_A23 LED2/GPIO_A24 RAM_D14 RAM_D15 63 62 61 60 59 58 57 56 DATA_08 DATA_09 DATA_10 DATA_11 DATA_12 DATA_13 DATA_14 DATA_15 DATA_[00:15] ETH_LEFT_LED# 226 1% 3.3V 13 14 RLED+ RLEDR20 11 12 LLED+ LLEDRAM_D0 RAM_D1 RAM_D2 RAM_D3 RAM_D4 RAM_D5 RAM_D6 RAM_D7 74 73 72 71 70 69 68 67 DATA_00 DATA_01 DATA_02 DATA_03 DATA_04 DATA_05 DATA_06 DATA_07 R13 100 10 nF 1 2 POE_TX TX+ TXPOE_45 POE_78 9 10 POE_45 POE_78 C105 3 TX_CT POE_RX 7 8 POE_RX POE_TX

GPIO_A22 GPIO_A23 JTAG_DOUT

43 44 45

LED0/GPIO_A22

Green

SHD SHD 15 16

Yellow

Reset Latch

R17 3.3V 226 1%

CONTROL_25

35 36 34

RAM_ADD0 V25_CONTROL V18_CONTROL V125_CONTROL REF_IN_1.25V RAM_ADD1 RAM_ADD2 RAM_ADD3 RAM_ADD4 RAM_ADD5 RAM_ADD6 RAM_ADD7 RAM_ADD8 CLK_32768KHZ CLK_OUT SYS_RESET# RAM_ADD9 RAM_ADD10 RAM_ADD11 RAM_ADD12

95 94 93 92 91 90 89 88 87 86 85 84 83

ADD_00 ADD_01 ADD_02 ADD_03 ADD_04 ADD_05 ADD_06 ADD_07 ADD_08 ADD_09 ADD_10 ADD_11 ADD_12 ADD_[00:12] FRAME R19 ETH_RIGHT_LED# 226 1% RJ_POE_4602

EC-MJKF4602-PA08

1.2V

66

Left LED

(Green)

FB3

POR

U5 2 VCC RESET# C72 .1 uF ST1001S-2.9V 3 GND 1

3.3V U3 3 D CLK CLR# VCC Q GND 5 4 2 CPU_TCK JTAG_TMS 104 101 105 100 R76 1.0K CPU_RESET# 41 42 XTAL_25_OUT XTAL_25_IN 99 32KHZ CPU_CLKOUT 31 120 106

Link / Activity

R39 WD_RESET# 510

UN-RESET

1 6

RAM_WR# JTAG_TCK RAM_RAS# JTAG_TMS RAM_CAS# JTAG_DIN RAM_CS# JTAG_DO RAM_CKE JTAG_RST# RAM_CLK# RAM_CLK RAM_BA0 RAM_BA1 RAM_DM0

80 78 79 50 51 52 53 77 76 55 54 49 48

RAM_WR# RAM_RAS# RAM_CAS# RAM_CS# RAM_CKE RAM_CLK# RAM_CLK RAM_BA0 RAM_BA1

LOW_VOLT#

74LVC1G175

OD Output

JTAG_DIN

R26 680K C103 U9 6 5 4 SD_POWER# 1 2 3 C37 15 pF DUAL04 EN_SD_POWER 10 nF

R27 680K 30 122 Y2 4 XTAL-HC49

RAM_DM0 RAM_DM1 RAM_QS0 RAM_QS1

FPGA_25MHZ

NC VFS_PGM STAR_8132 TEST_MODE_EN

RAM_DM1 RAM_QS0 RAM_QS1

3.3V

VCC

GND

25MHz

GND_USBD_AN GND_HOST_AN 17 C38 15 pF GND_HOST_AN 14 GND_DEV_AN GND_AN_ETH GND_AN_ETH

GND

GND

GND

GND

GND

GND

GND

GND

GND

124

110

102

21

26

97

96

81

65

46

40

37

SN74LVC2G04DCKR

FB9

GND

Technologic Systems

Title: Rev:

Date

May 30, 2009

PHY_GND

TS-7500 CPU, Ethernet, POR Designer

RLM

Sheet

of

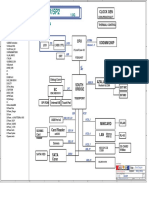

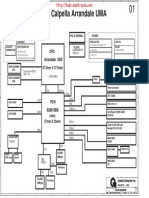

XP2-5 has: 5K LUTS 2 PLLs

44-Pin DIO Header

(Bottom)

HD2 POE_TX POE_78 DIO_40 DIO_38 DIO_36 DIO_34 DIO_32 DIO_30 DIO_28 DIO_26 DIO_24 DIO_22 DIO_20 SDA 44 42 40 38 36 34 32 30 28 26 24 22 20 18 16 DIO_14 DIO_12 3.3V DIO_08 DIO_06 JTAG_DIN JTAG_TMS 14 12 10 8 6 4 2 POE_4 POE_2 DIO_40 DIO_38 DIO_36 DIO_34 DIO_32 DIO_30 DIO_28 DIO_26 DIO_24 DIO_22 DIO_20 DIO_18 GND SPI_CLK/DIO MISO/DIO 3.3V CON_RXD DIO_6 JTAG_TDI JTAG_TMS POE_3 POE_1 DIO_39 DIO_37 DIO_35 DIO_33 DIO_31 DIO_29 DIO_27 DIO_25 DIO_23 DIO_21 DIO_19 DIO_17 5V MOSI/DIO CS#/DIO REBOOT#/DIO MODE1/TXD MODE2/DIO JTAG_TCK JTAG_TDO 43 41 39 37 35 33 31 29 27 25 23 21 19 17 15 13 11 9 7 5 3 1 POE_45 POE_RX DIO_39 28 DIO_37 DIO_35 DIO_33 DIO_31 DIO_29 DIO_27 DIO_25 DIO_23 DIO_21 DIO_19 SCL 5V DIO_13 DIO_11 DIO_09 DIO_07 DIO_05 JTAG_CLK JTAG_DOUT INT28 GPIO_A0 GPIO_A1 SPI_CLK 15 SPI_MOSI SPI_MISO 30 46 39 137 CPU_UART_TXD CPU_UART_RXD 37 13 IO OUT_CSSPIN IO_CLK IO IO_CLK IO IO IO

9 blocks of 1Kx18 Block RAM 12 18x18 Multipliers

FPGA with 5000 LUTs

DIO_[05:40] 87 96 88 74 91 93 99 58 133 104 143 100 IO_CLK IP IO_CLK IO DIO_05 DIO_06 DIO_07 DIO_08 DIO_09 DIO_11 DIO_12 DIO_13 DIO_14 DIO_19 DIO_20 DIO_21 63 101 103 107 109 110 108 113 114 VCCO_4 IO IO IO IO_CLK IO IO IO 141 90 125 R21 226 1% 56 IO IO IO IO IO IO_CLK IO 7 9 57 IO_CLK IN_PROGRAM# IO IN_CFG1 IO IO IO_CLK IO IO_CLK IO_CLK 72 IO IO_CLK IO IO IO IO_CLK IO IO 115 116 119 120 62 121 77 89 DIO_30 DIO_31 DIO_32 DIO_33 DIO_34 DIO_35 DIO_36 DIO_37 83 23 60 85 117 IO VCC_AUX1 IO VCC_AUX2 IO VCC_AUX3 IO_CLK VCC_AUX4 IO IO VCC_JTAG IO IO 123 53 66 43 6 44 55 61 IO DIO_22 DIO_23 DIO_24 DIO_25 DIO_26 DIO_27 DIO_28 DIO_29 4 14 VCCO_7 VCCO_7 IO IO 124 52 31 33 42 49 VCCO_5 VCCO_5 IO IO_CLK IO_CLK VCCO_6 IO_INIT# 76 IO VCCO_3 IO IO 95 105 112 3.3V 136 128 VCCO_0 VCCO_0 IO IO 122 98

100 I/O with 144 pin package "instant ON" = about 1.5 mS input PLL clock = 10 MHz min

1.8V max.

1 RN2-A 4.7K 3 RN2-B 4.7K 4 VCCO_1 IO IO VCCO_2 VCCO_2 IO_CCLK IO 29 129 16 48 102 45 19 18 35 22 21 20 SD_D0 SD_D1 SD_D2 SD_D3 SD_CMD SD_CLK UN-RESET WD_RESET# 2 32KHZ

CLK+

CLK-

IO IO IO IO_CLK IO IO IO IO

I2C

SDA SCL GPIO_A3 GPIO_A15 GPIO_A16 GPIO_A17

1 2 32 27 38 40 78 17

IO IO IO IO IO

EN_SD_POWER

SPI_CS0# SPI_CS1#

GPIO_A28 GPIO_A29

LED0

GPIO_A22

FLASH_CLK FLASH_MOSI FLASH_MISO

HD_JTAG44_7500 JTAG_TMS

MODE1 and MODE2 states are latched when CPU_RESET# is deasserted

JTAG_DIN

TS-7500

Mode 1 Mode 2

Boots from

GPIO_A23

R22 226 1%

142

SER_FLASH_CS# SER_FLASH_WP#

1

MODE1 and MODE2 have 4.7K resistor pull-ups on TS-7500

1 1 0 0

SPI Flash SD card

LED1

0 1 0

94

LED0 shows both

Off-board Flash

50 65

Activity and Link Reserved

Console always is enabled after power up (or reset) but can be switched to DIO after done booting 0 0 also boots from off-board Flash, but may

CPU_CLKOUT 11 71 144 IN_CSSPIS IO IO FPGA_25MHZ IO IO IO IO 70 69 134 130 DIO_38 DIO_39 DIO_40

140 67

VCC_PLL_0 VCC_PLL_1 IO IO IO 132 73 5 36 10 8 47 131 3.3V ETH_LEFT_LED# ETH_RIGHT_LED#

be changed in the future

Reboot# pin (DIO_09) defaults to DIO But can be switched to Reset function SPI bus default to DIO But can be switched

26 CFG0 TOE IO IO IO IO FPGA_CONFIG#

54 92 127 138 RTC_SDA RTC_SCL RTC_INT1

1.2V

24 59 84 118

VCC_INT1 VCC_INT2

IO IO

VCC_INT3 IO_DONE VCC_INT4 IO IO

to SPI function

25

JTAG_DOUT JTAG_DIN JTAG_CLK JTAG_TMS

82 80 81 79

JTAG_DOUT JTAG_DIN JTAG_CLK JTAG_TMS

U8 1 LATTICE_XP2_144 3 LED1

Green GND10 GND11 GND12 GND13 GND14 GND15 GND1 GND2 GND3 GND4 GND5 GND6 GND7 GND8 GND9 2 4

Red

DUAL_RTA_LED

106

111

126

135

139

12

34

41

51

64

68

75

86

97

R23 226 1%

R18 226 1%

Page 37 of Data Sheet (Hot Socketing) Power Supplies can be sequenced in any order but must be monotonic

Pull-up and pull-down resistors are 6 to 30K ohms

Technologic Systems

Title: Rev: TS-7500

Date May 30, 2009

All I/O lines are tri-stated during power cycling

FPGA, DIO Header, JTAG Designer

RLM

Sheet

of 4

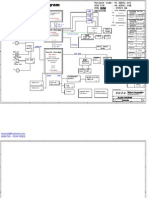

Micro SD Card Socket

3.3V 2 R77 SD_POWER# 1.0K 3 ADD_[00:12] CN7 C67 SD_D0 SD_D1 SD_D2 SD_D3 7 8 1 2 DATA_0 DATA_1 DATA_2 GND DATA_3 FRM1 COMMAND FRM2 SD_CLK 5 CLK FRM3 FRM4 CONN_MICRO_SD 2.5V 9 10 11 12 6 VDD 4 .1 uF ADD_00 ADD_01 ADD_02 ADD_03 ADD_04 ADD_05 ADD_06 ADD_07 ADD_08 ADD_09 ADD_10 ADD_11 ADD_12 1 Q1 1.2V

64 Mbyte DDR1 SDRAM

2.5V C120 U10 C82 .1 uF 49 VREF 19 DNU 50 DNU 14 NC 53 NC 1 VCCINT 18 VCCINT 33 VCCINT VCCIO VCCIO VCCIO VCCIO VCCIO 3 9 55 61 15 R11 100 R12 100 1.2V 10 nF C61 .1 uF C62 .1 uF C63 .1 uF C64 .1 uF C65 .1 uF C66 .1 uF

SD_CMD

29 30 31 32 35 36 37 38 39 40 28 41 42 17 26 27 20 47

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 NC/A13 BA0 BA1 LDM UDM

25 NC 43 NC LDQS UDQS 16 51

RAM_QS0 RAM_QS1 DATA_[00:15]

RAM_BA0 RAM_BA1 RAM_DM0 RAM_DM1

DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7

2 4 5 7 8 10 11 13

DATA_07 DATA_06 DATA_05 DATA_04 DATA_03 DATA_02 DATA_01 DATA_00

R51 2.00K

RAM_RAS# RAM_CAS# RAM_WR#

23 22 21

RAS# CAS# WE#

DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15

54 56 57 59 60 62 63 65

DATA_08 DATA_09 DATA_10 DATA_11 DATA_12 DATA_13 DATA_14 DATA_15

RAM_CKE 44 46 45 R15 100 RAM_CS# 24 RAM_CLK DDR1_RAM CKE CLK# CLK CS# GNDIO GNDIO GNDIO GNDIO GNDIO

4MB Serial Flash

U13 SER_FLASH_CS# FLASH_MISO FLASH_MOSI FLASH_CLK 1 2 5 6 CS# DOUT DIN CLK VCC HOLD# WP# GND 8 7 3 4 SER_FLASH_WP# 3.3V

RAM_CLK#

6 12 52 58 64

34 GND 48 GND 66 GND

DDR RAM Notes

The DDR clock differential pair is the most critical trace on the entire board

3.3V 1 RN1-A 4.7K RN1-B 4.7K 2 DIO_05

The data lines in each byte lane can be swapped on the RAM chip for optimal layout Example: D0 and D5 can be swapped, but not D7 and D8 The trace length of each data line (in a single byte lane) and the respective

5 3

FLASH_SERIAL

DIO_07

RN1-C 4.7K

QS and DM signals must be matched to within 2.5 mm

7

DIO_08

RN1-D 4.7K

JTAG_TMS

Address and Command signals can be grouped together, but must be isolated from data and M_DSQ and M_DM signals (by at least .5 mm) Or run them on different layer

3 1

RN3-A 4.7K RN3-B 4.7K

CPU_TCK SPI_MOSI

JTAG_DIN

5 RN2-C 4.7K 6

3.3V 7 RN5-D 2.2K 8 4 3 RN5-B 2.2K 6 6 5 7 5 RN5-C 2.2K

RTC

U12 SCL VCC SDA OUT BAT 1 XIN 3 8 3.3V

RN3-C 4.7K

EN_SD_POWER

RN3-D 4.7K

CPU_CLKOUT

RTC_SCL RTC_SDA RTC_INT1

RN4-A 2.2K

SDA

I2C bus

3 C83 .1 uF 5 K1 RN4-C 2.2K 7 RN4-D 2.2K 8 6 JTAG_CLK RN4-B 2.2K 4 SCL

UN-RESET 7 RN2-D 4.7K 8

Y1 2 1 4 M41T00S 2 12 pF 3 XOUT GND 4

FPGA_CONFIG#

XTAL_SMT_8X3

R75 1.00K

Technologic Systems

1 RN5-A 2.2K 2

Date

May 30, 2009

Title: Rev:

TS-7500 RAM, SD Card, RTC, Flash Designer

RLM

Sheet

of 4

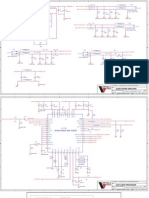

USB Device Port

3.3V Regulator

U6 4 3.3V 2 3.3V GND C99 470 uF 10V LM1117MP-3 1 5V 3 VIN C13 10 uF C70 .1 uF C71 .1 uF C100 C101 3.3V J2 FB4 3.3V 5V C56 .1 uF 10 nF 10 nF 10 nF C57 .1 uF C58 .1 uF C59 .1 uF C114 10 nF C116 10 nF C119 10 nF USB_DEV_DM USB_DEV_DP FB5 1 2 3 4

Single USB

5V DFRAME D+ GND FRAME 6 5

C102

CONN_USB_SINGLE 3.3V FRAME

C84 .1 uF

C85 .1 uF

C86 .1 uF

C87 .1 uF

C88 .1 uF

C112 10 nF

C113 10 nF

C79 .1 uF

C121 10 nF

3.3V

1.2V Regulator

R50 2.00K R99 1.8V 5V 1 ohm

USB Host Ports

PF1 FB2 PTC_750 1 2 3 4 5 6 7 8 FB1 J6

LOW_VOLT#

R47 18.7K

5V D Q4 3 1 + 2 5 U7 4 LMV321_DCK G S 1.2V USB_HOST1_DM USB_HOST1_DP FDN335N USB_HOST0_DP USB_HOST0_DM

Dual USB

9 FRAME 10 FRAME 11 FRAME 12 FRAME

750 uS time constant

C68 .1 uF R44 12.0K

1.2V CONN_USB_DUAL

2 1

C15 Q3 10 uF

C74 .1 uF

C51 .1 uF

C117 10 nF

C73 .1 uF

C106 10 nF

C107 10 nF

C108 10 nF

FRAME

2.5V Regulator 1.8V Regulator

FB6 5V C90 10 uF 6 EN 5 4 VIN PIN FB PGND AGND FAN2002 7 1 2 U11 SW 3 L2 COIL3.3UH R98 3.3V 1 ohm 2 R10 CONTROL_25 100 1.8V 3 2.5V 1 Q2

1.84V nominal

Est. 450 mA load

Est. 100 mA load

C91 10 uF

C92 C80 10 uF R9 15K .1 uF C81 .1 uF

C109

C110

C111 C53 10 nF .1 uF C54 .1 uF C55 .1 uF C115 10 nF

C14 10 uF

C69 .1 uF

C52 .1 uF

C118 10 nF

C60 .1 uF

10 nF

10 nF

DFN package

R33 11.5K

FAN2002

1.3 MHz freq. 50 uA quiescent

Vout = 800mV * [1+ Rtop/Rbot] > 90% eff. at 100-400 mA load 1000 mA max load

Technologic Systems

Title: Rev:

Date

May 30, 2009

TS-7500 Power Supplies, USB Ports Designer RLM Sheet 4 of 4

Das könnte Ihnen auch gefallen

- Aspire+5542+ +5542g.schematicDokument61 SeitenAspire+5542+ +5542g.schematicAndres LañaNoch keine Bewertungen

- Quanta QL4Dokument44 SeitenQuanta QL4Robson ZimmermannNoch keine Bewertungen

- Asus Eeepc 1008ha - Rev 1.3gDokument50 SeitenAsus Eeepc 1008ha - Rev 1.3gFelipeNoch keine Bewertungen

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDokument50 SeitenIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721Noch keine Bewertungen

- Wistron JV50-PU Rev SB PDFDokument61 SeitenWistron JV50-PU Rev SB PDFalbugNoch keine Bewertungen

- Hws 13642Dokument3 SeitenHws 13642dhieward100% (2)

- HP Compaq Presario CQ62 FOXCONN Safina RevMVDokument40 SeitenHP Compaq Presario CQ62 FOXCONN Safina RevMVLolitassAssNoch keine Bewertungen

- LG r480 - Quanta Ql3 Preso-II - Rev 1a PDFDokument39 SeitenLG r480 - Quanta Ql3 Preso-II - Rev 1a PDFJosé Da Silva MataNoch keine Bewertungen

- Acer Aspire 5740 (Wistron JV71-TR) - Wistron - JV71-TrDokument61 SeitenAcer Aspire 5740 (Wistron JV71-TR) - Wistron - JV71-TrCarlosNoch keine Bewertungen

- Asus Eeepc 1008ha - Rev 1.3gDokument50 SeitenAsus Eeepc 1008ha - Rev 1.3gS_sergNoch keine Bewertungen

- Scheme Emachines d640 Aser4251g Je40 DNDokument63 SeitenScheme Emachines d640 Aser4251g Je40 DNvideosonNoch keine Bewertungen

- Asus 1015p2 r1.0g SchematicsDokument43 SeitenAsus 1015p2 r1.0g SchematicsajustNoch keine Bewertungen

- g62 SchematicsDokument40 Seiteng62 SchematicszanaturNoch keine Bewertungen

- Asus Eeepc 1005ha - Rev 1.1gDokument48 SeitenAsus Eeepc 1005ha - Rev 1.1guimNoch keine Bewertungen

- Asus 1001px Rev 1.2g SCHDokument41 SeitenAsus 1001px Rev 1.2g SCHmirdas55Noch keine Bewertungen

- Fujitsu Siemens Lifebook Ah530 Quanta Fh2 Intel Calpella Arrandale Uma Rev 1a SCHDokument34 SeitenFujitsu Siemens Lifebook Ah530 Quanta Fh2 Intel Calpella Arrandale Uma Rev 1a SCHdutu590Noch keine Bewertungen

- Wistron Sjv50 TRDokument59 SeitenWistron Sjv50 TRvimaro24Noch keine Bewertungen

- Acer Aspire 4251 4551 Emachines d440 d640 d640g - Wistron Hm42-Dn Je40-Dn - Rev - 3Dokument63 SeitenAcer Aspire 4251 4551 Emachines d440 d640 d640g - Wistron Hm42-Dn Je40-Dn - Rev - 3chatmarNoch keine Bewertungen

- Asus Eee PC 1015p Rev 1.2gDokument42 SeitenAsus Eee PC 1015p Rev 1.2gYustiani RazakNoch keine Bewertungen

- LG R410 Quanta QL6 Rev 4A SCHDokument39 SeitenLG R410 Quanta QL6 Rev 4A SCHleethax0Noch keine Bewertungen

- At3u Si 0502aDokument37 SeitenAt3u Si 0502aAshok JangraNoch keine Bewertungen

- Asus 1000 r1.2g SchematicsDokument51 SeitenAsus 1000 r1.2g SchematicsEduardo GuajardoNoch keine Bewertungen

- Acer Aspire-5510 Schematic DiagramDokument40 SeitenAcer Aspire-5510 Schematic DiagramAbubakar SidikNoch keine Bewertungen

- HP Envy 15 (Quanta SP7)Dokument42 SeitenHP Envy 15 (Quanta SP7)efeln1Noch keine Bewertungen

- Asus 1015p Rev1.2gDokument42 SeitenAsus 1015p Rev1.2gNibiru CompNoch keine Bewertungen

- Diagrama 333Dokument1 SeiteDiagrama 333xerox4512Noch keine Bewertungen

- HP Compaq Presario Cq61 Quanta Op6 Op7 Tango Ballet Rev A SCHDokument37 SeitenHP Compaq Presario Cq61 Quanta Op6 Op7 Tango Ballet Rev A SCHHugo G.Noch keine Bewertungen

- Vertex 2 Pro SchematicsDokument38 SeitenVertex 2 Pro SchematicsSyed Hassan Raza Naqvi100% (1)

- Aopen Laptop Motherboard Schematic DiagramDokument47 SeitenAopen Laptop Motherboard Schematic DiagrampukymottoNoch keine Bewertungen

- Quanta Ax3 Winbledon Ax3.5 - Da0ax3mb6c2 Ddr3 - Rev 1aDokument30 SeitenQuanta Ax3 Winbledon Ax3.5 - Da0ax3mb6c2 Ddr3 - Rev 1afenixtec1100% (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Von EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Noch keine Bewertungen

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIVon EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINoch keine Bewertungen

- Beginning STM32: Developing with FreeRTOS, libopencm3 and GCCVon EverandBeginning STM32: Developing with FreeRTOS, libopencm3 and GCCNoch keine Bewertungen

- Exploring Arduino: Tools and Techniques for Engineering WizardryVon EverandExploring Arduino: Tools and Techniques for Engineering WizardryBewertung: 4.5 von 5 Sternen4.5/5 (5)

- Practical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11Von EverandPractical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11Noch keine Bewertungen

- 8051 Microcontroller: An Applications Based IntroductionVon Everand8051 Microcontroller: An Applications Based IntroductionBewertung: 5 von 5 Sternen5/5 (6)

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipVon EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNoch keine Bewertungen

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsVon EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsBewertung: 1 von 5 Sternen1/5 (1)

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationVon EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNoch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCVon EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNoch keine Bewertungen

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandVon EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandNoch keine Bewertungen

- CompTIA A+ CertMike: Prepare. Practice. Pass the Test! Get Certified!: Core 1 Exam 220-1101Von EverandCompTIA A+ CertMike: Prepare. Practice. Pass the Test! Get Certified!: Core 1 Exam 220-1101Noch keine Bewertungen

- Advanced Raspberry Pi: Raspbian Linux and GPIO IntegrationVon EverandAdvanced Raspberry Pi: Raspbian Linux and GPIO IntegrationNoch keine Bewertungen

- CCTV Surveillance: Video Practices and TechnologyVon EverandCCTV Surveillance: Video Practices and TechnologyBewertung: 4 von 5 Sternen4/5 (1)

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Von EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Noch keine Bewertungen

- Bridging: Transportation: Chapter 3: The Transportation Planning ProcessDokument28 SeitenBridging: Transportation: Chapter 3: The Transportation Planning ProcesspercyNoch keine Bewertungen

- Past Simple and Continuous - When - While Worksheet - Live WorksheetsDokument4 SeitenPast Simple and Continuous - When - While Worksheet - Live WorksheetsSaraí CaracúnNoch keine Bewertungen

- Fouzia AnjumDokument3 SeitenFouzia AnjumAbdul SyedNoch keine Bewertungen

- Shareholder Agreement 06Dokument19 SeitenShareholder Agreement 06Josmar TelloNoch keine Bewertungen

- REID CatalogDokument54 SeitenREID Catalogzhaoye maoNoch keine Bewertungen

- Andaman & Nicobar: Port BlairDokument4 SeitenAndaman & Nicobar: Port BlairDevan BhallaNoch keine Bewertungen

- Gamboa-Roces vs. Judge PerezDokument1 SeiteGamboa-Roces vs. Judge PerezDiane Dee YaneeNoch keine Bewertungen

- Polyhouse Gerbera CultivationDokument5 SeitenPolyhouse Gerbera CultivationArvindVPawar100% (2)

- Job Description Examples - British GasDokument2 SeitenJob Description Examples - British GasIonela IftimeNoch keine Bewertungen

- Dominar 400 Spare Parts CatalogueDokument82 SeitenDominar 400 Spare Parts CatalogueAkshayaNoch keine Bewertungen

- Soal TKM B. Inggris Kls XII Des. 2013Dokument8 SeitenSoal TKM B. Inggris Kls XII Des. 2013Sinta SilviaNoch keine Bewertungen

- Project of Consumer BehaviourDokument28 SeitenProject of Consumer BehaviourNaveed JuttNoch keine Bewertungen

- Roundup WG Bula MonsantoDokument16 SeitenRoundup WG Bula MonsantodandanyddNoch keine Bewertungen

- Es 590Dokument35 SeitenEs 590Adnan BeganovicNoch keine Bewertungen

- What Is SAP PS (Project Systems) ModuleDokument3 SeitenWhat Is SAP PS (Project Systems) ModuleahmerNoch keine Bewertungen

- ABAP On HANA Interview QuestionsDokument26 SeitenABAP On HANA Interview QuestionsNagesh reddyNoch keine Bewertungen

- Stps 20 H 100 CTDokument8 SeitenStps 20 H 100 CTPablo Cruz ArchundiaNoch keine Bewertungen

- Ad CVDokument2 SeitenAd CVzahid latifNoch keine Bewertungen

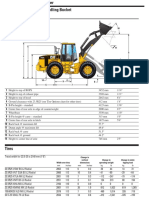

- Cat It62hDokument4 SeitenCat It62hMarceloNoch keine Bewertungen

- Guest AccountingDokument8 SeitenGuest Accountingjhen01gongonNoch keine Bewertungen

- Tamil Nadu Industrial Establishments (Conferment of Permanent Status To Workman Act, 1981Dokument12 SeitenTamil Nadu Industrial Establishments (Conferment of Permanent Status To Workman Act, 1981Latest Laws TeamNoch keine Bewertungen

- Global Grants Community Assessment FormDokument3 SeitenGlobal Grants Community Assessment Formlalitya xavieraNoch keine Bewertungen

- Occupational Stress Questionnaire PDFDokument5 SeitenOccupational Stress Questionnaire PDFabbaskhodaei666Noch keine Bewertungen

- FM - 30 MCQDokument8 SeitenFM - 30 MCQsiva sankarNoch keine Bewertungen

- Peace Corps Guatemala Welcome Book - June 2009Dokument42 SeitenPeace Corps Guatemala Welcome Book - June 2009Accessible Journal Media: Peace Corps DocumentsNoch keine Bewertungen

- 4 3 3LeaseLinesignedDokument42 Seiten4 3 3LeaseLinesignedJagat Brahma PatraNoch keine Bewertungen

- 2B. Glicerina - USP-NF-FCC Glycerin Nutritional Statement USP GlycerinDokument1 Seite2B. Glicerina - USP-NF-FCC Glycerin Nutritional Statement USP Glycerinchristian muñozNoch keine Bewertungen

- Electrical NTPCDokument24 SeitenElectrical NTPCSenthil KumarNoch keine Bewertungen

- National Geographic - April 2020 PDFDokument160 SeitenNational Geographic - April 2020 PDFIbn ZubairNoch keine Bewertungen

- Deploying MVC5 Based Provider Hosted Apps For On-Premise SharePoint 2013Dokument22 SeitenDeploying MVC5 Based Provider Hosted Apps For On-Premise SharePoint 2013cilango1Noch keine Bewertungen