Beruflich Dokumente

Kultur Dokumente

Familles Des Circuits Intégrés Logiques

Hochgeladen von

BALLOUK SoufianeOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Familles Des Circuits Intégrés Logiques

Hochgeladen von

BALLOUK SoufianeCopyright:

Verfügbare Formate

@ CY TecrCl02 dcembre 98 V1.

1 1 / 11 Familles de circuits intgrs logiques

Fam|||es de c|rcu|ts |ntgrs |og|ques

Les familles me font peur.

Georges Bernanos in Journal dun cur de campagne .

I. Prsentation - Gnralits

Il nest nul besoin de connatre de la manire la plus approfondie la structure interne dun composant

pour pouvoir le mettre en uvre de faon efficace, les notices techniques dlivrent toutes les informations

ncessaires la meilleure mise en oeuvre. Mais si on dsire apprhender le comportement exact dune

porte logique, lobservation externe nest plus de mise : il faut entrer au cur de la structure pour

comprendre le fonctionnement.

Lobjet de ce document est danalyser les technologies des circuits intgrs les plus utilises,

regroupes au sein de familles logiques.

Les aspects externes (tensions et courants dentre aux divers niveaux logiques) avaient dj t

voqus dans le document Caractristiques des circuits intgrs logiques . Les lments prsents ici

permettent de justifier les valeurs rencontres.

I.1. Les technologies en prsence

Une famille de circuits logiques intgrs regroupe un ensemble dlments ralisant chacun une

fonction logique lmentaire ou un systme logique plus ou moins complexe, mais btis sur des principes

de base communs. Ceci leur permet de pouvoir tre associs au sein dune mme famille en respectant un

comportement commun, cest la compatibilit.

Au cours du dveloppement industriel des circuits intgrs, plusieurs familles se sont succdes,

chacune ayant sa structure propre. Initialement la famille DTL, abrviation de Diode-Transistor Logic,

permettait de raliser simplement une porte NAND. Des modifications complmentaires, notamment le

remplacement des diodes dentre par un transistor multi-metteur, ont abouti la structure de base de la

famille TTL, abrviation de Transistor-Transistor Logic.

La famille TTL, ralise en technologie bipolaire, a acquis une position dominante pour les

applications courantes jusqu lapparition des circuits CMOS (Complementary Metal Oxide

Semiconductor), issus dune technologie plus rcente base de transistors MOS.

Pour des applications requrant une grande rapidit, la famille ECL (Emitter Coupled Logic), savre

la plus performante. Elle est simplement cite mais ne sera pas tudie dans ce document.

I.2. Rappels sur le transistor bipolaire

Les lments de prsentation du transistor bipolaire sont objet du document Lessentiel sur le

transistor bipolaire. Le fonctionnement logique ne requrant que le comportement non linaire ou satur-

bloqu du transistor.

I.3. Rappels sur le transistor MOS

Les lments de prsentation du transistor MOS sont objet du document Lessentiel sur le transistor

MOS . Ici aussi, seul le comportement non linaire est retenu.

II. Les familles TTL

II.1. Structure DTL

Pour comprendre le fonctionnement de la technologie TTL, on peut sintresser au fonctionnement de la

structure DTL (Diode-Transistor Logic) de la porte NAND deux entres dcrit lannexe 1.

II.2. Structure TTL

La structure TTL remplace les diodes dentre par un transistor multi-metteur comme lindique la

Figure 1. Ltage de sortie, appel totem pole (Figure 2) , amliore les commutations de la sortie et la

stabilit des niveaux logiques.

@ CY TecrCl02 dcembre 98 V1.1 2 / 11 Familles de circuits intgrs logiques

S

3

R

4

R

130

1 K

E1

E2

5V

3

Q

4

Q

2

Q

2

R

1,6 K

1

R

4 K

1

Q

2

D

1

D

3

D

S

3

R

4

R

3

Q

4

Q

2

Q

2

R

3

D

Figure 1 : structure TTL (NAND2). Figure 2 : totem pole. Figure 3

II.3. Etude de la structure TTL

Pour tudier la structure TTL, on remplace le transistor multi-metteur par son quivalent diodes

(Figure 3). On obtient une structure dont ltude prsente lannexe 2 se rapproche de la DTL.

II.4. Les variantes

II.4.1. Technologie TTL standard

La technologie TTL dite standard est celle dcrite dans les paragraphes II.2. et II.3. Elle correspond

au principe de base de la technologie TTL. Cette structure est peu rapide pour une consommation leve.

Chacun des dfauts est rgl par une variante technologique qui conduit dautres familles TTL.

II.4.2. Technologie TTL L

Premire amlioration : la consommation. Dans ce cas les circuits de faible consommation rpondent

la dnomination de TTL L (L pour Low power). La structure identique la TTL standard fait appel des

valeurs de rsistances plus leves. La consommation est videmment rduite mais cest au dtriment des

temps de propagation qui sallongent.

Cette technologie tait trs employe il y a une quinzaine dannes lorsquil fallait diminuer la

consommation.

II.4.3. Technologie TTL S

La diode Schottky

1

possde la proprit de limiter laccumulation des porteurs de charges lors des

commutations. Les temps de changement dtat (passant-bloqu et bloqu-passant) sen trouvent donc

fortement diminus. Leur utilisation comme diode de dsaturation des transistors amliore nettement les

performances temporelles : cest la technologie TTL S (S pour Schottky).

Figure 4 : diode Schottky. Figure 5 : transistor Schottky.

Le symbole dune telle diode est donn la Figure 4. Le transistor qui en est driv, dit Schottky, est

la Figure 5, tandis que la porte utilisant les nouveaux transistors est indique la Figure 6. Linconvnient

des rsistances de faible valeur demeure et handicape la consommation.

1

Schottky (Walter), physicien allemand (1886-1976). Inventeur de la ttrode, explication du bruit de grenaille dans les amplificateurs,

travaux sur les semi-conducteurs.

@ CY TecrCl02 dcembre 98 V1.1 3 / 11 Familles de circuits intgrs logiques

S

3

R

3

R

50

500

E1

E2

5V

4

Q

6

Q

2

Q

2

R

900

1

R

2,8 K

1

Q

2

D

1

D

3

Q

5

Q

5

R

250

4

R

3,5 K

S

7

R

4

R

120

1,5 K

E1

E2

5V

3

Q

5

Q

1

Q

3

R

8 K

1

R

20 K

2

D

1

D

2

Q

4

Q

6

R

3 K

5

R

4 K

2

R 12 K

D

3

D

4

D

5

D

6

Figure 6 : structure S. Figure 7 : structure LS.

II.4.4. Technologie TTL LS

Pour rgler le problme de consommation de la technologie TTL S, on effectue un mixage avec le

principe de la basse consommation des TTL L. Le rsultat est la technologie TTL LS qui joue sur les deux

tableaux de la consommation et de la vitesse.

La structure correspondante est donne la Figure 7. On remarquera une complexit accrue de la

structure. Cette technologie restait cependant jusqu il y a encore peu de temps la TTL ordinaire (voir le

cycle de vie des diffrentes technologies la Figure 18).

II.4.5. Technologie TTL F

Dans le soucis toujours plus marqu de favoriser la rapidit des composants (toujours plus vite !), la

technologie F (F pour fast) apporte sa contribution par lemploi de transistors bipolaires plus rapides que

la srie S avec une consommation 5 fois plus faible environ.

II.4.6. Technologies TTL avances : AS et ALS

Drives des technologies prsentes prcdemment, les technologies avances (A pour advanced)

mettent en uvre les progrs rcent en matire de circuits intgrs bipolaires (fin des annes 80).

II.4.7. Performances compares des technologies TTL

Std L S LS F AS ALS

Tension dalimentation V

CC

(V)

55% (74_ ) ou 10% (54_ )

V

OHmin

(V) 2,4 2,4 2,7 2,7 2,7 V

CC

-2 V

CC

-2

V

IHmin

(V) 2 2 2 2 2 2 2

V

OLmax

(V) 0,4 0,3 0,5 0,5 0,5 0,5 0,4

V

ILmax

(V) 0,8 0,8 0,8 0,8 0,8 0,8 0,8

Retard de propagation (ns) 9 33 3 9,5 6 3 5

Consommation (mW) 10 1 23 2 5 30 5

Frquence maximale (MHz) 25 3 80 30 100

@ CY TecrCl02 dcembre 98 V1.1 4 / 11 Familles de circuits intgrs logiques

II.5. Les entre et sorties particulires

II.5.1. Entre trigger de Schmitt

Lensemble Q

1

Q

2

de la Figure 8 (porte

inverseuse 7414) et les rsistances de

polarisation constituent un trigger de schmitt

transistors.

Derrire D

3

, on retrouve les tages de

sortie de tous types.

Rappel du symbole IEC :

E

3

Q

D

1

2

Q

1

Q

D

2

R

1

R

2

R

3

R

4

R

5

D

3

Figure 8 : entre trigger de Schmitt.

II.5.2. Sortie buffrise (amplifie)

S

5

R

3

R

4

Q

5

Q

2

Q

2

R

3

Q

4

R

Cette configuration reprend assez

largement la structure totem pole la

diffrence que le transistor suprieur est

remplac par un assemblage Darlington

2

.

Ceci a pour consquence de confrer ce

transistor quivalent un fort gain et donc un

courant dmetteur plus important.

On remarquera aussi la disparition de la

diode D

3

de la structure totem pole qui est en

fait compense par la diode base-metteur

du transistor supplmentaire.

Rappel du symbole IEC :

Figure 9 : sortie buffrise.

II.5.3. Sortie collecteur ouvert

S

3

R

3

Q

2

Q

2

R

Sur cette sortie le transistor et la diode

suprieurs ont t purement et simplement

gomms.

Il ne subsiste que le transistor infrieur

qui attire le potentiel de la sortie la masse.

Pour assurer un niveau logique 1 en

sortie, il faut complter la polarisation de Q

3

par une rsistance de tirage V

cc

.

Rappel du symbole IEC : .

Figure 10 : sortie collecteur ouvert.

II.5.4. Sortie trois tats

Le principe de cette porte trois tats apparat dans le document Caractristiques des circuits

intgrs logiques , paragraphe V.3.

La structure de la porte doit assurer le blocage des deux transistors de la sortie totem pole pour assurer

ltat haute impdance lorsque lentre de validation est inactive. Dans ces conditions, la borne est

flottante , cest dire quelle nimpose aucun potentiel. Pour obtenir cela, en examinant la Figure 11,

lentre de validation (contrle) place 0 assure le blocage travers une porte OUI interne des

transistors Q

11

et Q

13

. On remarquera la sortie gr par un montage Darlington pour assurer la

caractristique amplification .

On rappelle quune sortie trois tats est repre par un symbole ( ) plac en regard de la sortie.

2

Darlington (),

@ CY TecrCl02 dcembre 98 V1.1 5 / 11 Familles de circuits intgrs logiques

Contrle

5V

4

Q

5

Q

2

Q

1

R

1

Q

1

D

3

D

3

Q

2

R

3

R

4

R

5

R

6

R

7

R

9

R

10

R

8

R

11

R

6

Q

7

Q

8

Q

11

Q

9

Q

10

Q

12

Q

13

Q

2

D

4

D

5

D

Porte OUI Entre Porte NAND trois entres

6

D

S

Figure 11 : structure interne dune porte OUI trois tat (74126).

III. Familles CMOS

III.1. La technologie CMOS

III.1.1. Inverseur NMOS

Lassemblage de la Figure 12 assure que le canal de Q

1

est

toujours ouvert (transistor passant) car sa grille est polarise

positivement.

Si V

entre

= 0, alors le canal de Q

2

est ferm (transistor

bloqu). Sa rsistance de canal est trs leve. En consquence,

le potentiel de la sortie est proche de V

DD

.

Si V

entre

= V

DD

, Q

2

est passant. En supposant les transistors

identiques, la tension de sortie serait moiti de celle

dalimentation. En fait le transistor Q

2

est construit pour avoir

une rsistance de canal environ 100 fois plus faible que celle de

Q

1

. Il en rsulte que le potentiel de la sortie est proche de 0V.

Le fonctionnement obtenu est celui dun inverseur.

1

Q

2

Q

Entre

Sortie

VDD

Figure 12 : inverseur NMOS.

III.1.2. Inverseur CMOS

Dans le paragraphe prcdent, on a envisag la ralisation des oprateurs transistors NMOS

exclusivement. Mais en utilisant des transistors des deux types, assembls systmatiquement par paires, on

obtient des structures CMOS (Complementary MOS).

La Figure 13 montre le transistor MOS canal N associ

un MOS canal P pour former une paire dinterrupteurs

complmentaires (lorsque lun est ouvert, lautre est ferm, et

rciproquement).

Si V

entre

= 0, alors le transistor Q

1

quivalent un

interrupteur ferm tandis que Q

2

est quivalent un interrupteur

ouvert. Le potentiel de la sortie est alors proche de V

DD

.

Si V

entre

= V

DD

, alors le comportement est inverse si bien que

la tension de sortie est alors proche de 0.

Le fonctionnement obtenu caractrise celui dun inverseur.

1

Q

2

Q

Entre Sortie

VDD

Figure 13 : inverseur CMOS.

@ CY TecrCl02 dcembre 98 V1.1 6 / 11 Familles de circuits intgrs logiques

III.1.3. Autre structure : oprateur NAND CMOS

La structure de la Figure 14 prsente un oprateur NAND CMOS deux entres. Son tude est

prsente de manire synthtique dans le Tableau 1.

Tensions

dentre

Etat des transistors

Tension de

sortie

E1 E2 Q

1

Q

2

Q

3

Q

4

0 0 P P B B V

DD

0 V

DD

P B B P V

DD

V

DD

0 B P P B V

DD

V

DD

V

DD

B B P P 0

Tableau 1

2

Q

Entre 1

Sortie

VDD

3

Q

1

Q

4

Q

Entre 2

Figure 14 : oprateur NAND CMOS.

III.1.4. Protection des entres

Entre

R

Diodes

rparties

Vers la grille des

transistors MOS

La commande en tension des transistors MOS

offre un avantage notable. Mais la pellicule

isolante au niveau de la grille est trs mince ce

qui la rend trs sensible aux surtensions surtout

lectrostatiques. Cet effet provoque le claquage

de lisolant et la destruction du transistor surtout

lors des manipulations.

Figure 15 : protection dentre.

Pour se prmunir de se risque, les entres sont associes un circuit de protection contre les

surtensions comme lindique la Figure 13. Cette insensibilit aux surtensions est obtenue au dtriment du

courant consomm par la porte.

III.2. Les familles CMOS

III.2.1. Caractristiques des sries CMOS

La tension dalimentation (souvent note V

DD

) de ces circuits peut tre choisie entre 3 et 18 V

contrairement aux 5 V de la TTL. Ceci permet une immunit au bruit plus importante et assure une

adaptation aise en cas dutilisation de composants TTL.

En CMOS, les niveaux logiques correspondent pratiquement aux tensions extrmes : 0V pour 0 et

V

DD

pour 1 . Ceci est d aux faibles chutes de tension dans les transistors. Les valeurs limites des

tensions sont fixes par rapport la tension dalimentation (Tableau 2). On remarquera que ces niveaux

sont bien moins contraignants quen TTL. Ces valeurs justifient aussi laffirmation sur limmunit au bruit :

30% de V

DD

dans tous les cas et que lon augmente en levant la tension dalimentation.

Minimum Maximum

V

DD

3 V 18 V

V

OH

V

DD

V

IH

70% V

DD

V

OL

0 V

V

IL

30% V

DD

Tableau 2 : niveaux de tension en technologie CMOS.

En raison des rsistances leves donc des courants proches de 0, la consommation statique des CMOS

est pratiquement nulle (qq nW). Les CMOS sont les champions de la trs faible consommation ! Ds que la

frquence augmente, le nombre de commutations slve et la puissance dissipe augmente

proportionnellement (de lordre du mW 1 MHz).

Le problme de la sortance ne provient pas de la charge impose la sortie dune porte puisque les

courants sont trs faibles. Par contre la multiplication des entres connectes une sortie augmente la

capacit de charge et donc les temps de propagation lors des commutations. On admet une sortance de 50

environ en basse frquence. Lorsque la frquence augmente cette sortance diminue.

@ CY TecrCl02 dcembre 98 V1.1 7 / 11 Familles de circuits intgrs logiques

Dernier point, si une entre est inutilise, il est impratif de la relier au potentiel qui la rend inactive.

Laisse en lair, elle pourrait capter des signaux parasites auxquels elle est trs sensible. Sur ce mme

point, les entres sont protges par un ensemble de diodes contre les dcharges dlectricit statique qui

dtruisent les transistors.

III.2.2. La srie 4000 : lanctre

Cette srie est la plus ancienne. Elle apparat aussi dans la srie 74C mais avec les mmes numros de

botier et le mme brochage quen TTL (compatibilit de brochage). Elle appartient dsormais au pass.

III.2.3. Sries AC et ACT : lamlioration de la technologie CMOS

La srie AC (Advanced Cmos) est lvolution de la srie de C de base. Le suffixe T indique la

compatibilit des entres et sorties avec les sries TTL.

III.2.4. Sries HC, HCT, AHC et AHCT : la technologie CMOS rapide

Les sries disposant du suffixe H (High speed) sont fondes sur la technologie CMOS rapide. Elles

existent dans les diffrentes dclinaisons suivant quelles sont avances (A), compatibles TTL (T) ou

combinant ces caractristiques.

III.2.5. Sries LV, LVC, LVT et ALVC : la faible tension

Avec le dveloppement de llectronique dans les ensembles portables (mobiles, montres) utilisent des

sources dalimentation (piles ou batteries) basse tension (de lordre de 3 V). La nouvelle technologie LV

(Low Voltage) permet de travailler sous 3,3 V. Elle permet aussi de diminuer la taille des transistors sur le

substrat (technologie < 1 m) pour augmenter la densit dintgration. La srie LVT est une version

compatible TTL (technologie BiCMOS 0,8 m).

III.2.6. ABT et ALB : la technologie BiCMOS

Le prfixe B est relatif la technologie BiCMOS qui mixte lemploi de transistors bipolaires (Bi) et

CMOS. Les bipolaires apportent leur rapidit et leur capacit piloter des courants importants. Les CMOS

compltent les structures en amliorant la densit dintgration (distances entre liaisons allant de 0,8

0,3m), pour permettre une complexits accrue, et leur faible consommation.

La technologie ABT (advanced BiCMOS technology) supporte des courants jusqu 64 mA avec des

retards de propagation de lordre de 5 ns pour une consommation trs basse. La version ALB est la version

BiCMOS basse consommation.

III.3. Entres et sorties particulires

En CMOS, on retrouve les entres et sorties quivalentes la technologie TTL qui reposent sur des

solutions propres aux transistors MOS. On peut maintenant adjoindre une nouvelle fonction telle que la

porte de transmission qui est un interrupteur unidirectionnel command par un signal logique.

III.4. Performances compares des CMOS

4000B HC HCT AC ACT LVC LVT

Tension dalimentation V

CC

(V) 3 15 2 6

510%

2 6 5 23,6 2,73,6

V

OHmin

(V) 4,9 4,9 4,9 4,76

(1)(2

)

4,76

(2)

2,2

(1)(2)

2

V

IHmin

(V) 2 3,5 2 3,85

(1)

2 2 2

V

OLmax

(V) 0,1 0,1 0,1 0,44

(1)(2

)

0,44

(2)

0,55

(1)(2

)

0,55

V

ILmax

(V) 0,8 0,8 0,8 1,65

(1)

0,8 0,8 0,8

Retard de propagation (ns) 40 14 15 6 5 2,5 3,5

Consommation 100kHz (mW) 0,1 0,075 <1 <1

Frquence maximale (MHz) 12 150

(1)

V

CC

= 5,5 V ou V

CC

= 3 V en basse tension.

(2)

I

OH

= -24 mA ltat haut ou I

OL

= 24 mA ltat bas.

@ CY TecrCl02 dcembre 98 V1.1 8 / 11 Familles de circuits intgrs logiques

IV. Interfaage

Le terme interfaage regroupe les notions de liaison dun systme (par ses sorties) un autre (par ses

entres) ayant des caractristiques lectriques diffrentes. Dans le cas des TTL et des CMOS, la connexion

directe est rarement possible.

Le circuit dinterface est adapt pour recevoir les informations du montage amont et les transmettre de

manire compatible au montage aval.

IV.1. TTL pilote CMOS

La rsistance dentre des CMOS est trs leve, si bien que la tension de commande TTL ne varie

pratiquement pas. Rien ne soppose donc la liaison si V

DD

= 5 V mis part le fait que la tension TTL

V

OHmin

est trs proche de la tension V

IHmin

de la porte CMOS. Il faut donc garantir un tirage V

DD

comme le

reprsente la Figure 16.

Si les tensions sont diffrentes, il faut viter que la TTL frquente une tension suprieure 5 V en

intercalant une porte OUI collecteur ouvert dont la sortie est tire V

DD

par une rsistance (Figure 17).

&

R

&

V

DD

TTL CMOS

&

R

&

V

DD

TTL CMOS

1

TTL

V

CC

1 k

Figure 16 : TTL vers CMOS (tensions id.) Figure 17 : TTL vers CMOS (tensions diff.)

IV.2. CMOS pilote TTL

A ltat haut, le courant absorb par une entre TTL est trs faible, ce qui ne chargera que faiblement la

sortie CMOS. La tension V

OH

variera trs peu et la liaison pourra donc tre directe.

A ltat bas, le courant absorb par une porte TTL I

IL

est plus lev ( mA). En circulant dans la

rsistance de canal du transistor MOS de sortie, la somme des courants cr une chute de tension V

OL

qui

peut tre suprieure V

ILmax

ne garantissant plus un niveau logique 0 . On rsout ce problme en insrant

un circuit intermdiaire dont la sortie est collecteur ouvert. Cette solution permet aussi effectuer

ladaptation de tension.

V. Conclusion

Cet aperu des diffrentes technologies ne donne pas suffisamment dinformations sur leur volution.

Entre la recherche des performances (rapidit et consommation), la compatibilit, la prise en compte de la

disponibilit et des cots, les paramtres sont nombreux dans une perspective de conception et de

production de systmes industriels. Lvolution des composants numriques (et des autres aussi) est par

consquent un facteur essentiel observer attentivement. Pour illustrer cela, la Figure 18 indique le cycle

de vie des technologies (technologies dhier et daujourdhui) et la Figure 19 qui prsente un comparatif

des performances des diffrentes technologies (Le courant pilot et le temps de rponse).

Figure 18 : cycle de vie des technologies (document Texas Instruments).

@ CY TecrCl02 dcembre 98 V1.1 9 / 11 Familles de circuits intgrs logiques

Figure 19 : positionnement des diffrentes technologies (document Texas Instruments).

VI. Bibibliographie

Circuits numriques Thorie et applications. Ronald J. Tocci. Editions Ellipses. Collection INT.

1986. ISBN 2-7298-8650-8.

Electronique Tome 2. J.-D. Chatelain, R. Dessoulavy. Collection T3E. Dunod. 1981. ISBN 2-04-

015679-8.

Guide du technicien en lectronique. C. Cimelli et R. Bourgeron. Hachette Technique. ISBN 2-01-16-

6868-9.

Donnes Texas Instruments : data book, site ftp http://ftp.ti.com/sc/docs et document Logic

selection guide - Fourth quarter 1997 .

@ CY TecrCl02 dcembre 98 V1.1 10 / 11 Familles de circuits intgrs logiques

Annexe 1 : fonct|onnement de |a structure 0TL

Document complter

Les deux entres au niveau logique 1

S

6,8 K

2,7 K

E

1

E

2

D

1

V

cc

D2

R1

1 K

R3

D3 D4

Q1

R

2

Les diodes D

1

et D

2

sont bloques.

Un courant circule dans R

1

, D

3

, D

4

et R

2

polarisant le

transistor Q

1

qui devient passant.

Le potentiel de la masse est alors ramen la sortie S

( la chute de tension V

sat1

prs). Donc : V

s

0V.

Sortie : niveau logique bas (0).

Une entre au niveau logique 0

S

6,8 K

2,7 K

E

1

E

2

D

1

V

cc

D2

R1

1 K

R3

D3 D4

Q1

R

2

Lune au moins des deux entres est relie la masse

(NL0) et lautre V

CC

.

Un courant circule travers R

1

et (D

1

ou D

2

).

Le groupe D

3

, D

4

et R

2

est donc polaris par une

tension de seuil de diode (environ 0,7V). Les diodes

D

3

et D

4

sont bloques polarisant la base de Q

1

par une

tension nulle. Le transistor Q

1

est bloqu (interrupteur

ouvert).

Aucun courant ne circule dans le circuit collecteur-

metteur de Q

1

. La sortie est un potentiel proche de

V

CC

( la chute de tension prs dans R

3

).

Sortie : niveau logique haut (1).

Conclusion :

Remarque : si les entres sont en lair, la sortie est au niveau logique 0.

@ CY TecrCl02 dcembre 98 V1.1 11 / 11 Familles de circuits intgrs logiques

Annexe 2 : fonct|onnement de |a structure TTL

Document complter

Aprs remplacement du transistor multi-metteur par son quivalent diodes.

Les deux entres au niveau logique 1

1

R

4 K

b

D

c

D

a

D

S

3

R

4

R

130

1 K

5V

3

Q

4

Q

2

Q

2

R

1,6 K

3

D

Les diodes D

a

et D

b

sont bloques.

D

c

est passante. Un courant circule travers R

1

et D

c

.

Ce dernier sature Q

2

(interrupteur ferm).

Un courant est autoris travers R

2

, Q

2

et R

4

.

Q

4

est satur donc V

CE4

= V

CEsat4

0.

Paralllement, V

sat2

= V

D3

+ V

BE3

+ V

CB4

donc Q

3

est

bloqu et V

s

0.

Sortie : niveau logique bas (0).

Une entre au niveau logique 0

1

R

4 K

b

D

c

D

a

D

S

3

R

4

R

130

1 K

5V

3

Q

4

Q

2

Q

2

R

1,6 K

3

D

Un courant traverse R

1

et D

a

car cette dernire est

passante et D

b

bloque.

D

c

est bloque car la tension V

Da

de 0,7V se rpartie en

V

Dc

, V

BE2

et V

R4

.

Q

2

est donc bloqu (inter ferm) puisque i

b2

0.

En consquence i

b4

0. Q

4

est bloqu.

i

b3

circule dans R

2

saturant Q

3

.

Puisque D

3

est polarise en direct, le potentiel de la

sortie est V

cc

diminue des chutes de tension V

R4

,

V

CEsat4

et V

D3

.

V

S

vaut de 3,5 4 V.

Sortie : niveau logique haut (1).

Das könnte Ihnen auch gefallen

- Circuit IntegrésDokument21 SeitenCircuit IntegrésMohamedLashab100% (2)

- TTL Et CmosDokument5 SeitenTTL Et Cmosgirl Tech100% (3)

- CmosDokument32 SeitenCmosDhekra Jbeli100% (1)

- La Techologie TTL CMOSDokument7 SeitenLa Techologie TTL CMOSEcouter le françaisNoch keine Bewertungen

- Corrige TD Be 3imacs Ampli PuissanceDokument10 SeitenCorrige TD Be 3imacs Ampli PuissanceBilel Dekhili100% (1)

- Caractéristiques Des Circuits Intégrés LogiquesDokument6 SeitenCaractéristiques Des Circuits Intégrés LogiquesBALLOUK Soufiane100% (1)

- TP 1Dokument6 SeitenTP 1Samir Boss100% (1)

- Amplificateur de PuissanceDokument3 SeitenAmplificateur de PuissancePazoNoch keine Bewertungen

- Chapitre 1 Composants Electronique Puissance PDFDokument18 SeitenChapitre 1 Composants Electronique Puissance PDFMohamed ElmahdiNoch keine Bewertungen

- TD AmplificateursdepuissanceDokument3 SeitenTD Amplificateursdepuissancemutrace100% (1)

- Chapitre 03Dokument25 SeitenChapitre 03chaima michou99Noch keine Bewertungen

- Amplificateurs de Puissance Classe A Et Classe BDokument17 SeitenAmplificateurs de Puissance Classe A Et Classe BNouha Al-MajedNoch keine Bewertungen

- Etude Du Circuit NE 555Dokument10 SeitenEtude Du Circuit NE 555codety CODETYNoch keine Bewertungen

- TD 3 - Electronique Des Systèmes - Filtres ActifsDokument4 SeitenTD 3 - Electronique Des Systèmes - Filtres ActifsIhssan KHNoch keine Bewertungen

- Alimentation StabiliséeDokument1 SeiteAlimentation StabiliséeMouritaniDakhnawi100% (3)

- Cours OptocoupleursDokument1 SeiteCours Optocoupleurschicor9100% (1)

- Examen de Traitement de Signal 2018Dokument5 SeitenExamen de Traitement de Signal 2018DON DEVATTI100% (2)

- L3-Projet Fin Cycle - Licence TelecommunicationsDokument10 SeitenL3-Projet Fin Cycle - Licence TelecommunicationsÂmį Ňě100% (3)

- Chapitre I - Introduction À La MicroélectroniqueDokument7 SeitenChapitre I - Introduction À La MicroélectroniqueCy LaiNoch keine Bewertungen

- Exexrcie AOP Régime LinéaireDokument7 SeitenExexrcie AOP Régime LinéaireTc Ng100% (2)

- TD 1Dokument2 SeitenTD 1OUIAME NKHILINoch keine Bewertungen

- Corrigé Partiel VHDL FPGA M1 ELN SE 2020Dokument6 SeitenCorrigé Partiel VHDL FPGA M1 ELN SE 2020yasmine hmnNoch keine Bewertungen

- TD AOP 2 CorrigéDokument3 SeitenTD AOP 2 CorrigéYahya ElamraniNoch keine Bewertungen

- ELN Impulsions TP N°01Dokument2 SeitenELN Impulsions TP N°01sarah wiwi100% (1)

- Cours OptocoupleurDokument3 SeitenCours OptocoupleurIhab BenayacheNoch keine Bewertungen

- TRANSMISSION ANALOGIQUE Cours PDFDokument29 SeitenTRANSMISSION ANALOGIQUE Cours PDFHarun Le Principal Gomina100% (1)

- Chapitre 3 Amplificateur Différentiel PDFDokument29 SeitenChapitre 3 Amplificateur Différentiel PDFmed50% (2)

- Introduction Aux MC STM32 PDFDokument9 SeitenIntroduction Aux MC STM32 PDFZied HouanebNoch keine Bewertungen

- TD1: Les Circuits Programmables: Exercice 1Dokument2 SeitenTD1: Les Circuits Programmables: Exercice 1Dhouha Benzina100% (1)

- Pont de Wien.: Exercice N°1: Etude de L'oscillateur Sinusoïdal ÀDokument1 SeitePont de Wien.: Exercice N°1: Etude de L'oscillateur Sinusoïdal ÀMãrÿ Ōûmå100% (1)

- Alimentation ReguleDokument18 SeitenAlimentation ReguleKhaled Ouni100% (2)

- TP Electronique Analogique TS 2018-2019Dokument37 SeitenTP Electronique Analogique TS 2018-2019Degrize Meda100% (2)

- Master 1 MICROELECTRONIQUE - 2Dokument44 SeitenMaster 1 MICROELECTRONIQUE - 2Djelloul Ben Mohamed Hdi100% (1)

- Transmission en Bande de BaseDokument13 SeitenTransmission en Bande de BaseOthman Nchifa100% (2)

- 4 Du Transistor À La Logique CMOS PDFDokument17 Seiten4 Du Transistor À La Logique CMOS PDFJames Smith100% (1)

- Exercices Amplificateur Emetteur Commun Avec PDFDokument7 SeitenExercices Amplificateur Emetteur Commun Avec PDFMaison MeubleNoch keine Bewertungen

- Introduction Isis ProteusDokument36 SeitenIntroduction Isis Proteuskaram karam100% (1)

- l2 en TDDokument36 Seitenl2 en TDSissi Dadi100% (2)

- tp1 11 Filtre Actif Passe-BandeDokument1 Seitetp1 11 Filtre Actif Passe-BandeMohamed Aly Sow100% (2)

- Travaux Dirigés FPGA & VHDLDokument28 SeitenTravaux Dirigés FPGA & VHDLR.s. Félix75% (4)

- Développement Dune Voiture Télécommandée À Base D' Arduino Firas DOUKALIDokument43 SeitenDéveloppement Dune Voiture Télécommandée À Base D' Arduino Firas DOUKALIBassem Jouini100% (1)

- TP ElectroniqueDokument14 SeitenTP ElectroniqueSoufianeBattal100% (4)

- Sujets Dexamen Telecom PDFDokument13 SeitenSujets Dexamen Telecom PDFOffiana HORO100% (1)

- Alimentation StabiliséeDokument4 SeitenAlimentation StabiliséeMohammed Chnafa50% (2)

- Protection À Maximum de CourantDokument3 SeitenProtection À Maximum de CourantMED7733% (3)

- TDu CDokument49 SeitenTDu CnawzatNoch keine Bewertungen

- TP 3 Transmission Reseaux Modulations Numeriques OOK FSK PSK 2020Dokument8 SeitenTP 3 Transmission Reseaux Modulations Numeriques OOK FSK PSK 2020Mohamed Amine Tahiri0% (1)

- Cours E Transistor A Effet de ChampDokument6 SeitenCours E Transistor A Effet de Champmaropov123Noch keine Bewertungen

- QCM Modulation Analogique LicenseDokument15 SeitenQCM Modulation Analogique Licenseboris kenfackNoch keine Bewertungen

- EPREUVE DE Circuit Analogique&Numer - Séq4-2012Dokument5 SeitenEPREUVE DE Circuit Analogique&Numer - Séq4-2012ensetasse100% (1)

- Cours N°9 - (Monostables)Dokument6 SeitenCours N°9 - (Monostables)gg91100% (2)

- Logique ExercicesDokument4 SeitenLogique ExercicesMohamed JemmoudiNoch keine Bewertungen

- Les Circuits Logiques Programmables FPGADokument29 SeitenLes Circuits Logiques Programmables FPGAOUSSAMA ELHJOUJI0% (1)

- COUR2electronique DigitaleDokument25 SeitenCOUR2electronique Digitalemouadh.haouam.10Noch keine Bewertungen

- DocumentDokument15 SeitenDocumentSOUKAINA AKHRAISNoch keine Bewertungen

- AaaaDokument6 SeitenAaaaKhaled BenlekhalNoch keine Bewertungen

- Transistor-Transistor Logiq TTLDokument5 SeitenTransistor-Transistor Logiq TTLWaldja LaréNoch keine Bewertungen

- 1-Définition:: Pour en Savoir Plus Sur Les Portes Logiques Voici Un Tuto de RobocopDokument5 Seiten1-Définition:: Pour en Savoir Plus Sur Les Portes Logiques Voici Un Tuto de RobocopEcouter le françaisNoch keine Bewertungen

- Chapitre 3 Logiques CombinatoiresDokument20 SeitenChapitre 3 Logiques Combinatoireslilian camilleNoch keine Bewertungen

- Ingénieur Canandien PDFDokument778 SeitenIngénieur Canandien PDFBALLOUK SoufianeNoch keine Bewertungen

- Flexo Solutions FRDokument4 SeitenFlexo Solutions FRBALLOUK Soufiane0% (1)

- Guide Pratique Professionel 2017Dokument20 SeitenGuide Pratique Professionel 2017BALLOUK SoufianeNoch keine Bewertungen

- Indis Technique GraphikDokument98 SeitenIndis Technique GraphikBALLOUK SoufianeNoch keine Bewertungen

- CH 18 Mise en OeuvreDokument5 SeitenCH 18 Mise en OeuvreBALLOUK SoufianeNoch keine Bewertungen

- NF C 18-510Dokument253 SeitenNF C 18-510BALLOUK Soufiane100% (2)

- Pratique Du LeanDokument208 SeitenPratique Du LeanAnovar_ebooks100% (3)

- UTE C15 712 1 Photovoltaique ReseauDokument65 SeitenUTE C15 712 1 Photovoltaique ReseauBALLOUK Soufiane100% (5)

- Chap 3Dokument9 SeitenChap 3Melody NixonNoch keine Bewertungen

- Calcul Section Cable Eclairage - PublicDokument4 SeitenCalcul Section Cable Eclairage - Publiccherif yahyaoui100% (2)

- Clim8 ClimatisationDcent PDFDokument8 SeitenClim8 ClimatisationDcent PDFHassan OuikhalfenNoch keine Bewertungen

- Analyse de La Réglementation Marocaine Régissant Les Installations ÉlectriquesDokument3 SeitenAnalyse de La Réglementation Marocaine Régissant Les Installations ÉlectriquesBALLOUK SoufianeNoch keine Bewertungen

- 6Dokument46 Seiten6JeanDD03100% (3)

- Ute C 15 900Dokument71 SeitenUte C 15 900Patran ValentinNoch keine Bewertungen

- UTE C17-205U Guide Pratique Dim Conducteur Eckairage PublicDokument24 SeitenUTE C17-205U Guide Pratique Dim Conducteur Eckairage PublicBALLOUK Soufiane83% (6)

- Securite Groupe ElectrogeneDokument6 SeitenSecurite Groupe ElectrogeneABELWALIDNoch keine Bewertungen

- Norme UTE C 15 712Dokument32 SeitenNorme UTE C 15 712ABELWALID100% (2)

- NF C11 201 Reseaux de Distribution Publique D EnergieDokument134 SeitenNF C11 201 Reseaux de Distribution Publique D Energiebadrezzamane93% (15)

- Protection Des Installations ÉlectriquesDokument65 SeitenProtection Des Installations ÉlectriquesBESSEMYNoch keine Bewertungen

- CV BALLOUK SoufianeDokument1 SeiteCV BALLOUK SoufianeBALLOUK SoufianeNoch keine Bewertungen

- Catalogue Normes Marociane Electricité Édition Mai 2015Dokument54 SeitenCatalogue Normes Marociane Electricité Édition Mai 2015BALLOUK Soufiane100% (1)

- Norme de Passage Des Reseaux SouterrainsDokument12 SeitenNorme de Passage Des Reseaux SouterrainsBALLOUK SoufianeNoch keine Bewertungen

- Management Des Risques D'entreprise - Le Modèle Triple Impact™Dokument8 SeitenManagement Des Risques D'entreprise - Le Modèle Triple Impact™Mohamed ZoubairNoch keine Bewertungen

- Variateurs de Vitesse - de La Régulation Cascade À La Commande Vectorielle PSIMDokument55 SeitenVariateurs de Vitesse - de La Régulation Cascade À La Commande Vectorielle PSIMBALLOUK Soufiane100% (4)

- Echos N19 PDFDokument20 SeitenEchos N19 PDFdonsallusNoch keine Bewertungen

- Psim OnduleurDokument149 SeitenPsim OnduleurHuong Thao Le LuongNoch keine Bewertungen

- Toute La Fonction QSSE (Qualité Sécurité Environnement)Dokument526 SeitenToute La Fonction QSSE (Qualité Sécurité Environnement)BALLOUK Soufiane91% (11)

- Dimensionnement SolaireDokument73 SeitenDimensionnement SolaireN.NASRI Matlablog100% (25)

- Cours Des Moteurs AsynchronesDokument40 SeitenCours Des Moteurs AsynchronesBALLOUK Soufiane100% (5)

- Echos N18Dokument16 SeitenEchos N18BALLOUK SoufianeNoch keine Bewertungen

- Traité de Lélectronique Analogique Et NumériqueDokument39 SeitenTraité de Lélectronique Analogique Et NumériquezouhirNoch keine Bewertungen

- 03 PolymorphismeDokument142 Seiten03 PolymorphismeameniNoch keine Bewertungen

- Modicon M340 Sous Unity Pro: Modules D'entrée/sortie Numérique Manuel UtilisateurDokument306 SeitenModicon M340 Sous Unity Pro: Modules D'entrée/sortie Numérique Manuel UtilisateursimbamikeNoch keine Bewertungen

- Dta 5 14 2411 Fesco Effigreen AcierDokument18 SeitenDta 5 14 2411 Fesco Effigreen Acierjean thierry ndong obameNoch keine Bewertungen

- Delphi - Les MessagesDokument4 SeitenDelphi - Les MessagesHanen ChaibNoch keine Bewertungen

- Fascicule 2nd Semestre Droit AdministratifDokument116 SeitenFascicule 2nd Semestre Droit AdministratifMarie-Prune RobertNoch keine Bewertungen

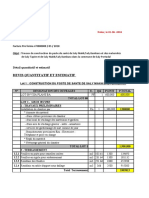

- Bordereau de Prix Centre de SantéDokument23 SeitenBordereau de Prix Centre de SantébgtNoch keine Bewertungen

- 6 7051 Dd4c241e PDFDokument26 Seiten6 7051 Dd4c241e PDFSAEC LIBERTENoch keine Bewertungen

- Projet D Investissement - CoursDokument13 SeitenProjet D Investissement - CoursMil De MilNoch keine Bewertungen

- Projet de Développement Canada - MarocDokument22 SeitenProjet de Développement Canada - MarocImane BoustiqueNoch keine Bewertungen

- Mémoire CODIFAD DRVSDokument60 SeitenMémoire CODIFAD DRVSMeurant FrançoiseNoch keine Bewertungen

- Cours L1 LOBADokument36 SeitenCours L1 LOBADohNoch keine Bewertungen

- Règles de Sécurité, Véhicules ÉlectriquesDokument11 SeitenRègles de Sécurité, Véhicules Électriquesmebarki aberraouf100% (1)

- Atelier N°5: Cours de ProfessionnalisationDokument11 SeitenAtelier N°5: Cours de ProfessionnalisationAlexis UsseglioNoch keine Bewertungen

- Anticor - Lanceur D'alerte Dans La Fonction PubliqueDokument5 SeitenAnticor - Lanceur D'alerte Dans La Fonction PubliqueKarim GhanmiNoch keine Bewertungen

- QCM Rappel Js 1 CorrectionDokument3 SeitenQCM Rappel Js 1 CorrectionhoudabizzzNoch keine Bewertungen

- Cahier 1AS - 2022-OfficielDokument112 SeitenCahier 1AS - 2022-Officielبسام أبوالسعود100% (1)

- ES - 1.règlement Des Admissions PDFDokument5 SeitenES - 1.règlement Des Admissions PDFQeti MaisuradzeNoch keine Bewertungen

- Exemples Gammes ReduDokument25 SeitenExemples Gammes Redumehdi100% (1)

- This Website Uses Cookies To Ensure You Get The Best Experience On Our WebsiteDokument83 SeitenThis Website Uses Cookies To Ensure You Get The Best Experience On Our WebsiteHerve ArseneNoch keine Bewertungen

- Formations IEDokument8 SeitenFormations IEsimon3dNoch keine Bewertungen

- Management de ProjetDokument7 SeitenManagement de ProjetChaimae merabetNoch keine Bewertungen

- Droit CommercialDokument24 SeitenDroit Commercialfrd100% (1)

- RefroidissementDokument17 SeitenRefroidissementBa Hamzik HPNoch keine Bewertungen

- Chapitre 5Dokument5 SeitenChapitre 5Nicolas GarciaNoch keine Bewertungen

- Finma Rs 2013 08 01012021 - DEDokument11 SeitenFinma Rs 2013 08 01012021 - DEsidNoch keine Bewertungen

- Série de TD #4 - Filtres NumériquesDokument2 SeitenSérie de TD #4 - Filtres Numériquesnour eddine aarousNoch keine Bewertungen

- Irrigation Localisée 2023Dokument136 SeitenIrrigation Localisée 2023Khouloud BenjaddaNoch keine Bewertungen

- Concilier Production Au Plus Juste Et Agilité Dans Les Chaines Logistiques Étendues - Un Double Éclairage Opérationel Et StratégiqueDokument19 SeitenConcilier Production Au Plus Juste Et Agilité Dans Les Chaines Logistiques Étendues - Un Double Éclairage Opérationel Et Stratégiqueyassin900Noch keine Bewertungen

- Recherches Récentes en FinanceDokument28 SeitenRecherches Récentes en FinanceBayoudh AmiraNoch keine Bewertungen