Beruflich Dokumente

Kultur Dokumente

Elonics E4000 Low Power CMOS Multi Band Tuner Datasheet

Hochgeladen von

benryanauCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Elonics E4000 Low Power CMOS Multi Band Tuner Datasheet

Hochgeladen von

benryanauCopyright:

Verfügbare Formate

MULTISTANDARDCMOSTERRESTRIALRFTUNER

E4000

KEYFEATURES

DESCRIPTION

The E4000 is a highly integrated multiband RF

tuner IC implemented in CMOS, ideal for digital

TV and radio broadcast receiver solutions. The

digitally programmable multiband tuner

architecture allows the user to reconfigure the

RFfrontendfordifferentbroadcaststandards.

SupportforMultipleBroadcastStandards

o NorDig2.0

o MBRAI2.0

ScalablePowerConsumption

o 118mWTypicalOperation

o 15mWinDVBHMode

o <60uWPowerDown

1.5VAnalogueandDigitalSupplyOperation

VariableGainLowNoiseAmplifier(LNA)

o AutonomousAutomaticGainControl

withRSSI

o <4dBReceiverNoiseFigure

o 64MHzto1700MHzInputFrequency

Range

FlexibleIFAmplifierandChannelFilter

o ProgrammableChannelBandwidth

o DigitalIFGainControl

FlexibleClockingModes

o MasterorSlaveModeDevice

o 16MHz32MHzInputFrequency

Range

o ProgrammableOutputClock

FrequencyRange

o CMOSorcustomlowpowerLVDS

OutputLevels

FractionalNSynthesiserwithFullyIntegrated

VCOandLoopFilter

I2CCompatibleControlBus

o 3.3VTolerantInterface

o 4Addresses

32PinQFNPackage

o 5x5x0.9mmBodySize

o PbFree

o RoHSCompliant

APPLICATIONS

DVBT(174240MHz,470858MHz)

CMMBTerrestrial(470858MHz)

DTMB(174240MHz,14521492MHz)

ISDBT(470862MHz)

DVBH(470858MHz,16721678MHz)

TDMB(174240MHz,14521492MHz)

DAB/DAB+(174240MHz,14521492MHz)

GPSL1band(1575MHz)(withadditional

LNA)

FMradio(64108MHz)

It is designed to interface directly to a digital

demodulator,andcontainsafullyintegratedLNA,

programmable RF filter, and RF mixers providing

superiorrealworldperformance.

At the heart of the E4000 is Elonics innovative

DigitalTune architecture, which allows the user

to adjust the performance of the tuner for

optimumlinearityornoisefigureaccordingtothe

signal conditions. It enables manufacturers to

significantly improve reception quality, whilst

supportingmultiplebroadcaststandards.

TVEnabledCellPhones

PortableMultimediaPlayers

The E4000 contains a single input LNA with RF

filter, whose centre frequency can be

programmedoverthecompletefrequencyrange

from 64MHz to 1700MHz. This greatly simplifies

antenna management especially for applications

thatrequiresupportformorethanonebroadcast

standard.

PCandPCPeripherals

IPTV

SetTopBoxes

NIMandhalfNIMmodules

E4000Datasheet4v0Copyright2010ElonicsLtd

DocumentNumber:SE4000DS001

www.elonics.com

E4000

TABLEOFCONTENTS

KEYFEATURES1

APPLICATIONS1

DESCRIPTION1

TABLEOFCONTENTS2

ORDERINGINFORMATION5

PACKAGEMARKINGDIAGRAM5

PINFUNCTIONS 7

ABSOLUTEMAXIMUMRATINGS 8

MOISTURESENSITIVITY 8

RECOMMENDEDOPERATINGCONDITIONS 8

DCELECTRICALCHARACTERISTICS9

ACELECTRICALCHARACTERISTICS 11

POWERCONSUMPTION 13

TIMINGCHARACTERISTICS 14

TYPICALCHARACTERISTICS 15

REGISTERMAP 17

DEVICEDESCRIPTION 23

1.1

TwoWire,I2CInterface 23

1.2

SerialInterfaceProtocol 23

1.3

FrequencySynthesiser 25

1.4

PLLFeedbackdivider(/Z) 26

1.5

X,Sigmadeltasetup 26

1.6

RVCOoutputdivider 26

1.7

Threephasemixing 26

1.8

ExampleFrequencysynthesizerconfiguration 27

1.9

VCOCalibration 27

1.10 E4000SignalPath 28

1.11 FrequencyBandSelection 29

1.12 GainControl 30

1.13 LNAGainControl 30

1.13.1

LNASerialInterfaceGainContro 31

1.13.2

LNAdigitalPWMgaincontrol32

1.13.3

LNAAutonomousGainControl33

1.13.4

LNASupervisorGainControl33

1.14 ReceivedSignalStrengthIndicator(RSSI)34

1.15 MixerGainControl 34

1 15.1

MixerGainSerialInterfaceControl34

1.15.2

MixerGainAutonomousControl35

1.16 LNAGainenhancement35

1.17 IFGainControl35

1.17.1

IFgainLinearity/SensitivityMode35

1.17.2

IFGainSerialInterfaceControl36

1.17.3

IFGainDigitalPWMControl40

1.17.4

IFGainDigitalControl41

1.18 OutputCommonModeVoltage42

1.19 RFFilter43

1.20 IFFilter44

1.21 MixerFilter44

1.22 IFRCFilter45

1.23 IFChannelFilter46

1.24 CombinedFilterResponse48

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page2

E4000

1.25 DCOffsetCorrection48

1.26 DCOffsetControl49

1.27 DynamicDCOffsetCorrection49

1.27.1

LookUptable49

1.27.2

TimeVaryingDCOffsetCompensation50

1.28 ClockOutput51

1.29 ClockInput53

1.30 Reset53

1.31 PowerSaveModes54

1.31.1

PowerDownMode 54

1.31.2

StandbyMode

54

1.32 Initialisation 55

APPLICATIONINFORMATION 56

PACKAGEDESCRIPTION 57

REVISIONHISTORY 58

LEGALNOTICES 59

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page3

E4000

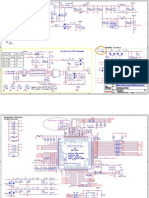

BLOCKDIAGRAM

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page4

E4000

ORDERINGINFORMATION

OrderCode

Ambient

TemperatureRange

Package

Moisture

SensitivityLevel

PeakSoldering

Temperature

E4000EQG

40to+85C

MSL1

260C

E4000EQGD

40to+85C

MSL1

260C

E4000EQGR

40to+85C

QFN325x5mm

body(Pbfree)

QFN325x5mm

body(Pbfree,

drypackedand

vacuumsealed)

QFN325x5mm

body(Pbfree,

tapeandreel)

MSL1

260C

Notes

1) Tubequantity=95

2) Reelquantity=3500

PACKAGEMARKINGDIAGRAM

E4000EQG

YYWWZMMC

Line1

Line2

Line3

ElonicsLogoFixed

E4000Fixed(DeviceName)

EQGFixed

YYWWVariable(DateCode)

Z Variable (Trace code e.g. A, B, C X, Y, Z lots molded in the

sameworkweek

MMCVariable(Manufacturingcode)

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page5

E4000

AGND

TUN_DVDD

TUN_DGND0

TUN_DGND1

CLOCKIN

XTAL

PLL_GND

AVDD

Top view

PLL_VDD

PININFORMATION

CKOUTP

VBG

CKOUTN

REXT

GAIN1

Elonics

E4000

RFSHIELD

RFIN

GAIN0

IVOUTP

IVOUTN

LNAGND

LNAGND2

QVOUTP

LNAVDD

QVOUTN

SCLK

SDAT

PDNB

STBYB

A1

A0

IFGND

IFVDD

QFN32

5x5mm

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page6

E4000

PINFUNCTIONS

Pin

1

Name

AGND

Type

Ground

VBG

AnalogueOutput

REXT

AnalogueOutput

4

5

6

7

8

9

10

11

12

RFSHIELD

RFIN

LNAGND

LNAGND2

LNAVDD

IFVDD

IFGND

A0

A1

Ground

AnalogueInput

Ground

Ground

Supply

Supply

Ground

DigitalInput

DigitalInput

13

STBYB

DigitalInput

14

PDNB

DigitalInput

15

16

17

18

19

20

SDAT

SCLK

QVOUTN

QVOUTP

IVOUTN

IVOUTP

DigitalI/O

DigitalInput

AnalogueOutput

AnalogueOutput

AnalogueOutput

AnalogueOutput

21

GAIN0

Digital/PWM

22

GAIN1

Digital/PWM

23

CKOUTN

24

CKOUTP

25

26

27

TUN_DVDD

TUN_DGND0

TUN_DGND1

LVDSorCMOS

output

LVDSorCMOS

output

Supply

Ground

Ground

28

CLOCKIN

Oscillator

29

30

31

32

XTAL

PLL_GND

PLL_VDD

AVDD

Oscillator

Ground

Supply

Supply

Description

0V.ConnecttoTuneranalogueground

Band gap voltage. A 10nF decoupling capacitor should be

placed between this pin and 0V. The capacitor should be

placedclosetothispin.

Reference current generation. A 10k, 1%, resistor should be

placedbetweenthispinand0V.

RFShield,connecttoLNAGND

RFinput.50Rimpedance.

0V

0V,connecttoLNAGND

1.5V

1.5V

0V

TunerI2Cdeviceaddresscontrol(bit0).(3 3Vtolerant).

TunerI2Cdeviceaddresscontrol(bit1).(3.3Vtolerant).

Normal operation = 1.5V (3.3V tolerant). Standby = 0V. If

unused,connectAVDD

Normaloperation=1.5V 3.3Vtolerant).Powerdown=0V.If

unused,connectAVDD

I2Cdata.Pullupto1 5V(3.3Vtolerant).Pullupresistor>4.5k

I2Cclockinput.(3V3tolerant).

QChanne Outputve

QChanne Output+ve

IChannelOutputve

IChannelOutput+ve

Gain control input. Either digital IF or IF PWM input (3V3

tolerant).

Gain control input. Either digital IF or RF PWM input (3V3

tolerant).

ClockOutputve.Ifunused,shouldbeleftasnoconnect.

ClockOutput+ve.Ifunused,shouldbeleftasnoconnect.

1.5V

0V

0V

ConnecttocrystalORClockinputfromexternalsource(1.5V

logiclevels).

Connecttocrystal.Ifunused,shouldbeleftasnoconnect.

0V.DonotconnectdirectlytoLNAGND

1.5V

1.5V

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page7

E4000

ABSOLUTEMAXIMUMRATINGS

Condition

StorageTemperature

SupplyVoltage(LNAVDD,PLL_VDD,IFVDD,

TUN_DVDD,AVDD)

Min

65

GND0.3

Max

+150

GND+1.65

Units

C

V

AnalogueInputs/Outputs

DigitalInputs

I2CInterfaceInputs

RFInputPower

LeadTemperature(10ssoldering)

GND0.3

GND0.3

GND0.3

AVDD+0.3

+3.6

+3.6

+10

+260

V

V

V

dBm

C

Stressesbeyondthoselistedmaycausepermanentdamagetothedeviceormayimpairdevicereliability.

Thedeviceshouldbeoperatedwithinrecommendedoperatingconditions.

ThisisanESDSensitiveDevicemanufacturedinaCMOSprocess.Itisthereforesusceptibletodamagefrom

excessive voltage such as is caused by static discharge. Proper ESD precautions must be taken during

handling,storageandoperationofthisdevice

MOISTURESENSITIVITY

Devices are qualified to IPC/JEDEC JSTD020B, determining moisture sensitivity and acceptable storage

conditions. The rating of this product is as indicated within the Ordering Information section of this

datasheet.

RECOMMENDEDOPERATINGCONDITIONS

Condition

OperatingTemperature

SupplyVoltage(TUN_DVDD,LNAVDD,PLL_VDD,

IFVDD,AVDD)

Min

40

+1.4

Typ

+25

+1.5

Max

+85

+1.6

Units

C

V

GroundVoltage

AnalogueInputs

DigitalInputs(ExceptCLOCKIN,pin28)

CLOCKIN

0

0

0.7

+1.6

+3.6

+1.6

V

V

V

V

DeviceFunctionandElectricalCharacteristicscanonlybemaintainedifoperatingconditionsareadhered

to.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page8

E4000

DCELECTRICALCHARACTERISTICS

Operating parameters specified with all supplies = 1.5V, GND = 0V, Tambient=25 degrees unless otherwise

stated.

Parameter

Description

Min

Typ

Max

Units

SupplyVoltages

AVDD,

Supplyvoltage

1.4

1.5

1.6

V

PLL_VDD,

LNAVDD,

IFVDD,

TUN_DVDD

IDDcont

Supplycurrent(Continuousoperating

79

mA

mode)

(Variesdependingontunerconfiguration)

IDDStby

Supplycurrent(standbymode)

mA

IDDPD

Supplycurrent(powerdown)

60

uA

ClockOutputs(CMOS)

VohCMOS

Outputsignalhigh

0.8x

V

TUN_DV

DD

VolCMOS

Outputsignallow

0.25x

V

TUN_DV

DD

ICMOS

Outputcurrent

mA

Jitter

ClockoutputRMSjitter

ps

ClockOutputs(Custom,lowpowerLVDS)

VohLVDS

Outputsignalhigh

TUN_DV

V

DD

VolLVDS

Outputsignallow

TUN_DV

V

DD0.4

ILVDS

Outputcurrent(Note1)

4

mA

RLVDS

Differentialoutputimpedance(LVDS)

500

Ohm

Jitter

ClockoutputRMSjitter

ps

ZSOURCE

Sourceimpedance(CMOS)(Note2)

1000

Ohm

DigitalInputs(PDNB.ADDR,GAIN,CLOCKIN)

VilCMOS

Voltageinputlow

0.3x

V

TUN_DV

DD

VihCMOS

Voltageinputhigh

0.7x

V

TUN_DV

DD

I2CInterface

VilI2C

Inputlogiclowlevel

0.3x

V

TUN_DV

DD

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page9

E4000

VihI2C

VolI2C

NOTES

1.

2.

3.

Inputlogichighlevel

Outputlogiclevellow(Note3)

0.4

LVDSoutputcurrentisprogrammable.

Ifloadimpedanceisdifferentmayrequireaterminationresistor.

PullupresistoronI2Cdatalineshouldbe>4k7Ohms.

E4000Datasheet4v0

SE4000DS001

August2010

0.7x

TUN_DV

DD

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page10

E4000

ACELECTRICALCHARACTERISTICS

RF

FIN

NFFM

NFVHF

NFUHF

NFLBAND

IIP3

S1150R

S1175R

InputFrequencyRange

Noisefigure(FM)

Noisefigure(VHF)

NoiseFigure(UHF)

Noisefigure(LBand)

InputreferredIP3point(minimumgain)

InputReturnloss(50Rsystem)

Inputreturnloss(75Rsystem)

64

4.5

4.5

3.8

4.3

5

15

20

1700

MHz

dB

dB

dB

dB

dBm

dB

dB

350

1700

MHz

200

10

MHz

dB

2

5

4

4

1

1dB

99

30

12

57

dB

dB

dB

dB

dB

dB

16

100

26

10

32

MHz

pF

W

ProgrammableRFtrackingFilter(Note4)

FC

RFFilterCentreFrequency(programmable

between)

F3BW

RFFilter3dBBandwidth

FREJ

RFoutofbandrejection(>150%FC)

TypicalGain(Note5)

Gt

TotalGainrange

G1

LNAGainRange

G2

MixerGainRange

G3

IFGainRange

G3

StepSize

G f

Gainflatness(IFfrequencyband)(Note6)

Referenceoscillator

Fosc

Frequency

Cosc

Load(presentedbyE4000)

Posc

Crystalpowercapability

NOTES

4.

5.

6.

RFfilterstrackwithLNA onfiguration.Whenoperatingatf<240MHzfilterislowpasstype.Forf>350MHzfilterisbandpasstype

Gainisprogrammab e.Valuesquoteddetailthetypicalrangetowhichgainscanbeset.

Filtersminimised.DC4MHz

FrequencySynthesiser(Note7)

FVCO

VCOfrequencyrange

/R

R(VCOoutput)dividerratio

FLO

LocalOscillatorFrequencyRange

FLO

LocalOscillatorFrequencyStepSize(Note8)

Integratedphasenoise(1kHz8MHz)

/Z

-29

3900

48

1700

20000

PhaseNoise@10kHz

-80

PhaseNoise@2MHz

-125

Z(phasedetector)divideratio

2600

2

64

10

64

255

MHz

MHz

Hz

dBc

dBc

/Hz

dBc

/Hz

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page11

E4000

IFChannelFiltering

Fc

ChannelFiltercornerfrequency(Note9)

A20M

Attenuationat10MHz(fc=4MHz,)

2.15

70

5.50

MHz

dB

mV

V

Ohm

Ohm

pF

dB

degree

IQBasebandOutputs

Vpp

DifferentialPeaktoPeakOutputVoltage

Vcm

CommonModeVoltage(Note10)

Rout

SingleEndedOutputImpedance

Load

Outputload

Outputloadcapacitance

AIMB

DifferentialItoQAmplitudeImbalance

PIMB

DifferentialItoQPhaseImbalance

1000

0.58

250

15k

10

0.2

5

NOTES

7.Section1.3documentsFrequencySynthesizerconfigurationforvariousstates.

8.LOfrequencystepsizevariesdependingon/Rratioset.

9.Programmablewith0.2MHzstepsize.

10.Commonmodeoutputvoltageisprogrammable

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page12

E4000

POWERCONSUMPTION

Thepowerconsumptionofthisdeviceisdependentontheoperatingmode.

Parameter

Min

Typ

Max

Units

PON(1)

108

mW

PON(2)

118

mW

PSTBY(3)

mW

PGATED(4)

15

mW

PGATED(5)

17

mW

PPWDN(6)

60

uW

NOTES

1.

2.

3.

4.

5.

6.

Continuousoperatingmode.CKOUToff.Normalreceptionenvironment

Continuousoperatingmode.CKOUTon.Severereceptionenvironment(Inthepresenceofastrongadjacentchannelinterferer)

Standbymode

Gated.AssumedeviceisinOperatingmodefor1cycleandStandbyfor9cycles.CKOUToff Normalreceptionenvironment

Gated.AssumedeviceisinOperatingmodefor1cycleandStandbyfor9cycles.CKOUTon. everereceptionenvironment

Powerdownmode

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page13

E4000

TIMINGCHARACTERISTICS

InitialisationTiming

Tinit

Signalpathinitialisation(frompoweron)

Tinit_stby

Signalpathinitialisation(fromstandby)

Tinit_osc

Oscillatorturnontime

2

1

100

20

2

ms

ms

s

tSU:STA

tHD:STA

tSU:DAT

tHD:DAT

tSU:STO

tBUF

SDAT

SCLK

tLOW

tHIGH

Figure1:I2CinterfaceTimingRequirements

Parameter

SetuptimeforStartcondition

HoldtimeforStartcondition

Clocklowtime

Clockhightime

Bus free time between Stop

andStart

I2Cclockfrequency

Symbol

tSU:S A

tHD:STA

tLOW

tHIGH

tSU:DAT

tHD DAT

tSU:STO

tBUF

Min

600

600

1300

600

100

600

500

Max

900

Units

ns

ns

ns

ns

ns

ns

ns

ns

CLKI2C

MHz

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page14

E4000

TYPICALCHARACTERISTICS

84

82

80

78

76

74 Baseband channel filter can be

72 disabled at low input power,

reducingsupplycurrent

70

-100

-80

-60

-40

Supply current (mA)

Supply current (mA)

Operatingparametersarespecifiedforallsupplies=1.5V,GND=0V,Tambient=25degreesunlessotherwise

stated.

-20

80

79

78

77

76

75

74

73

72

71

0

RF input pow er (dBm )

500

1000

1500

2000

Fre que ncy (M Hz)

Supplycurren vs.ope atingfrequency

10

77

76

75

74

73

72

Gain (dB)

Su p p ly cu rren t (m A )

Supplycurrentvs.RFinputpowertotuner

(maintaining1Vppdifferentialoutputamplitude)

1.4

1.45

1.5

1.55

1.6

5

0

0

400

800

1200

1600

-5

-10

Frequency (MHz)

Supply voltage (V)

Supplycurrentvs.operatingvoltage

E4000gainvs.frequency(normalised)

IIP3 (dBm)

20

0

-100

-80

-60

-20

20 0

40

60

-80

RF input pow er (dBm)

IIP3vs.RFinputpower(E4000gainssettomaintain

1Vppdiffoutputswing)

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page15

E4000

0

500

1000

1500

2000

500

1000

1500

2000

-5

-20

S11 (dB)

S11 (dB)

-10

-30

-40

-50

- 10

LNA gain

=25dB

- 15

- 20

LNA gain

=0dB

- 25

-60

- 30

Freque ncy (MHz)

Frequency (MHz)

0.00

0

10

15

20

-20.00

Attenuation (dB)

Attenuation (dB)

Return loss vs. frequency vs. LNA gain setting (75R Returnlossvs.frequencyvs.LNAgainsetting(50R

environment).

environment)

-40.00

-60.00

-80.00

Frequency (MHz)

0

-1400

-2

-3

-4

-5

-6

-7

-8

-9

-10

500

600

700

800

900

Frequency (MHz)

Programmable,basebandchannelfilterfrequency

response,(4.1MHzfiltercornerfrequencysettingis

shown)

Programmable, RF filter frequency response,

(666MHzsettingisshown).

Phase noise (dBc/Hz)

-60

-701000

10000

100000

1000000

-80

-90

-100

-110

-120

-130

Frequency offset from carrier (Hz)

Localoscillatorphasenoisevs.frequencyoffsetfrom

carrier

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page16

E4000

REGISTERMAP

Colour

Green

Yellow

Purple

Blue

Explanation

Reserved register

User control register R/W

User control register R

User should not over-write default values

Bitnumber

0x00h

Master2

Address

7(MSB)

Reserved

Default=00000

0x01h

Master2

0x02h

Master3

0x03h

Master4

0x04h

Master5

0x05h

Inputclock

0(LSB)

PORdetect

=1aftera

reset.

Write1to

clear

register

Standb

1=normal

operation

0=standby

mode

RESET

1=reset

0=normal

operation

Reserved

Default=00000000

Elonicsidentifier

Default=01000000

Elonicsidentifier

Default=00000000

Elonicsidentifier

Default=00000011

Reserved

Default=0000000

0x06h

Reference

clock

Reserved

Default=000

0x07h

Synth1

Reserved

Default=000

0x08h

Synth2

0x09h

Synth3

0x0ah

Synth

0x0bh

Synth5

0x0dh

Synth7

Reserved

Default=00000

Outputclockfrequency

00=Cry talfreq1

(default)

01=Crystalfreq2

10=Crystalfreq4

Inputclockfreqrange

00=1632MHz(default)

Alwayswrite00

Reserved

Default=00000000

Feedbackdivider/Z

Seesection1.4

SigmadeltaX(LSB)

Seesection1.5

SigmadeltaX(MSB)

Seesection1.5

Enable3

phase

mixing

0=disable

(default)

See1.7

E4000Clockselect

00=Crystalclocksource

(default)

01=DividedPLL

Donotwritetothisregister

Clockoutput

CMOSconfiguration

logic

Or

0=LVDS

LVDSdrivestrength

1=CMOS

(default)

See1.28

Frequencyband

PLLlocked

00=VHFII

1=locked

01=VHFIII

10=UHF(default)

11=Lband

VCOoutputdivider/R

Default=001

Seesection1.6

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page17

E4000

Bitnumber

0x0eh

Synth8

0x0fh

Synth9

0x10h

filt1

0x11h

filt2

0x12h

filt3

0x14h

Gain1

Address

6

7

Reserved

Default=00

VCOcal

warningflag

VCOrange

lowflag.

Usershould

updateloop

whena

value1is

read(bit2)

VCOrange

highflag

Usershould

updateloop

whena

value1is

read

(bit2)

Reserved

Default=0000

Reserved

Default=0000

Mixerfilter

Default=0000

Seesection1.21

Reserved

Filter

Default=00

disable

1=disable

0=enable

(default)

See0

Reserved

Default=0000

0x15h

Gain2

0x16h

Gain3

0x17h

Gain4

VCOcal

VCOcalmode

update

00=autocaloff

Write1to

01=autocalon(default)

update

10=supervisormode

whenin

11=autocaloff

supervisor

mode

VCOrange

Default=1000

RFfilterDefault=0000

Seesection1 19

IF Cfilt r

Defaul =0000

Seesection1.22

IFchannelfilter

Default=00000

Seesection0

LNAgain

00X0=5dB(default)

00X1=2.5dB

0100=0dB

0101=2.5dB

0110=5dB

0111=7.5dB

1000=10dB

1001=12.5dB

1010=15dB

1011=17.5dB

1100=20dB

1101=25dB

111X=30dB

Seesection1.13.1

Reserved

Default=0000000

Reserved

Default=0

Reserved

Default=00

IFstage4gain

00=0dB01=1dB

10=2dB(default)

11=3dB

Seesection0

IFstage3gain

00=0dB01=3dB(default)

10=6dB

11=9dB

Seesection0

IFstage6gain

000=3dB(default)

001=6dB

010=9dB

011=12dB

100=15dB

Seesection0

IFstage2gain

00=0dB01=3dB

10=6dB

11=9dB(default)

Seesection0

IFstage5gain

000=3dB(default)

001=6dB

010=9dB

011=12dB

100=15dB

Seesection0

Mixergain

0=4dB

(default)

1=12dBSee

1.15

IFstage1

gain

0=3dB

1=6dB(defa

ult)

See0

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page18

E4000

Bitnumber

0x1Ah

AGC1

0x1Bh

AGC2

0x1Ch

AGC3

0x1Dh

AGC4

0x1Eh

AGC5

0x1Fh

AGC6

0x20h

AGC7

0x21h

AGC8

0x24h

AGC11

0x25h

AGC11

0x29h

DC1

0x2Ah

DC2

0x2Bh

DC3

0x2Ch

DC4

Address

7

LNAgain

highflag

Usershould

updateloop

whena

value1is

read(bit5)

LNAgain

lowflag

Usershould

updateloop

whena

value1is

read(bit5)

LNAupdate

Write1to

updatein

supervise

mode

Linearity

mode

Seesection

1.17.1

Default=1

Gaincontrolmode

Seesection1.12

Default=0000

LNAautonomouscontrolcalibrationvalue

Receivedsignalstrengthindicator

Seesection0

LNAautonomouscontrolHighthreshold

WritethresholdvaluewhenE4000isinitialised

LNAautonomouscontrolLowthreshold

WritethresholdvaluewhenE4000isinitialised

Reserved

Reserved

LNA

LNAautonomouscontrolAveragingtime

Default=0

Alwayswrite=00

calibration

Default=0000

request

See1.13.3

Reserved

RFgain

Mixerthreshold

Mixergain

Default=00

control

See1.15.2

control

gainstep

mode

size0=

1=auto

2.5dB

(default)

1=5dB

Sensitivity/Linearitymodeswitchpoint

Sensitivity/

Default=0101101(45dB)

linearity

Seesection1.17 1

mode

control

1=auto

control

0=user

control

(default)

Reserved

LNAgainenhancementlevel

LNAgain

Default=00000

Default=00

enhance

enable

Reserved

Linearity

Linearity

Default=000000

monitor

monitorflag

resetflag

Donotwrite

Donotwrite

tothis

tothis

register

register

Reserved

DCoffsetcal

Default=0000000

request

Write1See

section0

Reserved

IchannelDCoffset

Default=00

Seesection0

Reserved

QchannelDCoffset

Default=00

Seesection0

Reserved

Qchanneloffsetrange

Reserved

Ichanneloffsetrange

Default=00

Seesection0

Default=00

Seesection0

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page19

E4000

Bitnumber

0x2Dh

DC5

Address

7

6

Reserved

Default=000

0x2Eh

DC6

0x2Fh

DC7

0x51h

QLUT1

0x52h

QLUT2

0x53h

QLUT3

0x60h

ILUT0

0x61h

ILUT1

0x62h

ILUT2

0x63h

ILUT3

0x70h

Dctime1

Qrange00

Lookuptabledata

Seesection1.27.1

Qrange01

Lookuptabledata

Seesection1.27.1

Qrange10

Lookuptabledata

Seesection1.27.1

Qrange11

Lookuptabledata

Seesection1.27.1

Irange00

Lookuptabledata

Seesection1.27.1

Irange01

Lookuptabledata

Seesection1 27.1

Irange10

Lookup abledata

Seesection1.27.1

Irange11

Lo kuptabledata

Seesection1 27.1

Reserved

Default=000

Timevarying

DCrange

DCoffset

enable

range

disables

increment

autorange

enable

calibration

Disable=0

(onlyduring

(default)

initialcal)

Seesection

1.27.2

DCoffsetthreshold

Seesection1.27.2

Reserved

Default=00000

Reserved

Default=000000

0x30h

DC8

0x50h

QLUT0

Timevarying

DCoffsetI

lowflag.

Usershould

updateloop

whena

value1is

read

DCrange

detector

enable

1=enable

(default)

Seesection

0

DCoffsetQ

LUTenable

Default=1

See1.27.1

DCoffsetI

LUTenable

Default=1

See1.27.1

IFcommonmodevoltageadjust

Seesection1.18

ZeroLNA.

Donotwrite

tothis

register

DCoffsetQ00

Look uptabledata

Seesection1.27.1

DCoffset Q01

Lookuptabledata

Seesecti n1.27.1

DCo fsetQ10

Look uptabledata

Seesection1.27.1

DCoffsetQ11

Lookuptabledata

Seesection1.27.1

DCoffsetI00

Lookuptabledata

Seesection1.27.1

DCoffsetI01

Lookuptabledata

Seesection1.27.1

DCoffsetI10

Lookuptabledata

Seesection1.27.1

DCoffsetI11

Lookuptabledata

Seesection1.27.1

Timevarying Timevarying

DCoffsetI DCoffsetI

highflag.

channel

Usershould

update.

updateloop

Write1to

whena

updateloop

value1is

supervisor

read

mode

ZeroLNA

Donotwrite

tothis

register

TimevaryingDCoffsetI

channelmode

00=TimevaryingDCoffset

off

01=TimevaryingDCoffset

on

10=Supervisormode

11=TimevaryingDCoffset

off

Seesection1.27.2

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page20

E4000

Bitnumber

0x71h

Dctime2

Address

7

Reserved

Default=000

0x72h

Dctime3

Timevarying

DCoffset

Qlowflag.

Usershould

updateloop

whena

value1is

read

Timevarying

DCoffset

Qhighflag.

Usershould

updateloop

whena

value1is

read

Timevarying

DCoffset

Qchannel

update.

Write1to

updateloop

supervisor

mode

TimevaryingDCoffsetQ

channelmode

00=TimevaryingDCoffset

off

01=TimevaryingDCoffset

on

10=Supervisormode

11=TimevaryingDCoffset

off

Seesection1.27.2

TimevaryingDCoffsetthreshold

Seesection1.27.2

Donotwritetothisregister

0x73h

Dctime4

Reserved

Default=00000

0x74h

PWM1

0x75h

PWM2

TimevaryingDCoffsettimercontrol

Seesection1.27.2

Donotwritetothisregister

PWMupperthresholdGain0

Default=00000011

Seesection1.17.3

PWMlowerthresholdGa n0

Default=11111100

Seesection1.17.3

PWMupperthresholdGain1

Default=00000011

Se section1.13.2

PWMlowerthresholdGain1

Default=11111100

Seesection1 13.2

Reserved

Default=000000

0x76h

PWM3

0x77h

PWM4

0x78h

Bias

0x79h

Rese ved

Default=0000

0x7ah

0x7bh

Cont olbit

Alwayswrite

0

0x7dh

Quadgenbias

Default=00

Referencecurrentcontrol

Donotwritetothisregister

Clockoutputpowerdownkey

Writing10010110willpowerdownE4000clockoutput

Seesection0

Channelfiltercalibrationvalue

Seesection0

Reserved

Default=0000000

Quadgendriverbias

Default=11

Referencecurrentcontrol

Seesection1.11

Dividerbias

Default=00

Referencecurrentcontrol

Donotwritetothisregister

Channel

filtercal.

Write1to

instructa

calibration

I2Cregister

address

address

increment

See1.3

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page21

E4000

Bitnumber

0x7eh

Key0

0x7fh

Key1

0x86h

Ctrl1

0x87h

Ctrl2

0x88h

Ctrl3

0x9fh

Ctrl4

0xa0h

Ctrl5

0xa3h

Ctrl6

0xa4h

Ctrl7

0xa5h

Ctrl8

0xa6h

Ctrl9

0xa7h

Ctrl10

Address

7

Writevalue=0x01htopermitaccesstosubsequentregisters

Writevalue=0xfehtopermitaccesstosubsequentregisters

Configuresdigitalup/downgaincontrolmode

0x50h(default)=PolarityA

0x51h=polarityB

ConfiguresMixer

Write0x20hwhentunerisinitialised

ConfiguresMixer

Write0x01hwhentunerisinitialised

ConfiguresLNA

Write=0x7fhwhentunerisinitialised

ConfiguresLNA

Write0x07hwhentunerisinit alised

ConfiguresIFgain

Default=0x21h.Ifrequired,write=0x10htoreduceIFgainby6dB(tooptimizesignallevelintoademodulator)

ConfiguresIFgain

Default=0x64h.Ifrequired,write=0x42htoreduceIFgainby6dB(tooptimizesignallevelintoademodulator)

ConfiguresIFgain

Default=0x1ah.Ifrequired,write=0x06htoreduceIFgainby6dB(tooptimizesignallevelintoademodulator)

ConfiguresIFgain

Default=0x42h.Ifrequired,write=0x21htoreduceIFgainby6dB(tooptimizesignallevelintoademodulator)

ConfiguresIFgain

Default=0xa6h.Ifrequired,write=0x64htoredu eIFgainby6dB(tooptimizesignallevelintoademodulator)

Note: Registers addresses above 0x80h should not be written to with the exception of those highlighted

above

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page22

E4000

DEVICEDESCRIPTION

1.1 TwoWire,I2CInterface

TheE4000usesatwowire,I2Ccompatibleserialinterface.Pins15(SDAT)and16(SCLK)areboth3.3V

tolerant,permittinginterfacingwith3.3VI2Cmasterdevices.

TheE4000isaslaveonlydevice,supportingsevenbitaddressing.Thedeviceaddresscanbeconfigured

usingtheA0&A1inputpins.Theaddressisconfiguredpertable1(Note:7and8bitaddressesarequoted.

The8bitaddressincludesthereadwritebit).

TheI2CdatalinerequiresapullupresistortoVDD(3.3Vtolerant).Thisresistorvalueshouldbe>4k7Ohms.

A1(Pin12)

A0(Pin11)

Deviceaddress(7

Deviceaddress(8

Deviceaddress(8

bit)

bit)(write)

bit)(read)

0

0

0x64h

0xc8h

0xc9h

0

1

0x65h

0xcah

0xcbh

1

0

0x66h

0xcch

0xcdh

1

1

0x67h

0xceh

0xcfh

Table1:Serialinterfacedeviceaddress

1.2 SerialInterfaceProtocol

Theserialprotocolsupportsserialwritesandreads,bothtoindividualandsequentialaddressestofacilitate

programmingspeed.Readorwriteoperationsareimplementedasshownbelow.

Figure2:SingleBytewrite

Figure3:Pagewrite

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page23

E4000

Figure4:Singlebyteread

Figure5:Sequen ialread

A dummy read or write command should be sent to the E4000 after the tuner is first powered on or is

reset.Thiswillnot beacknowledged butwill configure the E4000I2Cinterface.After thispointI2Cread

andwritecommandsbehavenormally.

Register0x7Dh[0]maybeusedtocontrolwhetherasequentialreadorwriteincrementsregisteraddress

betweeneachread.Toconfiguretocontinuousreadfromthesameregister setthisbit= 0.Thisfeature

maybeusefultoauserwhowishestocontinuouslyreadthesameregisterduringoperationofthetuner.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page24

E4000

1.3

FrequencySynthesiser

Figure6:FrequencySynthesizerarchitecture

ThearchitectureoftheE4000Frequencysynthesizerisshowninfigure6.Thisgeneratesthelocaloscillator

whichisusedinthemixertodownconvertRFtobaseband.TheVCOoutputisdividedbyRtogenerate

thelocaloscillatorforthedownconversionmixer.

TheVCOoutputisalsopassedtothefeedbackdivider,whereitsfrequencyisdividedbeforebeingsentto

thephase/frequencydetector.ThesigmadeltadynamicallydithersthedivisionbetweenZand

alternativedividersettings.Thispermitsset ingofanonintegerdividervaluegivinghighaccuracyinthe

frequenciestowhichthelocaloscillatorcanbelocked.Thearchitectureofthisdividerensuresthatthe

localoscillatormaintainslowphasenoiseacrosstherangeofsettings.

ThephasedetectorcomparesthedividedVCOfrequencywiththereferenceoscillatorfrequencyand

generatesatuningvoltagetopulltheVCOtothecorrectfrequency.

Thedividerandsigmadeltavaluesneedtobesetaspertheformulae

(equation1)

fVCO=fOscillator*(Z+X/Y)

And

fLO=fVCO/R

(equation2)

WhereY=65536andfOscillatoristhecrystalfrequency(e.g.26MHz).ValuesR,X,YandZareconfigurable

usingthetunerserialinterface.

Togeneratea0HzIFfrequency,thelocaloscillatorfrequencyshouldbesetsothatitisthesameastheRF

frequency.TheVCOshouldbeoperatedwithintherangeof2600to3900MHz.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page25

E4000

1.4 PLLFeedbackdivider(/Z)

The/Ndivideriscontrolledbyregister0x09h.

ForexampletosetN=99

Set0x09h=99(decimal)

1.5 X,Sigmadeltasetup

ThevalueofXisdefinedbyregisters0x0Ah[7:0](LSB)&0x0Bh[7:0](MSB).Thiscanbesetbetween0and

65535.

Forexample,tosetX=5041

(5041decimal=13b1hex)

Register0x0ah=b1h=177(decimal)

Register0x0bh=13h=19(decimal)

1.6

/RVCOoutputdivider

Theoutputdivider,R,issetaspertable2.Notethedifferenceinsettingswhenusingthreephasemixing

(describedinsection1.7).

Output divider /R Division (3 phase Division (3 phase

[2:0]

mixingdisabled)

mixingenabled)

0x0dh[2:0]

000

2

4

001

4

8

010

6

12

011

8

16

100

12

24

101

16

32

110

20

40

111

24

48

Table2:Outputdivider

1.7 Threephasemixing

Threephasemixingcombineshighspeedclockstocreatealocaloscillatorclockwithsloweredgespeeds.

Thisisusedtoreducethehighfrequencyharmonics,whichwhenoperatingatlowfrequencieswouldbe

withinthetunerbandwidth.Thisfeaturepreventsinterferersignalsmixingwithharmonicsofthelocal

oscillatorfrequency,increasingthedynamicrangeofthetuner..

ItisrecommendedthatthreephasemixingshouldbeusedforVHFoperationandnotforUHForLband

operation.Thisisenabledordisabledusingregister0x0Dh[3].Notetheeffectenablingthisfeaturehason

the/Rdivisionasshownintable2.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page26

E4000

1.8 ExampleFrequencysynthesizerconfiguration

TotunetoanRFsignalof666MHz,andforazeroIFoutputfrequency,theLOfrequency=666MHz

ThepermittedVCOfrequencyrangeisbetween2600and3900MHz.

666MHziswithintheUHFfrequencyband.ForUHFband,3phasemixingshouldbeturnedoff.

Usingsection1.3,equation2andchoosingR=4fromtable11givesaVCOfrequencyof2664MHz,(choose

anacceptableVCOfrequencyrangewhileusingavalueofRthatispossibletoset).

0x0Dh=1

Usingsection1.3equation1andfora26MHzcrystalfrequency.

N+X/Y=fvco/foscillator=2664/26=102.4615385

N=102

(theintegerpartofthis)

0x09h=102(decimal)

X/Y=0.4615385

(theremainder)

SinceY=65536

X=30247=7627

0x0Ah=0x27h=39(decimal)

0x0Bh = 0x76h = 118 (decimal)

1.9

VCOCalibration

TheE4000VCOshouldbecalib atedafterafrequencychangeinordertooptimiseperformance.A

calibrationisinstructedbywriting1to0x0Eh[2].Afterbeinginstructedtocalibrate,theE4000willself

calibratewithouttheneedforuserintervention.0x0Eh[1:0]shouldbeset=01,turningonautocalibration.

TheE4000periodicallymonitorswhethertheVCOisoperatinginitsoptimumcondition.Ifeverrequired,

theE4000willrecalibratetomaintainoptimalVCOperformance.However,arecalibrationwillbearare

event.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page27

E4000

1.10 E4000SignalPath

Figure7:BlockdiagramoftheE4000signalpath

TheE4000signalpathcontainsawidebandLNA(64MHzto1 7GHz).TheRFsignalisfiltered,reducingthe

effectoffaroutblockingsignals.Thesignalisthendownconvertedtobasebandbythemixer,withIandQ

phase channels generated. The IF signal is filtered to attenuate adjacent channel interferers. Signals are

thenamplifiedsuchthatlevelsareoptimalforsamplingbythebasebandsADCs.Tunergaincanbevaried

from2to99dBprovidingalargedynamicrangeofsignalreception.

TheLNAfrequencyresponseisoptimisedfordifferentfrequencybandsasdescribedinsection1.11.

Gains can be controlled by various methods, as described in section 1.12. These include on chip

autonomous control or baseband control using a PWM interface, digital up / down interface or using

registerwritesviathe 2Cserialinterface.

Filterscanbeconfiguredasdescribedinsection1.19to0.

UnwantedDCoffsetsintheIFgainpathareeliminatedasdescribedinsection1.25.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page28

E4000

1.11 FrequencyBandSelection

Thefrequencybandshouldbeinitialisedaspertable3.ThisregisterconfigurestheLNAtohaveoptimum

gainatthefrequencyofoperation.

Band

Register0x07h[2:1]

VHFII(64108MHz)

00

VHFIII(170240MHz)

01

UHF(default)(470858MHz)

10

L(14521680MHz)

11

Table3:Frequencybandselection

Whenselectingfrequencybandstheusershouldalsoconfigureregister0x78h[1:0].Thissetsbiascurrents

usedasreferences,suchthatthetunerisoptimizedforoperationinthedifferentfrequencybands.

Band

Register0x78h[1:0]

VHFII(64108M)

11

VHFIII(170240M)

11

UHF(default)(470858MHz)

11

L(14521680MHz)

00

Table4:Frequencybandbiascurrentreferenceoptimisation

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page29

E4000

1.12 GainControl

Theoptimumgainsettingsrequiredforthedifferentelementsofthesignalpathwillvary,dependingon

theenvironmentinwhichthetunerisbeingused.Forexample,thereceivedsignalmaybeatalowpower

level.Ifso,highgainsarerequiredtoachievethetunernoisefigurethatgivesoptimumsensitivity.Or

theremaybeahighpowersignalreceived,inwhichcaseoptimumgainsmaybelowerasamplifier

linearity,ratherthannoise,maybethetunerlimitation.

TheE4000canbeconfiguredsuchthatgainsmaybecontrolledusingavarietyofmechanisms.TheLNA

gaincanbecontrolledautonomouslybythetunerbasedonthepowerlevelmeasuredusinganonchip

widebandpowerdetector.Alternatively,LNAgainsmaybecontrolledbasedonpowersmeasuredbya

basebandspowerdetector.TheE4000supportsPWMorI2Cserialinterfacecontrolinterfacesthrough

whichthebasebandcaninstructagainchangeasrequired.

IFgainupdatesmayalsobeinstructedusingaPWMorI2Cserialinterface.Inaddition,theIFgaincontrol

alsosupportsa2pindigitalstepup/downcontrolinterface.

ThemodeinwhichTunergainsarecontrolledcanbeconfiguredpertable5.Themodeofoperationshould

beselectedusingregister0x1Ah[3:0].

AGC_mode[3:0]

AGCmode

0x1A[3:0]

0000

Serialinterfacecontrol

0001

IFPWMcontro LNAserialinterfacecontrol.

0010

IFPWMcontrol LNAautonomouscontrol

0011

IFPWMcontrol.LNAsupervisorcontrol

0100

IFserialinterfacecontrol.LNAPWMcontrol.

0101

IFPWMcontrol.LNAPWMcontrol.

0110

IFdigitalcontrol.LNAserialinterfacecontrol.

0111

IFdigitalcontrol.LNAautonomouscontrol.

1000

IFdigitalcontrol.LNAsupervisorcontrol.

1001

IFserialinterfacecontrol.LNAautonomouscontrol.

1010

IFserialinterfacecontrol.LNAsupervisorcontrol

Table5:Gaincontrol

1.13 LNAGainControl

It is recommended that the LNA gains are configured for different received power levels per figure 8.

Operation with the suggested settings maintains the optimum balance of noise figure and linearity for a

givenoperatingenvironment.

Two ranges are suggested the first is for the case where received power is seen to be increasing. The

second is for the case where received power is seen to be decreasing. This provides approximately 5dB

hysteresisandpreventsthegainfromchatteringduetominorfluctuationsinreceivedpower.Thepower

quotedisthewidebandpowerreceivedbythetuner.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page30

E4000

LNA Gain thresholds

35

30

LNA Gain (dB)

25

20

15

Increasing power

10

Decreasing power

5

0

5-

-50

-40

-30

-20

-10

10Input Power (dBm)

Figure8:LNAgaincontrol

Whenusingautonomousorsupervisormodes,theRFgaincontrolwillautomaticallyfollowthisprofile.LNA

gainstepsizeisapproximately2.5dB.Ifdesired,theusercaninstructalargerstepsizetobeused(5dB).

Thisiscontrolledbyregister0x20[5].

1.13.1 LNASerialInterfaceGainControl

The LNA gain can be controlled using register writes via the serial interface. Gains are configured as per

table6.

LNAgain

LNAgain(dB)

0x14h[3:0]

(typical)

00X0

5

00X1

2.5

0100

0

0101

2.5

0110

5

0111

7.5

1000

10

1001

12.5

1010

15

1011

17.5

1100

20

1101

25

111X

30

Table6:LNAserialinterfacecontrol

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page31

E4000

1.13.2 LNAdigitalPWMgaincontrol

WhenoperatinginPWMgaincontrolmode,thetunerchangesLNAgainbasedonadigitalPWMsignal

generated by the user and received by the tuner at pin 22 Gain1. The user should generate this PWM

signalaspertable7,toindicatewhetherthetunerneedstoincrementordecrementLNAgainorleavethe

gainunchanged.

PWMdutycycle

Tuneraction

50%

Nochangeingain

>75%

Incrementgain

<25%

Decrementgain

Table7:PWMIFgaincontrolDutycycle

ThePWM dutycycleforwhich the tunerwilltreatthereceivedsignalasanincrementcanbemodified

using register 0x76h. Similarly, the duty cycle for a decrement case can be modified by register 0x77h.

Values to which these registers should be programmed vary depending on the period of the PWM input

signal.

ThetunerusesadigitalinputtosamplethePWMsignalreceived Thesignalisoversampled.Timingofthe

detectorissuchthattheE4000inputiscompatiblewithaPWMcontrolsignalwithperiodbetween2and

157us. When calculating the duty cycle, the E4000 will treat every 2 falling edges received as a signal

period.Timingisillustratedinfigure9.

Period

Switch

Switch

Switch

Switch point

point

point

point

50% = No

>75% = Increment

change

Figure9:LNAPWMgaincontroltimingdiagram

Aflowdiagramdetailingoperationofthiscontrolschemeisshowninfigure10.

Thismethodisnotcompatiblewithpulsedensitymodulationcontrolsignals.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page32

E4000

Figure10:LNAPWMgaincontrolflowdiagram

1.13.3 LNAAutonomousGainControl

ThetuneriscapableofdeterminingwhentheLNAgainneedstobechangedandmodifyingthisgainsuch

thatoptimaloperationismaintained.Anonchipwidebandpowerdetectormeasuresthesignalamplitude

receivedbythetuner(inthebandwidth641700MHz).Thedetectorwillmeasureaveragereceivedsignal

poweroveraperiodoftimepertable8.Ifthevalueisaboveorbelowthethresholdlevelssetinregisters

0x1Dh and 0x1Eh, then the gain will be updated When changing gains, the control loop will step

sequentiallythroughthepossiblesettingsuntilthedesiredsignallevelisreached.

Register0x1F[3:0]

AGCcontrolloopupdaterate(us)

0000

60

0001

120

0010

240

0011

480

0100

960

0101

1920

0110

3840

0111

7680

1000

15360

1001

30720

1010

61440

Table8:AGCcontrolloopupdaterate

1.13.4 LNASupervisorGainControl

Insupervisormode,theLNAcontrolloopoperatesasper1.13.3LNAautonomouscontrol.However,the

controlloopwillnotupdategainsuntilinstructedtobytheuser.

TheE4000willindicatewhetheraLNAgainchangeisrequiredbysettingregister0x1Ah[7or6]=1.Ifa

gainchangeisrequired,theusershouldwrite0x1Ah[5]=1whichwillinstructthelooptoupdategain.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page33

E4000

1.14 ReceivedSignalStrengthIndicator(RSSI)

Thereceivedsignalstrengthmeasuredbythetunercanbeobservedbytheuserthroughregister0x1Ch.

TheRSSIwillfunctionacrossarangeofinputpowers(50to10dBm).Thisistherangeofinputpowers

overwhichtheLNAgainshouldbemodifiedtomaintainlinearity.Forreceivedpowerslowerthanthisthe

LNAshouldbesettomaximumgain.

TheRSSIindicatorcanbeaccessedwhenoperatinginautonomousorsupervisorgaincontrolmodebutnot

whenusingPWMorserialinterfacecontrol.

TheRSSIregisterisscaledvs.receivedpowerasperfigure11.

Figure11:RSSIdetectorregistervaluevs.detectorinputpower

Note:Thepowershowninfigu e11istheRMSinputpowertotheRSSIdetector.ThisrelatestotheE4000

inputpowerpertheformula

E4000inputpower=RSSIdetectorpowerLNAgain

1.15 MixerGainControl

1.15.1 MixerGainSerialInterfaceControl

TheMixermaybecontrolledusingregisterwritesviatheserialinterface.Gainsaresetaspertable9.The

mixer gain should be set high when a low signal level is received (<~ 35dBm) and set low when a high

signallevelisreceivedattheinputtothetuner(>~35dBm).TheE4000receivedpowercanbemonitored

usingtheRSSIindicator

Mixergain

Mixergain(dB)

0x15h[0]

(typical)

0

4

1

12

Table9:Mixergaincontrol

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page34

E4000

1.15.2 MixerGainAutonomousControl

TheMixermaybeconfiguredsuchthatagainchangeoccursautomaticallyastheLNAgainischanged.This

featureisenabledbysetting0x20h[0]=1.Register0x20h[4:1]shouldbeprogrammedwiththedesired

thresholdvalueforwhichtheuserwishesmixergaintochange.ThisthresholdcorrespondstoaLNAgain

valueasshownintable6.Itisrecommendedthattheuserconfigures0x20h=0x15h.Thiswouldmeanthat

themixergainswitchesstatewhenLNAgainissetto7.5dB.ForhigherLNAgains,Mixergain=12dB.For

7.5dBorlowergains,Mixergain=4dB.

SincetheLNAgaincontrolincludesHysteresis,themixergainwillnottogglearoundapointduetosmall

fluctuationsininputpower.

1.16 LNAGainenhancement

Itisrecommendedthatregister0x24hiswritten=5oninitializationofthetuner.ThiswillenabletheLNA

gain enhancement mode. This is an automated control feature that will ncrease the NA gain by an

additional 5dB when LNA and mixer are set to maximum gain levels. This mode s intended to optimize

tunernoisefigureincaseswheregainishigh,(smallsignalsarerece ved).TheLNAgainnumbersquoted

throughoutthisdocumentassumethatthisregisterisprogrammedtotherecommendedvalue.

1.17 IFGainControl

IFgainscanbecontrolledusingthemethodsdescribed nsections1.17.1to1.17.4.

1.17.1 IFgainLinearity/SensitivityMode

InsomecircumstancesitmaybepreferabletooptimisetheIFgainsfornoise(foroptimumsensitivity)or

linearity(largesignalhandling,suchasinthepresenceofanadjacentchannelinterferer).Theusercanset

whetherthetuneroptimisesgainsforoptimumsensitivityorlinearityusing0x1Ah[4].Themodemaybe

switchedbytheuserbasedonthetunersreceivedsignalpower(sensitivitymode<~60dBm)orbasedon

theuserdetectingthepresenceonanadjacentchannelinterferer.

AGCramp

IFgainmode

0x1A

4]

0

Linearity

1

Sensitivity

Table10:IFgaincontrolmode

Alternatively,thetunercanbeconfiguredtoautomaticallyswitchbetweensensitivityandlinearitymodes.

Thisfeatureiscontrolledusingregister0x21h.Bits6to1canbeprogrammedtothetunergainatwhich

theuserwishesthedevicetoswitchbetweenlinearity&sensitivitymodes.Forexample,defaultsetting=

45dB.WhenLNA+mixer+IFgainis<45dB,thetunerwilloperateinlinearitymode.SomeHysteresisis

includedtopreventmodesswitchingaroundduetosmallfluctuationsinpower.

Automatedcontrolofthisgainoptimisationmodeisenabledbysetting0x21h[0]=1.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page35

E4000

1.17.2 IFGainSerialInterfaceControl

IFstage1gain

0x16h[0]

0

1

IFstage1gain(dB)

(typical)

3

6

Table11:IFstage1gaincontrol

IFstage2gain

0x16h[2:1]

00

01

10

11

IFstage2gain(dB)

(typical)

0

3

6

9

Table12:IFstage2gaincontrol

IFstage3gain

0x16h[4:3]

00

01

10

11

IFstage3gain(dB)

(typical)

0

3

6

9

Table13:IFstage3gaincontrol

IFstage4gain

0x16h[6:5]

00

01

1x

IFstage4gain(dB)

(typical)

0

1

2

Table14:IFstage4gaincontrol

IFstage5gain

0x17h[2:0]

000

001

010

011

1xx

IFstage5gain(dB)

(typical)

3

6

9

12

15

Table15:IFstage5gaincontrol

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page36

E4000

IFstage6gain

0x17h[5:3]

000

001

010

011

1xx

IFstage6gain(dB)

(typical)

3

6

9

12

15

Table16:IFstage6gaincontrol

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page37

E4000

Linearity Mode

Register0x16h

0x7f

0x5f

0x3f

0x1f

0x5d

0x3d

0x1d

0x5b

0x3b

0x1b

0x59

0x39

0x19

0x5c

0x3c

0x1c

0x5a

0x3a

0x1a

0x58

0x38

0x18

0x50

0x30

0x10

0x48

0x28

0x08

0x40

0x20

0x00

0x40

0x20

0x00

0x40

0x20

0x00

0x40

0x20

0x00

0x40

0x20

0x00

0x40

0x20

0x00

0x40

0x20

0x00

0x40

0x20

0x00

0x40

0x20

0x00

Register0x17h

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x24

0x23

0x23

0x23

0x22

0x22

0x22

0x21

0x21

0x21

0x20

0x20

0x20

0x18

0x18

0x18

0x10

0x10

0x10

0x08

0x08

0x08

0x00

0x00

0x00

E4000Datasheet4v0

SE4000DS001

August2010

IFStage1 IFStage2 IFStage3 IFStage4 IFStage5 IFStage6 TotalGain(dB)

9

9

9

3

15

15

60

9

9

9

2

15

15

59

9

9

9

1

15

15

58

9

9

9

0

15

15

57

9

6

9

2

15

15

56

9

6

9

1

15

15

55

9

6

9

0

15

15

54

9

3

9

2

15

15

53

9

3

9

1

15

15

52

9

3

9

0

15

15

51

9

0

9

2

15

15

50

9

0

9

1

15

15

49

9

0

9

0

15

15

48

0

6

9

2

15

15

47

0

6

9

1

15

15

46

0

6

9

0

15

15

45

0

3

9

2

15

15

44

0

3

9

1

15

15

43

0

3

9

0

15

15

42

0

0

9

2

15

15

41

0

0

9

1

15

15

40

0

0

9

0

15

15

39

0

0

6

2

15

15

38

0

0

6

1

15

15

37

0

0

6

0

15

15

36

0

0

3

2

15

15

35

0

0

3

1

15

15

34

0

0

3

0

15

15

33

0

0

0

2

15

15

32

0

0

0

1

15

15

31

0

0

0

0

15

15

30

0

0

0

2

12

15

29

0

0

0

1

12

15

28

0

0

0

0

12

15

27

0

0

0

2

9

15

26

0

0

0

1

9

15

25

0

0

0

0

9

15

24

0

0

0

2

6

15

23

0

0

0

1

6

15

22

0

0

0

0

6

15

21

0

0

0

2

3

15

20

0

0

0

1

3

15

19

0

0

0

0

3

15

18

0

0

0

2

3

12

17

0

0

0

1

3

12

16

0

0

0

0

3

12

15

0

0

0

2

3

9

14

0

0

0

1

3

9

13

0

0

0

0

3

9

12

0

0

0

2

3

6

11

0

0

0

1

3

6

10

0

0

0

0

3

6

9

0

0

0

2

3

3

8

0

0

0

1

3

3

7

0

0

0

0

3

3

6

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page38

E4000

Sensitivity mode

Register0x16h

0x7f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x5f

0x3f

0x1f

0x57

0x37

0x17

0x4f

0x2f

0x0f

0x47

0x27

0x07

0x45

0x25

0x05

0x43

0x23

0x03

0x41

0x21

0x01

0x44

0x24

0x04

0x42

0x22

0x02

0x40

0x20

0x00

Register0x17h

0x24

0x24

0x24

0x24

0x1c

0x1c

0x1c

0x14

0x14

0x14

0x0c

0x0c

0x0c

0x04

0x04

0x04

0x03

0x03

0x03

0x02

0x02

0x02

0x01

0x01

0x01

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

0x00

E4000Datasheet4v0

SE4000DS001

August2010

IFStage1 IFStage2 IFStage3 IFStage4 IFStage5 IFStage6 TotalGain(dB)

9

9

9

3

15

15

60

9

9

9

2

15

15

59

9

9

9

1

15

15

58

9

9

9

0

15

15

57

9

9

9

2

15

12

56

9

9

9

1

15

12

55

9

9

9

0

15

12

54

9

9

9

2

15

9

53

9

9

9

1

15

9

52

9

9

9

0

15

9

51

9

9

9

2

15

6

50

9

9

9

1

15

6

49

9

9

9

0

15

6

48

9

9

9

2

15

3

47

9

9

9

1

15

3

46

9

9

9

0

15

3

45

9

9

9

2

12

3

44

9

9

9

1

12

3

43

9

9

9

0

12

3

42

9

9

9

2

9

3

41

9

9

9

1

9

3

40

9

9

9

0

9

3

39

9

9

9

2

6

3

38

9

9

9

6

3

37

9

9

9

0

6

3

36

9

9

9

2

3

3

35

9

9

9

1

3

3

34

9

9

9

0

3

3

33

9

9

6

2

3

3

32

9

9

6

1

3

3

31

9

9

6

0

3

3

30

9

9

3

2

3

3

29

9

9

3

1

3

3

28

9

9

3

0

3

3

27

9

9

0

2

3

3

26

9

9

0

1

3

3

25

9

9

0

0

3

3

24

9

6

0

2

3

3

23

9

6

0

1

3

3

22

9

6

0

0

3

3

21

9

3

0

2

3

3

20

9

3

0

1

3

3

19

9

3

0

0

3

3

18

9

0

0

2

3

3

17

9

0

0

1

3

3

16

9

0

0

0

3

3

15

0

6

0

2

3

3

14

0

6

0

1

3

3

13

0

6

0

0

3

3

12

0

3

0

2

3

3

11

0

3

0

1

3

3

10

0

3

0

0

3

3

9

0

0

0

2

3

3

8

0

0

0

1

3

3

7

0

0

0

0

3

3

6

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page39

E4000

1.17.3 IFGainDigitalPWMControl

WhenoperatinginPWMgaincontrolmode,thetunerchangesIFgainbasedonaPWMsignalgeneratedby

thebasebandandreceivedbythetuneratpin21Gain0.TheusershouldgeneratethisPWMsignalasper

table17,toindicatewhetherthetunerneedstoincrement/decrementIFgainorleavethisunchanged.

PWMdutycycle

Tuneraction

50%

Nochangeingain

>75%

Incrementgain

<25%

Decrementgain

Table17:PWMIFgaincontrolDutycycle

The duty cycle for which the tuner will treat the received signal as an increment can be modified using

register0x74h.Similarly,thedutycycleforadecrementcasecanbemodifiedbyregister0x75h.Values

towhichtheseregistersshouldbeprogrammedvarydependingontheperiodofthePWM nputsignal.

ThetunerusesadigitalinputtosamplethePWMsignalreceived Thesignalisoversampled.Timingofthe

detectorissuchthattheE4000inputiscompatiblewithaPWMcontrolsigna withperiodbetween2and

157us. When calculating the duty cycle, the E4000 will treat every 2 falling edges received as a signal

period.Timingisillustratedinfigure12.

Period

Switch

Switch

Switch

Switch point

point

point

point

50% = No

>75% = Increment

change

Figure12:IFPWMgaincontroltimingdiagram

Aflowdiagramdetailingoperationofthiscontrolschemeisshowninfigure13.

Thismethodisnotcompatiblewithpulsedensitymodulationcontrolsignals.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page40

E4000

Figure13:IFPWMgaincontrolflowdiagram

1.17.4 IFGainDigitalControl

ItispossibletocontrolIFgainusinga2pindigitalcontrolinterface.Thegainischangeddependingonthe

stateofPins21Gain0and22gain1.Gainsareincrementedordecrementedinstepsof1dB.Thedefault

truthtableisshowninTable18.

Digitalcontrol

Tuneraction

Gain1/Gain0

00

Decreasegain

01

Holdgain

10

Holdgain

11

Increasegain

Table18:IFgaindigitalinterfacecontrol

Analternativelogicschemeisprovided.Thislogiccanbecanbeselectedbysetting0x86h=0x51h.Atruth

tableisshownintable19.

Digitalcontrol

Tuneraction

Gain1/Gain0

00

Holdgain

01

Increasegain

10

Decreasegain

11

Holdgain

Table19:IFgaindigitalinterfacecontrol

Figure14detailstheflowdiagramthatshouldbefollowedwhenusingthisgaincontrolinterface.

Figure14:Digitalup/downgaincontrolinterfaceflowdiagram

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page41

E4000

Note: A no change condition must be sent between sequential increment or sequential decrement

commands.

Each state should be maintained for > 130ns in order for the E4000 to sample levels and instruct a gain

change.

1.18 OutputCommonModeVoltage

Thecommonmodeoutputvoltageofthetunerdefaultsto0.58V.ItispossibletoincreasethisDCvoltage

levelaspertable20.

Register0x2Fh[2:0]

Common mode voltage

(mV)

000

580

001

650

010

650

011

700

100

850

101

900

110

900

111

950

Table20:Outputcommonmodevoltage

It may be possible to programme the tuner output common mode voltage level to match the Baseband

ADCcommonmodevoltagelevel,eliminatingtherequirementforDCblockingcapacitors.Ifthisfeatureis

useditshouldbenotedthattunerlinear tymaydegradeascommonmodevoltageisincreased.Itshould

alsobenotedthatinsomecircumstances,voltagesmayvarybyupto+/160mVvs.nominalvalue,(dueto

a combination of process / temperature variation and tuner DC offsets). If DC blocking capacitors are

removed,thebasebandADCwouldberequiredtotoleratethisvariation.

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page42

E4000

1.19 RFFilter

TheE4000willfilterthesignalattheLNA.Thisfilteringisconfiguredusingregister0x10haspertable21.

NotetheeffectoftheFreqband[1:0]settinginregister0x07h.Boththetypeoffilter(lowpassorband

pass)anditsbandwidtharechangeddependingonthefrequencybandused.

1dB Bandwidth of 1dB Bandwidth of Centre frequency Centre frequency

LNAfilter[3:0]

Register

0x10h lowpassfilter.

lowpassfilter.

ofbandpassfilter. ofbandpassfilter.

(MHz)

[3:0]

(MHz)

(MHz)

(MHz)

Freq band [1:0] = Freq band [1:0] = Freq band [1:0] = Freq band [1:0] =

11(L)

00(VHFII)

01(VHFIII)

10(UHF)

0000(default)

268

509

360

1300

0001

268

509

380

1320

0010

268

509

405

1360

0011

268

509

425

1410

0100

268

509

450

1445

0101

268

509

475

1460

0110

268

509

505

1490

0111

268

509

540

1530

1000

299

656

575

1560

1001

299

656

615

1590

1010

299

656

670

1640

1011

299

656

720

1660

1100

299

656

760

1680

1101

299

656

840

1700

1110

299

656

890

1720

1111

299

656

970

1750

Table21:RFFilterbandwidth

Figure15:RFfilterfrequencyresponseexamples

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page43

E4000

1.20 IFFilter

TheIFpathcontains3filteringsectionsthatareusedtoattenuateadjacentchannelinterferersandprovide

antialiasfilteringsuchthathighfrequenciesareeliminated.Optimumfiltersettingswillvarydependingon

thechannelbandwidth,adjacentchannelinterferersize,ADCsamplingspeedandADCantialiasfilter

response.

1.21 MixerFilter

Thisfiltersectionislocatedbetweenthemixerand1stIFgainstage.Filterattenuationisconfiguredasper

table22andfigure16.

Reg0x11h[7:4]

0.2dBBandwidth

0xxx

27

1000

4.6

1001

4.2

1010

3.8

1011

3.4

1100

3

1101

2.7

1110

2 3

1111

1.9

Table22:Mixerfiltersettings

Figure16:Mixerfiltersettings

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page44

E4000

1.22 IFRCFilter

ThisfilterislocatedbetweenearlyIFgainstages.Filterattenuationisconfiguredaspertable23andfigure

17.

Reg0x11h[3:0]

3dB

bandwidth

(MHz)

0000

21.4

0001

21

0010

17.6

0011

14.7

0100

12.4

0101

10.6

0110

9

0111

7.7

1000

6.4

1001

5.3

1010

4.4

1011

3.4

1100

2.6

1101

1 8

1110

1 2

1111

1

Table23:IFRCfilterattenuation

Filtersetting0000

Filtersetting1111

Figure17:IFRCfilterresponse

E4000Datasheet4v0

SE4000DS001

August2010

UNCONTROLLEDWHENPRINTEDUNLESSSTAMPEDOTHERWISE

Copyright2010ElonicsLtd

Page45

E4000

1.23 IFChannelFilter

Thechannelfilterisasharprollofffilter,attenuatingadjacentchannelinterferers.Responseisaspertable

24andfigure18.

IFchannelfiltersetting Filtercornerfrequency

IFchannelfiltersetting Filtercornerfrequency

Register0x12h[4:0]

(MHz)

Register0x12h[4:0]

(MHz)

00000

5.5

10000

3

00001

5.3

10001

2.95

00010

5

10010

2.9

00011

4.8

10011

2.8

00100

4.6

10100

2 75

00101

4.4

10101

2.7

00110

4.3

10110

2.6

00111

4.1

10111

2.55

01000

3.9

11000

2.5

01001

3.8

11001

2.45

01010

3.7

11010

2 4

01011

3.6

11011

2.3

01100

3.4

11100

2.28

01101

3.3

11101

2.24

01110

3.2

11110

2.2

01111

3.1

11111

2.15

Table24:IFchannelfilter

Setting00000

Filter responses for

settings 11111, 10111,