Beruflich Dokumente

Kultur Dokumente

Contadores Teoria

Hochgeladen von

Louis CharlesOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Contadores Teoria

Hochgeladen von

Louis CharlesCopyright:

Verfügbare Formate

cedentes tericos 3 Desarrollo Materiales 13 Circuito propuesto 13 Desarrollo de la prctica 14 Resultados 14 Conclusiones 15 Antecedentes tericos Introduccin Conceptos Tericos.

1.1. Contadores. 1.2. Circuitos sncronos y asncronos. 1.3. Contadores sncronos (PARALELOS). 1.4. Operacin del circuito. 1.5. Ventajas de los contadores sncronos sobre los asncronos. 1.6. Contadores asncronos en CI. 1.7. Smbolo IEEF)ANSI para el contador 74293. 1.8. El Contador 74193 (LS193/HC193) 1.9. Mas acerca de la Notacin de Dependencia de IEEE/ANSI* 1.1. Contadores Los contadores son circuito electrnicos digitales importantes. Son circuitos lgicos secuenciales porque la temporizacin es obviamente importante y porque necesitan una caracterstica de memoria. Los contadores digitales tienen las siguientes caractersticas importantes: Un nmero mximo de cuentas (Modulo del contador). Cuenta ascendente o Descendente. Operacin sncrona o asncrona.

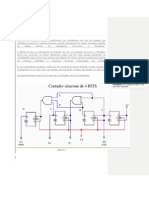

Autnomos o de autodetencin Como en otros circuitos secuenciales, los flip-flop se utilizan para construir contadores. Los contadores son muy tiles en los sistemas digitales; se pueden utilizar para contar eventos como, por ejemplo, nmero de pulso de reloj en un tiempo dado (medida de secuencia). Se pueden utilizar como divisores de frecuencia y para almacenar datos como, en un reloj digital; tambin se usan para direccionamiento secuencial y en algunos circuitos aritmticos. Los circuitos secuenciales generalmente se dividen en dos categoras amplias: la de los sncronos y la de los asncronos. 1.2. Circuitos sncronos y asncronos Un circuito lgico secuencial puede estar compuesto por compuertas y/o flip-flops interconectados en configuraciones quizs complejas que generalmente incluyen algn tipo de realimentacin. El circuito se considera asincrnico si no emplea una seal de reloj peridica C para sincronizar cambios de estado interno. Por consiguiente, los cambios de estado ocurren como respuesta directa a los cambios de seal en las lneas de entradas primarias (Datos) y distintos elementos de memoria pueden cambiar de estado en instantes diferentes. De acuerdo con esta definicin se puede considerar al contador conocido como Johnson como un circuito asncrono vase figura 1.La seal x aplicada a todas las entradas de reloj de todos sus flip-flop no se supone peridica y es una seal de datos ms que una seal de control. 1.3. Contadores sncronos (PARALELOS) El problema que se encuentra en los contadores de rizo es ocasionado por los retrasos acumulados en la propagacin de los FF; dicho de otra manera, no todos lo FF cambian de estado simultneamente en sincrona con los pulsos de entrada. Estas limitaciones pueden superarse con el uso de contadores sncronos o paralelos, en los que todos los FF se disparan en forma simultanea (en paralelo) por medio de los pulsos de reloj. Ya que los pulsos de entrada se aplican a todos los FF, debe utilizarse algn medio para controlar cuando un FF se dispare o permanezca inalterado por un pulso de reloj. Estos se logran utilizando las entradas J y K y se ilustra en la figura 1 para un contador MOD-16 de 4 bits.

figura 1 Si comparamos la comparacin del circuito para este contador sncrono con la de su contraparte asncrono de la figura 2 veremos las diferencias.

figura 2

La entrada CLK de todos los FF estn conectadas entre si de modo que la seal de entrada de reloj se aplica simultanemante a todos los FF. Solo el FF A, que es el LSB, tiene entradas J y K que estn permanentes en el nivel alto. Las entradas J y K de los dems FF son excitadas por alguna combinacin en las salidas de los propios FF. El contador sncrono requiere de mas circuiteria que un contador asncrono.

1.4. Operacin del circuito. El principio bsico de operacin del contador sncrono es el siguiente:

Las entradas J y K de los FF estn conectadas de forma tal que solo aquellos FF que se suponen cambiaran de estado en una determinada TPN tendr J = K =1 cuando se presente dicha TPN. A continuacin examinaremos cada principio de los FF con la ayuda de la secuencia de conteo que aparece en la figura 3.

figura 3 Esta secuencia de conteo muestra que el FF A tiene que cambiar de estado con cada TPN. Por esta razn sus entradas J y K permanecen siempre en alto para que el FF cambie de estado cada vez que se presenta una TPN en la seal de reloj. La secuencia de conteo seala que el FF B tiene que cambiar de estado con cada TPN mientras A = 1. Por ejemplo, cuando el conteo es 0001, la siguiente TPN tiene que cambiar a B hacia el estado 1; cuando el conteo es 0011, la siguiente TPN tiene que cambiar a B hacia el estado 0; y as sucesivamente. Esta operacin se logra conectando la salida A a las entradas J y K del FF B, para que J = K = 1 solo cuando A = 1. La secuencia de conteo indica que el FF C tiene que cambiar de estado con cada TPN que ocurre cuando A = B = 1. Por ejemplo cuando el conteo es 0011, la siguiente TPN tiene que cambiar el estado de C al estado de 1; cuando el conteo es 0111, la siguiente TPN tiene que cambiar el estado de C a 0; y as sucesivamente. Esta operacin esta garantizada si se conecta la seal AB a las entradas J y K de FF. De manera similar, se observa que el FF D, tiene que cambiar de estado con cada TPN que ocurre mientras A=B=C=1. Cuando el conteo es 0111, la siguiente TPN tiene que cambiar a D hacia el estado 1; cuando el conteo es 1111, la siguiente TPN cambiara a D hacia el estado 0. Esto se logra conectando la salida ABC a las entradas de FF D. 1.5. Ventajas de los contadores sncronos sobre los asncronos.

En un contador paralelo, todos los FF cambian de estado al mismo tiempo; es decir, todos estn sincronizados por las TPN de los pulsos de la seal del reloj. De este modo, a diferencia de los contadores asncronos, los retrasos de propagacin de los FF no se suman para producir un retraso global. En lugar de ello, el tiempo total de respuesta de un contador sncrono, con la figura 1, es igual al tiempo que le toma a uno de los FF cambiar de estado mas el tiempo necesario para que los nuevos niveles lgicos se propaguen a travs de una sola compuerta AND y enlace las entradas J y K. Esto es: Retraso total =t pd del FF+ t pd de la compuerta AND Ese retraso total es el mismo sin importar cuantos FF estn en el contador y generalmente ser mucho menor que el de un contador asncrono con el mismo nmero de FF. Por supuesto que el contador sncrono tiene una circuiteria ms compleja que el contador asncrono. 1.6. Contadores asncronos en CI. Existen varios contadores asncronos en CI, tanto TTL como CMOS. Uno de ellos es el TTL 74293 (74LS293, etc.). La figura 4 muestra el diagrama 16gico para el 74293 como aparece- ra en un libro de datos TTL del fabricante. Parte de la nomenclatura es diferente de la que se ha empleado hasta este momento, pero debe ser fcil averiguar lo que significa. Note los siguientes puntos: El 74293 tiene cuatro flip-flops J-K Con salidas Q0' Ql' Q2 y Q3, donde Qo Corresponde al LSB y Q4 al MSB. La distribucin de los FF es tal que el LSB se encuentra en el extremo izquierdo para satisfacer la convenci6n de que las seales de entrada al circuito aparezcan a la izquierda. Hemos dibujado loS contadores Con LSB a la derecha, para que la disposicin de los FF sea la misma que el orden de los bits en la cuenta binaria. Cada FF tiene una entrada CP (Pulso de reloj), que es slo otro nombre para la entrada CLK. Se puede tener acceso externo a las entradas de reloj para Q0 y Q1 marcadas Como CPo y CP1, respectivamente. Las barras de inversin sobre estas entradas indican que se activan por una TPN. Cada FF tiene una entrada asncrona BORRAR, CD. stas se encuentran conectadas entre s a la salida de una Compuerta NAND de dos entradas MR1 y MR2, donde MR denota reiniciaci6n maestra. Ambas entradas MR deben estar ALTAS para borrar el contador y ponerlo en 0000. Los flip-flops Ql, Q2, y Q3 ya estn conectados Como un contador de rizo de tres bits. El flip-flop Qo no est conectado internamente a nada. Esto permite que el usuario opte por Conectar Q0 a Ql para formar un contador de cuatro bits, o usar Q0 en forma separada, si as lo desea.

figura 4

1.7. Smbolo IEEE-ANSI para el contador 74293 La figura 5 muestra el smbolo IEEE/ ANSI para el 74293. Este smbolo contiene varios aspectos nuevos del estndar IEEE/ ANSI. A medida que los describimos, el lector comprender la forma en que est diseada la nueva simbologa IEEE/ ANSI para explicarnos la operacin de un CI. El smbolo contiene tres bloques distintos. El bloque de la parte superior (con las ranuras) es el bloque comn de control. La notacin "CTR" define este circuito integrado como un contador. Recuerde que en el captulo 5 mencionamos que el bloque de control comn se emplea cada vez que un CI tiene una o ms entradas comunes para ms de uno de los circuitos contenidos sobre el CI. Para e174293, las entradas MR1 y MR2 son comunes a todos los FF del contador . Estas entradas MR1 y MR2 se muestran como entradas activas en ALTO combinadas

internamente utilizando la operacin AND, la que est indicada por la notacin "&". Esto indica que MR1 y MR2 deben encontrarse al mismo tiempo en estado activo para restablecer el contador. La notacin "CT -O" indica que la accin de las entradas MR es hacer que la cuenta de salida sea igual a cero. El bloque de en medio est marcado con la etiqueta "DIV2" para sealar que ste es un contador MOD-2, el cual, claro est, es un solo FF. DIV2 significa que el contador dividir la

figura 5 1.8. EL CONTADOR 74193 (LS193/HC193)(Ascendente / descendente) La figura 6 muestra el smbolo l6gico y la descripci6n de entrada y salida del contador 74193. Este contador puede describirse como un contador ascendente / descendente prefijable MOD-16 con conteo sncrono, prefijable asncrono y reiniciaci6n maestra asncrona. observemos la funcin de cada entrada y salida,

figura 6 Entradas de reloj CPU y CPD. El contador responder a las TPP en una de las dos entra- das de reloj. CP u es la entrada de reloj de conteo ascendente. Cuando se apliquen los pulsos a esta entrada, el contador se incrementar (contar hacia arriba) en cada TPP hasta llegar a un conteo mximo de 1111 j entonces se recicla a 0000 y vuelve a comenzar. CPD es la entrada de reloj de conteo descendente. Cuando se apliquen los pulsos a esta entrada, el contador decrementar (contar hacia abajo) en cada TPP hasta llegar a un conteo mnimo de 0000; entonces se recicla a 1111 y vuelve a comenzar. De

este modo, se usar una entrada de reloj para contar en tanto que la otra est inactiva (se conserve en AL TO). Reiniciacin maestra (MR). Esta es una entrada asncrona activa en AL TO que reinicia al contador en el estado 0000. MR es un reiniciador de cd (corriente directa), de manera que mantendr al contador en 0000 en tanto que MR =1. Tambin elimina todas las otras entradas. Entradas prefijables. Los FF del contador pueden prestablecerse en los niveles 1ogicos presentes en las entradas paralelas de datos P3 hasta P0 pulsando momentneamente la entrada de carga paralela PL de AL TO a BAJO. Este es un prestablecimiento asncrono que elimina la operaci6n de conteo. No obstante, PL no tendr efecto si la entrada MR se encuentra en su estado activo en ALTO. Salidas del conteo. El conteo regular siempre est presente en las salidas Q3 hasta Qo de los FF, donde Q0 es el LSB y Q3 el MSB. Salidas finales del conteo. Estas salidas se utilizan cuando dos o ms unidades del 74193 se conectan como contador con etapas mltiples para producir un nmero MOD mayor. En el modo de conteo ascendente, la salida TCu del contador de orden inferior se conecta a la entrada CPu del siguiente contador de orden superior. En el modo de conteo descendente. la salida TCD del contador de orden inferior se conecta a la entrada CPD del siguiente contador de orden superior. TCu es el conteo ascendente final (tambin llamado acarreo). Se genera el chip 74193 utilizando la 1ogica que se muestra en la figura 7 (a). Evidentemente, TCu ser BAJO solo cuando el contador se encuentre en el estado 1111 y Cpu sea BAJO. As, TCu permanecer en AL TO cuando el contador cuente hacia arriba de 0000 a 1110. En la siguiente TPP de CP u' el conteo pasa a 1111, pero TCu no pasa a BAJO sino hasta que CPu retorna BAJO. La siguiente TPP en CPu recicla el contador a 0000 y tambin ocasiona que TCu retorne a ALTO. Esta TPP en TCu ocurre cuando el contador se recicla de 1111 a 0000, y se puede alimentar para cronometrar un segundo contador ascendente 74193 a su siguiente conteo superior. TCD es la salida del conteo descendente final (tambin llamado prstamo). Se genera como se muestra en la figura 7 (b). Normalmente es ALTO y no pasa a BAJO sino hasta que el contador haya contado hacia abajo hasta el estado 0000 y CPD sea BAJO. Cuando la siguiente TPP en CPD recicla el contador a 1111, ocasiona que TCD regrese a AL TO .Esta TPP en TC D se puede usar para cronometrar un segundo contador descendente 74193 en su siguiente conteo inferior.

figura 7 1.9. Mas acerca de la notacin de dependencia de IEEE/ANSI* Se puede aprender ms sobre la notaci6n de dependencia, que es una parte importante de la nueva simbologa IEEE/ ANSI, examinando el smbolo IEEE/ ANSI para el CI 74193 que se muestra en la figura 8. Cada tipo de CI que examinamos de esta forma, permitir al lector comprender mejor la nueva simbologa y le ayudar a prepararse para que en el futuro haga uso de ella. Una vez ms, debemos mencionar que el estndar IEEE/ ANSI solo especifica las etiquetas que se encuentran dentro de los rectngulos. Los nombres o etiquetas que se encuentran fuera de los contornos no son estndar, y de hecho, varan de un fabricante de CI a otro. Algunas de las notaciones empleadas en la figura 8 deben ser familiares. El smbolo delineado est dividido en un bloque comn de control que afecta a todos los FF y cuatro rectngulos pequeos que representan cada FF. El nmero entre corchetes que se encuentra dentro de cada rectngulo, denota su peso relativo en el contador. La etiqueta CTR DIV16 indica que este dispositivo, cuando opera normalmente, es un contador (CTR) con 16 estados (es decir, un contador que divide entre 16). L e entrada MR al bloque de control comn tiene la notacin CT = 0 para sealar que el contador ser reiniciado cuando MR sea ALTO.

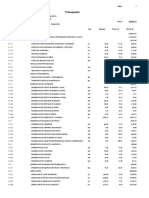

figura 8 Desarrollo Materiales

Software workbench Circuitmaket 1 C.I. 74293 (contador). Fuente de voltaje de 5v CD. 4 leds.

Circuito propuesto

Para esta practica se utilizara 1 circuitos contador asncrono en donde se utilizaran un tipo de integrados en el que en la salida del circuito se comprobara la tabla de verdad de este que se menciona anteriormente

Desarrollo de la prctica Para esta practica se realizara primero una simulacin del circuito anterior en el software workbench para as comprobar el comportamiento del contador ascendente asncrono, tambin se armara este circuito en una tarjeta de experimentacin donde se experimentara para as obtener los resultados de la tabla de verdad. Resultados A continuacin mostraremos una tabla donde se muestran los resultados obtenidos del circuito propuesto.

Conclusiones A travs de esta practica comprobamos que nuestros resultados obtenidos en el circuito propuesto contador ascendente asncrono son los mismos que en las tablas de verdad. Tambin es importante tener un diagrama de cada circuito para poder saber la forma que en el que se conectaran estas compuertas. As como que la resistencia que se utilice no sea demasiada grande sino el led no prendera. 12. Contador sncronos descendentes y ascendentes. Los contadores ascendentes / descendente (up/down) tambin llamados contadores bidireccionales; son capaces de avanzar en cualquier sentido a lo largo de una secuencia definida y puede invertir su conteo en cualquier punto de su secuencia. En el diagrama lgico se muestra un contador ascendente / descendente sncrono binario de tres bits diseado a partir de flip-flops J-K en configuracin toggle con disparo por borde de subida. Debido a que posee tres flip-flops, su ciclo bsico se compone de ocho estados que van desde cero (000) hasta siete (111) en forma secuencial y repetitiva.

13. Contadores con preestablecimiento. Muchos contadores sncronos(paralelo) que estn disponibles en CI estn diseados para ser prefijables; en otras palabras se pueden prefija r a cualquier valor inicial de conteo, ya sea en forma asncrona (independientemente de la seal de reloj) o sncrona ( durante la transicin activa de la seal de reloj) esta operacin de prefijado tambin se conoce como carga del contador. 14. Preestablecimiento sncrono. Muchos contadores sncronos paralelos de CI emplean el preestablecimiento sncrono con lo que el contador es prefijado durante la misma transicin activa de la seal de reloj que se emplea para el conteo. El nivel lgico aplicado en la entrada determina si transicin activa del reloj ser la que preestablesca el contador o si esta ser contada, como sucede durante el modo normal de operacin. 15. Decodificacin de un contador. Los contadores digitales se utilizan frecuentemente en aplicaciones donde deben determinarse o exhibirse de alguna manera el conteo representado por los estados de los flip-flops uno de los medios ms simples para exhibir el contenido de un contador consiste en conectar la salida de cada flip-flops a un diodo emisor de luz (LED). De esta manera, los estados de los flip-flops estn representados por los led en forma visible ( encendido = 1, apagado = 0) y el conteo se puede determinar mentalmente al decodificador los estados binarios de los LED . Por ejemplo, suponga que este mtodo se ocupa para un contador BCD y los estados de las lmparas son apagado- encendido -encendido-apagado, respectivamente.esto representara l numero binario 0110, que decodificaramos mentalmente como el 6 decimal. Otras combinaciones de estados de los LED representaran los posibles conteos.

El mtodo de LED indicador no es conveniente cuando aumenta el tamao ( numero de BIT) del contador, porque es muy difcil decodificar mentalmente los resultados. Por esto es conveniente desarrollar un medio que decodifique electrnicamente el contenido del contador y mostrar los resultados de inmediato y que no requiera operaciones mentales 16. Descodificacin activa en ALTO Un contador MOD-X tiene x diferentes estados, cada uno es modelo en particular de ceros y unos almacenados en los flip-flops del contador. Este sistema es un circuito lgico que genera x diferentes salidas, las cuales detectan ciertos estados del contador. Las salidas del decodificador pueden disearse para introducir un nivel alto o uno bajo cuando ocurra la deteccin. Un decodificador activo alto genera salidas altas para indicar deteccin. En la figura que veremos a continuacin muestra la lgica completa de descodificacin activa para un contador MOD-8. este cuenta de 8 compuertas and de 3 entradas, las cuales producen salidas altas para un estado en particular del contador. Por ejemplo, la compuerta and 0 tiene como entradas las salidas del flip-flops C, B y A. As su salida ser baja en todos los tiempos, excepto cuando A =B=C=0, es decir en el conteo 000. anlogamente, la compuerta and 5 tiene como entradas las salidas del flipflops C,B y A, donde su salida pasara a alto solo cuando C = 1, B = 0 y A = 1; es decir, en el conteo de 101 ( 5 decimal ) . el resto de las compuertas and se comportan de la misma forma para los otros posibles conteos. En cualquier instante, solamente una compuerta de la salida and es alta, la que se decodifica para la cuenta en particular esta presente en el contador. Las formas de onda de la figura lo muestran claramente. Las 8 salidas de and se pueden utilizar para controlar 8 indicadores LED por separado, lo que representa los nmeros decimales del 0 al 7. solo la lmpara estar indicando el conteo adecuado

17. Descodificacin activa en bajo Si se emplean compuertas nand en lugar de and, las salidas detectoras producirn una seal alta, la que pasa abajo solo cuando ocurre l numero que se decodifica. Se utilizan ambos tipos de decodificadores, dependiendo del tipo de circuitos que sean conducidos por las salidas detectoras 18. Descodificacin del contador BCD. Este tiene 10 estados y se pueden decodificar usando las tcnicas anteriores. Estos decodificadores ofrecen 10 salidas que corresponden a los dgitos del 0 al 9 representados por los estados de los flip-flops del contador. Las 10 salidas se pueden usar para controlar 10 indicadores elctricos LED y tener una exhibicin visual. Con mayor frecuencia en vez de utilizar 10 lmparas por separado, se utiliza un solo dispositivo para ver los nmeros del 0 al 9, este se denomina tubo nixie, contiene 10 filamentos muy delgados que son la forma de cada uno de los nmeros. El decodificador BCD controla que filamento esta encendido. Una clase ms nueva de dispositivo decimales de exhibicin visual contiene 7 pequeos segmentos hechos de un material (por lo general dispositivo de cristal liquido o LED ) que emite luz o reflejan la del medio ambiente. Las salidas del BCD controlan que segmentos estn encendidos para producir un patrn que represente uno de los dgitos decimales. 20. Decodificaciones de salidas falsas. Los retrasos entre las transiciones de los flip-flops pueden as mismo ocasionar problemas cuando se decodifica un contador de rizos. El problema se presenta en la forma de transiciones falsas( glitches) o espigas en las salidas de algunas de las compuertas de decodificacin. Esto se ilustra en la siguiente figura para un contador de rizos MOD 4. Las formas de ondas presentes en las salidas de cada flip-flops y compuertas de decodificacin se muestran en la figura. Note el retraso de propagacin que ocurre en las formas de onda de reloj y la salida A y entre las formas de onda A y B. Las transiciones falsas que ocurren en las formas de onda de decodificacin X0 y X2 son ocasionadas por el retraso entre las formas de onda A y B. X0 es la salida de la decodificacin de la compuerta and para l conteo normal 00. La condicin 00 tambin ocurre momentneamente cuando el contador pasa del conteo 01 al 10 como lo demuestra la forma de onda. Esto se debe a que B no cambia de estado sino hasta que A pasa a bajo. Este estado momentneo 00 solo dura algunos nano segundos pero puede ser detectado por la compuerta de decodificacin si la respuesta de la compuerta es lo suficientemente rpida, por ello la espiga en la salida X0. Una situacin anloga produce una transicin falsa en la salida X2. X2 es la decodificacin para la condicin 10 y ocurre momentneamente en el instante en que el contador pasa de 11 a 00 en respuesta al cuarto pulso de reloj, como se muestra en la forma de onda. Una ves ms esto se debe al retraso de la respuesta del flip-flops B depuse de que A a pasado a bajo.

21. Des habilitacin estroboscpica. Esta tcnica emplea una seal llamada seal estroboscpica para mantener deshabilitadas las compuertas and de decodificacin ( salidas en cero), hasta que todos los flip-flops hallan alcanzado un estado estable en respuesta a la transicin negativa del reloj, esto se ilustra en la figura donde la seal estroboscpica se conecta como entrada a cada una de las compuertas de descodificacin. Las formas de onda correspondiente muestran que la seal estroboscpica pasa a bajo cuando el pulso del reloj pasa a alto. Durante el tiempo en que la seal estroboscpica esta en bajo, las compuertas de decodificacin se conservan en bajo. La seal estroboscpica se mantiene en bajo. La seal estroboscpica se va a alto para habilitar las compuertas de decodificacin algn tiempo despus de que el pulso de reloj se fue a bajo. El mtodo estroboscpico no se emplea si un contador solamente se utiliza con fines de exhibicin visual, ya que las espigas en la decodificacin son demasiado angostas para afectar la exhibicin

22. Conexin en cascada de contadores BCD Los contadores BCD se utilizan siempre que se vayan a contar pulsos y los resultados se exhiban en forma decimal. Un solo contador BCD puede contar de 0 a 9 y luego regresa a 0.

Para contar nmeros decimales mayores, podemos conectar los BCD en forma de cascada como lo ilustrar la figura esta configuracin opera como sigue: Inicialmente todos los contadores son iniciados en el estado cero. As la exhibicin decimal es 0000. Cuando llegan los pulsos de entrada el contador BCD avanza un conteo por pulso, despus de que han ocurrido 9 pulsos los contadores BCD de centenas y decenas siguen todava en cero y el contador de unidades esta en nueve( 1001 binario). De este modo la exhibicin decimal se lee 0009. En el dcimo pulso de entrada el contador de las entradas se recicla a cero, ocasionando que las salidas que las salidas del flip-flops D vaya de 1 a 0, esta transicin de 1 a 0 acta como la entrada de reloj para el contador de las decenas y ocasiona que avanc un conteo. As despus de 10 pulsos de entrada, la lectura decimal es 010. Cuando ocurren otros pulsos adicionales, el contador avanza un conteo por pulso y cada vez que el contador de unidades se recicla a 0 el contador de las decenas avanza 1 conteo. De este modo despus de que han ocurrido 99 pulsos de entrada, el contador de las decenas esta en 9, al igual que el de las unidades. As la lectura decimales 099. En el pulso 100 de entrada, el contador de las unidades se recicla a 0, que a su ves ocasiona que el contador de las decenas se recicle a 0. as las salidas del flip-flops D del contador de las decenas realiza una transicin de 1 a 0 que acta como entrada de reloj para el contador de las centenas y ocasiona que avanc un conteo as despus de 100 pulsos la lectura decimal es 100. Este proceso continua hasta 999 pulsos. En el pulso 1000 todos los contadores se reciclan a 0.

23. Diseo de contadores sncronos. Existen varios mtodos para disear contadores que sigan secuencias arbitrarias, ahora presentaremos los detalles de un mtodo que utiliza flip-flops J K conectados en configuracin de contador sncrono la tcnica es uno de los numerosos procedimientos de diseo que forma parte de una rea del diseo de circuitos digitales que se llama diseo de circuitos secuenciales. Idea bsica:

En los contadores sncronos todos los flip-flops son disparado al mismo tiempo antes de cada pulso de reloj, las entradas J y K de cada flip-flops del contador deben tener el nivel correcto para asegurar que cada flip flop cambie Asia el estado correcto. El proceso de disear un contador sncrono se convierte en uno en que se disea los circuitos lgicos que decodifican los diferentes estados del contador, para proporcionar los niveles lgicos en cada entrada J y K. Las entradas de estos circuitos decodificadores provienen de las salidas de uno o varios flip-flops. Tabla de excitacin J- K. La columna del extremo izquierdo de la tabla enumera las posibles transiciones en la salida de un flip-flops. La segunda y tercera columna contiene el estado presente, simbolizado como Q ( N ) y el siguiente estado simbolizado como Q ( N+1), para cada transicin las ultimas dos columnas contienen los niveles J y K requeridos para producir cada transicin a continuacin examinamos cada caso. Transicin 0=> 0 el estado presente del flip-flops es cero y debe permanecer en cero cuando se aplica una entrada de reloj, de esta manera de entender como funciona un flipflops J- K, esto sucede cuando J=K=0 ( condicin de no cambio), o cuando J=0 y K = 1 (condicin de borrado). De este modo J tiene que ser 0, pero K puede tener cualquier nivel. La tabla indica esto con un 0 en la columna correspondiente a J y una x en la columna para K. Recuerde que x representa una condicin no importa. Transicin 0 =>1 este estado presente es 0 y cambia a 1, esto puede suceder ya sea cuando J=1 y K= 0 ( condicin de establecimiento) o cuando J =K = 1 (condicin de cambio de estado). De este modo J tiene que ser 1, pero para que esta transicin ocurra K puede tener cualquier nivel. Transicin de 1=>0, el estado presente es 1 y debe cambar a 0. esto puede ocurrir cuando J = 0 y K = 1 o J=K=1. De este modo K tiene que ser 1 pero J puede estar en cualquiera de estos niveles. Transicin 1=>1, el estado presente es 1 y permanecer en 1. esto ocurre cuando J=K=0 o J=1 y K = 0 as, K debe ser cero mientras J puede estar en cualquiera de estos niveles. Transicin en la salida 0=>0 0=>1 1=>0 1=>1 Estado presente Estado siguiente J Q(N) 0 0 1 1 Q(N+1) 0 1 0 1 0 1 X x K X X 1 0

24. Contadores con registro de corrimiento Contador de anillo: El contador de corrimiento ms simple es un registro de corrimiento circulante conectado de modo que el ultimo flip-flops desplace su valor al primer flipflops.

Esta configuracin se muestra en la figura utilizando flip-flops de tipo D (tambin se puede usar flip-flops de tipo J K). Estos se conectan d tal forma que la informacin se corra de izquierda a derecha, y de regreso de Q0 a Q3. En mucho casos solo hay un 1 en el registro y se hace que circule alrededor del registro en tanto se apliquen los pulsos del reloj. Por esta razn se le denomina contador de anillo. Las formas de onda la tabla de secuencia y el diagrama de estados muestran los diferentes estados del flip-flops a medida que se aplica los pulsos, suponiendo que el estado inicial es Q3 =1 y Q2 = Q1 =Q0 = 0. despus del primer pulso, el 1 a pasado de Q3 a Q2 de manera que el contador esta en el estado 0100. el segundo pulso produce el estado 0010, y el tercero produce el estado 0001. el cuarto pulso del reloj el estado 1 de Q0 se transfiere a Q3 lo que produce el estado 1000, que es desde luego el estado inicial. Los pulsos subsiguientes ocasionan que se repita la secuencia. Este contador funciona como un contador MOD 4 por que tiene 4 estados distintos antes de que se repita la secuencia. Note que cada forma de onda de salida del flip-flops tiene una frecuencia igual a un cuarto de la frecuencia de reloj. Un contador de anillo necesitara ms flip-flops que un contador binario para el mismo numero MOD, por ejemplo un contador de anillo MOD 8 requiere de 8 flip-flops en tanto que un contador binario MOD 8 solo necesita 3. A pesar de que es menos eficaz en el uso del flip-flops un contador de anillos sigue siendo til debido a que puede ser decodificado sin tiene que emplear compuertas de decodificacin. La seal de decodificacin para cada estado se obtiene en la salida de sus flip-flops correspondientes. Nota : los diagramas corresponden a un contador MOD 3.

25. Contador Johnson. Aparte de los contadores binarios que pasan por todos sus posibles estados y de los de secuencia truncada, en los cuales el nmero mximo de posibles estados es 2n, donde n corresponde al nmero de flip-flops, existen contadores que tengan un nmero de estados determinado por la regla 2n, donde n es el nmero de flip-flops. Adems estos contadores poseen una realimentacin de la salida complementaria de la ltima etapa independiente del nmero de etapas del contador, a la entrada del primer flip-flop, dando como resultado una secuencia caracterstica. En el diagrama lgico se muestra un contador de Johnson ascendente de tres bits diseado a partir de flip-flops Data con disparo por borde de subida. Debido a que posee tres flipflops, su nmero mximo de estados es 6, con un ciclo bsico que va desde cero (000) luego el contador se llenar de 1s de izquierda a derecha y luego se llenara de nuevo de 0s en forma repetitiva como se puede observar en el diagrama de tiempos.

. .

Conclusin.

Con el desarrollo de este trabajo se trato de explicar lo ms simplemente posible todas las aplicaciones de los contadores, donde se puede saber como son los nmeros MOD donde se designa la cantidad de flip-flops que se deben utilizar. Tambin la forma de onda se disminuye a la mitad de la frecuencia de entrada en cada salida del flip-flop. Otra forma es disminuir la cantidad de numero 2N mediante compuertas nand. Los contadores de dcadas que son todos aquellos que tiene 10 estados. Los contadores descendentes que son capaces de medir desde un numero mximo a un mnimo. Los flip flops paralelos que tienen la capacidad de contar en forma simultanea. Los ascendentes y descendentes tienen la capacidad de contar en ambos sentidos. Los contadores con preestablecimiento a estos se les puede fijar cualquier valor inicial de conteo. La conexin en cascada BCD es la conexin en forma que la informacin que se utiliza para el segundo flip-flops es sacada del primer, y del tercero del segundo y as sucesivamente. Esto se hace por que los BCD solo cuentan de 0 a 9, y para valores mayores se conectan en cascada. Los distintos tipos de contadores como los de anillo y Jonson.

Das könnte Ihnen auch gefallen

- Diagrama Logico de Un Contador 74193Dokument11 SeitenDiagrama Logico de Un Contador 74193Jose Gonzalez DonosoNoch keine Bewertungen

- Introducción a los contadores digitales síncronos y asíncronosDokument14 SeitenIntroducción a los contadores digitales síncronos y asíncronosAlee AlejandroNoch keine Bewertungen

- U6 Diseño LógicoDokument31 SeitenU6 Diseño LógicoluisNoch keine Bewertungen

- Exposicion CircuitosDokument24 SeitenExposicion CircuitosYamil Solis DiazNoch keine Bewertungen

- INTRODUCCIÓNDokument3 SeitenINTRODUCCIÓNKelvin HernandezNoch keine Bewertungen

- Contadores SíncronosDokument9 SeitenContadores SíncronosAndersson VacaNoch keine Bewertungen

- Contadores SíncronosDokument7 SeitenContadores SíncronosCristian Ochoa AriasNoch keine Bewertungen

- Comparador DigitalDokument6 SeitenComparador DigitalRommel GalminNoch keine Bewertungen

- Contadores SíncronosDokument9 SeitenContadores SíncronosanderssonNoch keine Bewertungen

- CorrimientoDokument11 SeitenCorrimientoEdgar AragonNoch keine Bewertungen

- ElctronicaDokument12 SeitenElctronicaPaulo Barrios RodriguezNoch keine Bewertungen

- Clase 10 - Tema 4 - Dispositivos Secuenciales y Contadores 2021-2Dokument6 SeitenClase 10 - Tema 4 - Dispositivos Secuenciales y Contadores 2021-2PlutonioNoch keine Bewertungen

- Contador Sincrónico Resumen Unidad 3Dokument2 SeitenContador Sincrónico Resumen Unidad 3Harold Cuevas PablusNoch keine Bewertungen

- Contadores y Registros InformeDokument22 SeitenContadores y Registros Informecristhianarevalo2001Noch keine Bewertungen

- Practica 7 Contadores BinariosDokument9 SeitenPractica 7 Contadores BinariosTorrealba GerardoNoch keine Bewertungen

- Contadores Asincronos y SincronosDokument30 SeitenContadores Asincronos y SincronosYamil Solis Diaz100% (3)

- Clase Registros Cuarta Parte 2020Dokument45 SeitenClase Registros Cuarta Parte 2020Unknowia MadnessNoch keine Bewertungen

- Contadores AsincronosDokument17 SeitenContadores AsincronosRonald Reyes100% (1)

- DIseño de COntadoresDokument17 SeitenDIseño de COntadoresCristinaNoch keine Bewertungen

- Contadores síncronos (paralelosDokument11 SeitenContadores síncronos (paralelosWilliams Molina EspirituNoch keine Bewertungen

- Tabla de Verdad de Pic Contador BinarioDokument14 SeitenTabla de Verdad de Pic Contador BinariojaviertdzoNoch keine Bewertungen

- Contadores síncronos: ventajas y funcionamientoDokument4 SeitenContadores síncronos: ventajas y funcionamientoRenato SaavedraNoch keine Bewertungen

- Pre Informe 4Dokument8 SeitenPre Informe 4Quicaño PradoNoch keine Bewertungen

- Diseño de ContadoresDokument20 SeitenDiseño de ContadoresDereck LeivaNoch keine Bewertungen

- Pre Informe de ContadoresDokument33 SeitenPre Informe de ContadoresHenrySolórzanoMartelNoch keine Bewertungen

- Contadores y MemoriasDokument26 SeitenContadores y MemoriasHector ValdiviaNoch keine Bewertungen

- Sid Ard Sem10Dokument11 SeitenSid Ard Sem10Arturo ReyesNoch keine Bewertungen

- Contador BCD síncrono de décadasDokument3 SeitenContador BCD síncrono de décadasYese CMNoch keine Bewertungen

- Contadores y Registros 2.0Dokument24 SeitenContadores y Registros 2.0Paul Tineo ChNoch keine Bewertungen

- Flip-Flops D2Dokument13 SeitenFlip-Flops D2Kenzo YCNoch keine Bewertungen

- Ejemplos Practicos de L CapDokument8 SeitenEjemplos Practicos de L Capmiguel ramosNoch keine Bewertungen

- Registro DesplazamientosDokument6 SeitenRegistro DesplazamientosElvis Paucar SocasiNoch keine Bewertungen

- Contadores Anillo Jhonson D-ADokument5 SeitenContadores Anillo Jhonson D-AArtur Faby Jimenez BonillaNoch keine Bewertungen

- Contadores Síncronos y AsincronosDokument9 SeitenContadores Síncronos y AsincronosDani GuerreroNoch keine Bewertungen

- Contadores SincronosDokument3 SeitenContadores SincronosMarijoc100% (1)

- Contadores y registros digitales: tipos y aplicacionesDokument6 SeitenContadores y registros digitales: tipos y aplicacionesAlexander MarcoNoch keine Bewertungen

- Registros, Contadores y MemoriaDokument31 SeitenRegistros, Contadores y MemoriaJorge Parra100% (1)

- Informe de Circuitos Logicos (Contadores) 4Dokument18 SeitenInforme de Circuitos Logicos (Contadores) 4Louis Charles86% (7)

- Sistemas I 8Dokument12 SeitenSistemas I 8Sergio Escobar MendozaNoch keine Bewertungen

- Pre Informe Lab - 5 Sistemas DigitalesDokument10 SeitenPre Informe Lab - 5 Sistemas DigitalesJosue Mendoza RuedaNoch keine Bewertungen

- Capitulo 5 - Circuitos SecuencialesDokument14 SeitenCapitulo 5 - Circuitos Secuencialesgeorge_rivera_26Noch keine Bewertungen

- Inicio de ContadoresDokument3 SeitenInicio de ContadoresErick BarretoNoch keine Bewertungen

- Informe 11 DigitalesDokument10 SeitenInforme 11 DigitalesedisontatayovNoch keine Bewertungen

- Curso de Inglés BBC English 01Dokument8 SeitenCurso de Inglés BBC English 01Luis Fernando LizarazoNoch keine Bewertungen

- Trabajo de ContadoresDokument24 SeitenTrabajo de ContadoresAbraham VergaraNoch keine Bewertungen

- Práctica 8Dokument8 SeitenPráctica 8Vicente IriarteNoch keine Bewertungen

- Tema A 3Dokument4 SeitenTema A 3Nacho RomanelloNoch keine Bewertungen

- 74193Dokument10 Seiten74193Dyalma PerezNoch keine Bewertungen

- ContadoresDokument11 SeitenContadoresDan GoldmannNoch keine Bewertungen

- Contador 0 A 7Dokument6 SeitenContador 0 A 7JUAN PABLO VARGASNoch keine Bewertungen

- Contando Con CircuitosDokument12 SeitenContando Con CircuitosPablo Mamani SuycoNoch keine Bewertungen

- Practica Contador Binario NuevoDokument9 SeitenPractica Contador Binario NuevoRominAgNoch keine Bewertungen

- Contador Binario de 4 y 8 BitsDokument7 SeitenContador Binario de 4 y 8 BitsAlan VazquezNoch keine Bewertungen

- El Contador en AnilloDokument14 SeitenEl Contador en AnilloJosé GuachoNoch keine Bewertungen

- Contadores en ParaleloDokument3 SeitenContadores en Paralelojsuarez_12380Noch keine Bewertungen

- Contador en AnilloDokument1 SeiteContador en AnilloIddar Olivares MoralesNoch keine Bewertungen

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiVon EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiBewertung: 5 von 5 Sternen5/5 (1)

- 100 Circuitos de Shields para MotoresVon Everand100 Circuitos de Shields para MotoresBewertung: 4.5 von 5 Sternen4.5/5 (4)

- Ensayo SociologiaDokument4 SeitenEnsayo SociologiaLouis CharlesNoch keine Bewertungen

- Estadistica Paso 4Dokument20 SeitenEstadistica Paso 4Louis Charles100% (2)

- Solucion - de - Guia 3 y 4Dokument15 SeitenSolucion - de - Guia 3 y 4Louis CharlesNoch keine Bewertungen

- Actividad Complementaria U1Dokument38 SeitenActividad Complementaria U1Louis Charles80% (5)

- INFORME DE PASANTÍAS REALIZADAS EN LA GOBERNACIÓN DE SUCRE - UltimateDokument87 SeitenINFORME DE PASANTÍAS REALIZADAS EN LA GOBERNACIÓN DE SUCRE - UltimateLouis CharlesNoch keine Bewertungen

- Act Complementarias U2Dokument12 SeitenAct Complementarias U2Louis Charles20% (5)

- SuperStack II Hub ™ 10Dokument16 SeitenSuperStack II Hub ™ 10Louis CharlesNoch keine Bewertungen

- Estadistica Paso 4Dokument20 SeitenEstadistica Paso 4Louis Charles100% (2)

- INFORME DE PASANTìAS REALIZADAS EN LA GOBERNACIoN DE SUCRE - Ultimate PDFDokument82 SeitenINFORME DE PASANTìAS REALIZADAS EN LA GOBERNACIoN DE SUCRE - Ultimate PDFLouis Charles100% (1)

- El Modelo OsiDokument9 SeitenEl Modelo OsiLouis CharlesNoch keine Bewertungen

- CentralDokument6 SeitenCentralLouis Charles100% (1)

- Complement AriaDokument17 SeitenComplement AriaLouis CharlesNoch keine Bewertungen

- Act Central U2Dokument9 SeitenAct Central U2Louis Charles83% (6)

- Actividad Central U1Dokument12 SeitenActividad Central U1Louis CharlesNoch keine Bewertungen

- Actividad 3Dokument9 SeitenActividad 3Louis CharlesNoch keine Bewertungen

- Algoritmo Ac4Dokument2 SeitenAlgoritmo Ac4Louis CharlesNoch keine Bewertungen

- Actividad 4Dokument5 SeitenActividad 4Louis CharlesNoch keine Bewertungen

- El ComputadorDokument3 SeitenEl ComputadorLouis CharlesNoch keine Bewertungen

- Actividad 2Dokument6 SeitenActividad 2Louis CharlesNoch keine Bewertungen

- GSMDokument10 SeitenGSMLouis CharlesNoch keine Bewertungen

- Implementación de Un Latch RSDokument17 SeitenImplementación de Un Latch RSLouis CharlesNoch keine Bewertungen

- Mantenimiento PreventivoDokument6 SeitenMantenimiento PreventivoLouis CharlesNoch keine Bewertungen

- Flip FlopsDokument6 SeitenFlip Flopsmono28Noch keine Bewertungen

- Informe de Circuitos Logicos (Contadores) 4Dokument18 SeitenInforme de Circuitos Logicos (Contadores) 4Louis Charles86% (7)

- Guía ZENERDokument6 SeitenGuía ZENERLouis CharlesNoch keine Bewertungen

- Contador Asincrono DecendenteDokument7 SeitenContador Asincrono DecendenteLouis CharlesNoch keine Bewertungen

- Informe de Circuitos Logico 1Dokument9 SeitenInforme de Circuitos Logico 1Louis CharlesNoch keine Bewertungen

- Flip Flop InformeDokument14 SeitenFlip Flop InformeLouis Charles100% (3)

- Control ConvertidoresDokument7 SeitenControl ConvertidoresLouis CharlesNoch keine Bewertungen

- CIRUITOS LOGICOS - InformeDokument16 SeitenCIRUITOS LOGICOS - InformeLouis CharlesNoch keine Bewertungen

- Tipos de MicrofonoDokument1 SeiteTipos de MicrofonoJaime Mompeán SánchezNoch keine Bewertungen

- Matriz de Impacto Ambiental EjemploDokument4 SeitenMatriz de Impacto Ambiental EjemploBetsayRzNoch keine Bewertungen

- SuspensiónDokument6 SeitenSuspensiónQuantyk Knight Punk SkNoch keine Bewertungen

- Micro y ManotecnologiaDokument2 SeitenMicro y ManotecnologiaJairo JairNoch keine Bewertungen

- Suelo ChacarillaDokument18 SeitenSuelo ChacarillaLigia HinojosaNoch keine Bewertungen

- Manual de EMovDokument25 SeitenManual de EMovalexander_osorio_1Noch keine Bewertungen

- Revista de Mineria PDFDokument76 SeitenRevista de Mineria PDFWilfredo Escobar100% (1)

- Catalogo Motores WEG Con DimensionesDokument10 SeitenCatalogo Motores WEG Con DimensionesCarlos Diaz100% (1)

- Origen de la termodinámica: calor y fuerzaDokument5 SeitenOrigen de la termodinámica: calor y fuerzaEliana Ocampo BNoch keine Bewertungen

- Memoria Descriptiva ScotiabankDokument8 SeitenMemoria Descriptiva ScotiabankchanchituNoch keine Bewertungen

- Pregunta de Ewxamen de Licencia de Conducir Nro 11Dokument12 SeitenPregunta de Ewxamen de Licencia de Conducir Nro 11Melvin Molina100% (1)

- Estabilidad de taludes minerosDokument20 SeitenEstabilidad de taludes minerosCardenas YhorNoch keine Bewertungen

- Taller 4 Trabajo y EnergíaDokument5 SeitenTaller 4 Trabajo y EnergíaJuldor ReiranNoch keine Bewertungen

- Base de Datos Frann.......Dokument36 SeitenBase de Datos Frann.......Frann HRNoch keine Bewertungen

- Carbonato de Calcio Práctica de LaboratorioDokument7 SeitenCarbonato de Calcio Práctica de LaboratorioJose PerezNoch keine Bewertungen

- Primer Informe de Mecanica de SuelosDokument19 SeitenPrimer Informe de Mecanica de SuelosJ Reynaldo Chambi100% (1)

- SKC S Product Data Sheet EspanolDokument2 SeitenSKC S Product Data Sheet EspanolCarlos CárdenasNoch keine Bewertungen

- HORNODokument5 SeitenHORNOFarit MoscosoNoch keine Bewertungen

- 76 - Ing. Padron - Geotecnia Presupuesto CeibosDokument1 Seite76 - Ing. Padron - Geotecnia Presupuesto CeibosfranNoch keine Bewertungen

- Diseño de Una Seccion Hueca CADokument19 SeitenDiseño de Una Seccion Hueca CAJhonChoqueBustinzaNoch keine Bewertungen

- Presupuesto Estructuras Hosp - TarapotoDokument4 SeitenPresupuesto Estructuras Hosp - TarapotoDiegoCastilloNoch keine Bewertungen

- Graben de EspinoDokument18 SeitenGraben de EspinoNoelNoch keine Bewertungen

- Diseño de Puente de 30 M de LuzDokument28 SeitenDiseño de Puente de 30 M de LuzHenry Hoyos100% (1)

- Los-Numeros-Romanos - Miércoles 20 de JulioDokument3 SeitenLos-Numeros-Romanos - Miércoles 20 de JulioMARCIA ANTONIETA IBARRA GANOZANoch keine Bewertungen

- Asme B30.2-2005Dokument45 SeitenAsme B30.2-2005alexanderNoch keine Bewertungen

- Construccion DL Ponton KM 1217+000 y Accesos Volumen VI PDFDokument88 SeitenConstruccion DL Ponton KM 1217+000 y Accesos Volumen VI PDFTeresa Rivera VilchezNoch keine Bewertungen

- Historia Del VehiculoDokument3 SeitenHistoria Del VehiculocarlosNoch keine Bewertungen

- Consumible de SoldaduraDokument6 SeitenConsumible de SoldaduraLuis GarciaNoch keine Bewertungen

- Análisis de transferencia de calor por convección y radiación en láminas metálicasDokument20 SeitenAnálisis de transferencia de calor por convección y radiación en láminas metálicasJoseAlejandroSeguraGalvisNoch keine Bewertungen