Beruflich Dokumente

Kultur Dokumente

Flancter App Note

Hochgeladen von

bigdogguruOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Flancter App Note

Hochgeladen von

bigdogguruCopyright:

Verfügbare Formate

July 2000 Application Note: The "Flancter" by Rob Weinstein

How To Set a Status Flag in One Clock Domain, Clear It in Another, and Never, Ever Have to Use an Asynchronous Clear for Anything but Reset

Overview

There are times when it is important to generate a status flag that is set by an event in one clock domain and reset by an event in a different clock domain. Using a D-type flip-flop where a is clocked in from one clock domain, and its 1 asynchronous reset is pulsed by logic in the second clock domain is the timehonored method to achieve this function. While there is nothing logically wrong with this, it introduces other problems such as combinational logic driving an asynchronous reset pin, uncertainty in timing constraint boundaries, and muddying the global reset function. Here I present an alternative method for generating a multiple clock domain flag register that mitigates these problems. It called the s Flancter(named by my colleague, Mark Long), and is shown in Figure 1. As you can see, it is made up of two D-type flip-flops, an inverter, and an

FF1

SET_CE SET_CLK

D Q CE CLR

Q1

OUT

FF2

RESET_CE RESET_CLK

D Q CE CLR

Q2

Figure 1 - Basic Flancter. exclusive OR (XOR) gate. Notice that the asynchronous reset inputs to the flipflops are shown unconnected for clarity only. Normally, these would be tied to the global set/reset net in the system. Operation of the Flancter is simple; when FF1 is clocked (rising edge of SET_CLK while SET_CE is asserted), OUT goes high. Contrariwise, when FF2 is clocked (rising edge of RESET_CLK while RESET_CE is asserted), OUT goes low. Note that this circuit must be used in an interlocked system where the flip-

Page 1 of 11

Application Note

The Flancter

flops won be continuously clocked by the two clock domains. Also, the output t must be synchronized with additional flip-flops to mitigate metastability when crossing clock domains (more about this later).

How It Works

To explain its operation, I like to rearrange the circuit as shown in Figure 2.

RESET_CE RESET_CLK

Q1 D Q CE D Q CE CLR CLR FF1 FF2

OUT

Q2

SET_CE SET_CLK

Figure 2 - Rearranged Flancter. This is exactly the same circuit as shown in Figure 1, but untwisted so that the two inputs to the XOR gate are clearly visible. You can see that the XOR gate s upper input is labeled Q1, while its lower input is labeled Q2. Also, Q1 and Q2 are the Q outputs of FF1 and FF2, respectively. Now for the trick part of this magic trick: the D input to FF1 comes from an inverter, so whenever FF1 is clocked, Q1 assumes the opposite state of Q2 and the output of the XOR gate will go high. When FF2 is clocked, Q2 becomes the same as Q1, and the output will go low. In summary, clocking FF1 causes OUT to go high and clocking FF2 causes OUT to go low. A timing diagram will help describe the Flancter operation. Figure 3 shows the s basic timing diagram:

Page 2 of 11

Application Note

The Flancter

SET_CLK SET_CE Q1 A C

RESET_CLK RESET_CE Q2 B OUT D

Figure 3 - Basic Flancter Timing. The basic points of interest in the timing diagram are: SET_CLK and RESET_CLK are asynchronous to each other. At point A, the rising edge of SET_CLK while SET_CE is high causes Q1 to go high because it gets the inverted value of Q2. Also, OUT goes high because it is the XOR of Q1 and Q2. At point B, the rising edge of RESET_CLK while RESET_CE is high causes Q2 to go high because it gets the value of Q1. Also, OUT goes low because it is the XOR of Q1 and Q2. At point C, Q1 again gets the inverted value of Q2, causing OUT to go high. At point D, Q2 goes low because it gets the value of Q1, causing OUT to go low.

So What Wrong With It? s

There are a few things wrong with the Flancter from the start. One problem is that it uses two flip-flops to create a single flag bit. This is a minor fault when you consider that most FPGAs have an abundant supply of flip-flops. A more serious issue is how to use the output. Remember that the output can change synchronously to either clock domain. You need to resynchronize the output to whichever clock domain needs to see it; often both clock domains. It is common to use two flip-flops in series as a metastability-resistant synchronizer. However, the most serious drawback to the Flancter is that operating the set and reset flip-flops must be mutually exclusive in time. This means that when logic in clock domain 1 sets the Flancter, it doesn attempt to set the Flancter again until t it sees that it has been reset. Likewise, the logic in clock domain 2 never attempts to reset the Flancter unless it sees that it has been set. Establishing this kind of interlocked protocol guarantees that both of the Flancter flip-flops won s t be clocked simultaneously (or within each other setup and hold time windows). s

Page 3 of 11

Application Note

The Flancter

Applications of the Flancter

There are many applications of the Flancter, but a very common application is interfacing a microprocessor to an FPGA. Typically, the microprocessor and FPGA logic run on separate clocks. When the microprocessor writes a control register within the FPGA, the Flancter can be used as a status flag to tell an internal state machine that new data is available. Likewise, a state machine within the FPGA can use the Flancter to generate an interrupt to the microprocessor that is subsequently cleared by a read or interrupt-acknowledge cycle from the microprocessor, as shown in Figure 4.

Part of FPGA

FF4 FF3

Q4

Q3

SYSCLK

D SYSCLK

CLR Control Inputs

CLR

FF1 SYSCLK State Machine SET_CE SYSCLK D Q CE CLR

Q1

SYSCLK Domain INT

uP Clock Domain

FF2 D Q CE CLR

Q2

uP

RD_L

RESET_CE

Address Decode

ADDRESS

PCLK

Figure 4 - Flancter Used for Microprocessor Interrupt.

Page 4 of 11

Application Note

The Flancter

Things to notice in Figure 4: The Flancter is made up of FF1, FF2, the inverter, and the XOR gate. The state machine, FF1, FF3, and FF4 are all synchronous to SYSCLK. The microprocessor (uP) runs off its own clock, PCLK. The state machine pulses SET_CE for one SYSCLK cycle when it needs to request an interrupt. The microprocessor performs a read cycle from a predefined address to reset the interrupt. Although not shown, reading from this address may also cause a status register to be driven onto the microprocessor data bus allowing s simultaneous reading of status and resetting of interrupt. FF3 and FF4 are resynchronizing flip-flops used to filter any metastable logic conditions from propagating into the state machine. The particular microprocessor used in this example employs metastable resistant techniques on its INT input. The interrupt sequence is defined such that setting and resetting the interrupt flag cannot occur simultaneously. The following timing diagram helps illustrate the operation:

SYSCLK SET_CE Q1 A

RD_L ADDRESS RESET_CE Q2 B INT Status Address

Figure 5 - Flancter Interrupt Timing Diagram. Things to notice in Figure 5: The FPGA state machine sets the interrupt request (INT) at point A. s Sometime later, the microprocessor responds to the interrupt by reading a status register, thus resetting the interrupt request at point B.

Page 5 of 11

Application Note

The Flancter

HDL Examples

Verilog Example

//--------------------------------------------------------------------// FileName : flancter.v // Author : Rob Weinstein // -------------------------------------------------------------------module flancter ( // Inputs ASYNC_RESET, SET_CLK, SET_CE, RESET_CLK, RESET_CE, // Outputs FLAG_OUT ) ; input input input input input output ASYNC_RESET; SET_CLK; SET_CE; RESET_CLK; RESET_CE; FLAG_OUT;

// Internal Registers reg SetFlop; reg RstFlop; // Output assignments assign FLAG_OUT = SetFlop ^ RstFlop ; // The Set flip-flop always @(posedge SET_CLK or posedge ASYNC_RESET) begin : set_proc if (ASYNC_RESET) SetFlop <= 0; else if (SET_CE) SetFlop <= ~RstFlop; // Flops get opposite logic levels. end // The Reset flip-flop always @(posedge RESET_CL K or posedge ASYNC_RESET) begin : reset_proc if (ASYNC_RESET) RstFlop <= 0; else if (RESET_CE) RstFlop <= SetFlop; // Flops get the same logic levels. end endmodule

Page 6 of 11

Application Note

The Flancter

VHDL Example

------------------------------------------------------------------ ------ FileName : flancter.vhd -- Author : Rob Weinstein ----------------------------------------------------------------------library IEEE; use IEEE.std_logic_1164.all; entity flancter is port ( ASYNC_RESET SET_CLK SET_CE RESET_CLK RESET_CE FLAG_OUT ); end flancter;

: : : : : :

in in in in in out

std_logic; std_logic; std_logic; std_logic; std_logic; std_logic

architecture flancter of flancter is signal SetFlop : std_logic; signal RstFlop : std_logic; begin --The Set flip-flop set_proc:process(ASYNC_RESET, SET_CLK) begin if ASYNC_RESET = '1' then SetFlop <= '0'; elsif rising_edge(SET_CLK) then if SET_CE = '1' then -- Flops get opposite logic levels. SetFlop <= not RstFlop; end if; end if; end process; --The Reset flip-flop reset_proc:process(ASYNC_RESET, RESET_CLK) begin if ASYNC_RESET = '1' then RstFlop <= '0'; elsif rising_edge(RESET_CLK) then if RESET_CE = '1' then -- Flops get the same logic levels. RstFlop <= SetFlop; end if; end if; end process; FLAG_OUT <= SetFlop xor RstFlop; end flancter;

Page 7 of 11

Application Note

The Flancter

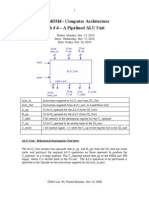

Synthesis Result The Verilog example was run through Synplify and the resulting HDL Analyst RTL view is shown in Figure below:

SET_CLK SET_CE RESET_CE 0 1 D Q R 1 0 D Q R FLAG_OUT

reset_proc_RstFlop_5 RstFlop

RESET_CLK ASYNC_RESET

set_proc_SetFlop_5 SetFlop

FLAG_OUT

Figure 6 - Synthesized Flancter. Note that in the RTL view, clock-enabled flip-flops are shown as multiplexers in front of D-type flip-flops.

Variations on a Flancter

While the basic Flancter is very simple, many useful variations are possible. I describe some of the more interesting variations below. Flancter Variation #1 One interesting variation lets you use a Flancter in lieu of a D-type flip-flop whose async clear input is used to save a clock cycle. In some single-clock-domain systems, the original designer relied on an async clear to immediately reset a flip-flop so that it would be reset by the next rising clock edge. A variation of a Flancter can give you the same functionality without relying on an async clear input. Figure 7 shows this variation:

FF1 SET_CE D Q CE CLR OUT CLK FF2 RESET_CE D Q CE CLR Falling Edge Triggered Q2 Q1

Figure 7 - Flancter Variation #1.

Page 8 of 11

Application Note

The Flancter

Note that this is the same as the Basic Flancter, but it uses a single clock input, CLK, and the reset flip-flop is clocked on the falling edge of that clock. Its operation is depicted in th timing diagram in Figure 8: e

CLK SET_CE Q1

RESET_CE Q2

OUT

Figure 8 - Flancter Timing for Variation #1. Things to notice in Figure 8: OUT goes high on the rising edge of CLK at point A in response to SET_CE. Sometime later, RESET_CE is pulsed for one CLK cycle, synchronous to the rising edge of CLK, but OUT responds to RESET_CE by going low on thefalling edge of CLK at point B. OUT is already low by the next rising edge of CLK at point C. If a synchronous reset had been used, OUT would still be high at point C. Flancter Variation #2 Another variation on the Flancter is to have OUT come up high after global reset. This is easily achieved by making sure that either FF1 or FF2 (but not both) uses an async preset instead of an async clear. Figure 9 shows wh I mean: at

Page 9 of 11

Application Note

The Flancter

SET_CE SET_CLK

FF1 PRE D Q CE

Q1

OUT

FF2 RESET_CE RESET_CLK D Q CE CLR Q2

Figure 9 - Flancter Variation #2.

Flancter Variation #3 This variation operates in three different clock domains.

FF1 SET_CE SET_CLK Q2 Q3 D Q CE CLR Q1

FF2 RESET1_CE RESET1_CLK Q1 Q3 D Q CE CLR Q2 OUT

FF3 RESET2_CE RESET2_CLK Q1 Q2 D Q CE CLR Q3

Figure 10 - 3-Way Flancter. The particular configuration shown inFigure 10 is set by one clock domain and reset by either of two other clock domains. Note that the flip -flop connected to the setting domain, FF1, has an inverter on its D input, while the flip -flops connected to the resetting domains, FF2 and FF3, do not. This variation works equally well with two setting domains and one resetting domain. The rule is to use inverters on the flip-flops in the setting domains and no inverters on the flip -flops in the

Page 10 of 11

Application Note

The Flancter

resetting domains. The inputs to the XO gates are simply the Q outputs of all R the registers except the one we are driving. For instance, the D input of FF1 uses the XOR of Q2 and Q3. Note that Q1 is not used in the input function to FF1. Likewise, FF2 is based on Q1 and Q3, but not Q2 and FF3is based on Q1 and Q2, but not Q3. A Flancter variation can be built with any number of setting and resetting clock domains; this is an n-way Flancter. The rules for building an n -way Flancter are: Use n flip-flops, one for each clock domain (FF1...FFn). The output of the n-way Flancter is simply the XOR of all of the Q outputs. The D input to any particular flip -flop (call it FFm), is the logical XOR of the Q outputs of all the flip-flops except the one we are driving (Q1 Qn except Qm). An inverter is inserted at the D inputs of a flip -flop based on whether that particular flip-flop is used for setting or resetting the n -way Flancter. Use inverters for setting flip-flops or no inverters for resetting flip -flops. Designing a protocol in which only one flip -flop is clocked at a time is the biggest problem with the n -way Flancter. Remember, the Flancter is only reliable when the flip -flops are never clocked simultaneously.

Summary

I turned 37 this year and I got to thinking that all the greatsdid their best work long before they reached my age. As I look back on my design career, I realize that I haven designed any circuits or developed any theorems that will bear my t name like the Pierce Oscillator or Shannon Sampling Theorem. The best I can s do is to offer the Flancter as my legacy. Perhaps someday, the Weinstein Flancter will be found in the indexes of engineering tomes right between Watt Hour and Wien-Bridge.

Page 11 of 11

Das könnte Ihnen auch gefallen

- Part 1 - FSM DesignDokument3 SeitenPart 1 - FSM DesignMENANI ZineddineNoch keine Bewertungen

- Report Clock Tree and Report Clock TimingDokument8 SeitenReport Clock Tree and Report Clock TimingDharma PangaNoch keine Bewertungen

- Activity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFDokument5 SeitenActivity 3.1.1 Sequential Logic - D Flip-Flops and JK Flip-Flops PDFChris Ronald CherestalNoch keine Bewertungen

- DigSilent TechRef - RecloserDokument17 SeitenDigSilent TechRef - RecloserАлишер ГалиевNoch keine Bewertungen

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosVon EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosBewertung: 5 von 5 Sternen5/5 (1)

- PIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Dokument16 SeitenPIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Ashim KumarNoch keine Bewertungen

- Chapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)Dokument6 SeitenChapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)amitpatel1991Noch keine Bewertungen

- Lab 04Dokument6 SeitenLab 04Bodour MohamedNoch keine Bewertungen

- ECET 105 Week 7 Lab Project Detailed DirectionsDokument14 SeitenECET 105 Week 7 Lab Project Detailed DirectionsMicro EmissionNoch keine Bewertungen

- Over Current ProctectionDokument25 SeitenOver Current ProctectionSarah FrazierNoch keine Bewertungen

- DLD Ch5Dokument55 SeitenDLD Ch5aboodNoch keine Bewertungen

- Pic Microcontroller: Technological University of The PhilippinesDokument15 SeitenPic Microcontroller: Technological University of The PhilippinesRonnel Joseph Cooper Renedo100% (1)

- BER MeterDokument8 SeitenBER Metersakti prasad nandaNoch keine Bewertungen

- Demystifying Resets Synchronous Asynchronous Other Design Considerations Part 1Dokument7 SeitenDemystifying Resets Synchronous Asynchronous Other Design Considerations Part 1alexNoch keine Bewertungen

- Lab 4 - Finite State Machines: GoalsDokument7 SeitenLab 4 - Finite State Machines: GoalsJoey WangNoch keine Bewertungen

- Asynchronous FIFODokument21 SeitenAsynchronous FIFOMarium Mazhar50% (2)

- Name of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabDokument7 SeitenName of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabAurongo NasirNoch keine Bewertungen

- EC 303 Chapter 2Dokument48 SeitenEC 303 Chapter 2PrevenaManiamNoch keine Bewertungen

- DSD Lab 9 HandoutDokument5 SeitenDSD Lab 9 HandoutFaiza Tabassam 546-FET/BSEE/F19Noch keine Bewertungen

- App of CFC Logic in Intel DevicesDokument14 SeitenApp of CFC Logic in Intel Devicesiwan.satyaNoch keine Bewertungen

- Ic 693 Cpu 313Dokument5 SeitenIc 693 Cpu 313mubashersaeedNoch keine Bewertungen

- Interrupt and ReturnDokument75 SeitenInterrupt and ReturnAlex PérezNoch keine Bewertungen

- Design and Implementation of Synchronous 4-Bit Up Counter Using 180Nm Cmos Process TechnologyDokument6 SeitenDesign and Implementation of Synchronous 4-Bit Up Counter Using 180Nm Cmos Process TechnologyreyysummerNoch keine Bewertungen

- Latticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Dokument28 SeitenLatticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Krishnakumar SomanpillaiNoch keine Bewertungen

- Latch and Flip-FlopDokument58 SeitenLatch and Flip-FlopDalila Nadia RazaliNoch keine Bewertungen

- Lect17 SeqDokument18 SeitenLect17 SeqorengeneralNoch keine Bewertungen

- VCLASS-2 M5 Perc Sintetik-28102020Dokument10 SeitenVCLASS-2 M5 Perc Sintetik-28102020Fatah Nur HidayatNoch keine Bewertungen

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitDokument8 SeitenECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilNoch keine Bewertungen

- uPF1 Monitor Program Listing (Original Scan)Dokument59 SeitenuPF1 Monitor Program Listing (Original Scan)Jose Luis Abasolo MayorNoch keine Bewertungen

- Digital Electronics Module 05Dokument44 SeitenDigital Electronics Module 05Yadana1Noch keine Bewertungen

- Step Replace Module Flexi BSC NokiaDokument19 SeitenStep Replace Module Flexi BSC Nokiarudibenget0% (1)

- LABDCT 2002 (Guide) Nexus.5020.Lab - GuideDokument52 SeitenLABDCT 2002 (Guide) Nexus.5020.Lab - Guidekds20850Noch keine Bewertungen

- 512 ManualDokument77 Seiten512 ManualHamada AlmasalmaNoch keine Bewertungen

- DSD Lab 9 HandoutDokument5 SeitenDSD Lab 9 HandoutMuhammad AnasNoch keine Bewertungen

- MSP Devie ErratasheetDokument8 SeitenMSP Devie ErratasheetmaanviNoch keine Bewertungen

- PIC16F628A ExperimentosDokument11 SeitenPIC16F628A ExperimentosCesar Matos100% (2)

- Sequential CircuitsDokument22 SeitenSequential CircuitsBaeNoch keine Bewertungen

- SN1-2223-Lab3 1-2 EngDokument4 SeitenSN1-2223-Lab3 1-2 EngBoualem MestafaNoch keine Bewertungen

- Search For DocumentsDokument9 SeitenSearch For DocumentsdineshvhavalNoch keine Bewertungen

- Lab 1Dokument8 SeitenLab 1Mulugeta AbebawNoch keine Bewertungen

- Gated Clock ConversionDokument8 SeitenGated Clock ConversionKillivalavan KaliyamoorthyNoch keine Bewertungen

- DVP Ss ManualDokument459 SeitenDVP Ss ManualjoaokalatecNoch keine Bewertungen

- Grupo 23 - Tarea 4Dokument23 SeitenGrupo 23 - Tarea 4alexis pedrozaNoch keine Bewertungen

- Experiment 9 Sequential Circuits Introduction To CountersDokument3 SeitenExperiment 9 Sequential Circuits Introduction To CountersKeshav MusunuriNoch keine Bewertungen

- Mod 5Dokument83 SeitenMod 5Jane BillonesNoch keine Bewertungen

- 555 GreenpackDokument17 Seiten555 GreenpackRuboto BotoNoch keine Bewertungen

- VWV FinalyDokument11 SeitenVWV FinalyYogesh PolNoch keine Bewertungen

- The Flancter DoulosDokument2 SeitenThe Flancter DoulosMiguel BrunoNoch keine Bewertungen

- Equations and Impacts of Setup and Hold Time: SkewDokument5 SeitenEquations and Impacts of Setup and Hold Time: SkewVardhan KarnatiNoch keine Bewertungen

- Equations and Impacts of Setup and Hold TimeDokument5 SeitenEquations and Impacts of Setup and Hold Timepavithra reddyNoch keine Bewertungen

- Clock PowerDokument8 SeitenClock PowerSathish BalaNoch keine Bewertungen

- Family Questions A Swers: Zao CRCDokument27 SeitenFamily Questions A Swers: Zao CRCfrankNoch keine Bewertungen

- Equations and Impacts of Setup and Hold TimeDokument5 SeitenEquations and Impacts of Setup and Hold TimeShravan Kumar AshannagariNoch keine Bewertungen

- Clock Optimization Techniques For Abutted Channelless Floorplanning MethodologiesDokument5 SeitenClock Optimization Techniques For Abutted Channelless Floorplanning MethodologiesBaluvu JagadishNoch keine Bewertungen

- TIMER Radovan RabrenovicDokument15 SeitenTIMER Radovan RabrenovicRadovan RabrenovicNoch keine Bewertungen

- A3 1 1IntroductionFlipFlopsDokument5 SeitenA3 1 1IntroductionFlipFlopsGoran MateiaseviciNoch keine Bewertungen

- MG4 HD4Dokument9 SeitenMG4 HD4VIJAYPUTRANoch keine Bewertungen

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksVon EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNoch keine Bewertungen

- Krell KST-100 Owners ManualDokument16 SeitenKrell KST-100 Owners ManualbigdogguruNoch keine Bewertungen

- Crystals: VCXO Voltage Controlled Crystal Oscillator R SeriesDokument2 SeitenCrystals: VCXO Voltage Controlled Crystal Oscillator R SeriesbigdogguruNoch keine Bewertungen

- Spru889 - High Speed DSP Systems DesignDokument77 SeitenSpru889 - High Speed DSP Systems DesignAriana Ribeiro LameirinhasNoch keine Bewertungen

- AUBTM-22 AT CommandsDokument36 SeitenAUBTM-22 AT Commandscris_sabrinaNoch keine Bewertungen

- Palazzoli ProductDokument468 SeitenPalazzoli ProductDeppi AdinataNoch keine Bewertungen

- UF4001 UF4007: 1.0 Amp High Efficiency RectifiersDokument2 SeitenUF4001 UF4007: 1.0 Amp High Efficiency RectifiersYonathan LopezNoch keine Bewertungen

- Samsung TFT-LCD Monitor Sync Master 732N, 732N Plus, 932B, 932B Plus, 932N Chassis LS17PEA LS19PEA LS19PEBDokument83 SeitenSamsung TFT-LCD Monitor Sync Master 732N, 732N Plus, 932B, 932B Plus, 932N Chassis LS17PEA LS19PEA LS19PEBIrian Pinheiro Pinheiro0% (1)

- Transducers - GTU DiplomaDokument27 SeitenTransducers - GTU Diplomandm.jhdpNoch keine Bewertungen

- Digital Indicating Controller Sdc30: DigitronikDokument12 SeitenDigital Indicating Controller Sdc30: DigitronikAkurato Tunas MandiriNoch keine Bewertungen

- V150-4.0 - 4.2MW DECS - AppendixCDokument7 SeitenV150-4.0 - 4.2MW DECS - AppendixCLưu SơnNoch keine Bewertungen

- Transformer Company CVDokument1 SeiteTransformer Company CVAnup Kumar JangidNoch keine Bewertungen

- Dokumen - Tips - Upto 145kv 40ka 3150a Operating Manual 56327f822540fDokument64 SeitenDokumen - Tips - Upto 145kv 40ka 3150a Operating Manual 56327f822540fSerik ZhilkamanovNoch keine Bewertungen

- Sepam 1000 (Relevador Multifuncional Schneider)Dokument198 SeitenSepam 1000 (Relevador Multifuncional Schneider)cande garciaNoch keine Bewertungen

- HUBER+SUHNER ENVIROFLEX 316 D DatasheetDokument2 SeitenHUBER+SUHNER ENVIROFLEX 316 D DatasheetFemi OketokiNoch keine Bewertungen

- Complete Overview of Lightning Arrester 3Dokument9 SeitenComplete Overview of Lightning Arrester 3VENKATESAN RNoch keine Bewertungen

- 7.arteche Combined HV - Ka72Dokument8 Seiten7.arteche Combined HV - Ka72Luis Blas100% (1)

- Im Trox Compact Controller EasyDokument8 SeitenIm Trox Compact Controller EasymichelesmiderleNoch keine Bewertungen

- 22CSP-102 - Workshop Technology Lab ManualDokument63 Seiten22CSP-102 - Workshop Technology Lab ManualMehal KumarNoch keine Bewertungen

- Bench Type Digital Multimeter: DescriptionDokument1 SeiteBench Type Digital Multimeter: DescriptionManuel RochaNoch keine Bewertungen

- Ic-A25 A25e Im PRT 1Dokument24 SeitenIc-A25 A25e Im PRT 1Reijean Alexfer Dos Santos SantosNoch keine Bewertungen

- Fts 10 BDokument18 SeitenFts 10 BMunaf HossainNoch keine Bewertungen

- 2019 NERC-NATF-EPRI Power System Modeling Workshop Presentations PDFDokument434 Seiten2019 NERC-NATF-EPRI Power System Modeling Workshop Presentations PDFJose ValdiviesoNoch keine Bewertungen

- 43.1 Description of Flash Code 43: Ddec Iii/Iv Single Ecm Troubleshooting GuideDokument4 Seiten43.1 Description of Flash Code 43: Ddec Iii/Iv Single Ecm Troubleshooting GuideMarco Antonio Rubiano GómezNoch keine Bewertungen

- Time Switch - Weekly (Wall Mount) TS1W1-1-20A: FeaturesDokument2 SeitenTime Switch - Weekly (Wall Mount) TS1W1-1-20A: Featureschandv7Noch keine Bewertungen

- TX-28/25/21MD4 Service ManualDokument36 SeitenTX-28/25/21MD4 Service ManualIpko SalimNoch keine Bewertungen

- CircuitiKz ManualDokument62 SeitenCircuitiKz ManualnospherathusNoch keine Bewertungen

- Title: Storage DevicesDokument3 SeitenTitle: Storage DevicesBiju PoudelNoch keine Bewertungen

- Revolving Field TheoryDokument1 SeiteRevolving Field TheorySudipto PramanikNoch keine Bewertungen

- Huggins, 2002. Simple Method To Determine Electronic and Ionic ComponentsDokument14 SeitenHuggins, 2002. Simple Method To Determine Electronic and Ionic ComponentsSol AngelNoch keine Bewertungen

- Schematich Acer - E5-473 - A4WAB - LA-C341P - r10Dokument57 SeitenSchematich Acer - E5-473 - A4WAB - LA-C341P - r10Double Helix100% (1)

- SYH Industria Ethernet Networking Manual 76Dokument607 SeitenSYH Industria Ethernet Networking Manual 76fabianbritez8489100% (2)

- Nri Institute of Technology: Department of Electronics & Communication EngineeringDokument7 SeitenNri Institute of Technology: Department of Electronics & Communication EngineeringDr. P. Rama Koteswara RaoNoch keine Bewertungen

- FHMA 1 FHMA SIMU MergedDokument3 SeitenFHMA 1 FHMA SIMU Mergedakashkumarswain213Noch keine Bewertungen

- CPC100 Manual PDFDokument32 SeitenCPC100 Manual PDFAnonymous wx4I4YQONoch keine Bewertungen