Beruflich Dokumente

Kultur Dokumente

Chapter 3 - Combinational Logic Circuits (Part 1) - Digital Electronics

Hochgeladen von

Rakesh KumarOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Chapter 3 - Combinational Logic Circuits (Part 1) - Digital Electronics

Hochgeladen von

Rakesh KumarCopyright:

Verfügbare Formate

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

Digital Electronics

R c mme d 25 eo n .k

Press Ctrl & '+' To enlarge text and pics!

Chapters

Home Topics Chapter 1 : Number System and Binary Code (Part 1) Chapter 1 : Part 2 Chapter 2 : Minimization of Logic Function (Part 1) Chapter 2 : Part 2 Chapter 3 : Combinational Logic Circuits (Part 1) Chapter 3 : Part 2 Chapter 4 : Sequential Circuits (Part 1) Chapter 4 : Part 2 Chapter 5 : D/A and A/D Converters (Part 1) Chapter 5 : Part 2 Chapter 6 : Semiconductor Memories Chapter 7 : Logic Families

Home

Chapter 3 : Combinational Logic Circuits (Part 1)

Remember These:

C mbn t n l i ut a ea d r s br co smut lx r d mut lx r ma ntd o iai a c c i r d e s u ta tr o r s lpe e s e lpe e , g i e i i u c mp r tr p r yg n r trc e k r t. o a ao , a i e e ao /h c e ec t A i mei c c i a eu e fr d io , u ta t nmut l aindvs n r h t i ut r s d o a dt n s br ci t c r s i o lpi t i c o ii o i H la d r su e fr d io o t bn r n mb r. af d e i s d o a dt n f wo ia y u e s i F la d r su e t p r r a dt no mo eta r bt ul d e i s d o e f m d io f r h r2 i o i s S r l d e r q i o efla d r o o ea dt n l i whl p r l l d e sr q i sN e i a d r e ur n ul d e fr n d io a bt i a al a d r e ur a e i e e e fla d r fr bt d io . ul d e s o n ia dt n i T mo ea d r a elo a e dc rya d r n B D a d r wo r d es r o k h a ar d e a d C d e. H l s br co s br cs t n mb r we g t2 o tu v r be ie df r n e a d af u ta tr u ta t wo u e s e up t a i ls a ie e c n f b ro orw F ls br co i s br cino 3bt. ul u ta tr s u ta t o f i s E c d r o v rsh ma ln u g it ma hn ln u g . n o e c n e t u n a g a e no c ie a g a e D c d r su e t c n e t c ieln u g t h ma ln u g . e o e i s d o o v r ma hn a g a e o u n a g a e Mut lx r a eu ie s l i ut whc s lcso eip t u o mut l ip t a dgv lpe e s r nv ra c c i i r s i ee t n n u o t f lpe n us n ie h i ia ar s l t s e ut D mut lx r e ev sifr t no s gel ea ddsr uet te2l e wh r n e lpe e r c ie no mai n i l i n i i t o h i o n n tb i s ee n a es lcinl e . r ee t o i s n Ma ntd c mp r tr su e t c mp r 2bn r n mb r g i e o a ao i s d o o a e ia y u e s u C d c n e tr a e to e whc c n e t a gv n c d t s me oh rc d E a ls o e o v re s r h s i o v rs h ie o e o o te o e x mpe ae r: ( ) r yt Bn r c d c n e tr a G a o ia y o e o v re ( ) ia yt G a c d c n e tr b Bn r o r y o e o v re () ia yt E c s 3c d c n e tr t. c Bn r o x e s o e o v re ec P r yg n r tr salgcc c iwhc g n r tstep r ybt fr v no o dp r y a i e e ao i o i i ut i e e ae h a i i o e e r d a i t r h t s t P r yg n r tr su e a teta s t r a i e e ao i s d t h r n mi e . t t P r yc e k r su e a ter c ie . a i h c e i s d t h e ev r t B D ds ly d iei b s al te B D t s v n s g n ds lyc d c n e trI ti C i a r p v s a i l h C o e e e me t i a o e o v re n hs c y p bn r c d dd c lsds ly do tes v ns g n ds ly ia y o e e i ma i i a e n h e e e me t i a s p p

Q 1. List the applications of decoders. Ans. D c d r a eu e i c u tr y tms 1 e o e s r s d n o ne s se 2 D c d r a eu e fr / c n e s n . e o e s r s d o A D o v ri . o 3D c d r a eu e fr / c n e s n e o e s r s d o D A o v ri o 4 D c d r a eu e i s v ns g n dgtl i ly . . e o e s r s d n e e e me t ii ds a s a p

ptuece.loremate.com/die/node/3 1/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

Q 2 Give functional block diagram of 2 1 MUX Ans.

Q 3 Explain half subtractor with the help of its internal circuit Ans. T s br c t n mb r i t I p t a ibe Aa dB weg t woo tu v r bei o u ta t wo u e s e wo n u v r ls n a et up t a i l a edf r n e n b ro o I i k o a h ls br co F n t n l ig a i s o : ie e c D a d o r w B ts n wn s af u ta tr u ci a da r m s h wn f o

Its truth table is as shown:

T u , h mii z dlgcfn t n a e h s te nmi e o i u ci s r : o

T ec c ida r m i a s o : h i ut ig a s s h wn r

Q 4. Implement half adder circuit using 4 : 1 MUX or multiplexers only. Ans. T uhtbeo h la d r sa s o : r t a l f af d e i s h wn

ptuece.loremate.com/die/node/3

2/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

Q 5. Implement using 4: 1 MUX Ans. T ei lme tt ntbei a s o : h mpe nai a l s s h wn o

Implementation:

Q 6. Design 3 bit Gray Code to binary converters Ans. T etuhtbefr bt r yC d t bn r c n e s ni a s o : h r t a l o 3 iG a o e o ia y o v ri s s h wn o

K-Maps: For 82:

For B1:

ptuece.loremate.com/die/node/3

3/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

For Bo:

Crut mpe naini a s o : i iI lme tt c o s s h wn

Q 7. Design BCD to Excess-3 code converter. Ans. BCD to Excess-3 Code Converter: T eip t a ibe a eB D s( , , a dD a do tu v r be a ee c s- c d ( 3 h n u v r ls r C A B C n ) n up t a i ls r x e s3 o e E , a a E , 1a dE ) 2E n 0

Truth Table

Atr 9 i . 0 1B D ma kd nt a ei .X. f . 1 0 C , r o c r . e e e Mii z t nU igK ma : nmi i ao s n - p Fr 3 oE

E = A+ B + B 3 D S

ptuece.loremate.com/die/node/3 4/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

Fr 2 oE

Fr 1 oE

Fr 0 oE

Implementation of Excess-3 Code Converter:

Q 8. Draw the logic circuit for the expression Ans.

ptuece.loremate.com/die/node/3

5/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

L gcc c ir p e e tt n o i i ut e r s nai . r o

Q 9 Draw the logic circuit for 3 line to 8 line decoder Ans. 3l et 8l ed c d r i utsa s o : i o i e o e c c ii s h wn n n r

I h str eip tie i . , a dC a dh seg t up tie t a he n u l s . A B n n e n a ih o tu l s n i . 0 D , 2 D , 4 D , 6a dD . D, 1D, 3D, 5D n 7 e

Q 10 Draw the logic circuit for the expression Ans Logic Circuit:

Q 11. Give significance of priority encoder. Ans. P ir ye c d r nas e ily eo e c d r I h sp ir isgv nt teip tie r i no e i ot p c tp f n o e . t a r ie ie o h n u l s a ot n f m hg e tp ir yip tl et lwe tp ir yip t ie I t o mo eip tl e a e r o ih s r i n u i o o s r i n u l , f wo r r n u i s r ot n ot n n a t e i . rhg a te s me t ,te te ip tl e wi hg e tp ir y wi b ci . 1 o ih t h a v e i me h n h n u i n t ih s r i h ot l e l c n ie e f s. o s rd i t d r

Q 12. How many select lines are there for a 30 to 1 MUX? Ans. F r 0 1MU , s lc l e a er q i d 4s lc l e a efr 6: MU a d o 3: X 5 ee ti s r e ur . ee ti s r o 1 1 n e n Xs n

ptuece.loremate.com/die/node/3 6/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

1s lc l efr2 1MU . ee t i o : n X

= M fr l i u e . e en= n mb r f ee tie a dM o mua s s d Wh r u e o s lc l s n n

a eten mb r fn usfr MU . r h u e o ip t o a X = 3 .h s 5s lc l e a en e e . 2T u , ee ti s r e d d n

Q 13. What are the various type of parity checkers and where do we use them? Ans. a i c e k r a eu e a ter c ie p r. h yc e ktep r yo ter c ie P r y h c e s r s d t h e ev r a t T e h c h a i f h e ev d t t wo da dp o u e i o tu. r a l p r yc e k r a eo t tp s r n r d c s t up t B o dy a i h c e s r f wo y e . s t ( O dp r yc e k r i d ai h c e ) t () v np r yc e k r i E e ai h c e. i t

Q 14. Design full subtractor using NAND gates. Ans. ul u ta tr su e t s br c tr ebt a dg n r t df r n ea db ro F ls br co i s d o u ta t h e i n e e ae ie e c n o r w. s f T uh tbeo fls br co i r t-a l ful u ta tr s :

Q 15. Construct 16-bit comparator using 4-bit comparator as a building block. Ans. bt o a ao I i 7 8 . 4 ic mp r tr C n 4 5 I i u e fr 6bt o a ao . ts s d o 1 ic mp r tr T u , I a eu e , i i a s o : h s 4 CS r s d whc s s h wn h

ptuece.loremate.com/die/node/3

7/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

Q 16. How can a DEMUX be used as a decoder? Ans. T es lcinl e o teD MU c nb u e a ip tie o d c d r n ite h ee t o i s fh E X a e s d s n u l s f e o e a d fh n n d t ip t f h d mut lx r su e a tee a l ip t f h d c d rte wec nu e aa n u o te e lpe e i s d s h n be n u o te e o e h n i a s ted mut lx r sad c d r h e lpe e a i e o e. Q 17. What is a parity checker? Ans. P r yc e k r salgcc c ita c e k tep r ybn r wo d Ap r ybtsa a i h c e i o i i ut h t h c s h a i ia y r . a i ii n t r t t a dt n l iwhc i a d dt abn r wo di o d rt ma eten mb ro o esi te d io a bt i s d e o i h ia y r n r e o k h u e f n n h n w wo dfr t se e fr v np r ya do dfr d p r y e r o ma a v n o e e a i n d o o d a i . t t Q 18. Obtain the truth table for a combinational circuit that accepts a three bit number and generates an output binary number equal to the square of the input number. Ans. T uhtbei a s o fr n usa dtec re p n igs u r o tus r t a l s s h wn o ip t n h o r s o dn q a e up t.

Q 19. Implement using 4 x 1 MUX

Ans.

ptuece.loremate.com/die/node/3

8/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

Q 20 Describe the operations performed by an encoder and a decoder. Ans. Operations Performed by Encoder: 1 E c d ri a c mbn t n l i utwhc e c d so e dgtln u c d t te dgtl no e s o iai a c c i o r i n o e n ii ip t o e o h m ii h a a o tu c d l eo tlobn r e c d r e i loB D e c d r t up t o e i ca t ia y n o e D c k ma t C n o e ec 2I p o ie tes c r yfr h d t b e c dn i t r vd s h e u i o te aa y n o ig t t 3I s v steb n wit o e tec a n l t a e h a d dh v r h h n es Operations Performed by Decoder 1Ad c d ri ac mbn t n l i ut ta c n e t nip t ia yifr t nt 2o tu e o e s o iai a c c i h t o v rs n u bn r no mai o o r , o up t l e eg2t 4l ed c d r t 8l ed c d r t i s n o i e o e 3 o i e o e ec n n 2I i u e a ter c ie p r t d c d teifr t n ts s d t h e ev r a t o e o e h no mai o Q 21. Implement the following function using 3 to 8 decoder

Ans. I lme tt nu ig3t 8d c d r mpe nai s o n o e o e:

Q 22 Define a demultiplexer Show how to convert a decoder into a demultiplexer indicate how to add a strobe to this system OR What is demultiplexer Explain the difference between DMIJX and MUX Ans. Demultiplexer:D mut lx ri ad vc whc h ss geip t iea d ma yi e lpe e s i ei e i a i l nu l h n n n n e o tu l e T e r lt no s e ico tu l ei c nr l db tev leo n s lcin up t i s h eai f p c i up t i s o tol y h au f ee t n o f n e o l e I p r r teiv reo e aino mut lx r i s t e f ms h n e s p r t n o o f lpe e i I c s o d c d r ih snip tie a d u iu o tu l e L t stk a e a l o n a e f e o e ,t a nu l s n n nq e up ti s e u a e n x mpe f n 2t 4l ed c d r oc n e t h d c d r noad mut lx r o i e o e t o v r te e o e it n e lpe e . i 2t 4l eD c d r o i n e o e:

ptuece.loremate.com/die/node/3

9/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

I c nb c n e tdit d mut lx riD i d t I p t iei c n e tdt al h A D t a e o v re no e lpe e f 1 e aa n u l s o v re o lte N i n g tss l n o s . ae i t e u l mu a y S r k s n lsas a d dt alh A D g tss l n o s a s o i f . to e i a i l d e o lte N ae i t e u l s h wn n i g o mu a y g

S r b s n lss lrt e a l s n lo c i s lcin I i a a t elw s n lI hg to e i a i i a o n be i a fr hp ee t . t s n ci o i a. f ih g mi g o v g s n lsa pid t sr k tec i wi b ds beb c u ei 0g e t al h A D g ts i ai pl g e o to e h hp l e i l e a s = l a o s o lte N ae A dwer c ien o tu a D , 1 D a dD n e ev o up t t 0 D , 2 n 3 Difference between DMUX and MUX:

Q 23 Design a Gray-to Excess-3 Code converter using NAND gates Ans. G a t E c s3c d c n e tr r y o x e s o e o v re :

K-maps for Excess 3-codes are

ptuece.loremate.com/die/node/3

10/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

Circuit Diagram:

Q 24. Design a 3-bit carry-look-ahead adder. Ans. 3-bit look ahead adder : T ebt o ka e dc rya d r p e su T ep o e sb h i lo h a a r d e s e d p h r c s y ei n t gr pec ryd ly I e a n sal h ip t i s l n o s a dg n r ts l ai i l a r ea . t x mie lte n u bt i t e u l n e e ae mi n p s mu a y c ry i- i fral tg ss l n o s .I i d n wi t a dt n l u cin c ry a r - bt o l sa e i t e u l t s o e t wo d io a fn t s a r n s mu a y h i o g n r t a dc ryp o a aefn t n e e ae n a r r p g t u ci . o T e c ry g n r t fn t n idc tsa t wh n a c ry o two l b g n r td b fl h a r e e ae u ci n i e s o e o a ar-u ud e e e ae y ul a d r A c ry o ti g n r td o l wh n b t te ip t bt a e 1 T i c n io i d e. a r - u s e e ae ny e oh h n us i r . hs o dt n s s i e p e s da teA D fn t no tet bt Aa dB x r se s h N u ci f h wo i o s n . C ryg n r t ( G = A. a r e e ae C ) B C ryp o a ae( P = A B ar rp g t G )

ptuece.loremate.com/die/node/3

11/12

10/3/12

Chapter 3 : Combinational Logic Circuits (Part 1) | Digital Electronics

ptuece.loremate.com/die/node/3

12/12

Das könnte Ihnen auch gefallen

- Groundwater Modelling: An Introduction with Sample Programs in BASICVon EverandGroundwater Modelling: An Introduction with Sample Programs in BASICNoch keine Bewertungen

- Interpolator For A Computer Numerical Control SystemDokument6 SeitenInterpolator For A Computer Numerical Control SystemJuan JacksonNoch keine Bewertungen

- Mackie D8B Service Notes SmallDokument117 SeitenMackie D8B Service Notes SmallsalvaesNoch keine Bewertungen

- Key and Solution Engineering Entrance - 2007Dokument22 SeitenKey and Solution Engineering Entrance - 2007Don TarunNoch keine Bewertungen

- Modern Image Processing: Warping, Morphing, and Classical TechniquesVon EverandModern Image Processing: Warping, Morphing, and Classical TechniquesNoch keine Bewertungen

- Assume Nothing: Previous Home NextDokument42 SeitenAssume Nothing: Previous Home NextHassaan RanaNoch keine Bewertungen

- Auto Electronics Projects: An Introduction to Your Car Electrics with Useful and Proven Self-Buld ProjectsVon EverandAuto Electronics Projects: An Introduction to Your Car Electrics with Useful and Proven Self-Buld ProjectsBewertung: 5 von 5 Sternen5/5 (1)

- CDMA 2000 1X: FP&A Summit, Hong Kong 10 Minute Win 7 MigrationDokument5 SeitenCDMA 2000 1X: FP&A Summit, Hong Kong 10 Minute Win 7 MigrationJelly WangNoch keine Bewertungen

- Design of Particulate Collectors Design of Particulate CollectorsDokument21 SeitenDesign of Particulate Collectors Design of Particulate CollectorsarkczestNoch keine Bewertungen

- Educational Electronics Equipment 1967–68: Pergamon Electronics Data SeriesVon EverandEducational Electronics Equipment 1967–68: Pergamon Electronics Data SeriesNoch keine Bewertungen

- USB - ModeSwitch - View Topic - Alcatel-Lucent T930SDokument18 SeitenUSB - ModeSwitch - View Topic - Alcatel-Lucent T930SMounir2105Noch keine Bewertungen

- A Simple Clock Using DS1307 + PIC16F877A - PIC Microcontroller NoteDokument14 SeitenA Simple Clock Using DS1307 + PIC16F877A - PIC Microcontroller Notelkemmerich100% (2)

- KMC 2013 Product CatalogDokument30 SeitenKMC 2013 Product CatalogGoodBikesNoch keine Bewertungen

- Safety Switches: in Plastic EnclosureDokument12 SeitenSafety Switches: in Plastic Enclosurechidambaram kasiNoch keine Bewertungen

- Handbook of Time Series Analysis, Signal Processing, and DynamicsVon EverandHandbook of Time Series Analysis, Signal Processing, and DynamicsD. S.G. PollockBewertung: 2 von 5 Sternen2/5 (2)

- Analysis Methods For Calculating Flexibility Factors of Nozzles and BranchesDokument111 SeitenAnalysis Methods For Calculating Flexibility Factors of Nozzles and BranchesfileseekerNoch keine Bewertungen

- A Tutorial On Data Representation - Integers, Floating-Point Numbers, and CharactersDokument25 SeitenA Tutorial On Data Representation - Integers, Floating-Point Numbers, and CharactersGoce StavreskiNoch keine Bewertungen

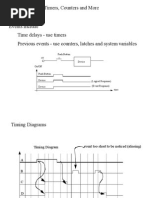

- Chapter - Latches, Timers, Counters and More: +V Push Button Device On/OffDokument18 SeitenChapter - Latches, Timers, Counters and More: +V Push Button Device On/OffModdy CavallindoNoch keine Bewertungen

- C Linux Interview Questions and AnswersDokument6 SeitenC Linux Interview Questions and AnswersSrimoy SupkarNoch keine Bewertungen

- Mitac 6120N ManualDokument141 SeitenMitac 6120N ManualLiviu LiviuNoch keine Bewertungen

- Computer Graphics Student HandbookDokument15 SeitenComputer Graphics Student HandbookPaing Paing Thwe SoeNoch keine Bewertungen

- Ieee No. 3, Computer Overcurrent Relay I E E E Commit'Tee Report"Dokument9 SeitenIeee No. 3, Computer Overcurrent Relay I E E E Commit'Tee Report"rockNoch keine Bewertungen

- Numerical Modelling of Groundwater BasinsDokument238 SeitenNumerical Modelling of Groundwater BasinsΒενιαμίν στέμμαNoch keine Bewertungen

- Thinking Parallel, Part 2Dokument10 SeitenThinking Parallel, Part 2cmaestrofdezNoch keine Bewertungen

- Digital Thermometer Using C# and ATmega16 Microcontroller - CodeProjectDokument10 SeitenDigital Thermometer Using C# and ATmega16 Microcontroller - CodeProjectAditya ChaudharyNoch keine Bewertungen

- Campaign Cartographer 3 (Download Torrent) - TPBDokument2 SeitenCampaign Cartographer 3 (Download Torrent) - TPBAdolf Bormann0% (4)

- Syn Flood Program in Python Using Raw Sockets (Linux)Dokument4 SeitenSyn Flood Program in Python Using Raw Sockets (Linux)gdayanand4uNoch keine Bewertungen

- Console Commands (Skyrim) - The Elder Scrolls WikiDokument6 SeitenConsole Commands (Skyrim) - The Elder Scrolls WikijhlkjhjhjklhkljhkkkkNoch keine Bewertungen

- ProkonDokument11 SeitenProkonmurugeshwaranNoch keine Bewertungen

- HDL Butterworth Filter DesignDokument5 SeitenHDL Butterworth Filter DesignArvind IndiaNoch keine Bewertungen

- Ulfath CV Alu Copy EmailDokument1 SeiteUlfath CV Alu Copy EmailUlfathbary ABNoch keine Bewertungen

- To ToDokument4 SeitenTo Toamitgh88Noch keine Bewertungen

- Thinking Parallel, Part 3Dokument11 SeitenThinking Parallel, Part 3cmaestrofdezNoch keine Bewertungen

- 023 - Cotton - Lightening ProtectionDokument15 Seiten023 - Cotton - Lightening ProtectionKerem AltıntaşNoch keine Bewertungen

- NS2 - How To Add New Routing Protocol - Causal NexusDokument10 SeitenNS2 - How To Add New Routing Protocol - Causal NexusJayrajsinh JadejaNoch keine Bewertungen

- File 0011Dokument1 SeiteFile 0011Ary Fakturrachman AryansyahNoch keine Bewertungen

- Practice QUestions-Annual Exam 2023-2024 Set-2Dokument10 SeitenPractice QUestions-Annual Exam 2023-2024 Set-2Aslam SyedNoch keine Bewertungen

- Preventative Maintenance ChecklistDokument1 SeitePreventative Maintenance Checklistajaysharma19686191Noch keine Bewertungen

- The MagPi Issue 4 FinalDokument32 SeitenThe MagPi Issue 4 FinalevanspcNoch keine Bewertungen

- Binding Crystal Report to DataSet in CDokument8 SeitenBinding Crystal Report to DataSet in Cmarco_ontiveros_12Noch keine Bewertungen

- Dungeon Keeper (PC)Dokument88 SeitenDungeon Keeper (PC)Kevin CruzNoch keine Bewertungen

- Numerical Study On Flow Past 2D Square Cylinder by Large Eddy Simulation - Comparison Between 2D and 3D ComputationsDokument8 SeitenNumerical Study On Flow Past 2D Square Cylinder by Large Eddy Simulation - Comparison Between 2D and 3D ComputationsMai ZhangNoch keine Bewertungen

- Tara Mueller Character ArtistDokument1 SeiteTara Mueller Character ArtistTara MuellerNoch keine Bewertungen

- 01 IntroductionDokument29 Seiten01 IntroductionindhumathiNoch keine Bewertungen

- Mixed BagDokument1 SeiteMixed BaglilacornphotoNoch keine Bewertungen

- Vikram Rana VFXartist RESUME 2010Dokument1 SeiteVikram Rana VFXartist RESUME 2010Vikram RanaNoch keine Bewertungen

- 3 540 45798 4Dokument509 Seiten3 540 45798 4QNE INTERNALNoch keine Bewertungen

- A Simple PDFDokument25 SeitenA Simple PDFacalin05Noch keine Bewertungen

- In Production, With N Face Turning, ?ig. I, During Nachining TheDokument4 SeitenIn Production, With N Face Turning, ?ig. I, During Nachining Theebi902000Noch keine Bewertungen

- NCH 350 Of.00Dokument13 SeitenNCH 350 Of.00manriquezorlandoNoch keine Bewertungen

- Doublet Lattice MethodDokument13 SeitenDoublet Lattice MethodRocco Musci100% (1)

- Mars 1Dokument35 SeitenMars 1Dax Mickelson100% (1)

- Device Drivers Part 9Dokument8 SeitenDevice Drivers Part 9ksenthil77Noch keine Bewertungen

- Basic Electronics Lab ManualDokument100 SeitenBasic Electronics Lab Manualalkeshkhatri87% (15)

- Thesis Neo Ubc 2007Dokument235 SeitenThesis Neo Ubc 2007nicolasNoch keine Bewertungen

- l1 PDFDokument30 Seitenl1 PDFRakesh KumarNoch keine Bewertungen

- Algorithms and ComplexityDokument140 SeitenAlgorithms and ComplexityFernando Gil de Vergara100% (1)

- Full TextDokument65 SeitenFull TextRakesh KumarNoch keine Bewertungen

- Ca Q&aDokument129 SeitenCa Q&aRavi TejaNoch keine Bewertungen

- Fundamentals of Communications Access TechnologiesDokument7 SeitenFundamentals of Communications Access TechnologiesRakesh KumarNoch keine Bewertungen

- What Is MetastabilityDokument4 SeitenWhat Is MetastabilityRakesh KumarNoch keine Bewertungen

- Chapter 3 - Combinational Logic Circuits (Part 1) - Digital ElectronicsDokument12 SeitenChapter 3 - Combinational Logic Circuits (Part 1) - Digital ElectronicsRakesh KumarNoch keine Bewertungen

- XCS 234Dokument20 SeitenXCS 234Balaji VenkatesanNoch keine Bewertungen

- Timing TutorialDokument13 SeitenTiming TutorialSai SandeepNoch keine Bewertungen

- Digital Logic Functions - LADDER LOGICDokument9 SeitenDigital Logic Functions - LADDER LOGICRakesh Kumar100% (1)

- What Are Set Up Time & Hold Time Constraints - What Do They Signify - Which One Is Critical For Estimating Maximum Clock Frequency of A CircuitDokument2 SeitenWhat Are Set Up Time & Hold Time Constraints - What Do They Signify - Which One Is Critical For Estimating Maximum Clock Frequency of A CircuitRakesh KumarNoch keine Bewertungen

- Digital Logic Functions - LADDER LOGICDokument9 SeitenDigital Logic Functions - LADDER LOGICRakesh Kumar100% (1)

- Clock Skew AnDokument13 SeitenClock Skew AnNimmalapudi SureshNoch keine Bewertungen

- DE09 SolDokument157 SeitenDE09 SolRakesh KumarNoch keine Bewertungen

- Outline: 1. Overview On Sequential CircuitDokument14 SeitenOutline: 1. Overview On Sequential CircuitbennettmatthewNoch keine Bewertungen

- Tutorial 4 Sequence Detector, ISE 10.1 On The Digilent Spartan-3E BoardDokument12 SeitenTutorial 4 Sequence Detector, ISE 10.1 On The Digilent Spartan-3E BoardRakesh KumarNoch keine Bewertungen

- Difference Between Verilog and VHDL - Difference Between - Verilog Vs VHDLDokument5 SeitenDifference Between Verilog and VHDL - Difference Between - Verilog Vs VHDLRakesh KumarNoch keine Bewertungen

- AE05 SolDokument135 SeitenAE05 SolVipul MahajanNoch keine Bewertungen

- Black BoxDokument1 SeiteBlack BoxRakesh KumarNoch keine Bewertungen

- CH 04Dokument36 SeitenCH 04Rahul GuptaNoch keine Bewertungen

- ENG112-Introduction to Electrical and Computer Engineering Fall 2003 Prof. Russell Tessier Understanding Sequential Circuit TimingDokument8 SeitenENG112-Introduction to Electrical and Computer Engineering Fall 2003 Prof. Russell Tessier Understanding Sequential Circuit Timingchuku7Noch keine Bewertungen

- Practice ProblemsDokument322 SeitenPractice Problems윤제율100% (1)

- Appendix - Design of The 11011 Sequence DetectorDokument9 SeitenAppendix - Design of The 11011 Sequence DetectorRakesh KumarNoch keine Bewertungen

- Frequency MultiplierDokument27 SeitenFrequency MultiplierRakesh KumarNoch keine Bewertungen

- Setup and Hold Time CalculationsDokument33 SeitenSetup and Hold Time CalculationsRashmi Periwal100% (11)

- Setup and Hold Time CalculationsDokument33 SeitenSetup and Hold Time CalculationsRashmi Periwal100% (11)

- Building A Gun Position Control SystemDokument36 SeitenBuilding A Gun Position Control SystemRakesh KumarNoch keine Bewertungen

- Building A Gun Position Control SystemDokument36 SeitenBuilding A Gun Position Control SystemRakesh KumarNoch keine Bewertungen

- HFGHGFDokument2 SeitenHFGHGFjimingeorgeNoch keine Bewertungen

- Storyboard Data Warehouse Planning GuestDokument15 SeitenStoryboard Data Warehouse Planning GuestHani SalemmNoch keine Bewertungen

- Syslog-Ng Guide HPUXDokument7 SeitenSyslog-Ng Guide HPUXDenilson NascimentoNoch keine Bewertungen

- The Business Case For GPON in FTTP NetworksDokument5 SeitenThe Business Case For GPON in FTTP NetworksTaha Wajahat100% (2)

- OpenocdDokument127 SeitenOpenocdEne AlexandruNoch keine Bewertungen

- Astm Protocol: Diagnostica Stago S.A.S - 9, Rue Des Frères Chausson - 92600 Asnières Sur Seine (France)Dokument48 SeitenAstm Protocol: Diagnostica Stago S.A.S - 9, Rue Des Frères Chausson - 92600 Asnières Sur Seine (France)Carlos Alberto Mollinedo GilNoch keine Bewertungen

- UNIX - Linux Commands For Oracle DBAs DBA TEAM - Vikram Gurung - Academia PDFDokument16 SeitenUNIX - Linux Commands For Oracle DBAs DBA TEAM - Vikram Gurung - Academia PDFShankar PujariNoch keine Bewertungen

- Learning Adobe Photoshop Elements 7 - Adjustment LayersDokument7 SeitenLearning Adobe Photoshop Elements 7 - Adjustment LayersGuided Computer Tutorials100% (4)

- Icamview en v2 3Dokument92 SeitenIcamview en v2 3giwrgos250% (1)

- HP Z240 Workstation Technical SpecsDokument4 SeitenHP Z240 Workstation Technical SpecsMartand Pratap SinghNoch keine Bewertungen

- Ccna 2 Module 11 v4.0Dokument3 SeitenCcna 2 Module 11 v4.0ccnatrainingNoch keine Bewertungen

- Backdoor MAC Eleanor FinalDokument10 SeitenBackdoor MAC Eleanor FinalElias Alboadicto Villagrán DonaireNoch keine Bewertungen

- Daily Reports Postilion: Alarms - A05W063Dokument7 SeitenDaily Reports Postilion: Alarms - A05W063dbvruthwizNoch keine Bewertungen

- 11unit 3 Data Path ImplementationDokument20 Seiten11unit 3 Data Path ImplementationsnNoch keine Bewertungen

- Tutorial 9Dokument4 SeitenTutorial 9Matthew SumNoch keine Bewertungen

- Asus F82 (Pra Se Basera Pegatron h24z) PDFDokument58 SeitenAsus F82 (Pra Se Basera Pegatron h24z) PDFNelson Junior De Oliveira Matos100% (1)

- Lzu1431171-M10 CompressDokument23 SeitenLzu1431171-M10 CompressTaulant BerishaNoch keine Bewertungen

- SF DumpDokument38 SeitenSF Dumppicochulo2381Noch keine Bewertungen

- Mini Project on Web DevelopmentDokument17 SeitenMini Project on Web Developmentjaggu verma100% (4)

- Veeam ExamDokument5 SeitenVeeam Examcrisandy3150% (2)

- Chapter - 3: Video Cassette RecorderDokument21 SeitenChapter - 3: Video Cassette Recorderapolloroka50% (2)

- SH 25 Ein 6 Difgr 9Dokument84 SeitenSH 25 Ein 6 Difgr 9akshayshetNoch keine Bewertungen

- 25 Log Files That Will Transform Your VSphere TroubleshootingDokument9 Seiten25 Log Files That Will Transform Your VSphere TroubleshootingRudra VmwareNoch keine Bewertungen

- Office 365 Administrator Resume: Career GoalDokument2 SeitenOffice 365 Administrator Resume: Career GoaldentisyNoch keine Bewertungen

- Wireless Network Fundamentals and ConceptsDokument2 SeitenWireless Network Fundamentals and ConceptsdjfgvhdvdfibNoch keine Bewertungen

- Iptables: System and Network SecurityDokument13 SeitenIptables: System and Network SecurityManoj SkNoch keine Bewertungen

- Juniper M5 M10 DatasheetDokument6 SeitenJuniper M5 M10 DatasheetMohammed Ali ZainNoch keine Bewertungen

- Top 20 CCNA Interview Questions and AnswersDokument4 SeitenTop 20 CCNA Interview Questions and Answerstaha aliNoch keine Bewertungen

- SQL Server Best Practices With CompellentDokument37 SeitenSQL Server Best Practices With Compellentkirkpatris910Noch keine Bewertungen

- Chapter ThiDokument119 SeitenChapter ThighumansmsaaNoch keine Bewertungen

- The Beekeeper's Lament: How One Man and Half a Billion Honey Bees Help Feed AmericaVon EverandThe Beekeeper's Lament: How One Man and Half a Billion Honey Bees Help Feed AmericaNoch keine Bewertungen

- Highest Duty: My Search for What Really MattersVon EverandHighest Duty: My Search for What Really MattersNoch keine Bewertungen

- Faster: How a Jewish Driver, an American Heiress, and a Legendary Car Beat Hitler's BestVon EverandFaster: How a Jewish Driver, an American Heiress, and a Legendary Car Beat Hitler's BestBewertung: 4 von 5 Sternen4/5 (28)

- The Fabric of Civilization: How Textiles Made the WorldVon EverandThe Fabric of Civilization: How Textiles Made the WorldBewertung: 4.5 von 5 Sternen4.5/5 (57)

- A Place of My Own: The Architecture of DaydreamsVon EverandA Place of My Own: The Architecture of DaydreamsBewertung: 4 von 5 Sternen4/5 (241)

- Dirt to Soil: One Family’s Journey into Regenerative AgricultureVon EverandDirt to Soil: One Family’s Journey into Regenerative AgricultureBewertung: 5 von 5 Sternen5/5 (124)

- Pale Blue Dot: A Vision of the Human Future in SpaceVon EverandPale Blue Dot: A Vision of the Human Future in SpaceBewertung: 4.5 von 5 Sternen4.5/5 (586)

- 35 Miles From Shore: The Ditching and Rescue of ALM Flight 980Von Everand35 Miles From Shore: The Ditching and Rescue of ALM Flight 980Bewertung: 4 von 5 Sternen4/5 (21)

- The Technology Trap: Capital, Labor, and Power in the Age of AutomationVon EverandThe Technology Trap: Capital, Labor, and Power in the Age of AutomationBewertung: 4.5 von 5 Sternen4.5/5 (46)

- Sully: The Untold Story Behind the Miracle on the HudsonVon EverandSully: The Untold Story Behind the Miracle on the HudsonBewertung: 4 von 5 Sternen4/5 (101)

- Recording Unhinged: Creative and Unconventional Music Recording TechniquesVon EverandRecording Unhinged: Creative and Unconventional Music Recording TechniquesNoch keine Bewertungen

- Data-ism: The Revolution Transforming Decision Making, Consumer Behavior, and Almost Everything ElseVon EverandData-ism: The Revolution Transforming Decision Making, Consumer Behavior, and Almost Everything ElseBewertung: 3.5 von 5 Sternen3.5/5 (12)

- The Future of Geography: How the Competition in Space Will Change Our WorldVon EverandThe Future of Geography: How the Competition in Space Will Change Our WorldBewertung: 4.5 von 5 Sternen4.5/5 (4)

- The Big, Bad Book of Botany: The World's Most Fascinating FloraVon EverandThe Big, Bad Book of Botany: The World's Most Fascinating FloraBewertung: 3 von 5 Sternen3/5 (10)

- Packing for Mars: The Curious Science of Life in the VoidVon EverandPacking for Mars: The Curious Science of Life in the VoidBewertung: 4 von 5 Sternen4/5 (1395)

- A Garden of Marvels: How We Discovered that Flowers Have Sex, Leaves Eat Air, and Other Secrets of PlantsVon EverandA Garden of Marvels: How We Discovered that Flowers Have Sex, Leaves Eat Air, and Other Secrets of PlantsNoch keine Bewertungen

- Reality+: Virtual Worlds and the Problems of PhilosophyVon EverandReality+: Virtual Worlds and the Problems of PhilosophyBewertung: 4 von 5 Sternen4/5 (24)

- The End of Craving: Recovering the Lost Wisdom of Eating WellVon EverandThe End of Craving: Recovering the Lost Wisdom of Eating WellBewertung: 4.5 von 5 Sternen4.5/5 (80)

- Transformed: Moving to the Product Operating ModelVon EverandTransformed: Moving to the Product Operating ModelBewertung: 4 von 5 Sternen4/5 (1)

- The Mushroom at the End of the World: On the Possibility of Life in Capitalist RuinsVon EverandThe Mushroom at the End of the World: On the Possibility of Life in Capitalist RuinsBewertung: 4 von 5 Sternen4/5 (139)

- The Things We Make: The Unknown History of Invention from Cathedrals to Soda CansVon EverandThe Things We Make: The Unknown History of Invention from Cathedrals to Soda CansNoch keine Bewertungen

- Across the Airless Wilds: The Lunar Rover and the Triumph of the Final Moon LandingsVon EverandAcross the Airless Wilds: The Lunar Rover and the Triumph of the Final Moon LandingsNoch keine Bewertungen

- Inventor of the Future: The Visionary Life of Buckminster FullerVon EverandInventor of the Future: The Visionary Life of Buckminster FullerBewertung: 4 von 5 Sternen4/5 (10)

- ChatGPT Money Machine 2024 - The Ultimate Chatbot Cheat Sheet to Go From Clueless Noob to Prompt Prodigy Fast! Complete AI Beginner’s Course to Catch the GPT Gold Rush Before It Leaves You BehindVon EverandChatGPT Money Machine 2024 - The Ultimate Chatbot Cheat Sheet to Go From Clueless Noob to Prompt Prodigy Fast! Complete AI Beginner’s Course to Catch the GPT Gold Rush Before It Leaves You BehindNoch keine Bewertungen

- Artificial Intelligence: A Guide for Thinking HumansVon EverandArtificial Intelligence: A Guide for Thinking HumansBewertung: 4.5 von 5 Sternen4.5/5 (30)