Beruflich Dokumente

Kultur Dokumente

Ee141 hw6 sp10

Hochgeladen von

Brenda PalmerOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ee141 hw6 sp10

Hochgeladen von

Brenda PalmerCopyright:

Verfügbare Formate

UNIVERSITY OF CALIFORNIA, BERKELEY

College of Engineering Department of Electrical Engineering and Computer Sciences

Jan M. Rabaey Homework #6

Due Friday, March 19 , 5pm, box in 240 Cory

EECS 141 (SP10)

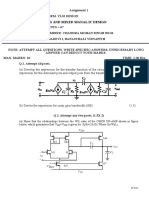

[PROBLEM 1] Pass Transistor Logic Consider the pass transistor logic implemented in a CMOS process as shown in Fig.1. Assume that VTN=|VTP|=0.3V. Ignore body effect, but dont ignore VT drop in pass transistor logic. VDD =1.2V (45 pts)

A C A B M1 S1

B M2 S2

M3 S3 M4 S4

Sinv

OUT

Fig.1. (a) What is the logic function performed by this circuit? (5 pts) (b) What is the purpose of having the two branches controlled by A and B ? (5 pts) (c) If OUT drives a large CL, derive an approximate expression for the worst-case propagation delay of the whole circuit. Assume the following parameters for the minimum-size NMOS and PMOS transistors, S=1: Reqn=10k, Reqp=20k, Cgs=Cgd=1fF; Cdb=Csb=1fF. The inverter is symmetrical sized, i.e. PMOS:NMOS=2:1. Ignore the miller effect at input and output of the inverter. Ignore overlap capacitances and feed-through from the gates of the switching transistors to the circuit nodes. (10 pts) (Hint: you may model the circuit as RC networks. Provide the delay expression in terms of Req and parasitic Cgs and Cgd of a transistor, i.e. use simple pass transistor model in prob.1(b) of HW#5.) (d) Explain qualitatively how you would like to size the pass transistors, S1 and S2. Derive relationship transistors size. (5pts) (e) Discuss the sources of static power dissipation in the circuit. (5pts) (f) Propose two circuit modifications to improve the performance and power dissipation of the circuit, and discuss the pros and cons of each of them. (5pts)

(g) What are the impacts on the performance and power consumption of this circuit if the threshold voltage of M1, M2, M3, and M4 is lowered? Assume that inverter has the same threshold voltage for nMOS and pMOS. (5pts) (h) What is minimum supply voltage for which this circuit is still operational? Show your line of thought. Assume that the inverter switches only when input is VDD/2.(5pts) [PROBLEM 2] Pass transistor gate with level restorer Consider the circuit in Fig.2. Let Cx = 50fF. M1 has W/L=0.5/0.25, and M2 has W/L = 0.5/0.5. Assume the output inverter doesnt switch until its input equals VDD/2 (VDD =2.5V). Use unified model. (30pts) NMOS: VTn = 0.5V, kn = 100A/V2, VD,VSAT = 0.6V, =0, =0.4V1/2, 2F = 0.6V PMOS: VTp = 0.5V, kp = 40A/V2, VD,VSAT = 1V, =0, =-0.4V1/2, 2F = 0.6V

VDD B A M1 CX M2 X

VDD

M3 OUT M4

Fig.2. (a) What is the function of M2? (5pts) (b) Describe qualitatively how this circuit operates for HL and LH input transitions. B is at 2.5V (5pts) (c) How long will it take M1 to pull node x down from 2.5V to 1.25V if 2.5V to 0V step input is applied to A, and B is at 2.5V? (5pts) (d) How long will it take M1 to pull node x up from 0 to 1.25V if 0V to 2.5V step input is applied to A, and B is at 2.5V? (5pts) (e) What is the minimum value of VB(Voltage of B input) necessary to pull Vx down to 1.25V when VA=0V? (5pts)

(f) If node B is at 2.5V, what is the maximum size of M2 such that the circuit still operates as intended? (5pts) [PROBLEM 3] Dynamic Logic Consider the domino circuit in Fig.3. Assuming that all inputs of the circuit shown in Fig.3 are initially Low (0V) during the pre-charge phase and that all internal nodes are at 0V. Ignore all other parasitic capacitance except C1, C2, and C3. It is given that VDD=2.5V, Vtn0=0.5V, 2F=0.6V and =0.4V0.5. (25pts)

VDD OUT CX=20fF A B C M1 M2 M3 C1=5fF C2=5fF C3=5fF

Fig.3. (a) Calculate the voltage drop on Vout (OUT node voltage) if A changes to High (2.5V) during the evaluation phase. (10pts) (Hint: Dont forget the body effect.) (b) Calculate the voltage drop on VOUT (OUT node voltage) if both A and B change to High (VDD=2.5V) (5pts). (c) What is the maximum number of transistors that can be connected in series to M1 and M2 (including M1 and M2, excluding M3) if the output should not fall below 0.9V during the evaluation phase? Assume that each one of the new transistors has the same intrinsic capacitance (to ground) as M1 and M2 (C=5fF). (10pts)

Das könnte Ihnen auch gefallen

- Assignment No. 6Dokument3 SeitenAssignment No. 6aditya nagrajanNoch keine Bewertungen

- EC3058D-VLSI Circuits and Systems Winter Semester-2020-21Dokument2 SeitenEC3058D-VLSI Circuits and Systems Winter Semester-2020-21Gamer AnonymousNoch keine Bewertungen

- Analysis and Design of Digital Integrated CircuitsDokument14 SeitenAnalysis and Design of Digital Integrated CircuitsfjwoemcuNoch keine Bewertungen

- EE 330 Exam 2 Spring 2015 PDFDokument10 SeitenEE 330 Exam 2 Spring 2015 PDFeng2011techNoch keine Bewertungen

- Questions On Small Signal Model of AmpDokument2 SeitenQuestions On Small Signal Model of AmpdevsrivastavaNoch keine Bewertungen

- Sheet 3 - SolutionDokument10 SeitenSheet 3 - SolutionMajid HelmyNoch keine Bewertungen

- Analog Guide RajaReddyDokument30 SeitenAnalog Guide RajaReddyKirti Susan VargheseNoch keine Bewertungen

- Assignment IDokument2 SeitenAssignment Ivaishnavi priyaNoch keine Bewertungen

- Analog and Digital Electronics PDFDokument34 SeitenAnalog and Digital Electronics PDFJatinNoch keine Bewertungen

- Identify The Structure Implemented in The Following Layout Diagram and Draw Its Equivalent CMOS ImplementationDokument2 SeitenIdentify The Structure Implemented in The Following Layout Diagram and Draw Its Equivalent CMOS Implementationrishika chhibberNoch keine Bewertungen

- Cat1Dokument3 SeitenCat1Manoharan KandasamyNoch keine Bewertungen

- iNVERTER aSSIGN6 1Dokument6 SeiteniNVERTER aSSIGN6 1Rohan ChopraNoch keine Bewertungen

- Exercise 2Dokument3 SeitenExercise 2momolololilo4Noch keine Bewertungen

- Analog CircuitsDokument33 SeitenAnalog Circuitsafireon80% (1)

- Chapter7 Ex PDFDokument5 SeitenChapter7 Ex PDFSathish Kumar100% (1)

- Exercise EEE418Dokument5 SeitenExercise EEE418Mohammad Zakir AlamNoch keine Bewertungen

- Electronics Design MOSFETDokument14 SeitenElectronics Design MOSFETbhanuNoch keine Bewertungen

- Sheet 5 PDFDokument3 SeitenSheet 5 PDFMajid HelmyNoch keine Bewertungen

- Analog ElectronicsDokument77 SeitenAnalog ElectronicsramyaranganayakiNoch keine Bewertungen

- Rabaey Dig ElectronicsDokument4 SeitenRabaey Dig ElectronicsRahul AgarwalNoch keine Bewertungen

- Solution ECE-438, MOS Transistor: W V I K V V V V L Min (V - VDokument10 SeitenSolution ECE-438, MOS Transistor: W V I K V V V V L Min (V - Vneeno2013Noch keine Bewertungen

- Analog Integrated Circuits Exercise 4: Common-Source and Differential AmplifiersDokument9 SeitenAnalog Integrated Circuits Exercise 4: Common-Source and Differential Amplifiersubuntu 13.04Noch keine Bewertungen

- General Instructions To The CandidateDokument4 SeitenGeneral Instructions To The Candidateapurv shuklaNoch keine Bewertungen

- Chapter03 ExDokument10 SeitenChapter03 ExKarthikeya VemparalaNoch keine Bewertungen

- Lab10 2011Dokument5 SeitenLab10 2011Venkat RamananNoch keine Bewertungen

- R09-Cmos Analog and Mixed Signal DesignDokument2 SeitenR09-Cmos Analog and Mixed Signal DesignbalashyamuNoch keine Bewertungen

- Solution Gates 2 SamplesDokument9 SeitenSolution Gates 2 SamplesluqmansulymanNoch keine Bewertungen

- Tutorial 5 MosDokument3 SeitenTutorial 5 MosomerNoch keine Bewertungen

- Subject: Analog and Mixed Signal Ic DesignDokument2 SeitenSubject: Analog and Mixed Signal Ic DesignchandravinitaNoch keine Bewertungen

- Jntu Hyd 2 2ece PDC Set 2Dokument18 SeitenJntu Hyd 2 2ece PDC Set 2Krishna RamaNoch keine Bewertungen

- An-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpDokument16 SeitenAn-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpbmmostefaNoch keine Bewertungen

- Application of Z-Source Converter in Photovoltaic Grid-Connected Transformer-Less InverterDokument5 SeitenApplication of Z-Source Converter in Photovoltaic Grid-Connected Transformer-Less InverterPaolo ProspNoch keine Bewertungen

- Ee270 HW2Dokument7 SeitenEe270 HW2saiedali2005Noch keine Bewertungen

- Question BankDokument4 SeitenQuestion BankKetan SalviNoch keine Bewertungen

- Chapter02 - Logic Design With MOSFETsDokument51 SeitenChapter02 - Logic Design With MOSFETsbal3xNoch keine Bewertungen

- EE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THDokument4 SeitenEE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THvedeshNoch keine Bewertungen

- Analog - RF VLSI Design (ECE 503) (Makeup) PDFDokument2 SeitenAnalog - RF VLSI Design (ECE 503) (Makeup) PDFRahul PinnamaneniNoch keine Bewertungen

- Q. 1 - Q. 25 Carry One Mark Each.: X A X AADokument14 SeitenQ. 1 - Q. 25 Carry One Mark Each.: X A X AAGauravArjariaNoch keine Bewertungen

- HW 1Dokument5 SeitenHW 1BrimwoodboyNoch keine Bewertungen

- 7.sheet OutputstagesDokument6 Seiten7.sheet OutputstagesAyman ElAshmawyNoch keine Bewertungen

- Sura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkDokument2 SeitenSura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkSaurabh SinghNoch keine Bewertungen

- I. Instructional Objectives: D S G D GDokument4 SeitenI. Instructional Objectives: D S G D Gcokelat_kNoch keine Bewertungen

- Design of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralDokument22 SeitenDesign of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralManraj GujralNoch keine Bewertungen

- ECE 410 Homework 7 - Solution Spring 2008Dokument4 SeitenECE 410 Homework 7 - Solution Spring 2008ET onlineNoch keine Bewertungen

- Singh 2018Dokument5 SeitenSingh 2018Tshering Sangmoo SherpaNoch keine Bewertungen

- Answers FinalDokument20 SeitenAnswers FinalMario HanyNoch keine Bewertungen

- EE 5311 Digital IC Design Tutorial 3 - Sep 25, 2015: N Ox 2 P Ox 2 Min Min T T Dsat Dsat DDDokument2 SeitenEE 5311 Digital IC Design Tutorial 3 - Sep 25, 2015: N Ox 2 P Ox 2 Min Min T T Dsat Dsat DDHarshithNoch keine Bewertungen

- Sheet 1Dokument4 SeitenSheet 1MohamedAlyNoch keine Bewertungen

- Ec3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopDokument2 SeitenEc3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopGamer AnonymousNoch keine Bewertungen

- HW1 2023fallDokument4 SeitenHW1 2023fallapplebao1022Noch keine Bewertungen

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsVon EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNoch keine Bewertungen

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsVon EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNoch keine Bewertungen

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Von EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)Noch keine Bewertungen

- Analog Circuit Design Volume Three: Design Note CollectionVon EverandAnalog Circuit Design Volume Three: Design Note CollectionBewertung: 3 von 5 Sternen3/5 (2)

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesVon EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNoch keine Bewertungen

- Exercises in Electronics: Operational Amplifier CircuitsVon EverandExercises in Electronics: Operational Amplifier CircuitsBewertung: 3 von 5 Sternen3/5 (1)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsVon EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNoch keine Bewertungen

- Power Systems-On-Chip: Practical Aspects of DesignVon EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNoch keine Bewertungen

- Unit 1 Bearer PlantsDokument2 SeitenUnit 1 Bearer PlantsEmzNoch keine Bewertungen

- HDO OpeationsDokument28 SeitenHDO OpeationsAtif NadeemNoch keine Bewertungen

- Corelink Mmu600ae TRM 101412 0100 00 enDokument194 SeitenCorelink Mmu600ae TRM 101412 0100 00 enLv DanielNoch keine Bewertungen

- Level of Organisation of Protein StructureDokument18 SeitenLevel of Organisation of Protein Structureyinghui94Noch keine Bewertungen

- ABHA Coil ProportionsDokument5 SeitenABHA Coil ProportionsOctav OctavianNoch keine Bewertungen

- Landscape ArchitectureDokument9 SeitenLandscape Architecturelisan2053Noch keine Bewertungen

- Quotation - 1Dokument4 SeitenQuotation - 1haszirul ameerNoch keine Bewertungen

- Answer: C: Exam Name: Exam Type: Exam Code: Total QuestionsDokument26 SeitenAnswer: C: Exam Name: Exam Type: Exam Code: Total QuestionsMohammed S.GoudaNoch keine Bewertungen

- Forensic IR-UV-ALS Directional Reflected Photography Light Source Lab Equipment OR-GZP1000Dokument3 SeitenForensic IR-UV-ALS Directional Reflected Photography Light Source Lab Equipment OR-GZP1000Zhou JoyceNoch keine Bewertungen

- Current Harmonics: Electric Power System Power QualityDokument3 SeitenCurrent Harmonics: Electric Power System Power QualityAlliver SapitulaNoch keine Bewertungen

- Flipkart Labels 06 Jul 2022 09 52Dokument37 SeitenFlipkart Labels 06 Jul 2022 09 52Dharmesh ManiyaNoch keine Bewertungen

- Emerging Technology SyllabusDokument6 SeitenEmerging Technology Syllabussw dr100% (4)

- FluteDokument13 SeitenFlutefisher3910% (1)

- Glossary of Blasting TermsDokument13 SeitenGlossary of Blasting TermsNitesh JainNoch keine Bewertungen

- Optical Transport Network SwitchingDokument16 SeitenOptical Transport Network SwitchingNdambuki DicksonNoch keine Bewertungen

- Norman, K. R., Pali Philology & The Study of BuddhismDokument13 SeitenNorman, K. R., Pali Philology & The Study of BuddhismkhrinizNoch keine Bewertungen

- Employee of The Month.Dokument2 SeitenEmployee of The Month.munyekiNoch keine Bewertungen

- Ships Near A Rocky Coast With Awaiting Landing PartyDokument2 SeitenShips Near A Rocky Coast With Awaiting Landing PartyFouaAj1 FouaAj1Noch keine Bewertungen

- Stratum CorneumDokument4 SeitenStratum CorneumMuh Firdaus Ar-RappanyNoch keine Bewertungen

- Eng Notes2Dokument10 SeitenEng Notes2Arti KapurNoch keine Bewertungen

- 6int 2008 Dec ADokument6 Seiten6int 2008 Dec ACharles_Leong_3417Noch keine Bewertungen

- OBOE GougerDokument2 SeitenOBOE GougerCarlos GaldámezNoch keine Bewertungen

- Method Statement FINALDokument61 SeitenMethod Statement FINALshareyhou67% (3)

- Energy Production From Speed BreakerDokument44 SeitenEnergy Production From Speed BreakerMuhammad Bilal67% (3)

- Coke Drum Repair Welch Aquilex WSI DCU Calgary 2009Dokument37 SeitenCoke Drum Repair Welch Aquilex WSI DCU Calgary 2009Oscar DorantesNoch keine Bewertungen

- Ode To The West WindDokument4 SeitenOde To The West WindCharis Mae DimaculanganNoch keine Bewertungen

- 1572 - Anantha Narayanan FFS CalculationDokument1 Seite1572 - Anantha Narayanan FFS CalculationAnantha NarayananNoch keine Bewertungen

- CV Ashish PDFDokument3 SeitenCV Ashish PDFRoshan KejariwalNoch keine Bewertungen

- Payment of Wages 1936Dokument4 SeitenPayment of Wages 1936Anand ReddyNoch keine Bewertungen

- 2015 NSPC Proposed Changes Book PDFDokument268 Seiten2015 NSPC Proposed Changes Book PDFMichelle Pinohermoso JabatNoch keine Bewertungen