Beruflich Dokumente

Kultur Dokumente

An Overview of High Voltage Direct Current Transmission System

Hochgeladen von

Emir DurmicOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

An Overview of High Voltage Direct Current Transmission System

Hochgeladen von

Emir DurmicCopyright:

Verfügbare Formate

U

Department of Electrical Engineering

ECE529: Session 44

An Overview of HVDC Transmission Systems

ECE 529 Spring 2009

HVDC Transmission Systems

1/24

Department of Electrical Engineering

ECE529: Session 44

Steady-State HVDC Converter Representation Steady state equivalent circuit

I dc

R dc

Inverter

V dcr

V dci

Rectifier

f ( ,Idc , |V |) ac

Have fast, direct control over (ring delay angle) Vdc = Vdo cos (ring delay angle) where Vdo = const |VLL| Some control of |Vac| with tap changing transformer DC current indirectly controlled by changing

HVDC Transmission Systems 2/24

Department of Electrical Engineering

ECE529: Session 44

Basic Six-Pulse Converter Based on line commutated, current source converter Thyristors used as devices Converter with stiff current source on dc side Stiff voltage source on ac side (turns off thyristors) Basic 6-pulse bridge:

Smoothing Reactor

A +

Ls

dc

ean (t)

+ C -

Xc

5

+ -

ebn (t)

+ B

ecn (t)

V 4 6 2

dc

Transformer Inductance

HVDC Transmission Systems

3/24

Department of Electrical Engineering

ECE529: Session 44

Basic Six-Pulse Converter Initially assume: 1) Ideal ac sources, 2) ideal switches, 3) Xc = 0, and 4) Ls source) AC side of converter has an ideal voltage source, dc side of converter has an ideal current source Apply Kirchhoffs Current Law: i1 + i3 + i5 = Idc (one switch always closed) i2 + i4 + i6 = Idc Apply Kirchhoffs Voltage Law: ean + ebn + ecn = 0 (balanced 3 phase set) Since Xc = 0, only one switch in (1,3,5) can be closed with a switch in (2,4,6)

HVDC Transmission Systems

4/24

Department of Electrical Engineering

ECE529: Session 44

Basic Six-Pulse Converter (cont.) Allowable combinations: 1 with (2 or 6) (4 shorts dc bus) 3 with (2 or 4) 5 with (4 or 6) 2 with (1 or 5) 4 with (1 or 3) 6 with (3 or 5) Need to determine a switching sequence Start from assumption of positive phase sequence Typical current waveforms: ia | | | | ib | | ic

HVDC Transmission Systems 5/24

Department of Electrical Engineering

ECE529: Session 44

Basic Six-Pulse Converter (cont.) Possible sequences: Top three switches: 1-3-5-1 or 1-5-3-1 Bottom three switches: 4-6-2-4 or 4-2-6-4

+ Assume: Vdc = Vdc - Vdc + Switch # Vdc Switch # Vdc 1 ean(t) 4 ean(t) 6 ebn(t) 3 ebn(t) 2 ecn(t) 5 ecn(t)

HVDC Transmission Systems

6/24

Department of Electrical Engineering

ECE529: Session 44

Basic Six-Pulse Converter (cont.) Positive sequence ( = 0, 1-3-5-1 and 4-6-2-4)

6.00 Voltage (V) -10.00

0.0

-6.00

-2.00

2.00

10.00

6.67

13.33 Time (mS)

20.00

26.66

33.33

Negative sequence ( = 0, 1-5-3-1 and 4-2-6-4)

6.00 Voltage (V) -10.00

0.0

-6.00

-2.00

2.00

10.00

6.67

13.33 Time (mS)

20.00

26.66

33.33

HVDC Transmission Systems

7/24

Department of Electrical Engineering

ECE529: Session 44

Basic Six-Pulse Converter (cont.)

5 6 1 2 3 4 5

I dc I dc

Phase currents:

Switch Combination 1-6 1-2 3-2 3-4 5-4 5-6

+ Vdc=Vdc - Vdc

Look at the line voltages:

eab= ean - ebn = Vdc eac= ean - ecn ebc= ebn - ecn eba = ebn - ean eca= ecn - ean ecb= ecn - ebn

If = 0, then Vdc =

HVDC Transmission Systems

3 2 |VLL |

= 1.35|VLL| We dene this as Vdo

8/24

Department of Electrical Engineering

ECE529: Session 44

Controlled Firing of Thyristors Now add a ring delay () for the thyristors. Same delay for all 6 switches

6.00 Voltage (V) -10.00

0.0

-6.00

-2.00

2.00

10.00

6.67

13.33 Time (mS)

20.00

26.66

33.33

HVDC Transmission Systems

9/24

Department of Electrical Engineering

ECE529: Session 44

Vdc =

2|VLL |cos()d + 6 3 2 Then Vdc = |VLL |cos 3 2 Dene Vdo = |VLL|

3

+ 6

Controlled Firing of Thyristors =

+ 3 2 6 |VLL |sin() | + 6

Therefore Vdc = Vdo cos = 0 diode bridge Vdc = Vdo 0 < 90 rectier Vdc > 0 = 90 P =0 Vdc = 0 90 < 180 inverter Vdc < 0 Current does not reverse

HVDC Transmission Systems

10/24

Department of Electrical Engineering

ECE529: Session 44

Commutation Overlap Now add source inductance (Lc = 0)

Ls

I

+

dc

Lc

V 4 6 2

dc r -

dc i

+ -

HVDC Transmission Systems

11/24

Department of Electrical Engineering

ECE529: Session 44

Current Transfer Between Switches Current does not fall to zero immediately in ac side inductance Temporarily create line to line short

Ls

1 Xc

3 Xc

ean (t)

ebn (t) ecn (t)

Xc

3

0

I dc

Ls

HVDC Transmission Systems

12/24

Department of Electrical Engineering

ECE529: Session 44

Current Transfer Between Switches (cont.) What happens if gets to big (i.e. 180)? I dc

1 1

0

This is called a commutation failure

Thyristor 3 fails to turn on and thyristor 1 fails to turn off This is more common if Lc is large, which is the case looking into a weaker ac system Normally corrects during next interval, although often have a second failure when thyristor 5 turns on, double commutation failure

HVDC Transmission Systems

13/24

Department of Electrical Engineering

ECE529: Session 44

Output Voltage During Commutation

+ Switch 1 contribution: Vdc1 = ean - Lc di1 dt + Switch 3 contribution: Vdc3 = ebn - Lc di3 dt + + During overlap we see the average between Vdc1 &Vdc3 + So Vdc

+ + Vdc1 +Vdc3 2

= ean+ebn 2 =0

Lc 2

di1 dt

+ di3 dt =

di1 dt

i1 + i3 = Idc, so

di1 +di3 dt

But since its a linear network:

di1 +di3 dt

+ di3 = 0 dt

+ So: Vdc = Vdc ecn = ean+ebn ecn = 2

eac+ebc 2

HVDC Transmission Systems

14/24

Department of Electrical Engineering

ECE529: Session 44

Recall: Vdo = = = where Em is peak line to neutral voltage Then we nd: 3 Vdc =

+ 3

3 2 |VLL |

Average DC Voltage with Overlap

3 6 |V | 3 3 |Em |

Emcosd +

+ 3 +

3|Em|cos( )d 6

Leading to: Vdc =

3 3 E [cos + cos( + )] 2 m

do Or Vdc = V2 [cos + cos( + )]

HVDC Transmission Systems

15/24

Department of Electrical Engineering

ECE529: Session 44

Average DC Current Start out with Lc = 0 and = 0 for now

120

Fundamental Current Component

210 0 30 150 180

330 360

Firing delay simply adds a phase shift to the current (always lagging), and cos = cos

E 30 I

a an

E 90 Ia

an

Fundamental Component 2 2 2 iacos()d = Idc i1pk = 2 |I1RMS| =

6 Idc

2 3 Idc cos()d = 3

3

HVDC Transmission Systems

16/24

Department of Electrical Engineering

ECE529: Session 44

Then i1(t) =

2 3 Idccos(t

Average DC Current )

Also: P = 3I1RMSVPcos = VdcIdc 3 6 So: 3I1RMSVPcos = VPcosIdc So: |Ia1RMS| =

6 I dc

as expected

3Em 2Lc eLL = 2Xc

During overlap: Idc = Ic =

i3(t) = Ic(cos cost) with t + where t = + at the end of the commutation interval So average current is: Idc = Ic(cos cos( + )) Also: Ic =

3Em 2Lc

3 |Vp | 2 Xc

|VLL = 2X|

HVDC Transmission Systems

17/24

Department of Electrical Engineering

ECE529: Session 44

Average DC Circuit Equations We have the following equations: Vdo Vdc = [cos + cos( + )] 2 Idc = Ic(cos cos( + )) 3 2 |VLL| Vdo = |VLL| Vdo Ic = = 6Xc 2Xc Substitute for the cos( + ) in the Vdc equation Then Vdc = Vdo cos Vdo Idc 2Ic Where Vdo = 2Ic

Vdo 2 6X c

Vdo

3 = Xc = Rc (called the commutating resistance)

So Vdc = Vdo cos IdcRc

HVDC Transmission Systems 18/24

Department of Electrical Engineering

ECE529: Session 44

Average DC circuit Rc represents a current dependent voltage drop due to overlap Rc does not represent any energy dissipation! So using Vdc = Vdo cos IdcRc we get:

R line Rc Rc

V cos

do

V cos do

RECTIFIER

INVERTER

HVDC Transmission Systems

19/24

Department of Electrical Engineering

ECE529: Session 44

Inverter Operation + + = Covers positive half cycle of voltage is dened as the extinction angle o is minimum extinction angle for proper turn-off Typical values: 15 20 So + 180 o gives limits for control settings Replace with 180 in averaged equations * note: cos(180 ) = cos()

HVDC Transmission Systems

20/24

Department of Electrical Engineering

ECE529: Session 44

Inverter Operation (cont.) Generate equations in terms on instead of Vdc = Vdc = Vdc = Idc = Idc = Vdo [cos + cos( + )] 2 Vdo [cos(180 ) + cos(180 )] 2 Vdo [cos( + ) + cos()] 2 Ic(cos cos( + )) Ic(cos cos( + ))

Sign reversal in voltage equation expected for inverter

HVDC Transmission Systems

21/24

Department of Electrical Engineering

ECE529: Session 44

Effect of Overlap on Power Transfer Pac = 3I1RMSVp cos Pdc = Idc Vdo cos+cos(+) 2 I1RMS = Idc 6 =

3 6Vp Idc

cos+cos(+) 2

Vdc Then cos = cos+cos(+) = Vdo 2

Note: overlap equations change if > 60, covered in Kimbark, Direct Current Transmission: Volume I. Wiley, 1971.

HVDC Transmission Systems

22/24

Department of Electrical Engineering

ECE529: Session 44

Transformer Loading

DC System AC system

x (p.u.)

Xc = Lc where X 12 20%

B ZB = VB I 2 3VB X 3VB IB 2 VLL

Xc = ZBX = Xc =

2 VBL X MVAB3

VB X IB

, this is

MVA3B

IB = I1RMS =

6 I dcB

So MVAB3 = 3VBIB = 3VB

HVDC Transmission Systems

6 IdcB

R = Vdo IdcB

23/24

Department of Electrical Engineering

ECE529: Session 44

Transformer Loading (cont.) Need to use true RMS (transformers sees all harmonic components) IRMS =

1 3 2 I d o dc

= Idc

2 3

R So MVAB3 = 3IRMSV = Vdo IdcB 3

Then Xc =

2 VBL MVAB3 X

with Vdo =

3 2 VBL

Vdo Then ZB = 6IdcB 3 Then from Vdc = Vdo cos Idc Xc we get 3 Vdc = Vdo cos Idc (ZBX ) dc Vdc = Vdo cos Vdo X IIdcB 2

Leading to a per unit expression:

Vdc Vdo

= cos X Idc 2

HVDC Transmission Systems

24/24

Das könnte Ihnen auch gefallen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Helical Pile Design Per IBC PDFDokument12 SeitenHelical Pile Design Per IBC PDFJorge Rosero QuevedoNoch keine Bewertungen

- 06ESL37 Analog Electronics Lab MANUALDokument70 Seiten06ESL37 Analog Electronics Lab MANUALSan AngadiNoch keine Bewertungen

- Electronics Circuit Design LabDokument34 SeitenElectronics Circuit Design Labsrvdhar100% (1)

- CE 351 Part 3 Chapter 4 B Pipe Network PDFDokument31 SeitenCE 351 Part 3 Chapter 4 B Pipe Network PDFAli M. ChehadehNoch keine Bewertungen

- Unit 4 InvertersDokument86 SeitenUnit 4 InvertersHaritha RkNoch keine Bewertungen

- Beginning Digital Electronics through ProjectsVon EverandBeginning Digital Electronics through ProjectsBewertung: 5 von 5 Sternen5/5 (1)

- Electrical EngineeringDokument58 SeitenElectrical EngineeringNor Syahirah MohamadNoch keine Bewertungen

- "Ugtank" - Underground Storage Tank Anchorage Design: Program DescriptionDokument3 Seiten"Ugtank" - Underground Storage Tank Anchorage Design: Program Descriptionharoub_nasNoch keine Bewertungen

- High Voltage Pspice Manual PDFDokument35 SeitenHigh Voltage Pspice Manual PDFMuhammad Ahtisham AsifNoch keine Bewertungen

- Final Report About HVDC TECHNOLOGYDokument21 SeitenFinal Report About HVDC TECHNOLOGYSefu BikorimanaNoch keine Bewertungen

- Electro-Static Discharge (ESD) in Turbine Oils: © 2015 Exxon Mobil Corporation. All Rights ReserveDokument14 SeitenElectro-Static Discharge (ESD) in Turbine Oils: © 2015 Exxon Mobil Corporation. All Rights Reserve'Izzad AfifNoch keine Bewertungen

- Lecture On Basic Concept Operation and Control of HVDCDokument74 SeitenLecture On Basic Concept Operation and Control of HVDCpongpum0% (1)

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlVon EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlBewertung: 5 von 5 Sternen5/5 (1)

- Introduction To InvertersDokument27 SeitenIntroduction To Invertersselaroth168Noch keine Bewertungen

- Analog Electronics Lab Manual-10esl67Dokument61 SeitenAnalog Electronics Lab Manual-10esl67manojmanojsarmaNoch keine Bewertungen

- RFID PresentationDokument22 SeitenRFID PresentationouiamNoch keine Bewertungen

- 3 Phase Controlled Rectifiers FinalDokument57 Seiten3 Phase Controlled Rectifiers FinalRama PrasadNoch keine Bewertungen

- CH 7Dokument53 SeitenCH 7Gautam TamangNoch keine Bewertungen

- CMOS InverterDokument16 SeitenCMOS Invertersreekanthreddy peramNoch keine Bewertungen

- Aula6 - ConversoresDokument26 SeitenAula6 - ConversoreslucianoNoch keine Bewertungen

- Rectifiers, Inverters & Motors DrivesDokument32 SeitenRectifiers, Inverters & Motors DrivesUtkarsh AgrawalNoch keine Bewertungen

- 10ESL37 - Analog Electronics Lab ManualDokument69 Seiten10ESL37 - Analog Electronics Lab ManualVinita AgrawalNoch keine Bewertungen

- EE42 100 Wb-Lecture16 073113-FDokument42 SeitenEE42 100 Wb-Lecture16 073113-FozanistzNoch keine Bewertungen

- Chapter 4Dokument41 SeitenChapter 4Anil ParmarNoch keine Bewertungen

- Class 7Dokument48 SeitenClass 7Lorin IravaNoch keine Bewertungen

- Dynamic Logic CircuitsDokument38 SeitenDynamic Logic Circuitssreekanthreddy peramNoch keine Bewertungen

- EE42 100 Wb-Lecture19 080713-FDokument37 SeitenEE42 100 Wb-Lecture19 080713-FozanistzNoch keine Bewertungen

- DC/DC Power Supply: by Rob Mcmurry Jason WellsDokument23 SeitenDC/DC Power Supply: by Rob Mcmurry Jason WellsKoopaa TapeNoch keine Bewertungen

- Analysis of 6 Pulse ConverterDokument27 SeitenAnalysis of 6 Pulse ConverterSowjanya BhamidipatiNoch keine Bewertungen

- 15 Trans VRDokument32 Seiten15 Trans VRAkbarDwiSyahputraNoch keine Bewertungen

- Asymmetric Half Bridge (AHB) Converters - by FairchildDokument19 SeitenAsymmetric Half Bridge (AHB) Converters - by FairchildahsansadaqatNoch keine Bewertungen

- DiodesDokument33 SeitenDiodesReddyvari VenugopalNoch keine Bewertungen

- Report About HVDCDokument21 SeitenReport About HVDCSefu BikorimanaNoch keine Bewertungen

- Thyristor Controlled ConverterDokument26 SeitenThyristor Controlled Converteramrit403Noch keine Bewertungen

- Class 3 Electronics II Spring 21Dokument9 SeitenClass 3 Electronics II Spring 21Esha JahinNoch keine Bewertungen

- North Bengal International University Department of Electrical & Electronic Engineering Course No.: Eee 2203 Course Title: Electronics IiDokument9 SeitenNorth Bengal International University Department of Electrical & Electronic Engineering Course No.: Eee 2203 Course Title: Electronics IiEsha JahinNoch keine Bewertungen

- Yaskawa Harmonic Mitigation PDFDokument55 SeitenYaskawa Harmonic Mitigation PDFRyan JayNoch keine Bewertungen

- Switched Capacitor DC-DC Converters: Topologies and ApplicationsDokument25 SeitenSwitched Capacitor DC-DC Converters: Topologies and ApplicationsNitu VlsiNoch keine Bewertungen

- ESDynamic Logic CircuitsDokument61 SeitenESDynamic Logic CircuitsMandovi BorthakurNoch keine Bewertungen

- 06ESL37 - Analog Electronics LabDokument70 Seiten06ESL37 - Analog Electronics LabqwertyjklfghNoch keine Bewertungen

- Design and Analysis of 24 Pulse Ac-Dc Converter: May 2015, Volume 2, Issue 5 JETIR (ISSN-2349-5162)Dokument8 SeitenDesign and Analysis of 24 Pulse Ac-Dc Converter: May 2015, Volume 2, Issue 5 JETIR (ISSN-2349-5162)anuragpugaliaNoch keine Bewertungen

- LAB2Dokument4 SeitenLAB2Anya SohailNoch keine Bewertungen

- JANARDDokument4 SeitenJANARDirinuca12Noch keine Bewertungen

- Lect 11Dokument30 SeitenLect 11Aswin Sivaraman100% (1)

- Dynamic Logic CircuitsDokument61 SeitenDynamic Logic Circuitsbirla_sNoch keine Bewertungen

- Timer Ic 555Dokument8 SeitenTimer Ic 555Pradnyesh VishwasraoNoch keine Bewertungen

- Single-Phase Converter Systems Containing Ideal RectifiersDokument51 SeitenSingle-Phase Converter Systems Containing Ideal Rectifiersselaroth168Noch keine Bewertungen

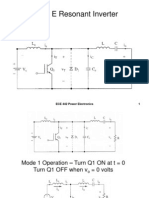

- Class E Resonant InverterDokument28 SeitenClass E Resonant InverterSenthil Kumar0% (1)

- Capacitance InductanceDokument68 SeitenCapacitance InductanceRonnel MontanezNoch keine Bewertungen

- Chang 09 Med PrimDokument6 SeitenChang 09 Med PrimSuselleNoch keine Bewertungen

- Calculation Algorithm For Single Phase Bridge Rectifier With Capacitor FilterDokument7 SeitenCalculation Algorithm For Single Phase Bridge Rectifier With Capacitor FilterAhmedNoch keine Bewertungen

- Part 1 BasicConceptsDokument43 SeitenPart 1 BasicConceptsmomoz141Noch keine Bewertungen

- 2.-Electrotecnia Unit2 PDFDokument12 Seiten2.-Electrotecnia Unit2 PDFJayaraj LathaNoch keine Bewertungen

- Tugas 4 - Linda Andriani N - 2101397Dokument6 SeitenTugas 4 - Linda Andriani N - 2101397Linda AndrianiNoch keine Bewertungen

- L23Dokument29 SeitenL23Mary MorseNoch keine Bewertungen

- MCQ - AC Voltage ControllerDokument8 SeitenMCQ - AC Voltage ControllerrajuNoch keine Bewertungen

- 3rd SEM EDI LAB Manual (18ECL37)Dokument48 Seiten3rd SEM EDI LAB Manual (18ECL37)Shreesha KalkoorNoch keine Bewertungen

- Dual Retriggerable Monostable Multivibrator: Order CodesDokument12 SeitenDual Retriggerable Monostable Multivibrator: Order Codeswrite2skNoch keine Bewertungen

- EC 2404 ESD Lab ManualDokument72 SeitenEC 2404 ESD Lab ManualSuba VenkateshNoch keine Bewertungen

- ch02 AnalogMultiplierDokument32 Seitench02 AnalogMultipliergamaladdiniNoch keine Bewertungen

- Lost WatersDokument132 SeitenLost WatersLauraHensonNoch keine Bewertungen

- Pharmaceutical Standardization of Herbal Lozenges Vasa CandyDokument6 SeitenPharmaceutical Standardization of Herbal Lozenges Vasa Candydrsa2Noch keine Bewertungen

- Optical Fibre FormulasDokument2 SeitenOptical Fibre FormulasImam Tri BaskoroNoch keine Bewertungen

- 2080iq4 2Dokument2 Seiten2080iq4 2RajeshNoch keine Bewertungen

- Short Note: Michael Wilt and Mitchel StarkiDokument6 SeitenShort Note: Michael Wilt and Mitchel StarkiRahmat HidayatNoch keine Bewertungen

- Effects of Dry Density and Grain Size Distribution On Soil-Water Characteristic Curves of Sandy SoilsDokument12 SeitenEffects of Dry Density and Grain Size Distribution On Soil-Water Characteristic Curves of Sandy SoilsmazharNoch keine Bewertungen

- 19EC402 QK-Signals and SystemsDokument34 Seiten19EC402 QK-Signals and SystemsSaranya AthipatlaNoch keine Bewertungen

- Babinet's PrincipleDokument3 SeitenBabinet's Principleperception888Noch keine Bewertungen

- Presentacion Sellos DoblesDokument33 SeitenPresentacion Sellos DoblesRolando Felipe Tapia MoyanoNoch keine Bewertungen

- Project ReportDokument14 SeitenProject ReportGitanshu kumarNoch keine Bewertungen

- Power CyclesDokument10 SeitenPower CyclesSNoch keine Bewertungen

- M408D Exam3 2009summer PDFDokument5 SeitenM408D Exam3 2009summer PDFexamkillerNoch keine Bewertungen

- Surge Propagation in Multiconductor Transmission Lines Below GroundDokument42 SeitenSurge Propagation in Multiconductor Transmission Lines Below GroundDejanNoch keine Bewertungen

- Star-Forming Environments in Smoothed Particle Magnetohydrodynamics Simulations I: Clump Extraction and PropertiesDokument18 SeitenStar-Forming Environments in Smoothed Particle Magnetohydrodynamics Simulations I: Clump Extraction and PropertiesTneerajNoch keine Bewertungen

- Chapter-2 Principle of FlightDokument8 SeitenChapter-2 Principle of FlightAgastia imranNoch keine Bewertungen

- IEEE-A Primer On Capacitor Bank Protection PDFDokument6 SeitenIEEE-A Primer On Capacitor Bank Protection PDFGustavo AguayoNoch keine Bewertungen

- Effect of Drying Temperature On The Stability of Polyphenols andDokument4 SeitenEffect of Drying Temperature On The Stability of Polyphenols andAna NunesNoch keine Bewertungen

- XPS PerovskiteDokument3 SeitenXPS PerovskiteJosé Luis Rosas HuertaNoch keine Bewertungen

- Note On Numerical Solutions For Gas Lubricated Journal BearingsDokument3 SeitenNote On Numerical Solutions For Gas Lubricated Journal Bearingsmanjunath k sNoch keine Bewertungen

- Extraction of Equivalent Beam Properties From Blade ModelsDokument23 SeitenExtraction of Equivalent Beam Properties From Blade ModelsggNoch keine Bewertungen

- Leica TP 1020 Automatic Tissue ProcessorDokument70 SeitenLeica TP 1020 Automatic Tissue ProcessorArbjan RusiNoch keine Bewertungen

- Quotation Yoke WIFL Sanaswadi 201718Dokument4 SeitenQuotation Yoke WIFL Sanaswadi 201718Deipak HoleNoch keine Bewertungen

- Failures Analysis of E-Glass Fibre Reinforced PipeDokument11 SeitenFailures Analysis of E-Glass Fibre Reinforced PipeScarllett Lalesca Santos LimaNoch keine Bewertungen

- Signal Flow GraphsDokument10 SeitenSignal Flow GraphsAmir DillawarNoch keine Bewertungen

- Physiology Assignment 1Dokument5 SeitenPhysiology Assignment 1abdul jabbarNoch keine Bewertungen

- C FIX Report0Dokument7 SeitenC FIX Report0Laurence SarmientoNoch keine Bewertungen