Beruflich Dokumente

Kultur Dokumente

MATLAB Based Cost Modeling For VLSI Testing

Hochgeladen von

Vinod KheraOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

MATLAB Based Cost Modeling For VLSI Testing

Hochgeladen von

Vinod KheraCopyright:

Verfügbare Formate

The Research Bulletin of Jordan ACM, Vol.

II (III)

P a g e | 95

MATLAB Based Cost Modeling for VLSI Testing

Balwinder Singh

Centre for Development of Advanced Computing (CDAC), Mohali, India +911812412927 Balwinder.cdacmohali@gmail.com

Arun Khosla

ECE Department Dr. B .R. Ambedkar National Institute of Technology, Jalandhar, India arun.khosla@gmail.com

Sukhleen Bindra Narang

Electronics Technology Department, Guru Nanak Dev University, Amritsar, India Sukleen2@yahoo.com

ABSTRACT

The cost for testing integrated circuits and systems is growing rapidly as their complexity is increasing as per Moores law. Cost modeling plays a very vital role in reducing test cost and time to market. It also gives estimate of overall testing. The economics modeling for VLSI testing with Automatic Test Equipment (ATE) is presented in this paper. The mathematical relations are developed for cost model to test the VLSI circuits based on the parameters of ATE testing; further cost modeling equations are modeled into Graphical User Interface (GUI) in Matlab, which can be used as a cost estimation tool. A case study is done for Set-top-box, Microprocessor, Device A to verify the functionality of the developed estimation tool. It helps the Test engineers for estimating the testing cost for the test planning.

focus on cost of the test will result in a better understanding of cost trade-offs between test methodologies as per ITRS 2007[1] as shown in figure1. Typically, the cost of test boosts exponentially with an improvement in defects per million (DPM). Mathematical modeling in MATLAB GUI (graphic user interface) is very powerful as it reduces the designers time. Modification of any designed function in MATLAB GUI is very easy. The flexibility of MATLAB is used for rapid deployment of the complex software to the end user.

Categories and Subject Descriptors

B.7.3 [Reliability and Testing]Built-in tests , Test generation ,Testability

General Terms

Design, Economics, Reliability, Verification.

Keywords

Cost Model, Automatic Test Equipment, Graphical User Interface, Design for Testability

Figure 1: Quality and cost Trade-offs [ITRS 2007]

The paper is organized as follows: Section 2 describes the related work of economics of VLSI Testing and cost modeling. Section 3 presents the test cost model that is used for the automatic test equipment for multisite module testing. In Section 4 gives procedure for the cost modeling tool development using Matlab. Section 5 discusses a case study three devices for the verification of the economic analysis tool. The paper ends with the conclusions in Section 6.

1. INTRODUCTION

Test cost is very important factor for complex chip designs. As the trend of System on Chip appears in the industry, the Integrated circuit designs turn into more complex than the conventional designs, so the expense of testing is increased. The cost related to the development of semiconductor testing procedures and methods for ATE are the main driving factor. The mathematical algorithms or parametric equations used to estimate the costs of a product or project are known as cost estimation models. These models are typically essential for business plans/budgets, and other financial planning and tracking mechanisms. The continuing

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Copyright 2011 IJJ: The Research Bulletin of Jordan ACM - ISWSA; ISSN: 2078-7952 (print); 2078-7960 (online)

2. RELATED WORK

Many researchers have explored the idea and benefits of the cost of manufacturing test in the past. Some of them are discussed here. VonKyoung Kim et. al.3] proposed a test cost prediction model which estimates and optimize manufacturing test cost. I.D. Dear et.al. [2] the authors discussed the economics of test. The EVEREST test strategy planner tool, which is used for the test planning. Andrew[4]developed a Semiconductor Test Economic Model that can easily be applied to lowering overall cost of test and improving throughput. It gives idea to the to the Test Engineers for better decisions on the issues related to: test time reduction, multisite testing, yield, handler index time, ATE Utilization, and ATE purchasing. Erik et.al[5] discussed the benefits and tradeoffs by applying the technical cost modeling on 4 applications. Kenneth[6] gives the estimated the economic benefits of

The Research Bulletin of Jordan ACM, Vol. II (III) the DFT and also suggested that testability features should not be added to complex or high volume products. Abadir et al. [7] developed Hi-TEA, a MCM testing strategy selection tool, which helps to select the cost effective test strategy for the multi-chip module(MCM). Their tool required cost parameters such as die test cost and wafer yield, which are the parameters difficult to know in the early stage of design. Therefore, their tool may not be practical to predict a chip testing cost early on.

P a g e | 96

The cost of Np probe cards, which cost Nlifetime-Volume of the product and maximum touchdowns Nmtd. The pseudo code the developed cost model is given below

{Enter the required data from user like Enter Probe card cost; Enter number of devices ;} First of all for the calculation of Nsites Matlab code is {Rsignal = .1; Nsite_ms = str2double (a)/str2double (b); Nsite_ms_ATE= str2double(c)/ str2double (d); if (Nsite_ms< Nsite_ms_ATE) Nsites_MS = Nsite_ms; Else(Nsites_MS= Nsite_ms_ATE;) : end }}{Similarly Matab code is developed calculate the total cost Ct}

3. ECONOMIC COST MODEL FOR ATE BASED VLSI TESTING

The cost of semiconductor test to the organization has many drivers that are labor cost, floor space cost, Maintenance cost, ATE cost per site etc. The significance of these drivers varies substantially from one device to another. Test development costs are more important for the products with lower volume. Cost model is structured with the help of cost parameters figure 2.

to

4. COST MODELING TOOL WITH MATLAB GRAPHICAL USER INTERFACE

Market modeling and Cost prediction/Estimation are new areas in which interest of physical and mathematical researchers is growing due the stochastic nature of the financial processes. Constraining by this interest it becomes necessary to develop comprehensive software environment, which will use the same models for the simplification for quantitative analysis. The main advantage for such approach is that it provides rapid prototyping, high-quality visualization, and enhanced model testing to the end users.

Figure 2: Economic cost model for ATE based VLSI Testing.

The cost model is targeted the reduction of the capital equipment cost and the test time. The area overhead due to Design for Testability (DFT) implementation is not considered here so silicon overhead cost for DFT is not modeled. Therefore, this model considers only cost associated with spending time on equipment and test engineering. Cost model is used for wafer sorting during testing. One assumption is made here is that all functional tests are done in package test [10]. The cost is calculated as:

=C

. N- life-volume e

.1 Figure 3: Tool development of Cost Modeling

GUI design is based on mathematical equations and user inputs Graphical User Interface is designed in MATLAB (.fig file) and backend callback functions are called from GUI for each calculation. Development of GUI and its link with the database are shown in figure 3. In this, GUI has been created for mathematical equations. Numbers of input variables are set depending upon the equation to be designed. Property of every single component is set in the Property Inspector. A MATLAB code is written, which is generated by the callbacks of a particular push button. An event is created by clicking on push button for final result calculations, which causes the function of the button to be executed. A link is established between database which is created in excel file and GUI. The model will help us evaluate the direct cost impacts of various values in the balanced scorecard, for the test processes. Using cost models, the relative effectiveness of two different test processes can be evaluated. To calculate the total cost of each test process user is

Ctest cell : Total capital equipment cost of the test cell, Np : Number of Probe cards Ttotal : Total time a die spends on the equipment Ct : Total time of a die spends on the ATE Nsites : Number of dies tested in parallel. Ccap : Constant consist amortization, utilization, labor cost, floor space, maintenance and training cost. To calculate Np equation is given as

Where Np : No. of probe cards Nmtd : Maximum touchdowns and N life-volume: Life time volume of dies

The Research Bulletin of Jordan ACM, Vol. II (III) required to enter the input data as per parameters required for estimation are shown in the figure 4.

P a g e | 97

GUI based cost-modeling tool for DFT, BIST, and SOC for web based application and standalone systems.

6. REFERENCES

[1] Semiconductor Industry Association (SIA), International Technology

Roadmap for Semiconductors (ITRS), 2007

[2] [3]

Dear, I.D., Dislis, C., Ambler, A.P., Dick, J. Economic effects in design and test, Design & Test of Computers, IEEE, vol.8(4) (1991):64-77 Kim, V., Chen, T., and Tegethoff, M., ASIC Manufacturing Test Cost Prediction at Early Design Stage. IEEE international Test Conference (1997) 356-61 Multisite Testing to Lower Cost of Test, International Test Conference 1999 (ITC'99)

[4] Andrew C. Evans, Applications of Semiconductor Test Economics, and

[5]

Erik H. Volkerink, Ajay Khoche, Jochen Rivoir, Klaus D. Hilliges, Test Economics for Multi-site Test with Modern Cost Reduction Techniques, 20th IEEE VLSI Test Symposium (2002), 411 - 416 Design. Test symposium 1999, 71-79

[6] Butler, K. M., Estimating the Economic Benefits of DFT 16th IEEE [7]

M. Abadir, A. Parikh, L. Bal, P. Sandborn, and C. Murphy,. High Level Test Economics Advisor (Hi-TEA), Journal of Electronic Testing Theory and Practice, vol. 5 (1994), pp. 195206. , Modeling the Economics of Testing: A DFT Perspective, IEEE Design and Test of Computers, (2002) 19(1): 29-41.

[8] Pranab K. Nag, Anne Gattiker, Sichao Wei, R.D. Blanton, Wojciech Maly Figure 4: A view of tool developed for VLSI test cost based on ATE.

4.

CASE STUDY FOR VERIFICATION OF COST MODELING TOOL

[9]

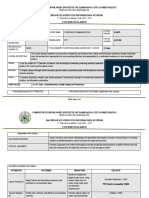

In this Case study three applications are considered. Data are taken for verification of developed tool from [5] as shown in Table 1. First device is a Set Top Box (STB) with medium complexity of 1 million transistor, second a Microprocessor chip (P) with 5 million of transistor complexity and also having high pin count, Third device A is taken with low volume of transistors i.e. 250 K only, which can be tested with one probe card only but more probe cards are needed for P IC tests on ATE. This tool gives the individual testing cost of the all devices and comparison of three of those devices is demonstrates graphical form in same GUI.

Karthik Sundararaman, Shambhu Upadhyaya, Martin Margala, Cost Model Analysis of DFT Based Fault Tolerant SOC Designs, 5th International Symposium on Quality Electronic Design (ISQED'04), (2004): pp 465-469 paradigm that scales with technology progress, Proceeding of European Test Workshop. 2001pp 201-12

[10] W. Radermacher and J. Rivoir, An Evolution to a DFT centric test

[11] Online: http://www.mathworks.com/products/matlab/, website of The

Math Works, Inc. developer and distributor of technical computing software Matlab.

[12] Chun-Ming Huang; Chien-Ming Wu; Chih-Chyau Yang; Wei-De Chien;

Shih-Lun Chen; Chi-Shi Chen; Jiann-Jenn Wang; Chin-Long Wey; , "Implementation and prototyping of a complex multi-project system-on-achip," Circuits and Systems, ISCAS 2009. IEEE International Symposium on , vol., no., pp.2321-2324, 24-27 May (2009)

5. CONCLUSION

In this paper, a cost modeling tool for ATE based VLSI testing is presented. The mathematical equations are modeled using MATLAB GUI interface in which a Graphical interface is provided to the test engineers which is helpful to save the time in cost calculations and that GUI also compares the three devices at a time, which will give the exact estimation for the testing cost during VLSI testing process. This work can be also extend for DFT or without DFT based cost models in MATLAB for the future wok. For the future work, we are developing

[13] Zixing Qin; Zhanhong Xin; Yunjin Fu; Jun Wu;, "Cost Analysis of China

IP Network Based on Improved Cost Proxy Model," Intelligent Information Technology Application, 2008.. Second International Symposium on , vol.3, no., pp.669-674, 20-22 Dec. (2008)

[14] Johnson, M.D.; Kirchain, R.; , "Developing and Assessing Commonality

Metrics for Product Families: A Process-Based Cost-Modeling Approach," Engineering Management, IEEE Transactions on , vol.57, no.4, pp.634-648, Nov.( 2010)

The Research Bulletin of Jordan ACM, Vol. II (III)

P a g e | 98

Table1. Devices for cost modeling and parameter specifications

Parameter N_lifetime G f_max,chain f_max,I/O P_total t_fix C_ATE0 C_site P_max,ATE f_max,ATE C_chan C_prober t_index c_capital c_volume P_ctrl f_max,probecard P_max,probecard C_probecard N_max,touchdown ns R_testport Description Device: Lifetime volume [k] Device: Number of logic gates [M] Device: Maximum scan chain frequency [MHz] Device: Maximum I/O frequency for scan [MHz] Device: Total number of device pads for wafer test Time for DC+PLL+ Mixed-signal+ Mem [s] ATE: Cost zero channel [k$] ATE: Cost per site resource [k$] ATE: Maximum number of channels ATE: Maximum ATE data channel frequency [MHz] ATE: Channel Cost High / Low [$] Prober: Cost [k$] Prober: Index time [s] Test cost per sec on M$ [$] ATPG test data volume per gate [bits] Number of control signals Probe card: Maximum frequency [MHz] Probe card: Maximum number of contacts Probe card: Cost [k$] Probe card: Maximum number of touchdowns [k] Test port [%] Application Set-top-box 1000 2 20 100 300 6 150 25 1000 250 1K/400 350 1 0.02 400 3 150 1000 20 150 50 P 5000 20 100 400 1000 2 150 60 1000 400 1K/400 350 1 0.02 400 6 150 1000 60 150 50 Device A 250 6 30 200 400 2 150 25 1000 400 1K/400 350 1 0.02 400 3 150 1000 20(reusable) 150 50

Authors Bio brief

Balwinder Singh has obtained his Bachelor of Technology degree from National Institute of Technology, Jalandhar and Master of Technology degree from University Centre for Inst. & Microelectronics (UCIM), Panjab University, Chandigah in 2002 and 2004 respectively. He is currently serving as Sr. Engineer in Center for Development of Advanced Computing (CDAC), Mohali and is a part of the teaching faculty. He has 6+ years of teaching experience to both undergraduate and postgraduate students. Singh has published two books and many papers in the International & National Journal and Conferences. His current interest includes Genetic algorithms, Low Power Techniques, VLSI Design & Testing, and System on Chip.

Arun Khosla received his PhD degree from Indraprastha University, Delhi in the field of Information Technology. He is presently working as Associate Professor and Head in the Department of Electronics and Communication Engineering, National Institute of Technology, Jalandhar. India. Dr. Khosla has been reviewer for various IEEE and other National and International conferences and also serves on the editorial board of International Journal of Swarm Intelligence Research. He is a life member of Indian Society of Technical Education.

Sukleen Bindra Narang received her PhD degree from Guru Nanak Dev University, Amritsar in the field of Electronics Technology and M. Tech from Indian Institute of Technology (IIT), Roorkee. She is presently working as Professor and Head in the Department of Electronics Technology, Guru Nanak Dev university, Amritsar. India. She has published number of research publications in reputed National and International journals and conferences and her current area of research are Microwave materials, neural networks, VLSI circuits.

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- POC Mobile App Scoping Documentv0.1Dokument24 SeitenPOC Mobile App Scoping Documentv0.1Rajwinder KaurNoch keine Bewertungen

- Entrepreneural Ventrures - Sample Assignment 1Dokument15 SeitenEntrepreneural Ventrures - Sample Assignment 1Owais JunaidNoch keine Bewertungen

- Reading Clue 1:: Teacher's GuideDokument183 SeitenReading Clue 1:: Teacher's GuideQuốc Nam LêNoch keine Bewertungen

- DLL Sektor NG AgrikulturaDokument7 SeitenDLL Sektor NG AgrikulturaFredielyn Santos LuyamanNoch keine Bewertungen

- Narrative ReportDokument6 SeitenNarrative ReportAko C Gra'y67% (9)

- Fault ModellingDokument58 SeitenFault ModellingVinod KheraNoch keine Bewertungen

- Spartan6 - Vlsi DesignDokument5 SeitenSpartan6 - Vlsi DesignVinod KheraNoch keine Bewertungen

- Identifying Dont Care PDFDokument6 SeitenIdentifying Dont Care PDFVinod KheraNoch keine Bewertungen

- An Experimental Chip To Evaluate Test TechniquesDokument10 SeitenAn Experimental Chip To Evaluate Test TechniquesVinod KheraNoch keine Bewertungen

- Asynchronous MCUDokument22 SeitenAsynchronous MCUVinod KheraNoch keine Bewertungen

- Essestial of VLSIDokument60 SeitenEssestial of VLSIVinod KheraNoch keine Bewertungen

- D Cube TestingDokument48 SeitenD Cube TestingVinod Khera100% (1)

- DQ-CMR Top T-Schoosl ReportDokument19 SeitenDQ-CMR Top T-Schoosl ReportVinod KheraNoch keine Bewertungen

- DocumentDokument14 SeitenDocumentgeorge_43Noch keine Bewertungen

- Notification AAI Manager Junior ExecutiveDokument8 SeitenNotification AAI Manager Junior ExecutivesreenuNoch keine Bewertungen

- Short Note:-: Neelanjan Ray 1305017048 Health Care Managemnet BBA (H) - 6 SEM BBA - 604Dokument8 SeitenShort Note:-: Neelanjan Ray 1305017048 Health Care Managemnet BBA (H) - 6 SEM BBA - 604neelanjan royNoch keine Bewertungen

- Edsp - Lesson Plan - Underhand ThrowingDokument7 SeitenEdsp - Lesson Plan - Underhand Throwingapi-535394816Noch keine Bewertungen

- Undergraduate Programme BrochureDokument8 SeitenUndergraduate Programme BrochureNITHISH PRANAV GNoch keine Bewertungen

- Lesson Plan-Primary 20 MinsDokument5 SeitenLesson Plan-Primary 20 Minsapi-2946278220% (1)

- Program IISMA 2021 KemdikbudDokument8 SeitenProgram IISMA 2021 KemdikbudRizky Fadilah PaneNoch keine Bewertungen

- A Description of A CelebrationDokument3 SeitenA Description of A CelebrationzhannaNoch keine Bewertungen

- Chapter 3Dokument10 SeitenChapter 3Fundashi LoverNoch keine Bewertungen

- Feedback Control System SyllabusDokument3 SeitenFeedback Control System SyllabusDamanMakhijaNoch keine Bewertungen

- Second Final Draft of Dissertation (Repaired)Dokument217 SeitenSecond Final Draft of Dissertation (Repaired)jessica coronelNoch keine Bewertungen

- Idioms Challenge 5 - TCHDokument2 SeitenIdioms Challenge 5 - TCHCamila PaulucciNoch keine Bewertungen

- Problems and Issues of Primary EducationDokument9 SeitenProblems and Issues of Primary EducationAbhimanyu Sharma50% (2)

- Curriculum Dualism AssignmentDokument7 SeitenCurriculum Dualism AssignmentMuhammad Mohsin AltafNoch keine Bewertungen

- Ess Ia Criteria 1Dokument7 SeitenEss Ia Criteria 1leoNoch keine Bewertungen

- Introduction To Research Track 230221Dokument24 SeitenIntroduction To Research Track 230221Bilramzy FakhrianNoch keine Bewertungen

- Pdhpe Term 1 KindergratenDokument26 SeitenPdhpe Term 1 Kindergratenapi-249015874Noch keine Bewertungen

- HUIZINGA - MypathtohistoryDokument18 SeitenHUIZINGA - MypathtohistoryRenato Ferreira LopezNoch keine Bewertungen

- Literature Review Synthesis TemplateDokument8 SeitenLiterature Review Synthesis Templateea84e0rr100% (1)

- Genre AnalysisDokument6 SeitenGenre Analysisapi-273164465Noch keine Bewertungen

- Activity in TC 3 - 7.12.21Dokument5 SeitenActivity in TC 3 - 7.12.21Nica LagrimasNoch keine Bewertungen

- Cengage LearningDokument12 SeitenCengage LearningerikomarNoch keine Bewertungen

- CHED Puroposive CommunicationDokument13 SeitenCHED Puroposive CommunicationCyril-J BalboaNoch keine Bewertungen

- Presentation SG9b The Concept of Number - Operations On Whole NumberDokument30 SeitenPresentation SG9b The Concept of Number - Operations On Whole NumberFaithNoch keine Bewertungen

- Unit 2 The Learning Process: V vN1aRN5bQQ0Dokument5 SeitenUnit 2 The Learning Process: V vN1aRN5bQQ0Mica Maureen HipolitoNoch keine Bewertungen

- Math Geo GuitarDokument20 SeitenMath Geo GuitarcoquizzzNoch keine Bewertungen