Beruflich Dokumente

Kultur Dokumente

Lcdenatel

Hochgeladen von

jaimeOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lcdenatel

Hochgeladen von

jaimeCopyright:

Verfügbare Formate

BATRON

Specification for BTHQ 128064AVD-SRE-06-COG

Version July 2003

0 DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 2 OF 16

DOCUMENT REVISION HISTORY 1: DOCUMENT REVISION FROM TO A DATE 2003.07.01 DESCRIPTION First Release. CHANGED BY CHECKED BY

SUNNY LEE DENG YU YUAN

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 3 OF 16

CONTENTS

Page No. 1. 2. 3. 4. 4.1 4.2 5. 5.1 5.2 6. GENERAL DESCRIPTION MECHANICAL SPECIFICATIONS INTERFACE SIGNALS ABSOLUTE MAXIMUM RATINGS ELECTRICAL MAXIMUM RATINGS (Ta=25 C) ENVIRONMENTAL CONDITION ELECTRICAL SPECIFICATIONS TYPICAL ELECTRICAL CHARACTERISTICS TIMING SPECIFICATIONS COMMAND TABLE 4 4 9 11 11 11 12 12 13 16

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 4 OF 16

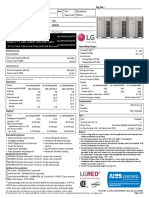

Specification of LCD Module Type Model No.: COG-BTD12864-01

1. General Description 128 x 64 Dots STN Positive Yellow Reflective Dot Matrix LCD Module. Viewing Angle: 12 oclock direction. Driving duty: 1/65 Duty, 1/7 bias. Epson S1D10605D04B (COG) Dot Matrix LCD Driver or equivalent. FPC

2.

Mechanical Specifications The mechanical detail is shown in Fig. 1 and summarized in Table 1 below. Table 1

Parameter Outline dimensions Viewing area Active area Display format Dot size Dot spacing Dot pitch Weight

Specifications 55.6(W) x 70.2(H) x 1.095(D) (Included FPC) 50.60(W) x 31.0(H) 46.577(W) x 27.697(H) 128(W) x 64(H) 0.349(W) x 0.418(H) 0.015(W) x 0.015(H) 0.364(W) x 0.433(H) Approx. 9

Unit mm mm mm dots mm mm mm grams

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 5 OF 16

Figure 1: Outline Drawing 1

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119 www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 6 OF 16

Figure 2: Outline Drawing 2

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119 www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 7 OF 16

COG-BTD12864 LCD GRAPHIC DISPLAY

32

32

128X64 DOTS

RES CS1 D/C R/W(WR) E(RD) D7~D0 VDD VSS VOUT C3C1+ C1C2C2+ V1 V2 V3 V4 V5 C86 P/S

8

DOT MATRIX LCD CONTROLLER/ DRIVER 'EPSON' S1D10605D04B (COG)

Figure 3: Block Diagram.

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119 www.data-modul.de

128

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 8 OF 16

Figure 4: Reference Circuit

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 9 OF 16

3. Interface signals Table 2(a): Pin Assignment Pin No. 1 Symbol P/S Description This is the parallel data input/serial data input switch terminal. P/S = HIGH: Parallel data input. P/S = LOW: Serial data input. The following applies depending on the P/S status: P/S Data/Command Data Read/Write Serial Clock HIGH D/C(A0) D0 to D7 RD, WR LOW D/C(A0) SI (D7) Write only SCL (D6) When P/S = LOW, D0 to D5 are HZ. D0 to D5 may be HIGH, LOW or Open. RD(E) and WR(R/W) are fixed to either HIGH or LOW. With serial data input, RAM display data reading is not supported. This is the MPU interface switch terminal. C86=HIGH: 6800 Series MPU interface. C86=LOW: 8080 MPU interface. This is multi-level power supply for liquid crystal drive. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown below. VDD (=V0) V1 V2 V3 V4 V5 Master operation When the power supply turns ON, the internal power supply circuits produce V1 to V4 voltages shown below. The voltage setting are selected using the LCD bias set command. For 1/7 bias: V1=(1/7)xV5, V2=(2/7)xV5, V3=(5/7)xV5, V4=(6/7)xV5. DC/DC voltage converter. Connects a capacitor between this terminal and C2 terminal. DC/DC voltage converter. Connects a capacitor between this terminal and C2+ terminal. DC/DC voltage converter. Connects a capacitor between this terminal and C1+ terminal. DC/DC voltage converter. Connects a capacitor between this terminal and C1 terminal. DC/DC voltage converter. Connects a capacitor between this terminal and C1+ terminal. DC/DC voltage converter. Connects a capacitor between this terminal and VSS. 0 V pin connected to the system ground (GND) and this is also the reference power supply for the step-up voltage circuit for the liquid crystal drive. Power supply for logic(+3.3V).

2 3 4 5 6 7

C86 V5 V4 V3 V2 V1

8 9 10 11 12 13 14 15

C2+ C2C1C1+ C3VOUT VSS VDD

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 10 OF 16

Table 2(b): Pin Assignment Pin No. 16 17 18 19 20 21 22 23 24 Symbol D7 D6 D5 D4 D3 D2 D1 D0 E(RD) Description This is an 8-bit bi-directional data bus that connects to an 8-bit standard MPU data bus. When the serial interface is selected (P/S = LOW), then D7 serves as the serial data input terminal (SI) and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance. When the chip select is inactive, D0 to D7 are set to high impedance.

When connected to an 8080 MPU, this is active LOW. This pin is connected to the RD signal of the 8080 MPU, and the S1D15605 series data bus is in an output status when this signal is LOW.

25

When connected to a 6800 Series MPU, this is active HIGH. This is the 6800 Series MPU enable clock input terminal. R/W(WR) When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU WR signal. The signals on the data bus are latched at the rising edge of the WR signal. When connected to an 6800 Series MPU: This is the read/write control signal input terminal. When R/W = HIGH: Read. When R/W = LOW: Write. This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or a command. D/C(A0)=High: Indicates that D0 to D7 are display data. D/C(A0)=Low: Indicates that D0 to D7 are control data. This is the chip select signal for first chip. When CS1=LOW and CS2=HIGH, then the chip select becomes active and the data/commands I/O is enabled. When RES is set to LOW, the settings are initialized. The reset operation is performed by the RES signal level.

26

D/C

27 28

CS1 RES

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 11 OF 16

4. 4.1

Absolute Maximum Ratings Electrical Maximum Ratings (Ta = 25 C) Table 3 Parameter Power Supply voltage (Logic) Power Supply voltage(VSS2)(VDD standard) Power Supply voltage(V5,VOUT)(VDD standard) Power Supply voltage(V1,V2,V3,V4)(VDD standard) Input voltage

Symbol VDD-VSS VSS2 V5,VOUT V1,V2,V3,V4 Vin

Min. -0.3 -4.0 -18.0 V5 -0.3

V3

Max. +6.0 +0.3 +0.3 +0.3 VDD+0.3

V4 V5.

Unit V V V V V

Note: 1.)The VSS2, V1 to V5 and VOUT are relative to the VDD=0V reference. 2.)The V1, V2, V3, and V4 voltages must always satisfy the condition of VDD V1 V2 3.)The modules may be destroyed if they are used beyond the absolute maximum ratings.

4.2

Environmental Condition Table 4 Operating Storage Temperature Temperature (Topr) (Tstg) Min. Max. Min. Max. 0 C +50 C -20 C +65 C 95% max. RH for Ta 40 C < 95% RH for Ta > 40 C Frequency: 10 55 Hz Amplitude: 0.75 mm Duration: 20 cycles in each direction. Pulse duration : 11 ms Peak acceleration: 981 m/s2 = 100g Number of shocks : 3 shocks in 3 mutually perpendicular axes.

Item Ambient Temperature Humidity Vibration (IEC 68-2-6) cells must be mounted on a suitable connector Shock (IEC 68-2-27) Half-sine pulse shape

Remark Dry no condensation 3 directions 3 directions

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 12 OF 16

5. 5.1

Electrical Specifications Typical Electrical Characteristics At Ta = +25 C, VDD = +3.3 5%, VSS = 0V. Table 5

Parameter Symbol Conditions Min. Typ. Max. Unit Supply voltage VDD-VSS 3.14 3.3 3.47 V (Logic) Supply voltage VLCD 8.80 V Ta = 0 C, (LCD) (built-in) =VDD-V5 Character mode VDD = +3.3V, Note 1 8.45 8.65 8.85 V Ta = 25 C, Character mode VDD = +3.3V, Note 1 7.95 V Ta = 50 C, Character mode VDD = +3.3V, Note 1 Low-level input VILC Note 2 VSS 0.2xVDD V signal voltage High-level input VIHC Note 2 0.8xVDD VDD V signal voltage Supply Current IDD VDD = +3.3V,Note 1, 0.3 0.45 mA (Logic & LCD) Character mode VDD = +3.3V,Note 1, 0.5 0.75 mA Checker board mode Note 1: There is tolerance in optimum LCD driving voltage during production and it will be within the specified range. Note 2: A0, D0 to D5,D6(SCL),D7(SI),E(RD),R/W(WR),CS1,C86,P/S,RES terminals.

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 13 OF 16

5.2

Timing Specifications System Bus read/Write Characteristics 1 (For the 8080 Series MPU) At Ta = 0 C to +50 C, VDD = +3.3V 5%, VSS = 0V. Table 6

*1 The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast, (tr + tf) (tCYCL(H)8 tCCLW tCCHW) for (tr + tf) (tCYCL(H)8 tCCLR tCCHR) are specified. *2 All timing is specified using 20% and 80% of VDD as reference. *3 tCCLW and tCCLR are specified as the overlap between CS1 being LOW (CS2=HIGH) and WR and RD being at the LOW level.

Figure 5: The timing diagram of system bus read/write (For the 8080 Series MPU)

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119 www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 14 OF 16

System Bus read/Write Characteristics 2 (For the 6800 Series MPU) At Ta = 0 C to +50 C, VDD = +3.3V 5%, VSS = 0V. Table 7

*1 The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast, (tr + tf) (tCYCH(L)6 tEWLW tEWHW) for (tr + tf) (tCYCH(L)6 tEWLR tEWHR) are specified. *2 All timing is specified using 20% and 80% for VDD as the reference. *3 tEWLW and tEWLR are specified as the overlap between CS1 being LOW (CS2=HIGH) and E.

Figure 6: The timing diagram of system bus read/write (For the 6800 Series MPU)

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119 www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 15 OF 16

The serial interface At Ta = 0 C to +50 C, VDD = +3.3V 5%, VSS = 0V. Table 8

Note 1: The input signal rise and fall (tr, tf) are specified at 15ns or less. Note 2: All timing is specified using 20% and 80% of VDD as the standard.

Figure 7: The timing diagram of serial interface Reset Timing At Ta = 0 C to +50 C, VDD = +3.3V 5%, VSS = 0V. Table 9

Note : All timing is specified with 20% and 80% of VDD as the standard.

Figure 8: Reset Timing

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119 www.data-modul.de

VL-FS-COG-BTD12864-01 REV. A (BTHQ 128064AVD-SRE-06-COG) JULY/2003

PAGE 16 OF 16

6.

Command Table Table 10

DATA MODUL AG Landsberger Str. 322 80687 Mnchen Tel.: 089/ 56017-0 Fax 089/ 56017-119

www.data-modul.de

Das könnte Ihnen auch gefallen

- Dspic 30 FDokument186 SeitenDspic 30 FCemil_Baki_K_y_3546Noch keine Bewertungen

- Understanding and Using DC Ac InvertersDokument3 SeitenUnderstanding and Using DC Ac Invertersglobalrevolution0% (1)

- Driver Mosfet TC4425Dokument18 SeitenDriver Mosfet TC4425jaimeNoch keine Bewertungen

- Display Matricia 7x5Dokument4 SeitenDisplay Matricia 7x5Luis Angel Fuantos TobiasNoch keine Bewertungen

- Lector de Corriente MAX4173-MAX4173TDokument10 SeitenLector de Corriente MAX4173-MAX4173TjaimeNoch keine Bewertungen

- Pic 18f45k20 ProgrammingDokument78 SeitenPic 18f45k20 ProgrammingAndrei NicolaeNoch keine Bewertungen

- Driver Mosfet Ucc27322xDokument26 SeitenDriver Mosfet Ucc27322xjaimeNoch keine Bewertungen

- 1996 Ford Windstar Owners ManualDokument394 Seiten1996 Ford Windstar Owners Manualdustyboner100% (9)

- Driver Mosfet Ucc27322xDokument26 SeitenDriver Mosfet Ucc27322xjaimeNoch keine Bewertungen

- Pic 18f45k20 ProgrammingDokument78 SeitenPic 18f45k20 ProgrammingAndrei NicolaeNoch keine Bewertungen

- 2SC5200Dokument6 Seiten2SC5200jaimeNoch keine Bewertungen

- Driver Mosfet TC428Dokument16 SeitenDriver Mosfet TC428jaimeNoch keine Bewertungen

- Three Phase InverterDokument62 SeitenThree Phase InverterHashim MunirNoch keine Bewertungen

- TL7117Dokument24 SeitenTL7117jaimeNoch keine Bewertungen

- 1000w Inverter PURE SINE WAVE Schematic DiagramDokument84 Seiten1000w Inverter PURE SINE WAVE Schematic DiagramPERWANA100% (3)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Whirlpool Microwave ServiceDokument80 SeitenWhirlpool Microwave ServicealexpetrNoch keine Bewertungen

- For ECE Engg Graduates, How Do I Prepare For The ISRO SC Exam? What All Subjects and Materials Do I Have To Prepare? How Do I Crack The Interview?Dokument5 SeitenFor ECE Engg Graduates, How Do I Prepare For The ISRO SC Exam? What All Subjects and Materials Do I Have To Prepare? How Do I Crack The Interview?Sree BloggersNoch keine Bewertungen

- Diesel Generator Set Specification Sheet - 500 kVA: Generator Specifications Alternator SpecificationsDokument2 SeitenDiesel Generator Set Specification Sheet - 500 kVA: Generator Specifications Alternator SpecificationsZaif MirzaNoch keine Bewertungen

- 30kv Hvkit Manual-ElsytecDokument6 Seiten30kv Hvkit Manual-ElsytececplpraveenNoch keine Bewertungen

- Panasonic LCD (2012) TX-l55wt50 (La34)Dokument67 SeitenPanasonic LCD (2012) TX-l55wt50 (La34)Jacob EvansNoch keine Bewertungen

- Electricity Generation With The Use of Wind EnergyDokument26 SeitenElectricity Generation With The Use of Wind EnergyStephany PolinarNoch keine Bewertungen

- Components of The Tidal Power PlantDokument5 SeitenComponents of The Tidal Power PlantGerry PersiaNoch keine Bewertungen

- Digital IR Fibre Optic Pyrometer With Mono Fibre Optic Cable With Bluetooth V2.0Dokument4 SeitenDigital IR Fibre Optic Pyrometer With Mono Fibre Optic Cable With Bluetooth V2.0DharmendraJainNoch keine Bewertungen

- Tutorial 6Dokument2 SeitenTutorial 6Rohan sharmaNoch keine Bewertungen

- West Bengal State Electricity Transmission Co. LTD.: List of LocationsDokument4 SeitenWest Bengal State Electricity Transmission Co. LTD.: List of Locationssamkarmakar2002Noch keine Bewertungen

- User Manual: SUN2000 - (20KTL, 29.9KTL, 30KTL, 36KTL, 40KTL) - M3Dokument112 SeitenUser Manual: SUN2000 - (20KTL, 29.9KTL, 30KTL, 36KTL, 40KTL) - M3Jorge DanielNoch keine Bewertungen

- Topic 5 - MultivibratorsDokument12 SeitenTopic 5 - MultivibratorsPatrick TeodoroNoch keine Bewertungen

- Daewoo FRS 2031 Fridge Freezer Operating Instructions User Guide ManualDokument78 SeitenDaewoo FRS 2031 Fridge Freezer Operating Instructions User Guide Manualplvg2009100% (1)

- Converting The Digitech Xp-100 To An XP-"All" Build InstructionsDokument66 SeitenConverting The Digitech Xp-100 To An XP-"All" Build InstructionsneonrenNoch keine Bewertungen

- SF0004-C10-7110 Gutor Schematic DiagramDokument172 SeitenSF0004-C10-7110 Gutor Schematic DiagramYounes SaifiNoch keine Bewertungen

- ASIC List For Garden LightsDokument1 SeiteASIC List For Garden LightsAnirudhNoch keine Bewertungen

- Neom Oxagon Local Control & Main PLC Panel Material Schedule 17-10-2022Dokument1 SeiteNeom Oxagon Local Control & Main PLC Panel Material Schedule 17-10-2022sachin francisNoch keine Bewertungen

- ARUM432BTE5Dokument3 SeitenARUM432BTE5Omar JuradoNoch keine Bewertungen

- Mid Term Exam IM - W23 - Dr. TanveerDokument2 SeitenMid Term Exam IM - W23 - Dr. TanveerRana AhsanNoch keine Bewertungen

- A Center-Fed Electric Dipole of Length L Is Attach...Dokument5 SeitenA Center-Fed Electric Dipole of Length L Is Attach...qasimNoch keine Bewertungen

- Powerboss Tech SpeakingDokument11 SeitenPowerboss Tech SpeakingAnand VairavanNoch keine Bewertungen

- Altech User Manual AlRitmaDokument63 SeitenAltech User Manual AlRitmaAndrew AllanNoch keine Bewertungen

- Multiple Choices Questions in Communications Engineering By: S. S. Cuervo & K. L. N. Suello 400 Solved Problems Transmission LinesDokument949 SeitenMultiple Choices Questions in Communications Engineering By: S. S. Cuervo & K. L. N. Suello 400 Solved Problems Transmission LinesEdmark AldeaNoch keine Bewertungen

- 3g Repeater Programmerbar Coiler Ps 2200 PDFDokument2 Seiten3g Repeater Programmerbar Coiler Ps 2200 PDFDuval FortesNoch keine Bewertungen

- BM3451 Series: 3/4/5 Cell Battery ProtectorsDokument28 SeitenBM3451 Series: 3/4/5 Cell Battery ProtectorsKaur77Noch keine Bewertungen

- Medium Voltage Induction Motor Protection and Diagnostics: Yi Du Pinjia Zhang Prof. Thomas G. HabetlerDokument61 SeitenMedium Voltage Induction Motor Protection and Diagnostics: Yi Du Pinjia Zhang Prof. Thomas G. HabetlervladalucarDNoch keine Bewertungen

- Multifunction Meter (Mfm-02) : FeaturesDokument1 SeiteMultifunction Meter (Mfm-02) : FeaturesBhageerathi SahuNoch keine Bewertungen

- Kriwan INT280-60 - DiagnoseDokument4 SeitenKriwan INT280-60 - DiagnosehamzaNoch keine Bewertungen

- Cablebusbrochure 2015Dokument31 SeitenCablebusbrochure 2015Emad ArafaNoch keine Bewertungen

- CSC-101 Line Protection IED Technical Application Manual - V1.01Dokument366 SeitenCSC-101 Line Protection IED Technical Application Manual - V1.01Ashwini Kumar RaiNoch keine Bewertungen