Beruflich Dokumente

Kultur Dokumente

78.hysteresis Modulation of Multilevel Inverters

Hochgeladen von

Sravan KumarOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

78.hysteresis Modulation of Multilevel Inverters

Hochgeladen von

Sravan KumarCopyright:

Verfügbare Formate

1396

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 5, MAY 2011

Hysteresis Modulation of Multilevel Inverters

Anshuman Shukla, Member, IEEE, Arindam Ghosh, Fellow, IEEE, and Avinash Joshi

AbstractThe hysteresis modulation for power electronic converters is attractive in many different applications because of its unmatched dynamic response and wide command-tracking bandwidth. Its application and benets for two-level converters are well understood, but the extension of this strategy to multilevel converters is still under development. This paper summarizes and reviews the various hysteresis modulation approaches available in the literature for multilevel converters. The pros and cons of various techniques are described and compared for tracking the reference signal in order to attain an adequate switching optimization, excellent dynamic responses and high accuracy in steady-state operation. By using the recently developed multilevel hysteresis modulation approaches, the advantages of using several accessible dc potentials in a multilevel inverter have been fully exploited. All of these hysteresis modulation approaches are tested for tracking a current reference when applied to a ve-level inverter. The relevant simulation and experimental results are also presented. This study will provide a useful framework and point of reference for the future development of hysteresis modulation for multilevel converters. Index TermsHysteresis modulation, multiband (MB), multioffset band (MOB), multilevel converter, time-based (TB).

Fig. 1.

(a) Two-level half-bridge inverter. (b) Two-level hysteresis control.

the dc link of inverter and their common point (n, neutral point) is grounded. The net controllable output voltage of the inverter is uVdc /2, where u is dened as the control input and represents the switching logic of inverter. It assumes the values +1 and 1 for the two-level inverter of Fig. 1(a). The inverter output voltage van can be represented as follows: uVdc dia = Ria + L + vback (1) 2 dt where ia is the load current, vback is the back EMF voltage, and L and R are the load inductance and resistance, respectively [see Fig. 1(a)]. As vback increases or as larger reference current slopes are required, larger average values of van need to be used. Since the voltage across the load resistance is often small, this value can often be neglected. Introducing a term diref /dt, where iref is the current reference to be tracked, (1) becomes as follows: uVdc /2 vback diref d(ia iref ) . (2) dt L dt It is evident from (2) that the current error (ce = ia iref ) can be reduced by increasing or decreasing van , depending on the polarity of ce . Fig. 1(b) represents the implementation logic for this correct voltage-level selection for a two-level inverter using hysteresis control. It can be seen that as the measured current (ia ) becomes greater than its reference (iref ) by the hysteresis band h, the inverter output voltage (uVdc /2) is switched to its lowest level (Vdc /2, u = 1) in order to decrease the current [according to (1)]. Likewise, when ia becomes less than iref by h, uVdc /2 is switched to its highest level (Vdc /2, u = +1) in order to increase the current. For the inverter of Fig. 1(a), u assumes the value +1 for the switching logic S1 = 1, S2 = 0 and 1 for S1 = 0 and S2 = 1. A three-phase system can also be simply implemented using three independent single-phase hysteresis current regulators. Based on the two-level hysteresis control logic described earlier, the control input u can be dened as follows: van = if (ce (t) +h) , else if (ce (t) h) , then u(t) = 1 then u(t) = +1. (3)

I. INTRODUCTION

HE hysteresis modulation for power electronic converters are preferred for applications, where performance requirements are more demanding such as to achieve good dynamic response, unconditional stability, and wide command-tracking bandwidth [1], [2]. In this approach, the controlled system variable is compared against hysteresis band(s) to create the switching commands for the converter. This control has been widely used to control the conventional two-level converter, showing its robustness and simplicity in a lot of applications [3][13]. A brief description of the standard two-level hysteresis control for output current regulation is presented in the following. The objective of standard two-level hysteresis current control is to switch the converter transistors in such a manner that the converter load current tracks a reference within a specied hysteresis band. Consider a single-phase half-bridge inverter, as shown in Fig. 1(a) for two-level hysteresis current control. In Fig. 1, two dc sources of magnitudes Vdc /2 are considered at

Manuscript received March 2, 2010; revised July 28, 2010; accepted September 9, 2010. Date of current version June 22, 2011. Recommended for Publication by Associate Editor Leon M. Tolbert. A. Shukla is with Power Technology, ABB Corporate Research, Vasteras 72178, Sweden (e-mail: anshuman.shukla@se.abb.com, anshukla@ gmail.com). A. Ghosh is with School of Engineering Systems, Queensland University of Technology, Brisbane 4001, Australia (e-mail: a.ghosh@qut.edu.au). A. Joshi is with Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur 208016, India (e-mail: ajoshi@iitk.ac.in). Color versions of one or more of the gures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identier 10.1109/TPEL.2010.2082001

0885-8993/$26.00 2011 IEEE

SHUKLA et al.: HYSTERESIS MODULATION OF MULTILEVEL INVERTERS

1397

Fig. 2. (a) Five-level cascaded H-bridge inverter. (b) Five-level diode-clamped inverter. (c) Five-level ying capacitor inverter. Fig. 3. MB ve-level hysteresis current control.

It should be noted that h is a suitable hysteresis band, whose size is determined by the maximum allowable switching frequency of the switching devices, as well as the maximum permitted level of current distortion. A low value of h may lead to increased switching actions, henceforth, larger switching losses, while a large value of h may result in increased distortion in the controlled current. Therefore, a tradeoff is always required in designing the hysteresis band size. As only two dc voltage levels are available, the two-level hysteresis control is relatively straightforward with each hysteresis boundary being mapped essentially to one converter-phase-leg switched state. However, for multilevel converters, as a larger number of output voltage levels are available, the task is to select a particular voltage-level output to force the control variable to zero on an instantaneous basis once it exceeds certain bounding limits. Therefore, a multilevel hysteresis modulator (MHM) requires additional logic to select the appropriate voltage level at any time instant so as to conne the control signal within a specied hysteresis band. The starting point toward the design of an adequate MHM could be the following: according to the instantaneous value of the controlled system variable (uc ), the controller should suggest what is the most suitable voltage level required. At any instant, when uc exceeds a hysteresis limit, the next higher (or lower) voltage level should be selected in an attempt to force it within the specied limits. However, this new converter voltage level may not be adequate to return uc to the specied limits. When this happens, the converter should switch to the next higher (or lower as appropriate) voltage level, and the process should cease only when the correct voltage level is selected that reverses the direction of uc . To exemplify it further, one of the standard multilevel inverter topologies, the single-phaseleg ve-level congurations of which are shown in Fig. 2, can be considered [14]. For a ve-level inverter, van in (1) may be dened as van = nVdc , where n = 1/2, 1/4, 0, 1/4, and 1/2, as a ve-level inverter may select between voltage levels Vdc /2, Vdc /4, 0, Vdc /4, and Vdc /2 for the net dc-link voltage of Vdc . Then, in a similar manner as described earlier, ce can be kept limited to a specied band by selecting a higher or lower voltage level than its present output depending on the polarity of ce [15][34].

To implement the logic for correct voltage-level selection, various schemes available in the literature have been described in the following sections on the basis of a single-phase ve-level inverter. In Section II, the multiband (MB) MHM scheme is presented, which has the feature of oating voltage levels at the boundaries of the band with symmetric inner bands placement. In Section III, the multioffset-band (MOB) approach is presented, which allots xed voltage levels at the band boundaries and needs to check the slope as well as the band region of the current error. A modication to this approach is also presented, so that it can be easily extended for higher level inverter systems and tracks the reference more efciently. Further, a time-based (TB) approach for MHM is presented in Section IV, which can be used to put a limit on maximum switching frequency as well as to achieve improved performances. The detailed simulation and experimental results for all these schemes have been presented to validate their functioning. Furthermore, a comparative evaluation of these schemes has been also presented. II. MB HYSTERESIS MODULATION The MB hysteresis modulation scheme for the multilevel converters uses symmetrical hysteresis bands to control the switching so that the inner band causes switching between adjacent levels, while the outer band causes an additional switching level change whenever necessary. The process, rst proposed in [15] and later used in [22], [26], [31], [32], is shown in Fig. 3 in the form of current regulation. Whenever the current error crosses the inner boundary B, the inverter output is decreased or increased by one level (depending on which hysteresis boundary has just been crossed). Generally, this voltage change will cause the current error to reverse its direction without reaching the next outer band. However, if the error does not reverse, it will continue through the boundary of B to the next outer boundary (placed at B out of B). At this point, next higher or lower level voltage will be switched. This process continues as discussed earlier until the current error direction reverses. It is important to note that if the voltage level applied at a boundary crossing of the current error is insufcient to force the error back, no next voltage level is applied as the error again crosses this boundary next time after the previous voltage level change with the same

1398

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 5, MAY 2011

Fig. 4. MB ve-level hysteresis modulation. (a) Current error and hysteresis band plots. (b) Inverter output voltage.

slope. The error in that case is allowed to go until the next voltage level change at next higher or lower boundary crossing of the error to force it back as is evident from Fig. 3. To further illustrate the principle of MB scheme, simulation studies are performed on a ve-level inverter, supplying an RL load of R = 35 and L = 30 mH with the dc-link voltage of 80 V. The back EMF voltage (vback ) is taken as zero and the inverter devices are assumed nearly ideal. The output current of inverter (ia ) is controlled using the MB hysteresis scheme (see Fig. 3) to follow a sinusoidal reference having peak-topeak values of 1.0 A. Corresponding to Fig. 3, the hysteresis band sizes are taken to be B = 0.04 A and B1 = B2 = 0.02 A. These values are taken for simplicity by following the considerations presented in [16]. All the simulation results presented in this paper for hysteresis modulation have been obtained by using the same set of parameters for a ve-level inverter. Fig. 4 shows the simulation results obtained with the MB scheme. It is evident that the error is contained within the allotted bands by the corresponding voltage levels appearing at the output of the inverter. The error trajectory can be similarly followed by referring it from Fig. 3. Fig. 5 shows the simulation results obtained under the same load conditions as earlier, but imposing a current reference of halved amplitude at 45 ms in the simulation run, and thus, testing it for a transient condition. If the rms value of the current required is lower (the load being the same), the rms value of the voltage must be lower. Fig. 5 shows that the control technique is self-adapting in an automatic and natural way; therefore, the converter feeds the load by using the lower voltages levels only [Vdc /4 and 0, Fig. 5(c)]. It is also seen from Fig. 5(c) that as soon as the step reference change occurs, the corresponding extreme voltage level (Vdc /2) appears at output of the inverter to rapidly force the current error back within the specied bands. It should be noted that if the change in reference is not that large, following a step change in the demanded current, the controller will remain in the corresponding switching state required to follow the reference as closely as possible until the current error reaches the hysteresis band. Hence, the advantages of a multilevel topology are fully exploited by this scheme. The fast-

Fig. 5. Transient performance of MB scheme. (a) Current error and hysteresis band plots. (b) Reference and measured load current. (c) Inverter output voltage.

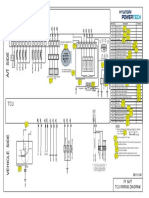

Fig. 6.

Overall structure of the experimental setup.

transient response of the current regulator can be appreciated from the results shown in Fig. 5(b). A. Experimental Setup An experimental setup is used to test the MHM schemes discussed in this paper. A prototype of a single-phase ve-level insulated gate bipolar transistor (IGBT)-based diode-clamped inverter is built in the laboratory. The overall structure of the experimental setup is shown in Fig. 6. The main power circuits consist of a single-phase ve-level voltage source diodeclamped inverter, load, and dc-link circuit. The inverter dc bus is supported by a separately controllable dc supply obtained from a single-phase transformer and diode rectier circuit. The dclink voltage and load parameters of the inverter are kept same as

SHUKLA et al.: HYSTERESIS MODULATION OF MULTILEVEL INVERTERS

1399

considered earlier in the simulation studies, i.e., Vdc = 80 V and R = 35 , L = 30 mH, respectively. In Fig. 6, HV2HV5 denotes the Hall effect voltage transducers for sensing the dc-link capacitor voltages and HC1 represents the Hall effect current transducer sensing the inverter load current (ia ). Each semiconductor switch shown in Fig. 6 consists of an IGBT with an antiparallel diode. The IGBT modules used is Mitsubishi CM75DY-24 H. This is a 1200 V/75 A IGBT with two IGBTs/ diodes in each module. For simplicity, the same IGBT modules are also used as clamping diodes with a shorted gate in the inverter, as shown in Fig. 6. The presence of back EMF would serve to create more variation in switching frequency, but without affecting the nature of the current error trajectory. Therefore, for simplicity, back EMF voltage source has not been used. In the experimental setup, a chopper circuit for the dc capacitor voltages equalization has also been used, as shown in Fig. 6. Its working principles and operational features can be referred from [35]. Without any dedicated control or additional hardware, the dc-link capacitor voltages tend to unbalance under most of the operating conditions in a diode-clamped inverter [35], [36]. This chopper circuit of Fig. 6 keeps the dc-link capacitor voltages balanced so that the inverter is able to generate ve different and correct voltage levels. It is also important to mention here that the chopper action is unaffected by the different hysteresis modulation methods used in this paper. The dc-link capacitors are Cd1 = Cd2 = Cd3 = Cd4 = 220 F and the chopper circuit parameters are R1 = R2 = 2.0 and L1 = L2 = 20 mH. Further structural and operational details of the chopper are not given here as these are not in the context of this paper. In Fig. 6, the block diagram for PC interfacing and other controllers are also shown. The low-voltage signals from the transducers connected to the power circuits are used as inputs to various controllers. The inverter load current signal is acquired by a PC (P1 V, 2.4 GHz) through AD converter (ADC) channels of a standard data acquisition card (NIDAQmx PCI6259) [37]. A sinusoidal reference input (iref ) is also fed through the ADC channels. Based on these quantities, a program written in Borland C++ is implemented for the control tasks. The corresponding switching decision signals are generated at the digital-output port of the DAQ and are passed to the IGBT driver circuits after introducing a lockout delay using blanking circuits. IGBTs require gate voltage signal in order to establish collector to emitter conduction or nonconduction. A singlephase ve-level inverter topology associated with the chopper circuit of Fig. 6 needs 12 gate drivers. Mitsubishi M57959 L hybrid IGBT driver modules are chosen to perform this task. This is a high-speed component that is endowed with a voltage logic-level input and insulated by a high-speed optocoupler that protects against the event of a short circuit [38]. For the MB scheme described earlier, the current reference and hysteresis band sizes are considered same (1.0 A, B = 0.04 A, and B1 = B2 = 0.02 A) as considered earlier in the simulation studies presented. Fig. 7(a) shows the performance of the MB hysteresis current controller. As expected and described earlier corresponding to the simulation results in Fig. 4, the controller is able to keep the current error in the dened hysteresis band. Fig. 7(b) shows the load current along

Fig. 7. Experimental results showing the MB hysteresis modulation performance. (a) Inverter output voltage and current error. (b) Inverter output voltage and controlled load current.

with the output voltage. By comparing the experimental results with those of the simulation results presented earlier, it can be said that the experimental results match closely with the simulation results, as expected. An advantage of this MB hysteresis control is that the (n 1) bands used here for an n-level inverter center about the zeroerror axis. In this case, the average value of the current error approaches zero even when current ripple periods are considered [15]. Therefore, no dc-tracking error is introduced into the output current (no analog offset compensation circuitry required). III. MOB HYSTERESIS MODULATION As opposed to the MB scheme, which uses symmetrically placed hysteresis bands for current error regulation, the MOB scheme uses the bands placed with an offset around the zerocurrent error line. The advantage of using the offsets is that different bands can be easily implemented. Also, the corresponding logic can also be easily programmed/implemented in a way that if the voltage appearing at the boundary of a band is insufcient to force the error back, it is allowed to move to the other band. As opposed to the previously presented scheme, xed voltage levels are applied in MOB scheme as the current error crosses a boundary of the band with a certain slope. In this section, rst the conventional MOB scheme is presented, and then, its modied version is presented, which offers improved performances. A. Conventional MOB Hysteresis Modulation A MOB scheme was proposed in [17] and [26] on the basis of a three-level inverter. In this scheme, the current can be controlled using n 1 offest bands for an n-level inverter. Fixed voltage levels are switched at each of the offset boundaries when the current error crosses the boundary of an offset band in a direction, away from the zero error line. A possible two-offset band arrangement (B1 , B2 ) for controlling a three-level inverter is shown in Fig. 8. It is shown in the gure that as the error (Ce ) touches the corresponding boundaries of B1 and B2 , xed output voltage levels are switched. The switching takes place when sign of the error and its slope at the boundary of a band are same, and the previous switching had not taken place at the same boundary of the same band. For example, positive error and positive slope at p1 and negative error and negative slope

1400

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 5, MAY 2011

Fig. 8.

Three-level MOB hysteresis modulation. Fig. 10. MOB ve-level hysteresis current control with xed voltage applied at the band crossings of the current error. (a) Current error trajectory along with the allotted bands. (b) Inverter switched output voltage.

Fig. 9.

Five-level MOB hysteresis modulation.

at p2 cause the switching (see Fig. 8). It can be followed that 0 voltage level is switched at the inner limits of B1 , B2 , Vdc /2 at the upper limit of B1 , and +Vdc /2 at the lower limit of B2 . It can also be seen from Fig. 8 that the selection of voltage levels for limiting the current error occurs from lower to higher value through a step and without skipping any intermediate level. This conrms an optimized use of the available voltage levels. The MOB scheme seems to work well for a three-level inverter, as it utilizes all the available voltage states in an optimized manner to conne the current error within the limits dened by the outer boundaries (B1 and B2 in Fig. 8). However, if the same scheme with the same logic sequence is applied to any higher level inverter, its optimization is lost [16]. To exemplify it, let us consider a ve-level multioffset hysteresis current regulation with Fig. 9 showing a possible current error trajectory along with the offset-band arrangements and corresponding switched output voltage levels. By following the scheme of [17], it requires four bands (B1 B4 ) and as the current error touches the corresponding boundaries of B1 B4 , xed output voltage levels are switched. It can be followed that 0 V is switched at the lower limits of B1 , B3 and upper limits of B2 , B4 , Vdc /4 at the upper limit of B1 , +Vdc /4 at the lower limit of B2 , Vdc /2 at the upper limit of B3 and +Vdc /2 at the lower limit of B4 . The limitation, when using this scheme for a higher level inverter can be seen by looking at the current error path from F to G. It is evident that a voltage-level transition from Vdc /2 to 0 V occurs at G, thereby, skipping the level Vdc /4. This results in inverter output voltage with large steps and large voltage stress across the devices at the switching instants.

To get a further insight into operational performance of the ve-level hysteresis control of Fig. 9, a simulation study is performed using this scheme with the same inverter parameters, load parameters, reference current value as considered in the previous section and the hysteresis band sizes of B1 = B2 = 0.06 A and B3 = B4 = 0.08 A. Fig. 10 shows the simulation results under this case, where it is evident that this control results in a poor quality voltage waveform. To justify this observation, let us rst focus on the current error trajectory in Fig. 10(a). As suggested earlier, between the points ta and tb , the error variation outputs the voltages 0 and +Vdc /4. As the error moves away from tb , it touches the lower boundary of B1 (see Fig. 10) at tc . By denition, at tc , 0 voltage level is switched. However, before tc , the output voltage was +Vdc /4 and at tc , the error is moving away from the zero line in the negative direction. Therefore, +Vdc /2 was required to force the error in opposite direction. But due to the logical sequence of control, 0 voltage level is applied at tc , resulting in further increase in the negative slope of the current error away from the zero line. The error then touches the lower boundary of B2 , and then, B4 . This results in consecutive switching of +Vdc /4 and +Vdc /2, respectively. This operation is repeated in the consecutive switching cycles and the voltage waveform is degraded. It is also evident that in this process, the intermediate level +Vdc /4 is skipped as the current error travels from tf to the upper boundary of B2 . It should be noted that since the current error remains in the allotted bands, the controlled current follows its reference. It is the voltage waveform, which is degraded. However, as is evident from Fig. 10, the error is bounded within a smaller band (B1 or B2 ) in the region when switching the voltage levels 0 and Vdc /4, while due to the control actions of this scheme, the error is bounded within a larger band (B3 or B4 ) in the region when it is required to output one of the two extreme voltage levels (Vdc /2). This results in variable-tracking performance in a single cycle of the current waveform itself. B. Modied MOB Hysteresis Modulation To overcome the drawbacks of the multilevel control of Fig. 9, a modied MOB (MMOB) hysteresis control is presented [16]. The band placement and functioning of MMOB scheme for a ve-level inverter is shown in Fig. 11. In this scheme, the current error is required to be bounded mainly between the bands B1

SHUKLA et al.: HYSTERESIS MODULATION OF MULTILEVEL INVERTERS

1401

Fig. 12. MMOB ve-level hysteresis modulation. (a) Current error and the hysteresis band plots. (b) Inverter output voltage.

Fig. 11.

MMOB ve-level hysteresis modulation.

and B2 , which are displaced by a small offset B. Further, two additional offsets of the same width B are placed out of B1 and B2 to provide a reliable and robust control. In general, a total number of n 2 offsets are required for an n-level inverter in both the positive- and negative-current-error regions. It differs from the MOB method in the decision logic of output voltage levels at the crossing points of current error and corresponding boundaries of the hysteresis bands and also in the total number of bands required. In the MMOB approach, the applied output voltage at the band crossing points of current error is not xed, but depends on the previous voltage level, i.e., just before the crossing point. In this scheme, the next voltage level is applied if a positive/negative boundary of B1 or B2 or B is crossed with positive/negative slope for the rst time. If this action is insufcient, the error will cross the same boundary second time. In such a situation, no action is taken until the next higher or lower boundary of another band is reached. This reduces the number of switching. If the current error crosses the positive boundary of a band with positive slope, next lower (than the previous) voltage level is switched (e.g., at A in Fig. 11). Similarly, if the error crosses the negative boundary of a band with negative slope, next higher (than the previous) voltage level is switched (e.g., at M in Fig. 11), with the earlier stated constraints applied. The advantage of MMOB method of Fig. 11 over the MOB method is evident in the manner that with MMOB method, output voltage quality is improved and the current follows its reference with minimum change in voltage levels needed. This guarantees that there is no skipping of the intermediate voltage levels. It should also be noted that in this scheme, the number of offset bands is decided by the number of steps needed to switch the voltage from one extreme (+Vdc /2 or Vdc /2) to another extreme (Vdc /2 or +Vdc /2, respectively) as the error travels from positive (negative) to negative (positive) region. This can be further understood by following the error trajectory from M to Q in Fig. 11. Another simulation study is performed using the MMOB scheme with the same inverter parameters as considered earlier and hysteresis band sizes as B1 = B2 = 0.06 A and B = 0.02 A. Fig. 12 shows the results. Similar current error trajectory analysis can be performed in Fig. 12 to justify the better

Fig. 13. Transient performance of MMOB modulation. (a) Current error and hysteresis band plots. (b) Reference and measured currents. (c) Inverter output voltage.

waveforms using the control scheme of Fig. 11. A comparison of Fig. 12 with Fig. 10 shows that in the new scheme, the switching always occurs between adjacent levels and no voltage level is skipped. Also, as opposed to MOB scheme, the currenttracking performance remains uniform throughout a complete load current cycle in MMOB scheme (see Fig. 12), as the current error is mostly bounded within the hysteresis bands of same width. It should be noted that, in Fig. 10, the controller acts as desired when switching between +Vdc /4, 0, and Vdc /4 and degrades when higher voltage levels (Vdc /2) are needed to be switched. This indicates that xed voltage-level switching as in [17] works ne for the three-level inverter and needs modication (as in Fig. 11) for higher level inverters. Fig. 13 shows the simulation results, obtained under the same transient condition, as considered in the previous sections. It is evident from Fig. 13 that the control technique is self-adapting in an automatic and natural way in the same manner as discussed earlier. Hence, the advantages of a multilevel topology are fully exploited by this scheme as well. The fast-transient response of the current regulator can be appreciated from the results shown in Fig. 13(b). As the band sizes are small, it is difcult to distinguish between the load current and the alternating reference [dashed line in Fig. 13(b)], which also conrms that the tracking is exact.

1402

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 5, MAY 2011

Fig. 15.

TB ve-level hysteresis current control.

Fig. 14. Experimental results showing the MOB hysteresis modulation performances. (a) Inverter output voltage and current error with the MOB method. (b) Inverter output voltage and current error with the MMOB method. (c) Load current with the MMOB method. (d) Inverter output voltage and load current with halved hysteresis band sizes and with the MMOB method.

The experimental investigations are carried out to validate the MOB and MMOB schemes with the same experimental setup as discussed in the previous section. The system parameters are same as considered in the simulation studies presented earlier. Fig. 14(a) shows the performance of MOB modulation. As expected and described earlier corresponding to the simulation results in Fig. 10, though the controller is able to keep the current error in the dened hysteresis bands, it suffers from poor inverter output voltage due to skipping of the intermediate voltage levels. Fig. 14(b) and (c) shows the performance of MMOB modulator with the same parameters. In Fig. 14(d), the results show the performance of MMOB modulator with halved values of B and B. Its better performance can be appreciated from the results shown and can be justied from the discussions presented earlier. It should be noted that the load current shown in Fig. 14(c) is almost same with both the MOB and MMOB methods as both are able to limit the error within the specied bands. The experimental results conrm the correctness of simulation and validate the similar behaviors described previously in the simulated cases. It should also be noted that since in both the conditions, the current error is bounded between the allotted limits, the controlled current waveform in all the cases resembles with the one presented in Fig. 14(c). Further, the tracking of the reference load current in the two cases can be conrmed by looking at the current errors presented in Fig. 14(a) and (b). As can be seen from Figs. 814, one disadvantage of this scheme is that the offset placements of the hysteresis bands about zero error introduce a steady-state tracking error. In steady state, the average value of the current error in Fig. 12(a) approaches zero only if the fundamental periods are considered. It does not increase the total harmonic distortion (THD) value of the current, but causes a decrease in the fundamental harmonic component. This problem may become a severe one if more than ve voltage levels are to be employed in which case a nonnegli-

gible phase lag between the load current and its reference may occur [15]. To counteract this dc offset, an offset compensation strategy to ensure zero average current error within each switching period is required for improved performance. Usually, this is achieved by adding a compensating factor of half the hysteresis band offset magnitude to the load current reference [15], [17]. This technique is robust, but has the general limitation of requiring increasingly complex analog circuitry for implementing the multiple hysteresis bands and offset compensation as the number of voltage level increases. Therefore, the MOB hysteresis method has not found wide applications. IV. TB HYSTERESIS MODULATION As discussed earlier, although the MOB schemes are easy to implement [15], it requires offset compensation signals to be added to the controlled system variable, since the bands are not symmetric about zero. The MB scheme, presented earlier in Section II, does not suffer from this steady-state-tracking error problem, but may still not have evenly symmetric current error waveform, especially for nonsinusoidal current references. In the following, a TB MHM is rst described, which works on the principle of controlling the system variable within a single band so that any type of current offset can be avoided. Then, a modied TB approach for MHM is discussed, which shows much better performances in terms of tracking as well as can be used with a limit on the maximum allowable switching frequency. A. TB Multilevel Hysteresis Modulation A TB multilevel hysteresis control scheme was proposed in [15] to use only one hysteresis band to detect an out-ofbounds current error. Digital logic is used to select the correct voltage level in response. Upon detecting the error exceeding the upper (or lower) hysteresis limit, the inverter output is switched down (or up) one voltage level so as to return the error back to zero, as earlier. But if the new inverter switched state is inadequate to reverse the error back to zero, the output is switched further down (or up) until the current-error direction reverses. A possible current error trajectory and inverter switched output for a ve-level inverter are shown in Fig. 15. Referring to Fig. 15, the objective of this method is to force the current error in a manner so that it remains within band B. It is evident that the

SHUKLA et al.: HYSTERESIS MODULATION OF MULTILEVEL INVERTERS

1403

Fig. 16. TB ve-level hysteresis modulation. (a) Current error and the hysteresis band plots. (b) Inverter output voltage.

inverter output is switched one level up or down as the current error touches the boundary of B. If this changed output is insufcient to force the error back toward zero (as at W ), next higher or lower voltage level is switched at the next crossing point of the error and the band limit (as at X). From Fig. 15, it is obvious that the technique does not create the steady-state tracking error of the MOB approach. To improve the performance and robustness of this technique, a current error slope detection algorithm was used in [18] to switch the voltage levels. An outer band was also placed to allow switching to the extreme voltage levels for rapid current error reduction during transient conditions (at B out of B, Fig. 15). An additional band placement was also introduced in [19] for higher level inverters. Further, a lockout delay (TB control) was proposed to be added (in [20]) in the switching process for a xed duration (say, t1 ) immediately after an inverter state changes to compensate for short delay between the generation of gating signals and sensing of the current error and its derivative. This TB approach can be seen in Fig. 15 between the instants Y and Z. It is evident that as the error keeps on increasing even if a voltage level change has occurred at Y , after a certain time delay (t1 , between the instants Y and Z), another voltage level change at Z forces the error in the opposite direction. To further illustrate the principle and functioning of the scheme of Fig. 15, simulation studies are performed using this scheme with the same system conditions as considered earlier and B = 0.04 A and B = 0.02 A. Fig. 16 shows the results obtained. With the system parameters under consideration, it is evident that the current error is conned within band B by selecting the voltage levels one after another in the manner discussed earlier. To look into detail, the functioning of this scheme and observing the TB control, another simulation study is performed with the same parameters and two small-step changes in the reference current magnitude at instants 14.013 ms (tk , Fig. 17) and at 14.23 ms (to , Fig. 17) in the simulation run. The value of xed delay t1 (dened earlier) is taken 0.2 ms. The corresponding results are shown in Fig. 17. It can be seen that at tm , when the current error crosses the boundary of B, the inverter switched output voltage (Vdc /4) is insufcient to force it back within B, and therefore, the error keeps on increasing. However, when the time period for which the error remains outside B with positive slope exceeds t1 , next lower voltage level is

Fig. 17. Control details of the TB hysteresis modulation. (a) Current error and hysteresis band plots. (b) Inverter output voltage. (c) Time interval between consecutive switching instants (in microsecond).

switched to provide extra force on the error to return back [e.g., Vdc /2 is switched at tn in Fig. 17 (c)]. In this way, the TB control is operative to control the current using the n number of available voltage levels for an n-level inverter. Now, at to , when a relatively larger change in reference magnitude is imposed, the current error comes out of the dened outer band at tp [see Fig. 17 (a)]. As stated earlier, this outer boundary at B below B is placed to allow switching to the extreme voltage levels for rapid current error reduction during transient conditions. Therefore, as can be seen from Fig. 17 (b), the extreme positive voltage level (+Vdc /2) is switched at tp to rapidly force the error back within B. The resulting error trajectory can be similarly analyzed as detailed earlier. Although the technique of [15] with the improvements of [18][20] offers good performance, it needs to be further modied for better performance under all loading conditions and for very narrow hysteresis band sizes. Under certain loading conditions and/or for very narrow hysteresis band sizes, the current error variations are rapid. In these cases, the error may not reverse suddenly at the boundaries of B (if it has to), but may take some nite time (say, t2 ) depending on the applied voltage level, hysteresis band size, and the load parameters. This type of phenomena may also occur under synchronous detuning problem, which may occur in hysteresis control operation [21]. For these cases, let us suppose t3 be the time interval for which the current error slope is positive (or negative). Now, if t3 is more than the xed delay t1 (dened earlier), the next higher or lower voltage level is switched after t1 according to the switching logic of [20]. This means that unnecessary voltage-level transition has taken place as the voltage level appearing just at the boundary of B was sufcient enough to force the current error direction (though, after t2 ). Therefore, it can be said that the current error slope detection with TB control may affect the hysteresis controller performance depending on various factors. A possible solution is to set a value of xed delay t1 , which is large enough for any t3 . This means that the switching process is ceased for a large t1 , each time after the inverter output voltage is

1404

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 5, MAY 2011

Fig. 18.

Modied TB ve-level hysteresis current control.

switched. However, the value of t1 is required to be tuned based on the parameters of the selected sensing device and differentiator logic [20]. Further, it has to be sufciently small considering the size of B (e.g., for the case when the error moves from the boundary of B toward outer boundaries at B, Fig. 15). These considerations result in a very small value of t1 . Therefore, for varying load and under high-switching frequency operation, this is not a reliable solution. Another limitation of this scheme is that the two processes: 1) ceasing of the switching process for t1 after a voltage level change at B and 2) switching the voltage level if the current error slope is still positive (negative) after t1 from a voltage level change at B, are locked through t1 . Since t1 is mostly dependent upon sensor parameters (which are xed) and the current error slope is mostly load dependent (which can vary), the approach certainly lacks robustness. Further, since this approach needs to measure the derivative of the current error, noise amplication may occur at the sensing end of the controller, which needs extra hardware to lter it out [20]. B. Modied TB Hysteresis Modulation To counter the limitations of the aforementioned TB scheme, an efcient modied TB multilevel hysteresis control scheme was proposed in [16] and is shown in Fig. 18. This approach requires (n 2) outer bands at B from their inner ones for an n-level inverter. Further, the current error slope-detection-based control (of [20]) is replaced by the algorithm of detection of only sign of the current error slope. The use of extra bands in the modied scheme implies that, for example, if the current error crosses B with a certain voltage switched at the boundary of B, the next voltage level will not be switched until the error touches the outer band at B from B. By doing so, the situation like that discussed in the earlier paragraph can be clearly avoided for a sufcient width of B. The TB control, however, is retained in the control process, though, for a different purpose. This is for the case when the two consecutive crossings of the current error and the band limits are too small timewise. For example, as shown in Fig. 18, the time interval between the instants P and Q is considered smaller than t1 , and therefore, another voltage level change does not occur at Q. Subsequently, the

error reaches at S so that a change in voltage level causes its reversal. Therefore, in effect, this method replaces the current error derivative detection control by a number of xed-width bands. Dening the modied scheme of Fig. 18 with respect to the method of Fig. 15, it can be said that, the modied method replaces the combined monitoring of the vertical movement of the current error and horizontal movement of the time (of [20]) by only the single monitoring of the vertical movement of the current error in deciding to switch the next voltage level out of B. This replacement is logical as the main aim of all the hysteresis control remains to check the vertical movement of the error (i.e., away from the zero current error line). The switching decisions are taken only at the boundaries of the bands when the current error moves away from the zero line. At each such crossing, the inverter output is changed by one step (e.g., from 0 to +Vdc /4, or to Vdc /4, etc.). In the lower boundary regions, the output voltage state changes from lower to higher (i.e., Vdc /2 to Vdc /4, Vdc /4 to 0, 0 to +Vdc /4, and +Vdc /4 to +Vdc /2) and in the upper boundary regions, from higher to lower (i.e., Vdc /2 to Vdc /4, Vdc /4 to 0, 0 to Vdc /4, and Vdc /4 to Vdc /2). At the outermost boundaries, the corresponding extreme output voltage levels (+Vdc /2 and Vdc /2) are applied for rapid current error reduction during transient conditions. These voltagelevel transitions ensure that the controlled current follows its reference with minimum control force needed. The switching strategy can be further understood from Fig. 18. At point M , the current error crosses the lower boundary of B. Before this point, the output voltage state was Vdc /2. Therefore, the next higher voltage level (Vdc /4) is applied at M . The current error then follows the path as shown, and at the crossing points shown in the gure (i.e., N , etc.), voltage state transition takes place as mentioned earlier. A total number of (n 1) bands required for an n-level inverter in this scheme can be justied by following the current error trajectory in Fig. 18 and the discussions presented in the earlier presented schemes. It is also clear that it can efciently work under varying load conditions as well. Based on the earlier discussion, the switching decisions under this scheme can be dened with respect to Fig. 18 for an n-level inverter as follows: if Ce 0 and else if Ce < 0 and dCe 1 > 0 , then u(tk ) = u(tk 1 ) + dt n1 dCe 1 < 0 , then u(tk ) = u(tk 1 ) . dt n1 (4) In (4), u(tk ) is the current value of the switching decision, while u(tk 1 ) is its immediate past value. This can be justied from Fig. 18 in which, tk 1 , tk , etc., shown on the horizontal axis are the time instants at which Ce crosses the earlier dened boundaries of the bands. It can be seen that depending on the sign of Ce and dCe /dt, the output voltage level is either increased or decreased by Vdc /4, at the crossing points. Note that, the inverter holds its output voltage level until tk , which it attained at tk 1 . It is also to be noted that with Ce > 0, dCe /dt < 0, and with Ce < 0, dCe /dt > 0, no voltage transition takes place

SHUKLA et al.: HYSTERESIS MODULATION OF MULTILEVEL INVERTERS

1405

Fig. 19. Modied TB ve-level hysteresis current control. (a) Current error and hysteresis band plots. (b) Inverter switched output voltage.

at the crossing points. This is because, in these regions, the control signal is heading toward zero line, which implies that the error between the controlled current and its reference value is reducing with the present output voltage level. Hence, no voltage transition is required for this. Another point to be noted is that, no exact evaluation is needed for the current error slope, as only the sign of the current error slope is needed at its crossing points with the band limits. At each sampling instant in the measurement process, the current value of the error is compared with its previous value. A positive value of this difference indicates a positive slope, while the negative value indicates a negative slope [16]. Therefore, this scheme does not suffer from noise amplication problem as in [20]. To get further insight into the modied TB scheme of Fig. 18 and exemplify its working, simulation studies are performed on a ve-level inverter with the current reference and inverter, and load parameters being the same as considered earlier and with hysteresis band sizes of B = 0.04 A and B = 0.02 A. The value t1 (delay in the TB control) is taken to be 200 s. This value of t1 is purposely taken to be almost equal to the minimum time interval between two consecutive switching decisions under the given system conditions to have a better viewing of the controller performance. The simulated waveforms are shown in Fig. 19. The current error variation across the hysteresis bands can be followed from the discussions presented earlier corresponding to Fig. 18. It is evident that at tq , the error touches the upper boundary of B and the voltage level +Vdc /4 is switched at the output of inverter to force the error in the opposite direction. However, at tr , when the error crosses the lower boundary of B, the next higher voltage level is not switched as the time interval between the instants tq and tr is less than t1 = 200 s. Therefore, the error crosses B at tr and is forced back in the opposite direction at ts , i.e., at B from the lower boundary of B, where voltage level +Vdc /2 is switched. In this way, the current is controlled to follow its reference by using the four bands for a ve-level inverter and a ve-level output voltage waveform is obtained [see Fig. 19(b)] for a sinusoidal reference current. It is evident from Fig. 19(a) that the TB control is also operative in this scheme, e.g., between tq and tr . It should be noted that in this scheme, the time differences between two consecutive switching is checked each time before a next voltage level is

Fig. 20. Control details of modied TB scheme. (a) Current error and hysteresis band plots. (b) Inverter output voltages. (c) Time interval between consecutive switching instants (in microsecond).

applied to have a TB control. Further, the tuning of t1 along with B and B should be properly done to have a good harmonic spectrum of the controlled current and voltage, while also taking into consideration the maximum allowable switching frequency. This TB control applied to control the current in this scheme can also be applied to the other schemes discussed in previous sections. To look into detail, the functioning of this scheme and observe its operation under a transient condition, another simulation study is performed with the same parameters and a small-step change in the reference current magnitude at instant 8.4 ms. (say, tt ) in the simulation run. The value of t1 is taken 40 s. The corresponding results are shown in Fig. 20. It can be seen that as the current error comes out of the outermost boundary following a step change in reference magnitude, the corresponding extreme voltage level Vdc /2 is switched to rapidly force the error within the band limits. However, the next higher voltage level Vdc /4 switched at tu is insufcient to force the error back. Therefore, it keeps on increasing and crosses the next boundary at tv . However, no other voltage-level switching takes place at tv as the time interval between tu and tv is less that t1 = 40 s [see Fig. 20(c)]. Therefore, the error keeps on increasing and even the next higher voltage level 0, switched at tw , is insufcient to force the error back toward B. As a result, the error touches the next allotted boundary at tx and here, the switched voltage +Vdc /2 forces it back toward B. After this, the consecutive control actions are processed as detailed earlier. In this way, the n number of output voltage levels control the current to track its reference using the allotted hysteresis band regions. It should again be noted that the relatively larger values of t1 in these simulation studies are correspondingly taken to highlight the TB control. In practice, its minimum possible value is limited only by the factors discussed earlier. Fig. 21 shows the simulation results, obtained under the same transient condition, as considered in the previous sections with the same inverter and load parameters. It is again evident from Fig. 21 that the control technique is self-adapting in an automatic and natural way in the same manner as discussed earlier. Hence,

1406

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 5, MAY 2011

Fig. 21. Transient performance of modied TB scheme. (a) Current error and the hysteresis band plots. (b) Reference and measured load current. (c) Inverter output voltage.

Fig. 23. Experimental results of TB ve-level hysteresis modulation with larger band sizes. (a) Inverter output voltage and current error. (b) Inverter output voltage and load current. (c) Inverter output voltage and time interval between consecutive switchings.

than t1 . Hence, the error had to cross B and next voltage level change takes place at pZ , i.e., at B from the lower boundary of B. The corresponding time intervals between consecutive switching instants are shown in Figs. 22(c) and 23(c). As detailed earlier, this value is checked each time before a next voltage level is applied to have a TB control. By comparing the experimental results of Fig. 22 with those of the simulation results presented in the previous section, it can be said that the experimental results matches closely with the simulation results as expected. V. COMPARISON OF THE MHM SCHEMES

Fig. 22. Experimental results of TB ve-level hysteresis modulation with smaller band sizes. (a) Inverter output voltage and current error. (b) Inverter output voltage and load current. (c) Inverter output voltage and time interval between consecutive switchings.

the advantages of a multilevel topology are fully exploited by this scheme as well. The experimental investigations are carried out to validate the TB modulation schemes with the same experimental setup as detailed in the previous sections. The system parameters are same as considered in the simulation studies corresponding to Figs. 19 and 20. In Fig. 22, the experimental results correspond to the hysteresis band sizes of B = 0.04 A and B = 0.02 A as considered earlier, while in Fig. 23, the results correspond to B = 0.06 A and B = 0.03 A. The results have been obtained with two different band sizes to generalize the performance evaluation. It is evident from the gures that the current control is achieved by using the ve voltage levels in the manner discussed earlier. The value of t1 = 200 s is taken to be the same as used in the simulation studies. It can be seen from Fig. 23(a) that the TB control is also operative as the time interval between the band crossing of the current error at pX and pY is less

In the previous sections, various methods for hysteresis modulation of multilevel converters have been described. As discussed earlier, though the implementation of MOB method is easier, it introduces a steady-state tracking error due to the offset placements of the hysteresis bands. This limitation is particularly more severe in the higher level inverters. To counteract this dc offset, an offset compensation strategy to ensure zero average current error within each switching period is required for improved performance [15]. The MOB technique is robust, but has the general limitation of requiring increasingly complex analog circuitry for implementing the multiple hysteresis bands and offset compensation as the number of voltage level increases [15]. Further, the conventional MOB method has the limitation of skipping of the intermediate voltage level between two successive switching for higher level inverter. The MMOB method, however, does not suffer from this limitation and can be applied to higher level inverter system as well. However, due to its main limitation of introducing the steady-state tracking error, the MOB method has not found wide applications. The MB scheme uses symmetric bands to control the control variable and has the advantage that it does not create any dctracking error, and therefore, no analog offset compensation circuitry is required as opposed to the MOB scheme. However,

SHUKLA et al.: HYSTERESIS MODULATION OF MULTILEVEL INVERTERS

1407

it may require a more complex digital circuitry to select a voltage level when a change is required [15]. This is because it needs to classify the previous crossing point of the current error with the boundary of the allotted band, each time at such crossing points. For example, by referring to Figs. 14 and 15, it can be seen that when the current error reaches a boundary of the allotted band with the previous crossing point being on the same boundary, no voltage-level switching takes place. In this case, the error travels to another higher or lower boundary placed at B from the boundary in question to change the output voltage level. However, if the previous crossing point had occurred at a different boundary, the voltage-level switching takes place. Therefore, this method is required to store the information of previous crossing point, which may require additional logical circuitry. However, with the various advanced logical device available, it may be programmed easily. Further, in this scheme, the current error waveform may still not be evenly symmetric, especially for nonsinusoidal current references. This is because, as is evident from Fig. 15, at each transfer of the output voltagelevel zone [e.g., from 0, +Vdc /4 to +Vdc /4, and +Vdc /2 in Fig. 15 (b)], the current error moves out of the inner band to the outer band for next voltage level change [see Fig. 15 (a)]. Due to this, a nonsinusoidal or changing current reference may introduce a net positive or negative shift in the current error, and therefore, in the controlled current. The TB method utilizes a single band to control the current as discussed earlier. It does not suffer from dc-tracking error problem but does require extra analog and digital circuitry for current error measurement as well as to apply the TB control [16]. The modied TB approach, however, does not need to measure the current error, and therefore, does not suffer from noise amplication problem. Depending on the available number of output-phase voltage levels of the inverter, it requires a number of bands, but with the aim of containing the current error within the main band, i.e., the innermost band only. It also does not need to store the information of previous crossing point, as opposed to the MB scheme. Therefore, the additional logical or analog circuitry requirement is minimal. Furthermore, the maximum possible switching frequency may be set by correspondingly designing the width of hysteresis band. The modied TB scheme keeps track of the switching duration between successive switchings and may be designed to always keep it larger than a certain allowed value. This modied TB control can be applied to the other multilevel hysteresis schemes as well [16]. The implementation of this TB control may be achieved by using a time counter with a programmable logic device or by programming it within a computer program itself, as used in this paper. A summary of the advantages and limitations of various multilevel hysteresis regulation schemes presented in this paper is given in Table I. To compare the tracking performances of the various schemes, simulation studies are performed with the same system congurations and parameters as taken in the simulation studies presented earlier in this section. For achieving comparable performances, the hysteresis band sizes are taken B = 0.12 A and B = 0.06 A for the TB scheme of Fig. 18, which is three times as used in the earlier presented simulation studies.

TABLE I ADVANTAGES AND LIMITATIONS OF THE VARIOUS MHM SCHEMES

The corresponding hysteresis band sizes for the MOB scheme is taken B1 = B2 = 0.12 A and B3 = B4 = 0.18 A and for the MB scheme is B = 0.12 A and B = 0.06 A. It should be noted that the main band for the current error regulation is taken of same widths in these three cases. The simulation studies show the percent THD values of the controlled current is 5.45% using the MOB scheme, 5.54% using the MB scheme, and 4.2% using the TB scheme. The better quality of the controlled current using the TB scheme is obvious, as it controls the current error mainly within a single symmetrically placed hysteresis band. Therefore, and also due to its various other advantages as detailed earlier, the TB control of Fig. 18 is recommended. VI. CONCLUSION This paper summarizes and reviews the various hysteresis modulation techniques available in the literature for the multilevel converters. This includes, in general, the MB, MOB, and TB hysteresis modulation techniques. To generalize the existing MHM techniques for higher level inverters, their modied versions have been also discussed. The basic principle of operation and logical sequence of the design choices has been described for each of these schemes. The advantages of using various accessible dc voltage levels have been fully exploited by using these schemes. The various schemes considered in this paper have been further investigated using simulation and experimental studies for a ve-level inverter system. However, these strategies can easily be extended to any multilevel inverter structure, even in the case of n-level voltage waveforms and three-phase systems. This paper also presents a comparative analysis of the various MHM schemes. Among these schemes, the modied TB

1408

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 26, NO. 5, MAY 2011

scheme offers a number of advantages in terms of better tracking performance, extra control over maximum allowable switching frequency, etc. It can be expected that with further investigation of the MHM methods and the development of modern technology, the hysteresis modulation will gain more popularity for controlling the multilevel converters in different applications. REFERENCES

[1] M. P. Kazmierkowski and L. Malesani, Current control techniques for three-phase voltage-source PWM converters: A survey, IEEE Trans. Ind. Electron., vol. 45, no. 5, pp. 691703, Oct. 1998. [2] S. R. Bowes and D. Holliday, Optimal regular-sampled pwm inverter control techniques, IEEE Trans. Ind. Electron., vol. 54, no. 3, pp. 1547 1559, Jun. 2007. [3] M.-C. Wong, Z.-Y. Zhao, Y.-D. Han, and L.-B. Zhao, Three-dimensional pulse-width modulation technique in three level power inverters for threephase four-wired system, IEEE Trans. Power Electron., vol. 16, no. 3, pp. 418427, May 2001. [4] J. Rodriguez, J. Pontt, C. A. Silva, P. Correa, P. Lezana, P. Cortes, and U. Ammann, Predictive current control of a voltage source inverter, IEEE Trans. Ind. Electron., vol. 54, no. 1, pp. 495503, Feb. 2007. [5] P. N Tekawani, R. S. Kanchan, and K. Gopakumar, Novel current error space phasor based hysteresis controller using parabolic bands for control of switching frequency variations, IEEE Trans. Ind. Electron., vol. 54, no. 5, pp. 26482656, Oct. 2007. [6] A. Schild, J. Lunze, J. Krupar, and W. Schwarz, Design of generalized hysteresis controllers for dc-dc switching power converters, IEEE Trans. Power Electron., vol. 24, no. 1, pp. 138146, Jan. 2009. [7] M. A. M. Radzi and N. A. Rahim, Neural network and bandless hysteresis approach to control switched capacitor active power lter for reduction of harmonics, IEEE Trans. Ind. Electron., vol. 56, no. 5, pp. 14771484, May 2009. [8] M. K. Mishra and K. Karthikeyan, An investigation on design and switching dynamics of a voltage source inverter to compensate unbalanced and nonlinear loads, IEEE Trans. Ind. Electron., vol. 56, no. 8, pp. 2802 2810, Aug. 2009. [9] B. Singh and J. Solanki, An implementation of an adaptive control algorithm for a three-phase shunt active lter, IEEE Trans. Ind. Electron., vol. 56, no. 8, pp. 28112820, Aug. 2009. [10] Z. Yao, L. Xiao, and Y. Yan, Dual-buck full-bridge inverter with hysteresis current control, IEEE Trans. Ind. Electron., vol. 56, no. 8, pp. 31533160, Aug. 2009. [11] V. George and M. K. Mishra, Design and analysis of user-dened constant switching frequency current-control-based four-leg dstatcom, IEEE Trans. Power Electron., vol. 24, no. 9, pp. 21482158, Sep. 2009. [12] X. Mao, R. Ayyanar, and H. K Krishnamurthy, Optimal variable switching frequency scheme for reducing switching loss in single-phase inverters based on time-domain analysis, IEEE Trans. Power Electron., vol. 24, no. 4, pp. 9911001, Apr. 2009. [13] B. S. Chen and G. Joos, Direct power ow of active lters with averaged switching frequency regulation, IEEE Trans. Power Electron., vol. 23, no. 6, pp. 27292737, Nov. 2008. [14] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo, M. A. M. Prats, and M. A. Perez, Multilevel inverters: An enabling technology for high-power applications, Proc. IEEE, vol. 97, no. 11, pp. 17861817, Nov. 2009. [15] M. Marchesoni, High performance current control techniques for applications to multilevel high-power voltage source inverters, IEEE Trans. Power Electron., pp. 189204, vol. 7, no. 1, Jan. 1992. [16] A. Shukla, A. Ghosh, and A. Joshi, Improved multilevel hysteresis current regulation and capacitor voltage balancing schemes for ying capacitor multilevel inverter,, IEEE Trans. Power Electron., vol. 23, no. 2, pp. 518 529, Mar. 2008. [17] G. H. Bode and D. G. Holmes, Implementation of three level hysteresis current control for a single phase voltage source inverter, in Proc. IEEE PESC, 2000, pp. 3338. [18] G. H. Bode, D. N. Zmood, P. C. Loh, and D. G. Holmes, A novel hysteresis current controller for multilevel single phase voltage source inverters, in Proc. IEEE PESC01, pp. 18451850. [19] A. Shukla, A. Ghosh, and A. Joshi, Hysteresis current control operation of ying capacitor multilevel inverter and its application in shunt compensation of distribution Systems, IEEE Trans. Power Del., vol. 22, no. 1, pp. 396405, Jan. 2007.

[20] P. C. Loh, G. H. Bode, D. G. Holmes, and T. A. Lipo, A time-based double band hysteresis current regulation strategy for single phase multilevel inverters, IEEE Trans. Ind. Appl., vol. 39, no. 3, pp. 883892, May/Jun. 2003. [21] H. Kanaan, K. A. Haddad, R. Chaffai, L. Duguay, and F. Fnaiech, A comparative study of hysteresis and PWM control techniques applied to an injection-current-based three-phase rectier, in Proc. Can. Conf. Electr. Comp. Eng., vol. 2, 2001, pp. 785792. [22] F. Zare and G. Ledwich, A hysteresis current control for single phase multilevel voltage source inverters: PLD implementation, IEEE Trans. Power Electron., vol. 17, no. 5, pp. 731738, Sep. 2002. [23] O. Vodyakho and C. C. Mi, Three-level inverter based shunt active power lter in three-phase three-wire and four-wire systems, IEEE Trans. Power Electron., vol. 24, no. 5, pp. 13501363, May. 2009. [24] O. Kukrer, H. Komurcugil, and A. Doganalp, A three-level hysteresis function approach to the sliding-mode control of single-phase ups inverters, IEEE Trans. Ind. Electron., vol. 56, no. 9, pp. 34773486, Sep. 2009. [25] S. Srikanthan, M. K. Mishra, and R. K. V. Rao, Improved hysteresis current control of three-level inverter for distribution static compensator application, in Proc. IET Power Electron., vol. 2, Sep. 2009, pp. 517526. [26] P. C. Loh, G. H. Bode, and P. C. Tan, Modular hysteresis current control of hybrid multilevel inverters, in Proc. IEE Electric. Power Appl., vol. 152, Jan. 2005, pp. 18. [27] P. N. Tekwani, R. S. Kanchan, and K. Gopakumar, Current-error spacevector-based hysteresis PWM controller for three-level voltage source inverter fed drives, in Proc. IEE Electric. Power Appl., vol. 152, Sep. 2005, pp. 12831295. [28] H. I. Eini, J. L. Schanen, S. Farhangi, and J. Roudet, A modular strategy for control and voltage balancing of cascaded h-bridge rectiers, IEEE Trans. Power Electron., vol. 23, no. 5, pp. 24282442, Sep. 2008. [29] P. R. Sanchez and E. Acha, Dynamic voltage restorer based on ying capacitor multilevel converters operated by repetitive control, IEEE Trans. Power Del., vol. 24, no. 2, pp. 951960, Apr. 2009. [30] M. Aime, G. Gateau, and T. A. Meynard, Implementation of a peakcurrent-control algorithm within a eld-programmable gate array, IEEE Trans. Ind. Electron., vol. 54, no. 1, pp. 406418, Feb. 2007. [31] R. Gupta, A. Ghosh, and A. Joshi, Cascaded multilevel control of DSTATCOM using multi-band hysteresis modulation, in Proc. IEEE Power Eng. Soc. General Meet., Jun. 2006, pp. 17. [32] R. Gupta, A. Ghosh, and A. Joshi, Switching characterization of cascaded multilevel-inverter-controlled systems, IEEE Trans. Ind. Electron., vol. 55, no. 3, pp. 10471058, Mar. 2008. [33] J. D. Barros and J. F. Silva, Optimal predictive control of three-phase npc multilevel converter for power quality applications, IEEE Trans. Ind. Electron., vol. 55, no. 10, pp. 36703681, Oct. 2008. [34] F. Zare, S. Zabihi, and G. F. Ledwich, An adaptive hysteresis current control for a multilevel inverter used in an active power lter, in Proc. Europ. Conf. on Powe Electron. and Appl., 2007, [CD ROM], pp. 18. [35] A. Shukla, A. Ghosh, and A. Joshi, Control schemes for dc capacitor voltages equalization in diode-clamped multilevel inverter based dstatcom, IEEE Trans. Power Del., vol. 23, no. 2, pp. 11391149, Apr. 2008. [36] N. Hatti, K. Hasegawa, and H. Akagi, A 6.6-kV transformerless motor drive using a ve-level diode-clamped pwm inverter for energy savings of pumps and blowers, IEEE Trans. Power Electron., vol. 24, no. 3, pp. 796803, Mar. 2009. [37] NI DAQmx PCI-6259 User Manual, National Instruments, Austin, TX, 2005. [38] Hybrid ICs M57959 L Datasheet, Mitsubishi, Cypress, CA, 1998.

Anshuman Shukla (S04M09) received the B.Sc. Eng. degree in electrical engineering from Muzaffarpur Institute of Technology, Muzaffarpur, India, in 2001, and the M.Tech. and Ph.D. degrees in electrical engineering from Indian Institute of Technology Kanpur, Kanpur, India, in 2003 and 2008, respectively. Since September 2008, he has been with ABB Corporate Research, Vasteras, Sweden. In 2008, he was a Research Associate in the Department of Electrical Engineering, University of South Carolina, Columbia. His current research interests include modulation and control of power electronic converters and new converter topologies.

SHUKLA et al.: HYSTERESIS MODULATION OF MULTILEVEL INVERTERS

1409

Arindam Ghosh (S80M83SM93F06) received the Ph.D. degree in electrical engineering from the University of Calgary, Calgary, AB, Canada, in 1983. He is currently a Professor of power engineering with Queensland University of Technology, Brisbane, Australia. From 1985 to 2006, he was with the Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur, India. His research interests include control of power systems and power electronic devices. Dr. Ghosh is a Fellow of the Indian National Academy of Engineering.

Avinash Joshi received the Ph.D. degree in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 1979. He is currently a Professor of electrical engineering at the Indian Institute of Technology Kanpur, Kanpur, India. From 1970 to 1973, he was with the General Electric Company of India Ltd., Calcutta, India. His research interests include power electronics, circuits, digital electronics, and microprocessor systems.

Das könnte Ihnen auch gefallen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetVon EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNoch keine Bewertungen

- BuckConverter Design Jpe10Dokument13 SeitenBuckConverter Design Jpe10joviflocasNoch keine Bewertungen

- A Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InverterDokument10 SeitenA Very High Frequency DC-DC Converter Based On A Class Pfi Resonant InvertererdemsecenNoch keine Bewertungen

- ST Company Presentation PDFDokument48 SeitenST Company Presentation PDFChao DongNoch keine Bewertungen

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetVon EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetBewertung: 2 von 5 Sternen2/5 (1)

- Phase Shifting TransformersDokument9 SeitenPhase Shifting TransformersAnonymous 7vSl1eAsEL100% (1)

- Voltage Regulation at Sites With Distributed GenerationDokument10 SeitenVoltage Regulation at Sites With Distributed GenerationpetarlNoch keine Bewertungen

- Cascaded Theory - FullDokument14 SeitenCascaded Theory - FullTJPRC PublicationsNoch keine Bewertungen

- UPEC2010 Review Voltage Control Techniques Networks Distributed Generations OLTC TransformersDokument6 SeitenUPEC2010 Review Voltage Control Techniques Networks Distributed Generations OLTC Transformersstrange_kid82Noch keine Bewertungen

- Electrical Document ReviewDokument15 SeitenElectrical Document ReviewJoselito Peñaranda Cruz Jr.Noch keine Bewertungen

- Iot Based Home Automation Using Android and Nodemcu 190421142053Dokument26 SeitenIot Based Home Automation Using Android and Nodemcu 190421142053Anvit NegiNoch keine Bewertungen

- Multilevel Dynamic Voltage RestorerDokument6 SeitenMultilevel Dynamic Voltage RestorerDinesh ChandraNoch keine Bewertungen

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDokument12 SeitenDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNoch keine Bewertungen

- Naresh DC Re Injection FinalDokument6 SeitenNaresh DC Re Injection FinalRamu ThommandruNoch keine Bewertungen

- Harmonic and Loss Analysis of Space-Vector Modulated ConvertersDokument6 SeitenHarmonic and Loss Analysis of Space-Vector Modulated Convertersahmet ozturkNoch keine Bewertungen

- Feed-Forward Space Vector Modulation For Single-Phase Multilevel Cascaded Converters With Any DC Voltage RatioDokument11 SeitenFeed-Forward Space Vector Modulation For Single-Phase Multilevel Cascaded Converters With Any DC Voltage RatiosatydeshNoch keine Bewertungen

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDokument5 SeitenImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNoch keine Bewertungen

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDokument6 SeitenMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadNoch keine Bewertungen

- Design and Implementation of An Observer Controller For A Buck ConverterDokument11 SeitenDesign and Implementation of An Observer Controller For A Buck ConverterLee DonghyeeNoch keine Bewertungen

- A Survey On Neutral Point Clamped Multi Level InverterDokument12 SeitenA Survey On Neutral Point Clamped Multi Level InverterrupaNoch keine Bewertungen

- Electrical - Ijeeer - 16 - Cell Back-To-back - NaveenaDokument12 SeitenElectrical - Ijeeer - 16 - Cell Back-To-back - NaveenaTJPRC PublicationsNoch keine Bewertungen

- Cascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementDokument5 SeitenCascaded 5-Level Inverter Type Dstatcom For Power Quality ImprovementSiri SarojaNoch keine Bewertungen

- Design, Simulation and Implementation of An Adaptive Controller On Base of Artificial Neural Networks For A Resonant DC-DC ConverterDokument4 SeitenDesign, Simulation and Implementation of An Adaptive Controller On Base of Artificial Neural Networks For A Resonant DC-DC Converterbacuoc.nguyen356Noch keine Bewertungen

- A Generalized State-Space Averaged Model of The Three-Level NPC Converter For Systematic DC Voltage BalancerDokument10 SeitenA Generalized State-Space Averaged Model of The Three-Level NPC Converter For Systematic DC Voltage Balancersherif_helmyNoch keine Bewertungen

- Design and Implementation of Parallel Connected DC-DC Buck ConvertersDokument6 SeitenDesign and Implementation of Parallel Connected DC-DC Buck ConvertersIJARTETNoch keine Bewertungen

- THD Reduction in Multilevel Inverters Using Real-Time AlgorithmDokument12 SeitenTHD Reduction in Multilevel Inverters Using Real-Time AlgorithmInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Analysis of An Asymmetric Modulation Method For Cascaded Multilevel InvertersDokument12 SeitenAnalysis of An Asymmetric Modulation Method For Cascaded Multilevel InvertersJoshua RealsteelNoch keine Bewertungen

- Seven-Level Shunt Active Power Filter For High-Power Drive SystemsDokument8 SeitenSeven-Level Shunt Active Power Filter For High-Power Drive SystemsDivya KoundinyaNoch keine Bewertungen

- Trubitsyn High Efficiency ECCEDokument8 SeitenTrubitsyn High Efficiency ECCEprabu2991991Noch keine Bewertungen

- Critical Bandwidth For The Load Transient Response of VRMDokument8 SeitenCritical Bandwidth For The Load Transient Response of VRMharis13harisNoch keine Bewertungen

- Conv DC-DC Paper ENglishDokument5 SeitenConv DC-DC Paper ENglishpepe890305Noch keine Bewertungen

- (IJET-V1I6P3) Authors:Bachwad M.R., Maske Ashadeep MDokument4 Seiten(IJET-V1I6P3) Authors:Bachwad M.R., Maske Ashadeep MInternational Journal of Engineering and TechniquesNoch keine Bewertungen

- Generalized Frequency Domain Formulation of The Switching Frequency For Hysteresis Current Controlled VSI Used For Load CompensationDokument10 SeitenGeneralized Frequency Domain Formulation of The Switching Frequency For Hysteresis Current Controlled VSI Used For Load CompensationRaja SekarNoch keine Bewertungen

- SPWM With Variable Carrier Synchronization for Multilevel InvertersDokument6 SeitenSPWM With Variable Carrier Synchronization for Multilevel InvertersDevendra HoleyNoch keine Bewertungen

- VX Ring Suppression: Current Sensor ADokument2 SeitenVX Ring Suppression: Current Sensor AVijyashree IyerNoch keine Bewertungen

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDokument12 SeitenLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadNoch keine Bewertungen

- Modelado DC DCDokument8 SeitenModelado DC DCAndrés Vanegas GuillénNoch keine Bewertungen

- Phase Current Unbalance Estimation in Multiphase Buck ConvertersDokument7 SeitenPhase Current Unbalance Estimation in Multiphase Buck ConvertersiMiklaeNoch keine Bewertungen

- Ee 328 Lecture 11Dokument55 SeitenEe 328 Lecture 11somethingfornowNoch keine Bewertungen

- Multistring Five-Level Inverter With Novel PWMDokument13 SeitenMultistring Five-Level Inverter With Novel PWMsandeepbabu28Noch keine Bewertungen

- (22559159 - Electrical, Control and Communication Engineering) Current Sensorless Control Algorithm For Single-Phase Three-Level NPC InverterDokument6 Seiten(22559159 - Electrical, Control and Communication Engineering) Current Sensorless Control Algorithm For Single-Phase Three-Level NPC InverterRaghunandan SubramanianNoch keine Bewertungen

- Slidin Mode Research PaperDokument33 SeitenSlidin Mode Research PaperAnimesh JainNoch keine Bewertungen

- Extension State Space Averaging Resonant Switches and BeyondDokument8 SeitenExtension State Space Averaging Resonant Switches and BeyondMC TimbuNoch keine Bewertungen

- Capacitor Balance in Anpc PDFDokument10 SeitenCapacitor Balance in Anpc PDFSulthan Basha ShaikNoch keine Bewertungen

- Research Paper A Novel Method For Near State Pulse Width Modulation (NSPWM) Based Chopper DrivesDokument4 SeitenResearch Paper A Novel Method For Near State Pulse Width Modulation (NSPWM) Based Chopper Drivesdivyamanikandan007Noch keine Bewertungen

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDokument6 SeitenCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNoch keine Bewertungen

- Seven Level Inverter With Nearest Level ControlDokument7 SeitenSeven Level Inverter With Nearest Level Controlsanjay sNoch keine Bewertungen

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDokument6 SeitenSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNoch keine Bewertungen