Beruflich Dokumente

Kultur Dokumente

Cuestionario U3 SO

Hochgeladen von

Joselyn Guerrero GarciaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Cuestionario U3 SO

Hochgeladen von

Joselyn Guerrero GarciaCopyright:

Verfügbare Formate

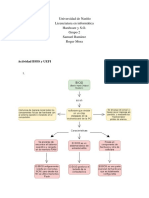

1-funcion y clasificacin de los gestores de memoria.

Su trabajo es seguir la pista de qu partes de la memoria estn en uso y cules no lo estn, con el fin de poder asignar memoria a los procesos cuando la necesiten, y recuperar esa memoria cuando dejen de necesitarla, as como gestionar el intercambio entre memoria principal y el disco cuando la memoria principal resulte demasiado pequea para contener a todos los procesos. Dos clases: 1.- los que mueven procesos de la memoria principal al disco y del disco a la memoria principal durante su ejecucin (intercambio y paginacin), y 2.- los que no lo hacen 2-Describe la mono programacin sin intercambio ni paginacin Consiste en ejecutar slo un programa a la vez, repartiendo la memoria entre ese programa y el sistema operativo. Descripcin: en el primer caso el programa de usuario podra estar en la parte superior de la memoria 3-describe la multiprogramacin con particiones fijas y su implementacin con una y multiples colas El tener mltiples procesos ejecutndose a la vez significa que cuando un proceso se bloquea esperando a que termine una operacin de E/S, otro proceso puede seguir haciendo uso de la CPU.

4-escribe la diferencia entre reubicacin esttica y dinmica

Dinmica: Otra solucin alternativa para tanto el problema de la reubicacin como el de la proteccin consiste en equipar la mquina con dos registros especiales de hardware, llamados el registro de base y el registro de lmite. Cuando se planifica un proceso, se carga el registro de base con la direccin donde comienza su particin, y el registro de lmite se carga con la longitud de la particin. Cada vez que se genera una direccin de memoria, se le suma de forma automtica el contenido del registro de base antes de enviarla a la memoria. Por ejemplo, si el registro base contiene el valor 100K, una instruccin CALL 100 se convierte efectivamente en una instruccin CALL 100K + 100, sin que la instruccin en s se modifique. Tambin se comparan las direcciones con el registro de lmite para asegurar que no intentan direccionar memoria fuera de la particin actual. El hardware protege los registros de base y de lmite para evitar que los programas de usuario los modifiquen.

Esttica: Una posible solucin consiste en modificar las instrucciones a medida que el programa se carga en la memoria. Los programas cargados en la particin 1 tendrn cada direccin incrementada en 100K, los programas cargados en la particin 2 tendrn sus direcciones incrementadas en 200K, y as sucesivamente. Para realizar la reubicacin durante la carga de esa manera, el enlazador deber incluir en el programa binario una lista o mapa de bits que indique qu palabras del programa son direcciones a reubicar y cules son cdigos de operacin, constantes u otras cosas que no deben reubicarse. OS/MFT trabajaba de esta manera. 5-escribe la diferencia entre intercambio (swapping) y memoria virtual (paginacin). Intercambio: la idea es de colocar procesos completos en la memoria principal o no colocarlos. Paginacin: partir esos procesos para colocarlos en la memoria. 6-explica con un dibujo la asignacin de memoria a varios procesos mediante swapping (dibujos)

7-que es la compactacin de memoria

Compactacin de memoria=Desfragmentacin Desventaja.- requiere mucho tiempo Cuando el intercambio crea mltiples huecos en la memoria, es posible combinar todos esos huecos en uno solo ms grande, moviendo todos los procesos hacia abajo hasta donde sea posible. Esta tcnica se denomina compactacin de la memoria. 8-explica con un dibujo la asignacin de espacio de memoria mediante swapping para procesos que puedan crecer.

Room for growth- espacio para el crecimiento; Stack- apilar; Actually in use- actualmente en uso; Data- datos

9-describe con un dibujo la asignacin de memoria con un mapa de bits y con listas doblemente enlazadas Control del uso de memoria en forma real Mapa de bits:

Hole.- agujero starts.- comienza length.- longitud. Process.- proceso

10-describe : primer ajuste (first fit), siguiente ajuste (next fit), mejor ajuste (best fit), peor ajuste (worst) y ajuste rpido (quick fit). El algoritmo ms sencillo es el del primer ajuste (first fit). El gestor de memoria explora la lista de segmentos hasta encontrar un hueco lo suficientemente grande. Luego el hueco se divide en dos partes, una para el proceso y otra para la memoria no utilizada, salvo en el caso poco probable de que el ajuste sea exacto. Este algoritmo es rpido porque la bsqueda es lo ms corta posible. Busca el primer hueco y ah acomoda al proceso. Siempre al inicio. VENTAJA.- posicionamiento rpido. DESVENTAJA.-desperdicio de memoria, si entra un proceso de 4kb y solo usa 1kb.

el siguiente ajuste (next fit). Su funcionamiento es similar al del primer ajuste, salvo que el algoritmo recuerda en qu punto de la lista se qued la ltima vez que encontr un hueco apropiado. Guarda posicin de memoria donde la encontr la ultima vez y empieza a buscar a partir de ah.

mejor ajuste (best fit). En este caso se recorre toda la lista para encontrar el hueco ms pequeo capaz de contener al proceso. DESVENTAJA.- lleva mucho tiempo encontrarlo. el peor ajuste (worst fit), es decir, escoger siempre el hueco ms grande disponible, de modo que el hueco resultante sea lo suficientemente grande como para ser til.

ajuste rpido (quick fit), que mantiene listas separadas para algunos de los tamaos solicitados ms frecuentemente. 11-que es la MMU y dibuja donde se encuentra posicionada (unidad de gestin de memoria) Se encarga de administrar las direcciones y cambiar las direcciones virtuales a direcciones fsicas para mandarlas al bus de memoria.

CPUpackage.- paquete de CPU.. the CPU sends virtual addresses to the MMU.- la CPU enva las direcciones virtuales a la MM the CPU sends physical addresses to the MMU.- la CPU enva las direcciones fsicas a la MMU 12- dibuja la relacin entre un espacio de direcciones virtuales de 64kb y una memoria fsica de 32kb con marcos de pagina de 8kb Relacin entre las direcciones virtuales y las direcciones fsicas esta dada por una tabla de pginas. Bit de presencia: nos indica si esta utilizada o referenciada la pagina.

13-que es una falta de pgina Necesita utilizar un proceso que no esta cargado en la memoria principal ah tendra que pasarle el control al SO y el SO tendra que tomar una decisin esa decisin la basa en los algoritmos (podra sacar la pagina que ya tenga mucho tiempo, que ya no se est utilizando, prioridad de procesos).

Qu sucede si el programa intenta utilizar una pgina que no tiene correspondencia, por ejemplo, ejecutando la instruccin

MOV REG,32780 Que referencia el byte 12 dentro de la pgina virtual 8 (que comienza en 32768)? La MMU ve que la pgina no tiene correspondencia (lo que se indica con una cruz en la figura) y provoca una excepcin que hace que la CPU ceda el control al sistema operativo. Esta excepcin se denomina una falta de pgina. 14-describe con un dibujo el funcionamiento interno de la MMU con 16 paginas de 4kb Si la direccin no tienen correspondencia es que hay falta d pagina y se le pasa el mando al SO y el SO toma la decisin

Outgoing physical address.- direccin fsica saliente incoming virtual adress.- direccin virtual de entrada. Bit offset copied directly from input to output.- Bit compensar copian directamente desde la entrada hasta la salida. Present/absent bit.- presente/ausente is used as an index into the page table.- se utiliza como un ndice en la tabla de pginas.

15 que problema se presenta con el uso de las tablas de paginas Las tablas de pginas son una funcin (sistema) que nos ayuda a convertir una direccin virtual a una direccin fsica. 1. La tabla de pginas puede ser extremadamente grande. Con 32 bits tendra que tener 10000 de direcciones las que tendra que referenciar. 2. La traduccin de direcciones debe realizarse muy rpidamente. Tendra que hacer la traduccin de direccin virtual a direccin fsica demasiado rpida, habra un cuello de botella. El primer punto se sigue del hecho de que los ordenadores modernos utilizan direcciones virtuales de por lo menos 32 bits El segundo punto es una consecuencia del hecho de que la traduccin de direcciones virtuales a direcciones fsicas debe realizarse cada vez que se hace referencia a la memoria. 16-describe con un dibujo las tablas de pginas multinivel

Divide los registros en secciones PT1( sabemos que tipo de memoria va a acceder, de datos, de pila o del programa), PT2, offset(desplazamiento de 12 bits). 17-describe los campos de una entrada tpica de la tabla de pginas Numero de campo de pgina Presencia: 0 falta de pagina y 1 referenciada Proteccin: tipo de acceso escritura lectura ejecucin. Modificada: si ya ha sido escrita Referencia: si tienen algn vinculo con otro marco de pgina. Deshabilitar el almacenamiento en cach. deshabilita o habilita los registros que se utilizan para esta direccin.

Los bits de Proteccin indican qu tipos de acceso estn permitidos. Los bits de pgina Modificada y Referenciada siguen la pista del uso de la pgina. El bit de Referenciada se activa siempre que se referencia una pgina, ya sea para leer o para escribir. Finalmente el ltimo bit permite inhabilitar el uso de la cach para la pgina. Caching disable.- deshabilitar el almacenamiento en cach 18-que es una TLB y como funciona Consiste en equipar al ordenador con un pequeo dispositivo de hardware que traduce direcciones virtuales a direcciones fsicas, sin hacer uso de la tabla de pginas. Este dispositivo, denominado TLB (Tranlation Lookaside Buffer), tambin conocido como memoria asociativa est dentro de la MMU y consiste en un pequeo nmero de entradas, ocho en este ejemplo, pero casi nunca ms de 64. Cada entrada contiene informacin sobre una pgina, incluido el nmero de pgina virtual, un bit que se establece cuando la pgina se modifica, el cdigo de proteccin (permisos para leer/escribir/ejecutar) y el marco de pgina fsico en el cual est cargada la pgina. Estos campos tienen una correspondencia uno a uno con los campos de la tabla de pginas. VENTAJA.- acelera la paginacin. 19-mensiona una ventaja y una desventaja en las tablas de paginas invertidas Aunque las tablas de pginas invertidas ahorran una enorme cantidad de espacio, al menos cuando el espacio de direcciones virtual es mucho ms grande que la memoria fsica, tienen un serio inconveniente: la traduccin de direcciones virtuales a fsicas es mucho ms difcil. Cuando el proceso n hace referencia a la pgina virtual p, el hardware no puede ya encontrar la pgina fsica utilizando p como un ndice sobre la tabla de pginas del proceso n, sino que debe buscar una entrada (n, p) recorriendo la tabla de pginas invertida. Adems, esa bsqueda debe efectuarse en cada referencia a la memoria, y no slo cuando se generan faltas de pgina. Recorrer una tabla de 64 K en cada referencia a la memoria no es la forma de conseguir que la mquina sea excepcionalmente rpida. 20-explica y describe con un dibujo el algoritmo de sustitucin de pginas ptimo

Se basa en el nivel de jerarqua. Debe sustituirse la pgina con el valor ms alto de esa etiqueta. En este caso es A para que entre E. 1000 2000 1000 4000 D C B A

1000 2000 1000 1000 D C B E

No se puede implementar porque el sistema no puede saber cuando se volver hacer referencia a cada una de las pginas. 21-explica y describe con un dibujo el algoritmo de sustitucin de paginas NRU (No recientemente usado) R.- se activa cada vez que referencia la pgina (para leer o escribir) M.- se activa cada vez que se escribe en la pgina (se modifica) Cuando se presenta una falta de pgina, el SO inspecciona todas las pginas dividindolas en cuatro categoras segn los valores actuales de sus bits de R y M. Clase 1: pgina ni R ni M Clase 2: pgina no R y M Clase 3: pgina R y no M Clase 4: pgina R y M 0 1 0 1 1 0 0 1 D C B A Sacrificar a B para que entre E porque no esta ni referenciada ni modificada. M 0 1 1 1 R 1 0 1 1 D C E A M R

22-explica y describe con un dibujo el algoritmo de sustitucin de paginas FIFO (Primero en entrar primero en salir). Se tomara la primera pgina que entro que en este caso es la A. Nuevo Viejo final inicio R 4 3 2 1 D C B A Al querer entrar E se sacrificar el primero en entrar que en este caso seria A. Nuevo final R 4 3 2 D C B Puede tambin tomar en cuenta el tiempo. Viejo inicio 1 E

23-explica y describe con un dibujo el algoritmo de sustitucin de pginas de la segunda oportunidad Modificacin de la FIFO que consiste en examinar el bit R de la pgina mas antigua. final inicio 1 1 0 1 D C B A 4 3 2 1 Pasamos por A y como esta referenciado con 1 le damos otra oportunidad y lo pasamos a 0, en seguida pasamos por B y como no esta referenciado lo sacrificamos y ah ponemos a E. R final 1 D 4 inicio 1 A 1

1 C 3

0 E 2

24-explica y describe con un dibujo el algoritmo de sustitucin de paginas de reloj

25-explica y describe con un dibujo el algoritmo de sustitucin de paginas LRU (Recientemente usado) Encontrar una pgina en la lista, sacarla de la lista y reinsertarla al frente es una operacin muy lenta.

26-explica y describe con un dibujo el algoritmo de sustitucin de paginas NFU

27-explica y describe con un dibujo el algoritmo de sustitucin de paginas de envejecimiento

28-explica y describe con un dibujo el algoritmo de sustitucin de conjunto de trabajo Se denomina paginacin bajo demanda. Si todo el conjunto de trabajo esta en la memoria, el proceso se ejecuta sin provocar muchas faltas de pgina hasta que pasa a otra fase de su ejecucin. 29-describe y explica con un dibujo el algoritmo de sustitucin de paginas WSClock

Figura 4-22. Funcionamiento del algoritmo WSClock. (a) y (b) dan un ejemplo de lo que sucede cuando R = 1. (c) y (d) dan un ejemplo de R = 0.

Das könnte Ihnen auch gefallen

- Administración de sistemas operativosVon EverandAdministración de sistemas operativosBewertung: 3.5 von 5 Sternen3.5/5 (8)

- Ejercicio Memoria ResueltosDokument4 SeitenEjercicio Memoria ResueltosmayyyNoch keine Bewertungen

- Ejercicios de Parciales ResueltosDokument18 SeitenEjercicios de Parciales ResueltosdndpaipaiNoch keine Bewertungen

- Tarea 1 Ricardo MacielDokument5 SeitenTarea 1 Ricardo MacielRicardo MacielNoch keine Bewertungen

- Sistemas Operativos - Capitulo IIIDokument11 SeitenSistemas Operativos - Capitulo IIILuis Fernando JimenezNoch keine Bewertungen

- Ut03 Sistemas Operativos Gestic3b3n de Memoria Aso (Asir)Dokument5 SeitenUt03 Sistemas Operativos Gestic3b3n de Memoria Aso (Asir)RtyRteyNoch keine Bewertungen

- Sistemas Operativos Exposicion - Memoria VirtualDokument16 SeitenSistemas Operativos Exposicion - Memoria Virtualdiegoaguas22Noch keine Bewertungen

- Gestion de Memoria - S.ODokument16 SeitenGestion de Memoria - S.Oeduardo balzaNoch keine Bewertungen

- Fso 20170707 Extraordinaria TestDokument3 SeitenFso 20170707 Extraordinaria TestHector BazarteNoch keine Bewertungen

- Test Soluciones 20190411 FSO ParcialDokument4 SeitenTest Soluciones 20190411 FSO ParcialFIDEL HUANCO RAMOSNoch keine Bewertungen

- Preguntas de Tipo TestDokument5 SeitenPreguntas de Tipo Testjuan godoyNoch keine Bewertungen

- Soluciones Tema 2Dokument3 SeitenSoluciones Tema 2Sergio Muñoz100% (1)

- Examen SO1 2017 Feb Mar Solucion PDFDokument6 SeitenExamen SO1 2017 Feb Mar Solucion PDFFlavioNoch keine Bewertungen

- FSO 20190520 Ordinaria p2 Test SolucionesDokument4 SeitenFSO 20190520 Ordinaria p2 Test SolucionesHector BazarteNoch keine Bewertungen

- Sog 2013 09Dokument5 SeitenSog 2013 09Lyon T IonNoch keine Bewertungen

- Examenes Con Soluciones SODokument231 SeitenExamenes Con Soluciones SOCyrusNoch keine Bewertungen

- Examenes Final SsooDokument36 SeitenExamenes Final SsooAlex Gómez López100% (1)

- Funciones y capas del sistema operativoDokument41 SeitenFunciones y capas del sistema operativoAngel VazquezNoch keine Bewertungen

- Tema 17-1Dokument30 SeitenTema 17-1cheliNoch keine Bewertungen

- Sog 2013 02 N2Dokument4 SeitenSog 2013 02 N2Lyon T IonNoch keine Bewertungen

- Sog 2012 02 N2Dokument6 SeitenSog 2012 02 N2Lyon T IonNoch keine Bewertungen

- Sog 2014 02 N1Dokument5 SeitenSog 2014 02 N1Lyon T IonNoch keine Bewertungen

- Sog 2013 02 N1Dokument6 SeitenSog 2013 02 N1Lyon T IonNoch keine Bewertungen

- Sog 2014 02 N2Dokument5 SeitenSog 2014 02 N2Lyon T IonNoch keine Bewertungen

- Fundamentos de Los Sistemas Operativos Examen Parcial, 9 de Abril de 2018 Preguntas Del TestDokument4 SeitenFundamentos de Los Sistemas Operativos Examen Parcial, 9 de Abril de 2018 Preguntas Del TestBrenda Nahomi Quispe GonzalesNoch keine Bewertungen

- BIOS y UEFIDokument10 SeitenBIOS y UEFIRoger MoraNoch keine Bewertungen

- TestDokument27 SeitenTestAngel Luis Tovar PazNoch keine Bewertungen

- RES FINAL Labo ComputadorasDokument11 SeitenRES FINAL Labo Computadorasoscarmr893Noch keine Bewertungen

- Historia Del MouseDokument9 SeitenHistoria Del MouseSYSNG INTERNETNoch keine Bewertungen

- MicroprocesadoresDokument67 SeitenMicroprocesadoresJaime Ballesta Julio100% (1)

- Como Funciona El Procesamiento en ParaleloDokument4 SeitenComo Funciona El Procesamiento en ParaleloFrancesco RuggieroNoch keine Bewertungen

- Comparativa Manejo de Memoria Windows Vs LinuxDokument1 SeiteComparativa Manejo de Memoria Windows Vs LinuxAlarisNoch keine Bewertungen

- Algoritmo BanqueroDokument12 SeitenAlgoritmo BanqueroMark Fortón OchoaNoch keine Bewertungen

- Talleres Arquitectura, Cap1 Al 3Dokument16 SeitenTalleres Arquitectura, Cap1 Al 3Edwin David Gomez DelgadoNoch keine Bewertungen

- SO Tema4 Ejercicios PlanificacionDokument4 SeitenSO Tema4 Ejercicios PlanificacionAngel CroesNoch keine Bewertungen

- Memoria virtual, caché y espectro de almacenamiento en sistemas operativosDokument21 SeitenMemoria virtual, caché y espectro de almacenamiento en sistemas operativosPablo Cesar Medina BarretoNoch keine Bewertungen

- Niveles memoriaDokument10 SeitenNiveles memoriaHugo RodríguezNoch keine Bewertungen

- Unidad #1 Introducción Al Lenguaje EnsambladorDokument5 SeitenUnidad #1 Introducción Al Lenguaje EnsambladoringgafabifiNoch keine Bewertungen

- Memoria Virtual y PaginacionDokument39 SeitenMemoria Virtual y PaginacionJohnny Acero GuamanNoch keine Bewertungen

- Test 3Dokument9 SeitenTest 3Valeria Del CastilloNoch keine Bewertungen

- 1.4 El Concepto de InterrupcionesDokument3 Seiten1.4 El Concepto de InterrupcionesAbraham Kantu100% (1)

- Paginación y SegmentaciónDokument3 SeitenPaginación y SegmentaciónRafael PinedaNoch keine Bewertungen

- Algoritmos Planificacion FCFS SJF SRTF Round RobinDokument10 SeitenAlgoritmos Planificacion FCFS SJF SRTF Round RobinRamon Lloret PertusaNoch keine Bewertungen

- ExamenDokument4 SeitenExamenMaria Ruiz LinoNoch keine Bewertungen

- Multiprocesamiento Simétrico y Micro Núcleos-FinalDokument13 SeitenMultiprocesamiento Simétrico y Micro Núcleos-FinalOscar CobbNoch keine Bewertungen

- Kernel y Partes Del KernelDokument4 SeitenKernel y Partes Del KernelAlam Garcia0% (1)

- Memoria virtual Linux iOS: Paginación, Buddy, LRU, COWDokument10 SeitenMemoria virtual Linux iOS: Paginación, Buddy, LRU, COWAnderson JordanNoch keine Bewertungen

- Algoritmo de Planificacion SPNDokument12 SeitenAlgoritmo de Planificacion SPNJohn Paul AmbuludiNoch keine Bewertungen

- 1 11 EjerdelucamemoriaDokument8 Seiten1 11 EjerdelucamemoriaEveling CastroNoch keine Bewertungen

- Gestión de Almacenamiento SecundarioDokument20 SeitenGestión de Almacenamiento SecundariojdavcNoch keine Bewertungen

- Resumen Gestion de MemoriaDokument17 SeitenResumen Gestion de MemoriaAnghelita CaldheronNoch keine Bewertungen

- Sistema Operativo Windows 7Dokument10 SeitenSistema Operativo Windows 7Camilo Flórez EsquivelNoch keine Bewertungen

- Sistemas Operativos I - Estructuras de datos para el manejo de dispositivosDokument10 SeitenSistemas Operativos I - Estructuras de datos para el manejo de dispositivosFernando Fuentes BetancourtNoch keine Bewertungen

- Técnicas Administración Del PlanificadorDokument6 SeitenTécnicas Administración Del PlanificadorJaqueline Cuahtepitzi CBNoch keine Bewertungen

- Sistemas Operativos Unidad 3Dokument8 SeitenSistemas Operativos Unidad 3Spam SpamNoch keine Bewertungen

- Actividad Semana 2-4Dokument8 SeitenActividad Semana 2-4LUIGI davian patiño cardonaNoch keine Bewertungen

- Mientras Que Los Registros Base y Límite Se Pueden Utilizar para Crear La Abstracción de Los Espacios de DireccionesDokument6 SeitenMientras Que Los Registros Base y Límite Se Pueden Utilizar para Crear La Abstracción de Los Espacios de Direccionesvictor0josue-975742Noch keine Bewertungen

- Tarea SODokument33 SeitenTarea SOOlgaa BautistaNoch keine Bewertungen

- Sistema Operativo 1Dokument16 SeitenSistema Operativo 1guillermo memoNoch keine Bewertungen

- Preguntas para Final de Arquitectura de ComputadoresDokument3 SeitenPreguntas para Final de Arquitectura de ComputadoresAndro Erick Valero MedinaNoch keine Bewertungen

- Automat As 1Dokument5 SeitenAutomat As 1Joselyn Guerrero GarciaNoch keine Bewertungen

- 3.2.4 Arquitectura de Referencia para Sistemas de Informacion PDFDokument5 Seiten3.2.4 Arquitectura de Referencia para Sistemas de Informacion PDFJoselyn Guerrero Garcia0% (1)

- I.A. - Unidad 3Dokument15 SeitenI.A. - Unidad 3Willed EdwillNoch keine Bewertungen

- 3.2.4 Arquitectura de Referencia para Sistemas de Informacion PDFDokument5 Seiten3.2.4 Arquitectura de Referencia para Sistemas de Informacion PDFJoselyn Guerrero Garcia0% (1)

- Estudiar Estudiar EstudiarDokument8 SeitenEstudiar Estudiar EstudiarJoselyn Guerrero GarciaNoch keine Bewertungen

- F 0840734Dokument8 SeitenF 0840734Joselyn Guerrero GarciaNoch keine Bewertungen

- Windows Linux Dispositivos ExtraiblesDokument2 SeitenWindows Linux Dispositivos Extraiblesjhon eduar campo ladeuthNoch keine Bewertungen

- Sistema de Control de Versiones PDFDokument35 SeitenSistema de Control de Versiones PDFDayred Linares100% (1)

- Pasos para Instalar Un Sistema OperativoDokument46 SeitenPasos para Instalar Un Sistema OperativoMosquera OswardNoch keine Bewertungen

- Cuestionario de La Unidad 1Dokument9 SeitenCuestionario de La Unidad 1Luis Angel Zacarias CalizNoch keine Bewertungen

- Clonación de DiscosDokument3 SeitenClonación de Discossaeltuus churacNoch keine Bewertungen

- Crack WinRar v.3.50 Garantizado Por LuismiDokument2 SeitenCrack WinRar v.3.50 Garantizado Por LuismiNacho GarciaNoch keine Bewertungen

- SI08Dokument14 SeitenSI08Yasmina SosaNoch keine Bewertungen

- Archivos y Comandos de Configuracion de Usuarios en LinuxDokument11 SeitenArchivos y Comandos de Configuracion de Usuarios en Linuxr.ramosmediavillaNoch keine Bewertungen

- Guía Contestada 2-2015-2aDokument4 SeitenGuía Contestada 2-2015-2aMaribel Trejo ChavezNoch keine Bewertungen

- Ejercicio Unix 3 ResueltoDokument6 SeitenEjercicio Unix 3 ResueltozyzzNoch keine Bewertungen

- 1 Crear Una Máquina Virtual de Kali Linux GuiaKaliVMDokument5 Seiten1 Crear Una Máquina Virtual de Kali Linux GuiaKaliVMAlex0107Noch keine Bewertungen

- Curso Terminal CLIDokument126 SeitenCurso Terminal CLIjavierth Enrique AraucoNoch keine Bewertungen

- Instalar Servidor FTP en LinuxDokument6 SeitenInstalar Servidor FTP en LinuxhamzabeddoukaNoch keine Bewertungen

- Sistemas OperativosDokument12 SeitenSistemas OperativosChaAvitha HdzNoch keine Bewertungen

- Un Sistema de Archivos: DiscoDokument2 SeitenUn Sistema de Archivos: DiscoEzequiel AcevedoNoch keine Bewertungen

- Guia InstalacióDokument13 SeitenGuia InstalacióIván FernándezNoch keine Bewertungen

- Sistemas OperativosDokument3 SeitenSistemas Operativosmision sucre santa rita coordinacion municipalNoch keine Bewertungen

- Coda PDFDokument19 SeitenCoda PDFHugo Molina Ch100% (1)

- Practica 3 - Operaciones Con DirectoriosDokument5 SeitenPractica 3 - Operaciones Con DirectoriosIgnacio Ruiz ValenzuelaNoch keine Bewertungen

- Creación de Un Dispositivo de Memoria USB Multi-Arranque Formateado Con NTFSDokument10 SeitenCreación de Un Dispositivo de Memoria USB Multi-Arranque Formateado Con NTFSMartin GarciaNoch keine Bewertungen

- Comandos LinuxDokument34 SeitenComandos LinuxRoberto CidNoch keine Bewertungen

- Solucionario Comandos LinuxDokument17 SeitenSolucionario Comandos LinuxCarliños HzNoch keine Bewertungen

- Reparar USB Formato RAW Sin Softwares y FACILDokument2 SeitenReparar USB Formato RAW Sin Softwares y FACILjose101728Noch keine Bewertungen

- Presentacion NFSDokument34 SeitenPresentacion NFSJoseNoch keine Bewertungen

- 010 - Tabla Comparativa de Distribuciones LinuxDokument2 Seiten010 - Tabla Comparativa de Distribuciones LinuxJhonny Lozano100% (1)

- Posix ThreadsDokument14 SeitenPosix Threadscarlos18277Noch keine Bewertungen

- TP Unsam 2014 2Dokument11 SeitenTP Unsam 2014 2Mariana Casella0% (1)

- 10 Preguntas Servidor NfsDokument3 Seiten10 Preguntas Servidor NfsDoryPlùasLNoch keine Bewertungen

- SEGMENTACIÓN Y PAGINACIÓN EN LA ADMINISTRACIÓN DE MEMORIADokument16 SeitenSEGMENTACIÓN Y PAGINACIÓN EN LA ADMINISTRACIÓN DE MEMORIAWagner CusmeNoch keine Bewertungen

- Comandos básicos de LinuxDokument23 SeitenComandos básicos de Linuxjuan david rendonNoch keine Bewertungen