Beruflich Dokumente

Kultur Dokumente

Ejercicios Electronica Digital I

Hochgeladen von

scorpio19Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ejercicios Electronica Digital I

Hochgeladen von

scorpio19Copyright:

Verfügbare Formate

UNIVERSIDAD TECNOLGICA DEL PER

INGENIERA BIOMDICA

ELECTRNICA DIGITAL I

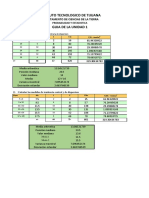

EJERCICIOS ELECTRNICA DIGITAL I A. CIRCUITOS SECUENCIALES BASICOS a. DIAGRAMAS DE TIEMPO PARA LOS FFs: hallar el diagrama de tiempo para el siguiente circuito: CONSIDERACIONES PARA ? ? LA SOLUCIN: En general ? para estos casos deben 1 hacer una TABLA DE ESTADO, en donde UDS tabularn los ESTADOS: PRESENTE y SIGUIENTE que se presentarn en las salidas de los FFs. Consideremos que se 1 considera ESTADO PRESENTE, al Estado de las 1 salidas de los FFs antes de la ocurrencia del PULSO DE RELOJ (flanco de subida o flanco de bajada), ESTADO PRESENTE ESTADO SIGUIENTE QA, QB, QC. QA QB QC QA* QB* QC* Por lo tanto cuando ocurre el PULSO DE RELOJ las salidas pasan al 0 0 0 ESTADO SIGUIENTE, teniendo en cuenta cuales eran los valores que haban en las entradas de los FFs y la tabla del FF que estn analizando, OK?, tendremos QA*, QB* y QC*. Ya saben, si no se dice nada se asume que inicialmente las salidas de los FFs eran CEROS (0). Con estos valores iniciales, UDS deben CK escribir las ecuaciones para c/u de las JA entradas de los FFs, para el ckto dado, si el KA FF de la izquierda es A, el del centro B y el de QA la derecha C; entonces para el FFA tendremos: JA = QB+QC ; KA = 1, tambin JB = QA y JB KB = 1, del mismo modo JC = (QA.QB) y KC = (QB xor QA), entonces en estas ecuaciones KB reemplazamos las condiciones iniciales y sabremos cuales sern las entradas a los FFs QB que estarn esperando la ocurrencia del PULSO DE RELOJ, para provocar el cambio en JC sus salidas (de acuerdo a su tabla) y generar el ESTADO SIGUIENTE, que ser ahora el nuevo ESTADO PRESENTE y repetimos como si estos fueran los nuevos valores iniciales. KC QC OKKKKK? Debern repetir el proceso hasta que UDS observen que todos los estados vuelven a repetirse. OK?????... Pues bien a trabajar. UDS. Debern pasar la Tabla al Diagrama de Tiempos, arriba, OK? Los 1 en el PRESET y CLEAR, dejarn que la secuencia exista.

1 2 3 RELOJ 74LS32 1 2 3 74LS00

2 7 S S

4 1

15

9 6

11

4 1

15

CLK K

CLK K

1 2

CLK K

74LS76

74LS76

74LS86

16

14

12

10

16

14

74LS76

b. Aplicar lo revisado en la construccin del diagrama de tiempos para el siguiente circuito

? ?

2 3 3 74LS02 Q 8 D CLK 1 3 2

1

U1:A(CLK)

74LS86

10

D CLK

D CLK

2 3

12 11

A

R

Q 6

B

R 13

74LS74

C

1 R

Q 6 74LS74

74LS74

DOCENTE: ING. Luis Pacheco Cribillero

UNIVERSIDAD TECNOLGICA DEL PER

INGENIERA BIOMDICA

ELECTRNICA DIGITAL I

B. DISEE UN REGISTRO ESPECIAL, DE 4 BITS, USANDO FFS TIPO D (74LS74) QUE REALICE LAS SIGUIENTES OPERACIONES: OPERACIONES Carga de datos en paralelo Desplazamiento a la derecha Carga de nuevos datos, en paralelo Desplazamiento a la izquierda SOLUCIN En este tipo de diseos deben considerar los siguientes comentarios y pasos a realizar: Como hay 4 operaciones, entonces con 2 variables x e y, sabemos que tendremos 22 = 4 combinaciones, c/u de las cuales servir para controlar una operacin a la vez, entonces podemos implementar la siguiente Tabla: X Y OPERACIN COMENTARIOS QUE DEBE TENER EN CUENTA 0 0 Carga de datos en paralelo Todos los FFs deben cargarse a la vez 0 1 Desplazamiento a la derecha Los datos desplazados se pierden cuando avanzan 1 0 Carga de nuevos datos, en paralelo Todos los FFs deben volver a cargarse otra vez 1 1 Desplazamiento a la izquierda Los datos desplazados se pierden cuando avanzan Como siguiente paso debemos dibujar nuestro esquema circuital, recordando que ser sobre los 4 FFs que conforman el Registro, en donde ocurrirn las operaciones de la tabla, esto lo debemos entender como que habran 4 circuitos diferentes para hacer cada una de las operaciones indicadas. Entonces si sobre un solo circuito, que es el registro, se van a realizar cuatro operaciones, entonces debe haber algn dispositivo o circuito combinacional que lo permita: ser en este caso un MULTIPLEXOR de 4x1 es decir un 74LS153, el cual posee en su interior 2 Mux de 4x1.

1

U1

6 5 4 3 10 11 12 13 14 2 1 15 1X0 1X1 1X2 1X3 2X0 2X1 2X2 2X3 A B 1E 2E 74LS153

S

REGISTRO ESPECIAL DE 4 BITS

1Y D CLK

S

2 3

SET O PRESET

U2:A

Q 5

0

IN SHR

?

OUT SHL

A

1 R

2Y

A = MSB D = LSB

?

74LS74

10

U4

6 5 4 3 10 11 12 13 14 2 1 15 1X0 1X1 1X2 1X3 2X0 2X1 2X2 2X3 A B 1E 2E 74LS153 1Y 7 2 3 D CLK

D CLK

12 11

U2:B

U3:A

Q 5

B

R

C

1 R

2Y

13

1 0 0 1

CARGA DE DATOS

U2:B(CLK)

74LS74

74LS74

D CLK

RESET O CLEAR

12 11

10

U3:B

Q 9

?

OUT SHR

D

13 R

1 1

IN SHL CONTROL

74LS74

En el circuito CARGA DE DATOS, es para colocar cualquier numero de 4 bits (0000 1111) que luego se desplazar hacia la derecha o izquierda. CONTROL corresponde a los valores de X = B e Y = A en la Tabla con ellos realizamos las secuencias pedidas. Se dan cuenta que A y B son los pines de control del MUX verdad?... 1Y es la salida del Mux superior y 2Y es la salida del Mux inferior. 1E Y 2E son los pines de habilitacin para que los MUX puedan trabajar (se habilitan con 0)

DOCENTE: ING. Luis Pacheco Cribillero

UNIVERSIDAD TECNOLGICA DEL PER

INGENIERA BIOMDICA

ELECTRNICA DIGITAL I

IN SHR, es el pin de entrada de datos seriales para desplazarse a la derecha, si tiene el valor 0 como en el esquema, luego del desplazamiento el registro queda lleno de CEROS, y si tuviera el valor 1 quedara lleno de UNOS, verifquelo. IN SHL, es anlogo al anterior pero para desplazarse a la izquierda, OK?... Si SET fuese 0 todas las salidas iran a UNO, se entiende por qu?. Si RESET fuese 0 todas las salidas iran a CERO y tendramos un RESETEO Noo? OK?... 1E habilita Mux superior, prefijos 1X, mientras que 2E habilita Mux inferior con prefijos 2X, OK?.. OUT SHR es el pin por donde salen los datos desplazados a la derecha y OUT SHL es el pin por donde salen los datos desplazados a la izquierda. OBSERVE Y PRACTIQUE: si UD quita el Logic State IN SHR y esa entrada lo conecta a QD y tambin, al mismo tiempo quita el Logic State IN SHL y esa entrada lo conecta a QA, cambiar la accin de desplazamiento por uno denominado de rotacin, en donde el dato cargado, si le controlamos 4 pulsos de reloj, observaremos que todos los bits salieron pero, despus de los 4 pulsos, volvieron a su posicin de cargados.

1

U1

6 5 4 3 10 11 12 13 14 2 1 15 1X0 1X1 1X2 1X3 2X0 2X1 2X2 2X3 A B 1E 2E 74LS153

S

REGISTRO ESPECIAL DE 4 BITS

1Y D CLK

S

2 3

SET O PRESET

U2:A

Q 5

QD

?

OUT SHL

QA

IN SHR

A

R

2Y

74LS74

10

U4

6 5 4 3 10 11 12 13 14 2 1 15 1X0 1X1 1X2 1X3 2X0 2X1 2X2 2X3 A B 1E 2E 74LS153 1Y 7 2 3 D CLK

D CLK

12 11

U2:B

U3:A

Q 5

QD

A = MSB D = LSB

B

R

C

1 R

2Y

13

1 0 0 1

CARGA DE DATOS

U5:A(A)

74LS74

74LS74

D CLK

RESET O CLEAR

1 74LS08 3

12 11

10

U3:B

Q 9

?

OUT SHR

D

13 R

1 1

CONTROL

CONTROL CLOCK

IN SHL

QA

74LS74

Observe como hemos quitado INSHR y INSHL y hemos conectado QD y QA, respectivamente, y hemos aadido tambin el control de clock, con el cual podemos parar el clock, cuando queramos y con solo colocar en el Logic State un 0. Para conectar QD y QA hemos usado los TERMINALS del men, OK?... sabes cmo? Noo? a. Entonces, luego del desarrollo anterior les propongo disear el circuito para realizar las siguientes operaciones, usando la misma filosofa explicada para el diseo anterior, OK?..:

OPERACIONES Cargar dato de 4 bits Rotar datos a la derecha Rotar datos a la izquierda Cargar nuevo dato Rotar datos a la izquierda Rotar datos a la derecha Poner todas las salidas a 1 Poner todas las salidas a 0

DOCENTE: ING. Luis Pacheco Cribillero

NOTAS PARA LA SOLUCIN: Se dan cuenta que ahora necesitarn ____ variables para realizar todo el control, verdad?.. Que ahora para controlar las ____ operaciones necesitarn un Mux de _____ Que ahora solo se les pide rotacin y no desplazamiento

UNIVERSIDAD TECNOLGICA DEL PER

INGENIERA BIOMDICA

ELECTRNICA DIGITAL I

C. USANDO COMPARADORES 74LS85 DISEAR UN SISTEMA DE CONTROL DE MODO QUE SI SE TIENE UN DATO DE ENTRADA IGUAL A 8, SE ACTIVE UNA LAMPARA QUE FUNCIONA A 220 VAC 60 HZ, Y CUANDO LA ENTRADA ES MENOR O IGUAL QUE 6 UN CARRITO DE JUGUETE AVANCE HACIA DELANTE, Y SI EL DATO ES MAYOR O IGUAL QUE 10 EL CARRITO RETROCEDA, ENTRE 7 Y NUEVE EL CARRITO ESTAR DETENIDO. SOLUCIN

ENTRADA DE DATOS MANUAL

U5

3 2 6 7 12 13 Q0 Q1 Q2 Q3 TCU TCD D0 D1 D2 D3 UP DN PL MR 15 1 10 9 5 4 11 14

ENTRADA DE DATOS AUTOMATICA

U6:A

1 3 2 74LS08 U6:A(B)

1 CONTROL RELOJ

74LS193

1 0

B1

10

12

13

0 1 0 1

0 1 1 0

0 0 0 1

10

U4(VSS)

3 6 8 11

12V

L1

220V

D1

1N4001

4 3 2 1 14 11 9 15 13 12 10 4 3 2 1 14 11 9 15 13 12 10 4 3 2 1 14 11 9 15 13 12 10

RL1

12V

A>B A=B A<B B3 B2 B1 B0 A3 A2 A1 A0

A>B A=B A<B B3 B2 B1 B0 A3 A2 A1 A0

74LS85

74LS85

A>B A=B A<B B3 B2 B1 B0 A3 A2 A1 A0 QA>B QA=B QA<B

U1

U2

U3

74LS85

QA>B QA=B QA<B

QA>B QA=B QA<B

5 6 7

5 6 7

5 6 7

16 2 7 1 IN1 IN2 EN1 VSS

8 VS OUT1 OUT2

U4

3 6

R1

1k

Q1

2N3904

220V

60Hz

ENABLE

9 10 15

EN2 IN3 IN4

GND

OUT3 GND OUT4

11 14

L293D

MOTORES DE RUEDAS DELANTERAS

DOCENTE: ING. Luis Pacheco Cribillero

Das könnte Ihnen auch gefallen

- Guia Unidad 1 ProbabilidadDokument12 SeitenGuia Unidad 1 ProbabilidadJorge TorresNoch keine Bewertungen

- Cuestionario 2Dokument21 SeitenCuestionario 2Gleitze RamosNoch keine Bewertungen

- Retardos1 Por Software en Los Microcontroladores Pic PDFDokument3 SeitenRetardos1 Por Software en Los Microcontroladores Pic PDFscorpio19Noch keine Bewertungen

- Tesis Datamart Logistica Transporte PublicoDokument97 SeitenTesis Datamart Logistica Transporte PublicoXiomy Torrez LazaroNoch keine Bewertungen

- Retardos1 Por Software en Los Microcontroladores PicDokument3 SeitenRetardos1 Por Software en Los Microcontroladores Picscorpio19Noch keine Bewertungen

- Multiplexores TeoriaDokument19 SeitenMultiplexores Teoriascorpio19Noch keine Bewertungen

- Multiplexores TeoriaDokument19 SeitenMultiplexores Teoriascorpio19Noch keine Bewertungen

- Señales Digitales en MATLABDokument9 SeitenSeñales Digitales en MATLABscorpio19Noch keine Bewertungen

- Retardos PIC en MPLABDokument12 SeitenRetardos PIC en MPLABscorpio19Noch keine Bewertungen

- Teoria UsbDokument10 SeitenTeoria Usbscorpio19Noch keine Bewertungen

- Ejemplos Manejo de Interrupciones Múltiples - TMR0Dokument5 SeitenEjemplos Manejo de Interrupciones Múltiples - TMR0scorpio19Noch keine Bewertungen

- Nociones Sobre Muestreo y Reconstrucción de SeñalesDokument9 SeitenNociones Sobre Muestreo y Reconstrucción de Señalesscorpio19Noch keine Bewertungen

- CUADERNODokument15 SeitenCUADERNOJenniffer velezNoch keine Bewertungen

- Estructura de Pilas o StackDokument3 SeitenEstructura de Pilas o StackSergio DominguezNoch keine Bewertungen

- Utilizacion Del Programa Hec-HmsDokument67 SeitenUtilizacion Del Programa Hec-HmselmerNoch keine Bewertungen

- Analisis Costo BeneficioDokument10 SeitenAnalisis Costo BeneficioCamila Torrico BarriosNoch keine Bewertungen

- Densidad y Sus AplicacionesDokument7 SeitenDensidad y Sus AplicacionesAngela VelozNoch keine Bewertungen

- Inecuaciones de Primer Grado y Segundo Grado PDFDokument4 SeitenInecuaciones de Primer Grado y Segundo Grado PDFRoy VasquezNoch keine Bewertungen

- Tecnologia, Un Enfoque FilosoficoDokument116 SeitenTecnologia, Un Enfoque FilosoficoVero GonzalesNoch keine Bewertungen

- Hallar El Vértice y Las Intersecciones Con El Eje X de Una Parábola.Dokument3 SeitenHallar El Vértice y Las Intersecciones Con El Eje X de Una Parábola.Maria Jose Lopez NeedhamNoch keine Bewertungen

- SESIÓN-30 - Reemplazamos Valores de Patrones para Operar AdicionesDokument5 SeitenSESIÓN-30 - Reemplazamos Valores de Patrones para Operar AdicionesGladys Pastor RodríguezNoch keine Bewertungen

- Trabajo Final Algebra LinealDokument16 SeitenTrabajo Final Algebra LinealRicky AlmonteNoch keine Bewertungen

- Temas 9 y 10 Números ÍndicesDokument12 SeitenTemas 9 y 10 Números ÍndicesanNoch keine Bewertungen

- Raz. Matematico PDFDokument74 SeitenRaz. Matematico PDFJosue ChumanNoch keine Bewertungen

- Trabajo en LayoutDokument22 SeitenTrabajo en LayoutFernando Erazo NavarreteNoch keine Bewertungen

- Unidad 1 - Etapa - 1 - Presaberes - G53Dokument11 SeitenUnidad 1 - Etapa - 1 - Presaberes - G53Vctr MaderaNoch keine Bewertungen

- 1 Ieee 1012Dokument58 Seiten1 Ieee 1012SusblankNoch keine Bewertungen

- TESIS Coaquira - Saldivar - Shadia PDFDokument132 SeitenTESIS Coaquira - Saldivar - Shadia PDFApaza Ninaraque DaviddanNoch keine Bewertungen

- Circuitos Contadores PDFDokument6 SeitenCircuitos Contadores PDFmars1972100% (1)

- Ejercicio 4 Calculo de Potencia Contra Angulo de PotenciaDokument4 SeitenEjercicio 4 Calculo de Potencia Contra Angulo de Potenciajarick garcia osorioNoch keine Bewertungen

- Tesis Carlos Uranga 2 CorregidaDokument147 SeitenTesis Carlos Uranga 2 CorregidaCarlos UrangaNoch keine Bewertungen

- GEOGEBRA EN EL AULA - Trabajo Fin de MásterDokument49 SeitenGEOGEBRA EN EL AULA - Trabajo Fin de MásterMartin_Ruiz_JerezNoch keine Bewertungen

- Aporte 1 Jorge Eliecer DiazDokument8 SeitenAporte 1 Jorge Eliecer DiazOscar Fernando Portilla GómezNoch keine Bewertungen

- Matematica Regla de Tres Actualizado 1 10Dokument25 SeitenMatematica Regla de Tres Actualizado 1 10robert guevara cruzNoch keine Bewertungen

- Medida de La Presión de Vapor Del AguaDokument7 SeitenMedida de La Presión de Vapor Del AguaDory Cano DíazNoch keine Bewertungen

- Poesía MatemáticaDokument20 SeitenPoesía MatemáticaIván Hilario QuispeNoch keine Bewertungen

- Historia de Ingeneria EconomicaDokument2 SeitenHistoria de Ingeneria Economicaanon_497465990% (1)

- EJEMPLO de Matriz TPACK para El Diseño de Actividades Del ProyectoDokument6 SeitenEJEMPLO de Matriz TPACK para El Diseño de Actividades Del Proyectogloria amparo garciaNoch keine Bewertungen

- Delgado RubiDokument1 SeiteDelgado RubiJorge Máximo Castillo MinayaNoch keine Bewertungen

- Matematicas-Octavo Ficha 1Dokument2 SeitenMatematicas-Octavo Ficha 1victor quizhpeNoch keine Bewertungen