Beruflich Dokumente

Kultur Dokumente

Design of A Linear and Wide Range Current Starved Voltage Controlled Oscillator For PLL

Hochgeladen von

James MorenoOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Design of A Linear and Wide Range Current Starved Voltage Controlled Oscillator For PLL

Hochgeladen von

James MorenoCopyright:

Verfügbare Formate

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.

1, February 2013

DESIGN OF A LINEAR AND WIDE RANGE CURRENT STARVED VOLTAGE CONTROLLED OSCILLATOR FOR PLL

Mr. Madhusudan Kulkarni1 and Mr. Kalmeshwar N Hosur2

M.Tech student Asst. Professor (Senior Grade) Department of Electronics and Communication Engineering SDM College of Engineering and Technology, Dharwad, Karnataka, INDIA

2

1

madhusudankulkarni15@gmail.com, 2kalmeshwar10@rediffmail.com

ABSTRACT

This paper focuses on design and analysis of Current Starved Ring Voltage Controlled Oscillators (CSVCO) for PLL application. The CSVCO circuit is designed and simulated using GPDK 180nm CMOS Technology. The CSVCO has frequency range from 53 MHz to 2.348 GHz and power consumption is 848W. The jitter is improved by connecting a D Flip Flop. In this design the maximum time jitter after D flip flop is 3.1ps and 1.5ps for rising and falling edge respectively and output frequency is from 173MHz to 1.2GHz. The supply voltage VDD is 1.8V.

KEYWORDS

Ring Oscillator, Voltage Controlled Oscillator (VCO), Current Starved Voltage Controlled Oscillator (CSVCO).

1. INTRODUCTION

In VLSI field the design of a linear and wide range voltage controlled oscillator for RF application is a challenging work for Electronics Engineers. VCO is the main component in the many RF circuits. VCO is the heart of Phase Lock Loop system. An oscillator is an autonomous system which generates a periodic output without any input. The VCO is an electronic circuit which produces the frequency signal depending on its input voltage. VCO is voltage to frequency converter. The Barkhausen criteria for oscillation can be met without resonators as in ring oscillators. If the open loop circuit exhibits sufficient gain at the zero phase frequency, oscillations occurs. The important requirements of VCO are Frequency accuracy, wide tuning range, tuning linearity, low power consumption, small size and low phase noise [1].

2. DIFFERENT ARCHITECTURES OF VCO

The different architectures of VCO are

2.1. LC VCO

These VCOs are made by using inductors and capacitors, with an amplifier. A very high frequency voltage controlled oscillations are generated by using inductors and capacitors. This architecture is preferred for sinusoidal wave output and can be integrated where space is not important issue.

DOI : 10.5121/ijci.2013.2104

23

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.1, February 2013

2.2. Source Coupled VCO

These VCOs are made by using transistors connected back to back. This technique gives high frequency VCOs. These are also used to generate rectangular and saw tooth wave forms. These VCOs can be designed to dissipate less power than the current-starved VCO. The major disadvantage of these configurations is the need for a capacitor, something that may not be available in a single-poly pure digital process without using parasitic.

2.3. Current Starved Ring VCO

These VCOs are made by using ring oscillator. The ring oscillator works by controlling the charging and discharging of the gate capacitance of the next inverter. Decreasing the peak available charging current increases the time to charge and discharge the gate capacitance; consequently, the frequency is decreased [7]. Ring oscillators generate high frequency up to 10 GHz.

3. TRANSFER FUNCTION OF VCO

Ideally the VCO must be capable of transfer the input voltage to frequency linearly as shown in Figure 1.

Figure 1. Transfer Function of VCO The output frequency of the VCO is given by = + . rad/sec where Vinvco is the input voltage to the VCO, o is the free running frequency, KVCO is the gain of the VCO and is given by =2 . rad/sec-volts

(1)

(2)

4. VCO DESIGN

4.1. VCO Design parameters

The VCO designed according to the following specifications as shown in Table 1.

24

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.1, February 2013

Table 1. VCO Design Specifications Parameter Power supply (VDD) Centre frequency No of inverter stages Inverter delay Random jitter (rms) Technology Value 1.8 V 1GHz 3 35ps < 20ps GPDK 180nm

4.2. Ring oscillator

The ring oscillator is made up of 3 inverters connected in ring fashion as shown in Figure 2. The length is fixed at 180nm. The width of PMOS transistor is 3 m and width of NMOS is 700nm is considered for switching point (VSP) at 0.9V. The average delay of each inverter with an inverter as load is 35ps.

Figure 2. Schematic of Ring Oscillator. The frequency of this ring oscillator will be = Hz where N is number of inverter stages = 3 Td is the average time delay of each inverter = 35ps Oscillation frequency is 4.698GHz.

. .

(3)

4.3. Why current starved architecture?

The VDD varies 10% of 1.8V i.e. from 1.62V to 1.98V. For this voltage variation the Ring architecture produces an output frequency from 4.175GHz to 5.077GHz with the difference of 992MHz, which is large variation as shown in Figure 3.

25

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.1, February 2013

Figure 3. Vdd versus output frequency of ring VCO. The output frequency is not stable when it is dependent on VDD. This is made stable by supplying current to each inverter instead of VDD as shown in Figure 4.

4.4. Current Starved VCO

Figure 4. Schematic of Current Starved VCO [2] The schematic of current-starved VCO is shown in Figure4. Its operation is similar to the ring oscillator. MOSFETs M2 and M3 operate as an inverter, while MOSFETs Ml and M4 operate as current sources. The current sources, M1 and M4, limit the current available to the transistor M2 and M3. In other words, the inverter is starved for current. The drain currents of MOSFETs M5 and M6 are the same and are set by the input control voltage. The currents in M5 and M6 are mirrored in each inverter/current source stage. The total capacitance on the drains of M2 and M3 is given by = + (4) = ( + )+ ( + ) (5) This is simply the output and input capacitances of the inverter.This equation can be written in a more useful form as = ( + ) (6) The time taken to charge Ctot from zero to VSP with the constant current ID4 is given by = . (7) where VSP is switching point of the inverter. While the time taken to discharge Ctot from VDD to VSP is given by

26

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.1, February 2013

If we set ID4= ID1= ID (which we will label IDcentre when VinVCO = Vdd/2), then the sum of t1 and t2 is simply . + = (9) The oscillation frequency of the current-starved VCO for N (an odd number > 3) stages is = ( = . . ) (10) which is equal to fcenter (at VinVCO = VDD/2 and ID = IDcenter). The VCO stops oscillating, when VinVCO < VTN. Therefore, we can define Vmin = VTN and fmin= 0. The maximum VCO oscillation frequency, fmax is determined by finding ID when VinVCO=VDD. At the maximum frequency, Vmax= VDD.

(8)

4.5. Linearizing VCO Gain

Figure 5. Linearizing VCO Gain [2] To make the current in a MOSFET linearly related to the VCO's input voltage, consider the circuit shown in Figure 5. The width of M5R is made wide so that its VGS is always approximately VTN. Note that the current in M6R is mirrored over to M6 and M5 to control the current used in the current-starved VCO. The drain current of M5R is shown in Figure 6. The drain current linearity is also depends on the width of M6R transistor. The width of M6R is 10m and the width of M5R is made high and is taken as 100m. The Figure 6 shows the VinVCO vs drain current of M5R transistor. Drain current is linearly dependent on VinVCO.

Figure 6. Drain current of M5R versus VinVCO. The average current drawn by the VCO is

27

. = . . or Iavg = ID The average power dissipated by the VCO is = . = .

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.1, February 2013

(11) 12) (13)

5. IMPLEMENTATION AND RESULTS

The final design of linear wide range current starved voltage controlled oscillator is shown in Figure 7.

Figure 7. Complete Current Starved VCO

2500 2000

1500 Frequency (MHz) 1000

500

0 0 0.5 1 1.5 2

Figure 8. Vinvco versus output frequency

Figure 9. Vdd versus output frequency of current starved VCO in cadence, difference is 64MHz.

28

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.1, February 2013

It is observed from Figure 9 that the variation in VDD from 1.62V to 1.98V i.e. 10% of 1.8V, which varies the output frequency by 64MHz. Therefore the output frequency of VCO is controlled by current. This produces stable oscillations irrespective of VDD variations.

5.1. Jitter Improvement

The jitter of the complete current starved VCO is as shown in Figure 10. The Figure 11 shows the eye diagram of output waveforms of the VCO after divider.

Figure 10. Eye diagram of the VCO output waveform at 1.456GHz when input is 1V (Contains approx. 708 cycles). There is a time difference of 99.3ps at 50% of VDD. VDD values at top and bottom are 1.519V and 50.22mV respectively. The time jitter can still be made less by connecting a D flip flop at output of VCO. But we get half of the VCO output frequency. In this design we observed the maximum time jitter after D flip flop 3.1ps and 1.5ps for rising and falling edge respectively, and output frequency is from 173MHz to 1.2GHz.

Figure 11. Jitter calculation after D Flip flop (Divide by 2).

6. CONCLUSIONS

The CSVCO circuit is designed and simulated using GPDK 180nm CMOS Technology. The CSVCO has frequency range from 53 MHz to 2.348 GHz and power consumption is 848W. The jitter is improved by connecting a D Flip Flop (divide by 2). The supply voltage VDD is 1.8V. The current starved oscillator gives a linear voltage controlled oscillations, which is useful for PLL upto a certain GHz frequency range.

29

International Journal on Cybernetics & Informatics ( IJCI) Vol.2, No.1, February 2013

ACKNOWLEDGMENT

The authors would like to acknowledge CEO of ekLakshya VLSI R&D Centre, Hubli, Karnataka, India. We express our sincere thanks to Principal Prof. Dr. S. Mohan Kumar and Prof. Dr. Vijaya C., Head of the Department, staff of Department of E&CE, SDM College of Engineering and Technology, Dharwad for providing their valuable assistance to carry out this work.

REFERENCES

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] Floyd M Gardner, Phase Lock Techniques, 3rd ed., Wiley Interscience Publication, 2005. R. Jacob Baker. CMOS circuit design, Layout and simulation, John Wiley and Sons Inc, Publication, 2010. Paul R Gray, Paul J Hurst, Stephen H. Lewis, Robert G. Meyer, Analysis and Design of Analog Integrated Circuits, 4th Edition, John Wiley & Sons, Inc. Farid Golnaraghi, Benjamin C. Kuo, Automatic Control Systems, 9th Edition, John Wiley & Sons, Inc. Roland E. Best, Phase-Locked Loops Design, Simulation and Applications, 5th edition, McGrawHill Publications. William F. Egan, Phase-Lock Basics, John Wiley & Sons, Inc. Stanley Goldman, Phase-Locked Loop Engineering Handbook for Integrated Circuits, Artech House, Inc, 2007. Behzad Razavi, RF Microelectronics, Prentice Hall communication engineering series. Behzad Razavi, Design of Analog CMOS Integrated Circuits, International Edition, McGraw Hill publications, 2001. Cadence manual, 2004.

Authors Short Biography Mr. Madhusudan Kulkarni was born in Kukanur Karnataka in 1978. He received the AMIE Degree in Electronics and Communication Engineering from Institution of Engineers (India), Kolkata in 2005 & pursuing M.Tech. Degree in Digital Electronics at SDMCET, Dhavalgiri, Dharwad. Currently he is working on Design of PLL for RF application. He was Head of Department and Lecturer in Electronics & Communication at Oxford Polytechnic, Hubli. His interests are in Digital System Design using VLSI/CMOS Technology, Analog and Mixed mode Designs and Network Analysis. Prof. Kalmeshwar N. Hosur was born in Karnataka in 1975. He received the M.Tech. in VLSI Design and Embedded Systems from VTU extension centre, SJCE Mysore in 2007. Currently he is working as Assistant Professor Senior Grade, Department of Electronics and Communication, SDMCET, Dhavalgiri, Dharwad and he is pursuing Ph.D. at VTU, Belgaum. His interests of research are in VLSI Field (Data Converter Architectures, Analog Electronic Circuits, Network Analysis, CMOS VLSI Design, Analog & Mixed Mode VLSI Circuits, VHDL).

30

Das könnte Ihnen auch gefallen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Design of High Frequency Voltage Controlled OscillDokument5 SeitenDesign of High Frequency Voltage Controlled OscillmoezawNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- CMOS Quadrature VCO Implemented With TwoDokument3 SeitenCMOS Quadrature VCO Implemented With Two2K20-A1-32 AbdelrahmanNoch keine Bewertungen

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsVon EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNoch keine Bewertungen

- A Low Power VCO Design Using Composite Load For Delay Cell With IMOS Varactor For Wider Tuning RangeDokument21 SeitenA Low Power VCO Design Using Composite Load For Delay Cell With IMOS Varactor For Wider Tuning RangeDEEPAK PRAJAPATINoch keine Bewertungen

- 110 Waveform Generator Projects for the Home ConstructorVon Everand110 Waveform Generator Projects for the Home ConstructorBewertung: 4 von 5 Sternen4/5 (1)

- Design and Implementation of 1 GHZ Current Starved Voltage Controlled Oscillator (Vco) For PLL Using 90Nm Cmos TechnologyDokument6 SeitenDesign and Implementation of 1 GHZ Current Starved Voltage Controlled Oscillator (Vco) For PLL Using 90Nm Cmos Technologyanon_701088587Noch keine Bewertungen

- A Wide Tuning Range Voltage-Controlled Ring Oscillator Dedicated To Ultrasound TransmitterDokument4 SeitenA Wide Tuning Range Voltage-Controlled Ring Oscillator Dedicated To Ultrasound TransmitterEldhose VargheseNoch keine Bewertungen

- A 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyDokument9 SeitenA 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyAdam HernandezNoch keine Bewertungen

- Review Paper On Vco - FinalDokument4 SeitenReview Paper On Vco - FinalPunitAgrawalNoch keine Bewertungen

- CMOS Current Starved Voltage Controlled Oscillator Circuit For A Fast Locking PLLDokument5 SeitenCMOS Current Starved Voltage Controlled Oscillator Circuit For A Fast Locking PLLSai KishoreNoch keine Bewertungen

- A 6.1-7.68 GHZ CMOS LC-Voltage Controlled Oscillators (VCO)Dokument4 SeitenA 6.1-7.68 GHZ CMOS LC-Voltage Controlled Oscillators (VCO)dhrubNoch keine Bewertungen

- Low Phase Noise Current Starved Ring VCO On MOS Capacitance: Ashu Tilwe, R.C.Gurjar, D.K.MishraDokument6 SeitenLow Phase Noise Current Starved Ring VCO On MOS Capacitance: Ashu Tilwe, R.C.Gurjar, D.K.MishraManoj BoraNoch keine Bewertungen

- MV - An E-Band Low-Noise Transformer-Coupled Quadrature VCO in 40 NM CMOSDokument9 SeitenMV - An E-Band Low-Noise Transformer-Coupled Quadrature VCO in 40 NM CMOSsm123ts456Noch keine Bewertungen

- L.C Oscillator Tutorial: 1 AbstractDokument18 SeitenL.C Oscillator Tutorial: 1 AbstractChi PhamNoch keine Bewertungen

- Ijatcse18692202020200511 64048 Alnur7 With Cover Page v2Dokument7 SeitenIjatcse18692202020200511 64048 Alnur7 With Cover Page v2YasmenNoch keine Bewertungen

- VCO Based ADCDokument3 SeitenVCO Based ADCBlake PayriceNoch keine Bewertungen

- Analysis and Characterization of Various Current Mirror Topologies in 90 NM TechnologyDokument6 SeitenAnalysis and Characterization of Various Current Mirror Topologies in 90 NM TechnologyGurinder Pal SinghNoch keine Bewertungen

- AN650 - Max038 PDFDokument15 SeitenAN650 - Max038 PDFbetodias30Noch keine Bewertungen

- GuhaRoyAnkurElectricalEngineeringComputerScience350mV5GHzClass DEnhancedSwing PDFDokument41 SeitenGuhaRoyAnkurElectricalEngineeringComputerScience350mV5GHzClass DEnhancedSwing PDFAhmed EmadNoch keine Bewertungen

- CMOS Implemented VDTA Based Colpitt OscillatorDokument4 SeitenCMOS Implemented VDTA Based Colpitt OscillatorijsretNoch keine Bewertungen

- Wide Frequency Range Voltage Controlled Ring Oscillators Based On Transmission GatesDokument4 SeitenWide Frequency Range Voltage Controlled Ring Oscillators Based On Transmission GatesRam MNoch keine Bewertungen

- Department of Computer Engineering, University of Maiduguri, NigeriaDokument11 SeitenDepartment of Computer Engineering, University of Maiduguri, NigeriaOyeniyi Samuel KehindeNoch keine Bewertungen

- Designs of CMOS Multi-Band Voltage Controlled Oscillator Using Active InductorsDokument4 SeitenDesigns of CMOS Multi-Band Voltage Controlled Oscillator Using Active Inductorsrahms79Noch keine Bewertungen

- Using A VCXODokument6 SeitenUsing A VCXOBulentNoch keine Bewertungen

- A Multiobjective Optimization Based Fast and Robust Design Methodology For Low Power and Low Phase Noise Current Starved VCODokument6 SeitenA Multiobjective Optimization Based Fast and Robust Design Methodology For Low Power and Low Phase Noise Current Starved VCODarshan GabhaneNoch keine Bewertungen

- PLL 4Dokument9 SeitenPLL 4vermavikki97Noch keine Bewertungen

- Ring Oscillators: Characteristics and Applications: M K Mandal & B C SarkarDokument10 SeitenRing Oscillators: Characteristics and Applications: M K Mandal & B C SarkarIdk RebollosNoch keine Bewertungen

- Single-Phase Sine Wave Frequency Inverter Power SuDokument7 SeitenSingle-Phase Sine Wave Frequency Inverter Power SuCesar JakobyNoch keine Bewertungen

- A Low-Voltage Current Conveyor Using Inverter-Based Error Amplifier and Its Oscillator ApplicationDokument7 SeitenA Low-Voltage Current Conveyor Using Inverter-Based Error Amplifier and Its Oscillator ApplicationAshin AntonyNoch keine Bewertungen

- Cascode AmplifierDokument4 SeitenCascode AmplifierappuamreddyNoch keine Bewertungen

- 665report - Design of CMOS Ring VCO and Quadrature LC VCO For 8 Phases GenerationDokument17 Seiten665report - Design of CMOS Ring VCO and Quadrature LC VCO For 8 Phases GenerationapplebeeNoch keine Bewertungen

- A Low-Jitter Phase-Locked Loop Architecture For Clock Generation in Analog To Digital ConvertersDokument4 SeitenA Low-Jitter Phase-Locked Loop Architecture For Clock Generation in Analog To Digital ConvertersMadhavi PokuriNoch keine Bewertungen

- Implementation of Frequency Demodulator Using The PLL Demodulation MethodDokument4 SeitenImplementation of Frequency Demodulator Using The PLL Demodulation MethodasmonovNoch keine Bewertungen

- Low Cost LCD Frequency MeterDokument54 SeitenLow Cost LCD Frequency MeterSumit AgarwalNoch keine Bewertungen

- Digitally Controlled Oscillator ReportDokument18 SeitenDigitally Controlled Oscillator ReportVinidhra ShivakumarNoch keine Bewertungen

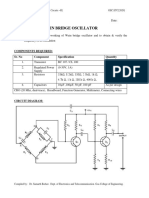

- Expt 5 - Wein Bridge Oscillator (2020)Dokument3 SeitenExpt 5 - Wein Bridge Oscillator (2020)samarthNoch keine Bewertungen

- Cntfet Technology Based Precision Full-Wave Rectifier Using DDCCDokument8 SeitenCntfet Technology Based Precision Full-Wave Rectifier Using DDCCresearchinventyNoch keine Bewertungen

- Chidumes Presentation 2Dokument13 SeitenChidumes Presentation 2Chidume NonsoNoch keine Bewertungen

- The Analog Behavior of Pseudo Digital Ring Oscillators Used in VCO ADCsDokument14 SeitenThe Analog Behavior of Pseudo Digital Ring Oscillators Used in VCO ADCszhaohhhengNoch keine Bewertungen

- MT 028Dokument7 SeitenMT 028SuwitnoNoch keine Bewertungen

- Realization of Voltage Mode Universal Filter by Using Single Differential Voltage Current Conveyor Transconductance AmplifierDokument4 SeitenRealization of Voltage Mode Universal Filter by Using Single Differential Voltage Current Conveyor Transconductance AmplifierijsretNoch keine Bewertungen

- Analysis of Low Voltage Bulk-Driven High Swing Cascode Current Mirrors For Low Voltage ApplicationsDokument10 SeitenAnalysis of Low Voltage Bulk-Driven High Swing Cascode Current Mirrors For Low Voltage ApplicationsIJRASETPublicationsNoch keine Bewertungen

- Lab ManualDokument56 SeitenLab ManualNarendra ReddyNoch keine Bewertungen

- D Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various ProtectionsDokument6 SeitenD Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various Protectionsঅর্ণব কোলেNoch keine Bewertungen

- Ijecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)Dokument10 SeitenIjecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)IAEME PublicationNoch keine Bewertungen

- An Ultra-Low Voltage High Gain Operational Transconductance Amplifier For Biomedical ApplicationsDokument4 SeitenAn Ultra-Low Voltage High Gain Operational Transconductance Amplifier For Biomedical Applications90413027Noch keine Bewertungen

- FSKDokument10 SeitenFSKJyotirmoy DekaNoch keine Bewertungen

- Integrated Circuit Systems, IncDokument11 SeitenIntegrated Circuit Systems, Incroger marqNoch keine Bewertungen

- Application Note 9017 Manufacturing Technology of A Small Capacity Inverter Using A Fairchild IGBTDokument28 SeitenApplication Note 9017 Manufacturing Technology of A Small Capacity Inverter Using A Fairchild IGBTRajesh VyasNoch keine Bewertungen

- Robust Study and Design of A Low Power CMOS CSVCO Using 45nm TechnologyDokument4 SeitenRobust Study and Design of A Low Power CMOS CSVCO Using 45nm TechnologyManoj BoraNoch keine Bewertungen

- Design-of-Astable-Multivibrator-Circuit - Mini Projects - Electronics Tutorial - Electronics TutorialDokument6 SeitenDesign-of-Astable-Multivibrator-Circuit - Mini Projects - Electronics Tutorial - Electronics TutorialGangireddy SanjeevNoch keine Bewertungen

- A Wide Range CMOS VCO For PLL Applications: Abstract - This Paper Describes A Six Phase Differential WideDokument6 SeitenA Wide Range CMOS VCO For PLL Applications: Abstract - This Paper Describes A Six Phase Differential WideRamesh SNoch keine Bewertungen

- Phase Locked Loop (Design and Implementation) : SNEHIL VERMA (14700)Dokument22 SeitenPhase Locked Loop (Design and Implementation) : SNEHIL VERMA (14700)dharmendra kumarNoch keine Bewertungen

- 11 Chapter03 PDFDokument13 Seiten11 Chapter03 PDFAtulNoch keine Bewertungen

- Performance Analysis of PWM Based Full Wave Bridge InverterDokument9 SeitenPerformance Analysis of PWM Based Full Wave Bridge InverterIJRASETPublicationsNoch keine Bewertungen

- Ijecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)Dokument10 SeitenIjecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)IAEME PublicationNoch keine Bewertungen

- 2009 Lu VcoDokument4 Seiten2009 Lu VcoVijay MuktamathNoch keine Bewertungen

- Sliding Window Sum Algorithms For Deep Neural NetworksDokument8 SeitenSliding Window Sum Algorithms For Deep Neural NetworksJames MorenoNoch keine Bewertungen

- Call For Papers-International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenCall For Papers-International Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- Call For Papers-International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenCall For Papers-International Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- Call For Papers-International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenCall For Papers-International Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- Call For Papers-International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenCall For Papers-International Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- Improving User Experience With Online Learning Using Analytical Comparasions Between Instructors & Students of Qatar UniversityDokument26 SeitenImproving User Experience With Online Learning Using Analytical Comparasions Between Instructors & Students of Qatar UniversityJames MorenoNoch keine Bewertungen

- Call For Papers-International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenCall For Papers-International Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- A Review of Cybersecurity As An Effective Tool For Fighting Identity Theft Across The United StatesDokument12 SeitenA Review of Cybersecurity As An Effective Tool For Fighting Identity Theft Across The United StatesJames MorenoNoch keine Bewertungen

- A New Method To Explore The Integer Partition ProblemDokument9 SeitenA New Method To Explore The Integer Partition ProblemJames MorenoNoch keine Bewertungen

- Call For Papers-International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenCall For Papers-International Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- Investigating The Future of Engineer of 2020' Attributes: Moving From Access To Engagement & Sense of BelongingDokument11 SeitenInvestigating The Future of Engineer of 2020' Attributes: Moving From Access To Engagement & Sense of BelongingJames MorenoNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- Advancesin Vision Computing:An International Journal (AVC) : Call For PapersDokument2 SeitenAdvancesin Vision Computing:An International Journal (AVC) : Call For PapersAnonymous zsOsFoNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- Advancesin Vision Computing:An International Journal (AVC) : Call For PapersDokument2 SeitenAdvancesin Vision Computing:An International Journal (AVC) : Call For PapersAnonymous zsOsFoNoch keine Bewertungen

- Call For Papers - InformaticsEngineering, anInternationalJournal (IEIJ)Dokument2 SeitenCall For Papers - InformaticsEngineering, anInternationalJournal (IEIJ)Anonymous w6iqRPANoch keine Bewertungen

- Scope & Topics: ISSN: 0976-9404 (Online) 2229-3949 (Print)Dokument2 SeitenScope & Topics: ISSN: 0976-9404 (Online) 2229-3949 (Print)ijgcaNoch keine Bewertungen

- International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenInternational Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenInternational Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenInternational Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- International Journal of Game Theory and Technology (IJGTT)Dokument2 SeitenInternational Journal of Game Theory and Technology (IJGTT)CS & ITNoch keine Bewertungen

- Call For Papers-International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenCall For Papers-International Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- International Journal On Cybernetics & Informatics (IJCI)Dokument2 SeitenInternational Journal On Cybernetics & Informatics (IJCI)James MorenoNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- International Journal On Cloud Computing: Services and Architecture (IJCCSA)Dokument2 SeitenInternational Journal On Cloud Computing: Services and Architecture (IJCCSA)Anonymous roqsSNZNoch keine Bewertungen

- Teaching and Learning With Ict Tools: Issues and ChallengesDokument8 SeitenTeaching and Learning With Ict Tools: Issues and ChallengesJames MorenoNoch keine Bewertungen

- Blinking RGB Led Using Arduino UNO.: Practical No:-1 Aim: - Circuit DiagramDokument29 SeitenBlinking RGB Led Using Arduino UNO.: Practical No:-1 Aim: - Circuit DiagramSanket DalviNoch keine Bewertungen

- ME1117 (Pb-Free) : 1A Low Dropout Voltage RegulatorDokument9 SeitenME1117 (Pb-Free) : 1A Low Dropout Voltage RegulatorGeovanny SanJuanNoch keine Bewertungen

- M7A39v1.4 B350M GAMING PRO Placa Baza PC IonutDokument21 SeitenM7A39v1.4 B350M GAMING PRO Placa Baza PC IonutdjbobyNoch keine Bewertungen

- PHY-101 - Applied OpticsDokument2 SeitenPHY-101 - Applied Opticspriyanshi mishraNoch keine Bewertungen

- PUTDokument15 SeitenPUTDaisuke NiwaNoch keine Bewertungen

- Keller: P T T S 21 RDokument2 SeitenKeller: P T T S 21 RAmal AntonyNoch keine Bewertungen

- Modular Valves PDFDokument63 SeitenModular Valves PDFMd EliasNoch keine Bewertungen

- Physics Paper 2 SF 026/2 PSPSM Semester 2 Session 2013/2014Dokument11 SeitenPhysics Paper 2 SF 026/2 PSPSM Semester 2 Session 2013/2014Fun Fun Tik TokNoch keine Bewertungen

- ARK-B 220 L5: Powered byDokument4 SeitenARK-B 220 L5: Powered byJegadeshwaran RNoch keine Bewertungen

- Course+Assessment+Rubrics+Microprocessor+Interfacing+ +programmingDokument3 SeitenCourse+Assessment+Rubrics+Microprocessor+Interfacing+ +programmingHassan AliNoch keine Bewertungen

- High Performance Mobile Surgical C-Arm: H.F. Generator & Rotating Anode Tube With Digital WorkstationDokument5 SeitenHigh Performance Mobile Surgical C-Arm: H.F. Generator & Rotating Anode Tube With Digital WorkstationNasr Eldin Aly100% (1)

- Service Manual: Portable Minidisc PlayerDokument26 SeitenService Manual: Portable Minidisc PlayerAnonymous Lfgk6vygNoch keine Bewertungen

- Ormazabal Reference List Secondary Gis 2016Dokument32 SeitenOrmazabal Reference List Secondary Gis 2016ThiagoPinheiroNoch keine Bewertungen

- DATA LOGGER Trouble ShootingDokument74 SeitenDATA LOGGER Trouble ShootingGhyliving GhyNoch keine Bewertungen

- Confidential: Service ManualDokument108 SeitenConfidential: Service Manualmrservice7782100% (1)

- Auto1232 - 1238-532 - E - Controller - Revised 4 - 28 - 21Dokument66 SeitenAuto1232 - 1238-532 - E - Controller - Revised 4 - 28 - 21Edgar MartínNoch keine Bewertungen

- Intensium Max+ 20E: ® Very High Energy Lithium-Ion Container 1.2 MWH - 2.5 MWDokument2 SeitenIntensium Max+ 20E: ® Very High Energy Lithium-Ion Container 1.2 MWH - 2.5 MWCristian HernándezNoch keine Bewertungen

- Synchronous Machines3Dokument103 SeitenSynchronous Machines3Daniela CastroNoch keine Bewertungen

- Marshalling KioskDokument4 SeitenMarshalling KioskThant Zin100% (1)

- 01-04 ChassisDokument433 Seiten01-04 ChassisThị Thanh Thảo TrầnNoch keine Bewertungen

- GroE Fiam ImoedanceDokument2 SeitenGroE Fiam ImoedanceJawad AmjadNoch keine Bewertungen

- LonWorks Design Guide BRDokument14 SeitenLonWorks Design Guide BRasifaliabidNoch keine Bewertungen

- Anna University: Chennai - 600 025Dokument4 SeitenAnna University: Chennai - 600 025RamJiDRNoch keine Bewertungen

- 0044-092-05 - Fireray One User Guide EnglishDokument16 Seiten0044-092-05 - Fireray One User Guide EnglishVladimir BukaricaNoch keine Bewertungen

- Central Power Research Institute PDFDokument26 SeitenCentral Power Research Institute PDFKhashane Willy MohaleNoch keine Bewertungen

- 1 Component Surface Mount Technology (SMT) : Intel® Manufacturing Enabling Guide May 2010Dokument23 Seiten1 Component Surface Mount Technology (SMT) : Intel® Manufacturing Enabling Guide May 2010Marco TassiNoch keine Bewertungen

- American University of Sharjah Department of Electrical EngineeringDokument5 SeitenAmerican University of Sharjah Department of Electrical EngineeringNajmul Puda PappadamNoch keine Bewertungen

- OIM GB 1190056002 Cnt0Dokument360 SeitenOIM GB 1190056002 Cnt0Sandi Junior SihotangNoch keine Bewertungen

- Air Cooled Type Chiller: Operation ManualDokument28 SeitenAir Cooled Type Chiller: Operation ManualmodussarNoch keine Bewertungen

- S1500e Series Installation Guide v260-V30Dokument47 SeitenS1500e Series Installation Guide v260-V30Jose Enrique SantamariaNoch keine Bewertungen

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonVon EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonBewertung: 5 von 5 Sternen5/5 (2)

- Electronics All-in-One For Dummies, 3rd EditionVon EverandElectronics All-in-One For Dummies, 3rd EditionBewertung: 5 von 5 Sternen5/5 (2)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeVon EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeBewertung: 4.5 von 5 Sternen4.5/5 (9)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesVon EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesBewertung: 5 von 5 Sternen5/5 (1)

- Digital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosVon EverandDigital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosBewertung: 5 von 5 Sternen5/5 (1)

- Analog Design and Simulation Using OrCAD Capture and PSpiceVon EverandAnalog Design and Simulation Using OrCAD Capture and PSpiceNoch keine Bewertungen

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialVon EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialBewertung: 3.5 von 5 Sternen3.5/5 (3)

- ARDUINO CODE: Mastering Arduino Programming for Embedded Systems (2024 Guide)Von EverandARDUINO CODE: Mastering Arduino Programming for Embedded Systems (2024 Guide)Noch keine Bewertungen

- Upcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)Von EverandUpcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)Bewertung: 4.5 von 5 Sternen4.5/5 (2)

- Practical Power Distribution for IndustryVon EverandPractical Power Distribution for IndustryBewertung: 2.5 von 5 Sternen2.5/5 (2)

- Current Interruption Transients CalculationVon EverandCurrent Interruption Transients CalculationBewertung: 4 von 5 Sternen4/5 (1)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tVon EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tBewertung: 4.5 von 5 Sternen4.5/5 (27)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsVon EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsBewertung: 3.5 von 5 Sternen3.5/5 (2)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionVon EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionBewertung: 4.5 von 5 Sternen4.5/5 (543)

- Heat Transfer Engineering: Fundamentals and TechniquesVon EverandHeat Transfer Engineering: Fundamentals and TechniquesBewertung: 4 von 5 Sternen4/5 (1)

- The Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesVon EverandThe Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesBewertung: 5 von 5 Sternen5/5 (1)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersVon Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersBewertung: 5 von 5 Sternen5/5 (1)

- Wearable Sensors: Fundamentals, Implementation and ApplicationsVon EverandWearable Sensors: Fundamentals, Implementation and ApplicationsEdward SazonovNoch keine Bewertungen