Beruflich Dokumente

Kultur Dokumente

Circuitos Secuenciales

Hochgeladen von

Vitore MorleoneOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Circuitos Secuenciales

Hochgeladen von

Vitore MorleoneCopyright:

Verfügbare Formate

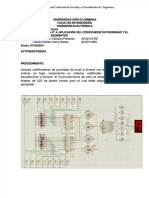

INSTITUTO TECNOLGICO DE AGUASCALIENTES

DEPARTAMENTO DE ELCTRICA Y ELECTRNICA INGENIERIA ELECTRNICA ELECTRONICA I LABORATORIO DE ELECTRNICA

CIRCUITOS SECUENCIALES

PROF: ING. PEDRO LUIS MUOZ LOPEZ

ALUMNO: MORA RO MO VJCTOR MANUEL

30/ 05 /2003

CIRCUITOS SECUENCIALES

MODELOS PAEA LOS CIRCUITOS SECUENCIALES El concepto secuencial no se restringe a los sistemas digitales. Por ejemplo, consideraremos el funcionamiento de un evaluador en un edificio de 4 pisos. El elevador acta como un circuito secuencial, ya que sus acciones estn determinadas por seales de entrada de sus tableros de control (en el elevador y en cada piso) y por su condicin actual, en el piso 1, 2, 3 o 4. El elevador debe recordar su posicin actual para determinar su siguiente transicin de piso. Por tanto, definimos el estado presente del elevador como una descripcin de su posicin de piso actual, con un historial de sus transiciones de piso pasadas. Un circuito lgico secuencial es aquel cuyas salidas no slo dependen de sus entradas actuales, sino tambin de una secuencia de entradas anterior, que, tal vez, sea arbitrariamente grande. El circuito de botones para el control de canales ascendentes y descendentes de una televisin o video casetera, es un circuito secuencial: la seleccin del canal depende de la secuencia pasada de pulsos de botn ascendente o descendente de canal, desde 10 horas antes, por lo menos o, quizs, desde la primera vez que activ la televisin. As, es inconveniente y, a menudo, imposible describir el comportamiento de un circuito secuencial por medio de una tabla que liste las salidas en funcin de la secuencia de entradas que se han recibido hasta el momento presente. Con el selector de canales de la televisin es imposible determinar que canal se ha seleccionado en el momento con slo ver la secuencia precedente de cambios en el selector de canales, ni aunque veamos la secuencia de los 10 o 100 pulsos precedentes, Se necesita ms informacin: el estado actual del selector de canales. El estado de un circuito secuencial, es una coleccin de variables de estado, cuyos valores en cualquier momento contienen toda la informacin pasada necesaria para establecer el comportamiento futuro del circuito. En un circuito lgico digital, las variables de estado son valores binarios correspondientes a ciertas seales lgicas del circuito. Un circuito con n variables de estado binarias tiene 2 n estados posibles. Por muy grande que parezca, 2 n siempre es finito, nunca infinito, de modo que los circuitos secuenciales son llamados, algunas veces, maquinas de estado finitos. los cambios de estado de la mayora de los circuitos secuenciales ocurren en tiempos especficos por una seal de reloj que corre libremente.

Los circuitos secuenciales en cambio, utilizan elementos de memoria (capaces de almacenar informacin binaria), por lo que la respuesta en las salidas no depende solamente del estado presente en las entradas sino tambin de la informacin previamente almacenada; es decir, una misma combinacin de estados en las entradas puede producir estados de salida diferentes. Los elementos de memoria ms simples son los latchs (o cerrojos biestables) y los flip-flops (o multivibradores biestables).

Son circuitos secuenciales: Las puertas los latchs y los flip-flops, los codificadores, los generadores de pulsos, los decodificadores, los registros de almacenamiento, los multiplexores, los registros de desplazamiento, los demultiplexores, los contadores, algunos circuitos aritmticos las memorias y los microprocesadores.

Los sistemas digitales pueden operar en forma asncrona o sncrona. En los sistemas asncronos, las salidas de los circuitos lgicos pueden cambiar de estado en cualquier momento en que una o mas de las entradas cambie. En los sistemas sncronos los tiempos exactos en que alguna salida puede cambiar de estado se determinan por medio de una seal denominada reloj o clock. Esta seal de reloj consiste en una serie de pulsos rectangulares o cuadrados como se muestra en la figura.

Denominaremos periodo al tiempo entre transiciones sucesivas en la misma direccin, esto es entre dos flancos de subida o entre dos flancos de bajada. La transicin de estado en los circuitos secuenciales sncronos se efectan en el momento en el que el reloj hace una transicin entre 0 y 1 (flanco de subida) o entre 1 y 0 (flanco de bajada). Entre pulsos sucesivos de reloj no se efectan cambios. DISPOSITIVOS DE MEMORIA En las aplicaciones de circuitos de conmutacin, casi todos los elementos de memoria son circuitos electrnicos biestables; es decir, existen indefinidamente en uno de dos posibles estados estables, 0 y 1. Los datos binarios se guardan en un elemento de memoria haciendo que el elemento pase al estado 0 para almacenar un 0 y al estado 1 para almacenar un 1. La salida q del circuito indica el estado presente del memoria. cada circuito de memoria tiene una o ms entradas de excitacin, llamadas as por que sirven para excitar o llevar el circuito a un estado deseado. los dispositivos de memoria reciben por lo general su nombre con base en sus entradas de excitacin particulares, diferentes de un dispositivo a otro.

El inverso del periodo es lo que denominamos la frecuencia del reloj. El ancho del pulso de reloj es el tiempo durante el cual la seal de reloj est en 1.

En el anlisis anterior sobre el latch SC podemos ver que es un circuito asncrono, ya que el estado cambia en cualquier momento que cambiemos las entradas y no sincronizado con un pulso de reloj. Para hacerlo sncrono se aade una entrada adicional como se muestra en la figura. El flip-flop sincronizado por reloj consiste del latch bsico con compuertas NOR mostrado anteriormente y dos compuertas AND. La salida de las dos compuertas AND quedar en 0 mientras el pulso de reloj est en 0, sin importar los valores de entrada de S y C. Cuando el pulso de reloj est en 1, la informacin de las entradas S y C pasa hacia el latch bsico. Como puede verse en el diagrama de tiempo, en este tipo de FF ahora los cambios se producen solamente cuando la seal de reloj est en 1. Pero esto no previene que el FF cambie varias veces durante un ciclo de reloj, y esto no es un comportamiento deseado, por lo tanto de alguna manera este FF sigue siendo de alguna manera asncrono (por lo menos mientras el pulso de reloj est en 1). Hay dos maneras de arreglar esto. Una es la de que el estado cambie una vez que termine el ciclo de reloj, y otra es la que el cambio ocurra en los flancos de bajada o de subida del pulso de reloj. Mas adelante se explicar como hacerlo. Nota: Hasta ahora hemos hablado indistintamente de latch o Flip-flop. La literatura es variada en este aspecto, y para efecto de este curso nos referiremos en general a todos estos circuitos como flip-flop(FF). En general se llama latch al circuito que sea asncrono y transparente, y Flip-Flop a los que sean sncronos y no transparentes. 1. Asncrono: las salidas cambian independientemente del reloj . 2. Transparente: las salidas cambian inmediatamente en respuesta a un cambio en las entradas. 3. Sncrono: las salidas cambian en los flancos de subida o bajada del pulso de reloj.

4. No transparente: durante la duracin del pulso de reloj, los cambios en las entradas no se reflejan en las salidas. En la gua siguiente (Flip-Flop) nos referiremos al tipo de FF que utilizaremos a lo largo del curso: los FF disparados por flanco.

Antes de pasar definitivamente a estudiar el comportamiento de los flip flop veamos otras configuraciones.

Flip Flop tipo J K

Un flip flop JK es un refinamiento del flip flop SC, en el que se elimina el estado indeterminado. Para J=K=1 el estado futuro ser igual al estado presente negado: Qn+1 =

TABLA CARACTERISTICA

S C Qn+1 0 0 0 1 1 0 1 1 Qn 0 1

Flip Flop tipo D

El flip-flop tipo D mostrado en la figura es una modificacin del FF SC. La entrada D va directamente hacia la entrada S y el complemento de D hacia la entrada C. De esta forma tenemos que el estado futuro ser igual al valor de la entrada D.

TABLA CARACTERISTICA

D 0 1

Qn+1 0 1

Flip Flop tipo T

Un flip flop tipo T se obtiene uniendo las dos entradas de un flip flop tipo JK. Si T=0 se mantendr el estado, si T=1 el estado futuro ser igual al complemento del estado presente.

TABLA CARACTERISTICA

T 0 1

Qn+1 Qn

Para todos los FF anteriores la tabla caracteristica describe el comportamiento del FF mientras el reloj est en 1. Durante el periodo en el que el reloj est en 0, no hay cambios en las salidas. Se denominan flip flop disparados por nivel. No es objetivo de este curso el anlisis detallado del comportamiento interno de los flip flops. Solo se muestra la circuiteria interna como referencia. En lo futuro indicaremos los flip flops con su diagrama simplificado.

Entradas asncronas

Los Flip-flops contenidos en los circuitos integrados a menudo proveen unas entradas adicionales para fijar en el estado 1 o en el 0 al FF en cualquier momento de forma asncrona, sin importar las condiciones presentes en las otras entradas. Esta entradas son normalmente llamadas SET o PRESET (para fijar en 1) o CLEAR (para fijar en 0). Son tiles para colocar los FF en un estado inicial, antes de comenzar con su funcionamiento de forma sncrona, sin la necesidad de utilizar un pulso de reloj. Por ejemplo, despus de encender un sistema digital, el estado inicial de los FF es indeterminado. Activando la entrada de clear, se inicializan en cero, y luego se comienza con el funcionamiento normal.

La figura muestra un FF con las entradas adicionales mencionadas. Para efecto de este curso y para simplificar los diagramas, a menudo se obviar la inclusin de estas entradas adicionales, si no son necesarias. Estas entradas pueden actuar con un nivel ALTO ( 1 ) o con un nivel BAJO (0) . En las tablas de especificaciones de los circuitos integrados se incluyen tablas que indican en cada caso la forma de funcionamiento. En el caso que se muestra, al aplicar un 0 en la entrada de clear el FF se fijar en 0.

TABLAS Y DIAGRAMAS DE ESTADO Las ecuaciones lgicas y las ecuaciones vectoriales definen por completo el comportamiento del circuito secuencial, para un dispositivo de memoria dado. Sin embargo, la descripcin, si bien es completa, no presenta una imagen calara de las relaciones entre las variables pertinentes. La relacin funcional existente entre la entrada, la salida, el estado presente y el siguiente estado se muestran de manera clara en tabla estados o diagramas de estados. El diagrama de estados es una representacin grfica de un circuito secuencial, en la que los estados del circuito aparecen como crculos y las transiciones de estado (el paso del estado presente y al siguiente estado Y) se indican con flechas. cada flecha est rotulada con las entrada x y la salida del circuito correspondiente z. La figura 4.2 muestra el diagrama de estados del contador. Notar que como no existen entradas, slo hay una posible alternativa como estado siguiente dado un estado actual.

Figure 4.2: Diagrama de estados de un contador BCD.

Figure 4.5: Diagrama de estados de un contador sncrono BCD ascendente/descendente.

Figure 4.8: Diagrama de estados de un detector de tres o ms unos consecutivos.

El comportamiento de los circuitos secuenciales se determina de las entradas, las salidas y los estados de los multivibradores (MVB). Ambas entradas y el estado siguiente son una funcin de las entradas y del estado presente. El anlisis de los circuitos secuenciales consiste en

obtener una tabla o un diagrama de la secuencia de tiempos de las entradas, salidas y estados internos. Es posible escribir expresiones booleanas que describan el comportamiento de los circuitos secuenciales. Sin embargo, estas expresiones deben incluir la secuencia de tiempos necesaria directa o indirectamente. Un diagrama lgico secuencial se reconoce como un circuito si ste incluye multivibradores. Los MVB pueden ser de cualquier tipo y el diagrama lgico puede o no incluir compuertas combinacionales. Muchos circuitos lgicos contienen multivibradores biestables, monoestables y compuertas lgicas que se conectan para realizar una operacin especfica. Con frecuencia se usa una seal de reloj primaria para ocasionar que los niveles lgicos del circuito pasen a travs de una determinada secuencia de estados. En trminos generales, los circuitos secuenciales se analizan siguiendo el procedimiento que se describe a continuacin:

Das könnte Ihnen auch gefallen

- Circuitos SecuencialesDokument5 SeitenCircuitos SecuencialesJuan BagurNoch keine Bewertungen

- Características de La Fuente de Alimentación y Consumo de Potencia Del MicrocontroladorDokument3 SeitenCaracterísticas de La Fuente de Alimentación y Consumo de Potencia Del MicrocontroladorEduardo Vicente Melchi Lagunes100% (1)

- Bitácora de Soporte y MantenimientoDokument5 SeitenBitácora de Soporte y MantenimientoAlejandra Sosa100% (1)

- Circuitos Secuenciales SincronosDokument0 SeitenCircuitos Secuenciales Sincronoswlen2012Noch keine Bewertungen

- Circuitos Secuenciales FlipDokument68 SeitenCircuitos Secuenciales FlipJam PierNoch keine Bewertungen

- Flip - FlopDokument17 SeitenFlip - FlopAna Laura Rios Cayoja100% (1)

- Informe Previo #1aDokument13 SeitenInforme Previo #1aDiego Gutierrez AyalaNoch keine Bewertungen

- Practica Del SemaforoDokument14 SeitenPractica Del SemaforoCristian EscobarNoch keine Bewertungen

- Logica SecuencialDokument15 SeitenLogica SecuencialJose IssaNoch keine Bewertungen

- Dispositivos SecuencialesDokument12 SeitenDispositivos SecuencialesJesus BecerraNoch keine Bewertungen

- Trabajo Investigación Tema 4 (N°c.18500311)Dokument32 SeitenTrabajo Investigación Tema 4 (N°c.18500311)Jason ClementeNoch keine Bewertungen

- Flip FlopsDokument9 SeitenFlip FlopsCarlos ArredondoNoch keine Bewertungen

- Electronica ResumeDokument13 SeitenElectronica ResumeDaniel LopezNoch keine Bewertungen

- Circuito Logico Secuenciales-Sistemas DigitalesDokument11 SeitenCircuito Logico Secuenciales-Sistemas DigitalesJesusNoch keine Bewertungen

- Tema 7Dokument8 SeitenTema 7ALEXIS RONAY SANDOVAL RIOSNoch keine Bewertungen

- I. Resumen Teórico: A) Circuitos SecuencialesDokument24 SeitenI. Resumen Teórico: A) Circuitos SecuencialesAnonymous UI7JawqNoch keine Bewertungen

- Logica SecuencialDokument9 SeitenLogica SecuencialBruno Hernández MartínezNoch keine Bewertungen

- Flip FlopsDokument7 SeitenFlip FlopsJuan LainaNoch keine Bewertungen

- Flip FlopDokument12 SeitenFlip FlopespinozaNoch keine Bewertungen

- 4.4 MultivibradoresDokument33 Seiten4.4 MultivibradoresIvanna LemusNoch keine Bewertungen

- Conclusión: Poseen Dos Estados Estables: .: Circuitos Biestables o Flip-Flop (FF)Dokument12 SeitenConclusión: Poseen Dos Estados Estables: .: Circuitos Biestables o Flip-Flop (FF)Francisco RomeroNoch keine Bewertungen

- TP 14 LocoDokument12 SeitenTP 14 LocoNombre PendienteNoch keine Bewertungen

- Laboratorio 7 de RichardDokument7 SeitenLaboratorio 7 de RichardloganmasterNoch keine Bewertungen

- SISTEMAS DIGITALES Asignacion 9 y 10Dokument25 SeitenSISTEMAS DIGITALES Asignacion 9 y 10jose2001Noch keine Bewertungen

- Unidad 1, 2, 3Dokument30 SeitenUnidad 1, 2, 3Roberto Ruiz AlcántaraNoch keine Bewertungen

- Lección #06 Diseño de Contadores SincronosDokument8 SeitenLección #06 Diseño de Contadores SincronosAnghel CarreroNoch keine Bewertungen

- Resumen de Flip FlopsDokument10 SeitenResumen de Flip FlopserickNoch keine Bewertungen

- Práctica 8 Latches y Flip FlopsDokument4 SeitenPráctica 8 Latches y Flip FlopsRay GzzNoch keine Bewertungen

- Flip FlopDokument24 SeitenFlip FlopCortac BistruishNoch keine Bewertungen

- Sistemas SecuencialesDokument48 SeitenSistemas SecuencialesCristhian Arevalo SilupuNoch keine Bewertungen

- 7Dokument22 Seiten7Percy Flores MoralesNoch keine Bewertungen

- Informe Previo N°7Dokument22 SeitenInforme Previo N°7Hubert Vásquez Cueva100% (1)

- Cto. SecuencialDokument32 SeitenCto. SecuencialAlonso HernándezNoch keine Bewertungen

- UNIDAD 3 ED - Latches y FlipFlopDokument27 SeitenUNIDAD 3 ED - Latches y FlipFlopMynor Augusto Hernández GonzálezNoch keine Bewertungen

- Trabajo Practico Flip-Flops y Circuitos Secuenciales PDFDokument10 SeitenTrabajo Practico Flip-Flops y Circuitos Secuenciales PDFDonaldo Leonel Vargas AnguloNoch keine Bewertungen

- Diseño de Sistemas Digitales Resumen PDFDokument24 SeitenDiseño de Sistemas Digitales Resumen PDFJesus Gerardo Alcocer NavarroNoch keine Bewertungen

- Trabajo Sistemas Digitales Unidad 3Dokument13 SeitenTrabajo Sistemas Digitales Unidad 3Oswaldo RosasNoch keine Bewertungen

- Trabajo de CDDokument10 SeitenTrabajo de CDEricBellidoCastilloNoch keine Bewertungen

- Practica 7 Contadores BinariosDokument9 SeitenPractica 7 Contadores BinariosTorrealba GerardoNoch keine Bewertungen

- Previo 7Dokument7 SeitenPrevio 7Gabriel Hostiliano CoblentzNoch keine Bewertungen

- Bie StablesDokument18 SeitenBie Stableslady67lauraNoch keine Bewertungen

- U03 Circuitos Secuenciales - MultivibradoresDokument25 SeitenU03 Circuitos Secuenciales - MultivibradoresAnonymous m3tTeasYKNoch keine Bewertungen

- cd2 Final1Dokument8 Seitencd2 Final1Eleazar CastilloNoch keine Bewertungen

- Circuitos Logicos SecuencialesDokument6 SeitenCircuitos Logicos SecuencialescesarNoch keine Bewertungen

- Circuitos Lógicos SecuencialesDokument28 SeitenCircuitos Lógicos SecuencialesElian MartinezNoch keine Bewertungen

- 03 - Circuitos Digitales (Secuenciales)Dokument47 Seiten03 - Circuitos Digitales (Secuenciales)Juan Manuel AlmironNoch keine Bewertungen

- Laboratorio 3Dokument14 SeitenLaboratorio 3Alee AlejandroNoch keine Bewertungen

- Informe Previo N 7Dokument22 SeitenInforme Previo N 7Heraud MendozaNoch keine Bewertungen

- Latch's y Flip-FlopDokument21 SeitenLatch's y Flip-FlopWilmar Yovany RojasNoch keine Bewertungen

- Flip FlopDokument6 SeitenFlip FlopJulian Andres EcheverryNoch keine Bewertungen

- Implementación Del Flip-Flop Mediante Compuertas LógicasDokument13 SeitenImplementación Del Flip-Flop Mediante Compuertas LógicasArmandoNoch keine Bewertungen

- Contador Asincrono AscendeneDokument13 SeitenContador Asincrono AscendeneAndiie RiveraNoch keine Bewertungen

- Flip Flop JKDokument6 SeitenFlip Flop JKMigue PicazoNoch keine Bewertungen

- Generador de Disparo Por Circuito Divisor de Frecuencia.Dokument17 SeitenGenerador de Disparo Por Circuito Divisor de Frecuencia.madura123Noch keine Bewertungen

- I Circuitos Secuenciales Básicos 3-09Dokument18 SeitenI Circuitos Secuenciales Básicos 3-09valeria LopezNoch keine Bewertungen

- Electronica Digital Miguel GonzalezDokument14 SeitenElectronica Digital Miguel GonzalezmyhuxNoch keine Bewertungen

- Capitulo 6Dokument5 SeitenCapitulo 6Fanny Vanessa Uc PootNoch keine Bewertungen

- Informe Final de Sistemas DigitalesDokument8 SeitenInforme Final de Sistemas DigitalesnepeNoch keine Bewertungen

- Guia Practica 4Dokument9 SeitenGuia Practica 4jorihuelaNoch keine Bewertungen

- 100 Circuitos de Shields para MotoresVon Everand100 Circuitos de Shields para MotoresBewertung: 4.5 von 5 Sternen4.5/5 (4)

- Formato-Descripción Del Tema o ActividadDokument2 SeitenFormato-Descripción Del Tema o ActividadVitore MorleoneNoch keine Bewertungen

- Documento Practicas 6Dokument108 SeitenDocumento Practicas 6Vitore MorleoneNoch keine Bewertungen

- Practica 2Dokument36 SeitenPractica 2Vitore MorleoneNoch keine Bewertungen

- Practica 2Dokument11 SeitenPractica 2Vitore MorleoneNoch keine Bewertungen

- Practica 1Dokument9 SeitenPractica 1Vitore MorleoneNoch keine Bewertungen

- Problemas Primera ParteDokument15 SeitenProblemas Primera ParteVitore MorleoneNoch keine Bewertungen

- Practica 1Dokument11 SeitenPractica 1Vitore MorleoneNoch keine Bewertungen

- Practica 1Dokument18 SeitenPractica 1Vitore MorleoneNoch keine Bewertungen

- Proyecto Final Selector de CochesDokument12 SeitenProyecto Final Selector de CochesVitore MorleoneNoch keine Bewertungen

- Proyecto Final de Circuitos ElectricosDokument38 SeitenProyecto Final de Circuitos ElectricosUniElectronica50% (2)

- Practica 2n - Circuito CombinacionalDokument13 SeitenPractica 2n - Circuito CombinacionalUniElectronicaNoch keine Bewertungen

- ApuntesDokument5 SeitenApuntesVitore MorleoneNoch keine Bewertungen

- Proteus en 3dDokument21 SeitenProteus en 3dbob75Noch keine Bewertungen

- Reporte Visualizacion y Control de ProcesosDokument11 SeitenReporte Visualizacion y Control de ProcesosVitore MorleoneNoch keine Bewertungen

- Carro Seguidor de LineaDokument37 SeitenCarro Seguidor de LineaUniElectronicaNoch keine Bewertungen

- CAM00006 JPGDokument5 SeitenCAM00006 JPGVitore MorleoneNoch keine Bewertungen

- CopiasDokument20 SeitenCopiasUniElectronicaNoch keine Bewertungen

- Luces AudioritmicasDokument4 SeitenLuces Audioritmicasjosevazxo100% (1)

- Display LED Manejado Con CD 4511Dokument2 SeitenDisplay LED Manejado Con CD 4511Dan RoadsNoch keine Bewertungen

- Clase 13Dokument16 SeitenClase 13Nelson AlbaNoch keine Bewertungen

- Proyecto Final Selector de CochesDokument12 SeitenProyecto Final Selector de CochesVitore MorleoneNoch keine Bewertungen

- CAM00006 JPGDokument5 SeitenCAM00006 JPGVitore MorleoneNoch keine Bewertungen

- Atenuador Con Potenciómetro para Lámparas IncandescentesDokument2 SeitenAtenuador Con Potenciómetro para Lámparas IncandescentesVitore MorleoneNoch keine Bewertungen

- DimmerDokument46 SeitenDimmerVitore MorleoneNoch keine Bewertungen

- Manual Reporte Tabla FenólicaDokument9 SeitenManual Reporte Tabla FenólicaUniElectronicaNoch keine Bewertungen

- Análisis de Circuitois MTR2014!2!2C - Unidad IIIDokument3 SeitenAnálisis de Circuitois MTR2014!2!2C - Unidad IIIVitore MorleoneNoch keine Bewertungen

- Proyecto Final Selector de CochesDokument12 SeitenProyecto Final Selector de CochesVitore MorleoneNoch keine Bewertungen

- Reporte de Proyecto Unidad IiiDokument13 SeitenReporte de Proyecto Unidad IiiVitore MorleoneNoch keine Bewertungen

- ManualDokument13 SeitenManualVitore MorleoneNoch keine Bewertungen

- Reporte de Proyecto Unidad IiiDokument13 SeitenReporte de Proyecto Unidad IiiVitore MorleoneNoch keine Bewertungen

- Informe Completo 1 Primer Parcial, Compuertas or y andDokument10 SeitenInforme Completo 1 Primer Parcial, Compuertas or y andHenry Scrim CPNoch keine Bewertungen

- Formato F-5 (Solicitd PC) 2020Dokument1 SeiteFormato F-5 (Solicitd PC) 2020MauricioD.MéndezNoch keine Bewertungen

- Lab 03 Arqser192Dokument6 SeitenLab 03 Arqser192Carlos SANoch keine Bewertungen

- 5 Proyectos de Microcontroladores (Montajes) - SE342Dokument9 Seiten5 Proyectos de Microcontroladores (Montajes) - SE342Cambiando CaminosNoch keine Bewertungen

- Laboratorio n4 Aplicación Del Codificador de Prioridad y El Decodificador de 7 SegmentosDokument6 SeitenLaboratorio n4 Aplicación Del Codificador de Prioridad y El Decodificador de 7 SegmentosJuan Pablo Penagos LosadaNoch keine Bewertungen

- 2.1 Pic16f877a 1105Dokument29 Seiten2.1 Pic16f877a 1105Viel.proyectosintegralesNoch keine Bewertungen

- Laboratorio de Hardware IDokument2 SeitenLaboratorio de Hardware ILeopoldo Jose MorenoNoch keine Bewertungen

- Cartel de Contenidos Electronica - 2016-CorregidoDokument3 SeitenCartel de Contenidos Electronica - 2016-Corregidodperalta30Noch keine Bewertungen

- Sistemas EmbebidosDokument3 SeitenSistemas Embebidosjoselyn mantuanoNoch keine Bewertungen

- Examen ComputacionDokument9 SeitenExamen Computacionanon_869390812Noch keine Bewertungen

- Practica 5Dokument11 SeitenPractica 5Andrea Alexandra Trujillo OrellanaNoch keine Bewertungen

- Taller 1.2 Componentes Internos y Externos de Un Equipo ComputoDokument9 SeitenTaller 1.2 Componentes Internos y Externos de Un Equipo Computogranjas七つの大罪Noch keine Bewertungen

- SYC Catalogo PDFDokument149 SeitenSYC Catalogo PDFNaciConSolNoch keine Bewertungen

- Test Fund Logica Digital Tarjeta 1Dokument8 SeitenTest Fund Logica Digital Tarjeta 1Jason BourneNoch keine Bewertungen

- Unidad V PLCDokument25 SeitenUnidad V PLCBlas Uriel Castro MirandaNoch keine Bewertungen

- Componentes de Equipo de Computo DDokument33 SeitenComponentes de Equipo de Computo Djucaba76Noch keine Bewertungen

- Qué Es Una Memoria SDRAMDokument4 SeitenQué Es Una Memoria SDRAMAlbertoCoboDiazNoch keine Bewertungen

- Examen 1Dokument14 SeitenExamen 1Alan GrajedaNoch keine Bewertungen

- EEPROM InternaDokument11 SeitenEEPROM InternaJuan Guillermo MansillaNoch keine Bewertungen

- Universidad Autonoma de Quito - UNAQ-: Facultad de Sistemas E Informática - ISINDokument2 SeitenUniversidad Autonoma de Quito - UNAQ-: Facultad de Sistemas E Informática - ISINjose_fc182Noch keine Bewertungen

- Unidad 4 InterfacesDokument13 SeitenUnidad 4 InterfacesGerax TurilliNoch keine Bewertungen

- Tema 12Dokument42 SeitenTema 12holdenNoch keine Bewertungen

- Electronica Digital BasicaDokument3 SeitenElectronica Digital BasicaDavid DavichoNoch keine Bewertungen

- EVOLUPIC Bootloader 16F88 MANUAL V.1 PDFDokument29 SeitenEVOLUPIC Bootloader 16F88 MANUAL V.1 PDFJavier OsorioNoch keine Bewertungen

- Codigo A CombinarDokument10 SeitenCodigo A CombinarMartin PerdomoNoch keine Bewertungen

- Set Instrucciones Intel Sobre Emu8086 2017Dokument5 SeitenSet Instrucciones Intel Sobre Emu8086 2017Esteban RodriguezNoch keine Bewertungen

- Problema2 Control DigitalDokument5 SeitenProblema2 Control DigitalabelNoch keine Bewertungen

- Tutorial MSP430 Prender LedDokument4 SeitenTutorial MSP430 Prender LedHenry LaredoNoch keine Bewertungen