Beruflich Dokumente

Kultur Dokumente

WebPack Generate FPGA

Hochgeladen von

Mehadi Alom ChoudhuryOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

WebPack Generate FPGA

Hochgeladen von

Mehadi Alom ChoudhuryCopyright:

Verfügbare Formate

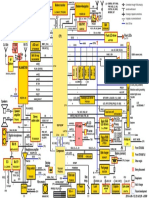

Xilinx ISE Version 12 - Downloading to the FPGA - The final stage!

Target Harware Once the logical behaviour of the VHDL code has been verified through simulation then the design can then be progressed through to Synthesis. Up to now the development has been carried out purely in a "Soft" environment.

Real devices come in different packages with each package having a number of input/output pins, VDD & VSS (Power and Ground) pins, and what are called JTAG pins that allow the device to be configured to fit the design in question. Packages in turn go on Printed Circuit Boards (PCBs) to form an overall system. Some pins may route to LEDs - Some may be connected to switches - others may provide an input clock.

The Board shown here is the Digilent Spartan-3.

Making sure that the "implementation" button is selected in the Hierarchy View And that the correct top level entity is also selected Then using the "Project > New Source" wizard Select Implementation Constraints File And enter a File Name... (Normally the file name is the same as the system, or top level, entity for the design being implemented) And then click "Next >" and then "Finish" in the final window to confirm.

Selecting the "UCF" file in the Hierarchy Window and double clicking "Edit Constraints" in the Processes window will open an empty text edit window: Link Signal names to Pins (UCF) So that the design being created may function correctly on the hardware then the Signal names, or NETS, defined and used within the VHDL may be linked to specific Pins on the device. This may be achieved in various ways according to the version of WebPack being used - but in general the pin mapping information is entered into the "User Constraints File" (.UCF) as a source file within the Project For pin assignments to specific resources on the board such as Switches, Buttons, LEDs, and the Seven Segment Display, please refer to the Spartan 3 Reference Manual.

Page 1 of 3

Xilinx ISE Version 12 - Downloading to the FPGA - The final stage!

"Translate", "Map" and "Place and Route" Device

The remaining tasks of :

Synthesize... Convert the VHDL model into a hardware logic netlist - ie gates and wires, Translating the design netlist into a form that may be then go through Mapping onto the Logic Blocks found on the device. The location of the actual blocks that will be used and interconnected is achieved for an FPGA based design through the use of Place and Route software.

Making sure that the Top Level entity is selected in the Hierarchy window and that "implementation" is also selected in the "Processes" window.... if you Click the '+' sign next to Implement Design then subcommands appear... Double click "Synthesize" - After a short time a green tick should appear. (If there are any Errors then they need to be corrected before proceeding.) Next, Double click "Implement Design" - Further green ticks should appear next to "Translate", "Map" and "Place & Roure". (Again if there are any errors [such as a mistake in the UFC file] then these will need correction and the "implement Design" process repeated. A Double click on "Generate Programming File" creates a .BIT file that holds the configuration data for the FPGA. Configure the FPGA

First make sure that the Power Supply and the Serial Cable to the Programming Port is correctly connected to the FPGA board - and then switch on the power supply. Double Click "Manage Configuration" to open the iMPACT window. The software first needs to detect the FPGA on the board Double click "Boundary Scan" and an empty window opens

Page 2 of 3

Xilinx ISE Version 12 - Downloading to the FPGA - The final stage!

Next "right click" in the empty Boundary Scan window and on the pop-up menu that appears select "Intialize Chain" The systems will then communicate with the Board via the programming cable and identify any devices connected. On the Spartan 3 board two devices should be detected The FPGA and a Serial Prom (not used) The system will then ask if you wish to continue and assign a configuration file. Click "Yes" to continue For the FPGA In the "Assign New Configuration File" prompt select the top_level_name.bit (You may need to navigate to the correct location to find the active Project Folder on your N: Drive) and click Open The "Assign New Configuration File" prompt will appear for the second device - Click "Bypass" to ignore the SPROM. (The System may ask to confirm the device properties Click OK to continue)

FinallyClick the FPGA package symbol in the boundary scan window (it should turn green) And then "Right Click" and select "Program"

A "Program Succeeded" message should appear. (Sometimes the configuration file does not download correctly where one then gets "Program Fail". If this occurs try another "Program" command.) The FPGA will automatically detect any configuration data so there is no need to reset the device to download a new configuration file.

Page 3 of 3

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- MUSW-001 CE Certificate PDFDokument33 SeitenMUSW-001 CE Certificate PDFMehadi Alom ChoudhuryNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

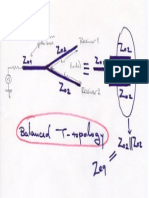

- Balanced T TopologyDokument1 SeiteBalanced T TopologyMehadi Alom ChoudhuryNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Radimation PDFDokument398 SeitenRadimation PDFMehadi Alom ChoudhuryNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Transmission Line Basics II - Class 6: Prerequisite Reading Assignment: CH2Dokument49 SeitenTransmission Line Basics II - Class 6: Prerequisite Reading Assignment: CH2Mehadi Alom ChoudhuryNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Systems Analysis and Control: Matthew M. PeetDokument25 SeitenSystems Analysis and Control: Matthew M. PeetMehadi Alom ChoudhuryNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- LinesADokument89 SeitenLinesAMehadi Alom ChoudhuryNoch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Electronics Tutorial About FiltersDokument53 SeitenElectronics Tutorial About FiltersMehadi Alom ChoudhuryNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Mohd Azizul Ghafur Bin RahimiDokument24 SeitenMohd Azizul Ghafur Bin RahimiMehadi Alom ChoudhuryNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Toshiba Satellite L200 M200 M203 M206 KBTIDokument59 SeitenToshiba Satellite L200 M200 M203 M206 KBTIYakub LismaNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Service Manual: (E65 MOST-BUS CDC (F/L) )Dokument29 SeitenService Manual: (E65 MOST-BUS CDC (F/L) )Matt MichiganNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Installation Manual: Cardax N32RDokument12 SeitenInstallation Manual: Cardax N32RCristian GurbetNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The HD58X Jubilee Is Available Through OnlyDokument20 SeitenThe HD58X Jubilee Is Available Through Only전유신Noch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- JMUX Reference Manual Issue 4.0Dokument99 SeitenJMUX Reference Manual Issue 4.0gradeli100% (2)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- MC InstallGuide PDFDokument56 SeitenMC InstallGuide PDFrqodriNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- 8251 USART (Programmable Communication Interface)Dokument10 Seiten8251 USART (Programmable Communication Interface)Syed Siddique MridulNoch keine Bewertungen

- gx5500s MoDokument100 Seitengx5500s MoHenry AlvaxNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Motor InterfacingDokument3 SeitenMotor InterfacingMemoh BranleyNoch keine Bewertungen

- KINETROL Rotary ActuatorDokument56 SeitenKINETROL Rotary ActuatorJoseNoch keine Bewertungen

- Guard Phone For Apartment Unit: WarrantyDokument6 SeitenGuard Phone For Apartment Unit: Warrantylokuras de la vidaNoch keine Bewertungen

- Sabouni AdaptivecoverageforfutureltenetworksDokument158 SeitenSabouni AdaptivecoverageforfutureltenetworksWided AhmadiNoch keine Bewertungen

- Neo900 Block DiagramDokument1 SeiteNeo900 Block Diagramjornada660Noch keine Bewertungen

- Westinghouse Lighting Rampliter III HID Airport Floodlight System Spec Sheet 8-72Dokument2 SeitenWestinghouse Lighting Rampliter III HID Airport Floodlight System Spec Sheet 8-72Alan MastersNoch keine Bewertungen

- Course "EEM 42 Three-Phase Asynchronous Machines: Dahlander Motors"Dokument38 SeitenCourse "EEM 42 Three-Phase Asynchronous Machines: Dahlander Motors"Daus VillaNoch keine Bewertungen

- SCH MainDokument2 SeitenSCH MainDjrichardMixNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Orange CR20L Manual V16Dokument13 SeitenOrange CR20L Manual V16Jesus ContrerasNoch keine Bewertungen

- Power Quality: Case StudyDokument6 SeitenPower Quality: Case StudymarinflorentinaoanaNoch keine Bewertungen

- 2SD863Dokument5 Seiten2SD863FeryBaleaNoch keine Bewertungen

- Work Sheet DC MotorDokument10 SeitenWork Sheet DC MotoridealparrotNoch keine Bewertungen

- ELBI General CatalogDokument68 SeitenELBI General CatalogTapelea CristianNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Powerflex 523 Adjustable Frequency Ac Drive: Product InformationDokument2 SeitenPowerflex 523 Adjustable Frequency Ac Drive: Product Informationelecrical gresikNoch keine Bewertungen

- DSE M643 Data SheetDokument7 SeitenDSE M643 Data SheetY.EbadiNoch keine Bewertungen

- Relays PresentationDokument32 SeitenRelays PresentationbijoyNoch keine Bewertungen

- 2N3715Dokument7 Seiten2N3715Perica RakićNoch keine Bewertungen

- ECE2280 Homework #1 Fall 2011: Use: Ignore R - V - 0.7, V 20+0.001sin (20t) I VXDokument11 SeitenECE2280 Homework #1 Fall 2011: Use: Ignore R - V - 0.7, V 20+0.001sin (20t) I VXXxx CccNoch keine Bewertungen

- Enc Inverter: Shenzhen Encom Electric Technologies Co., LTDDokument16 SeitenEnc Inverter: Shenzhen Encom Electric Technologies Co., LTDMr CdtNoch keine Bewertungen

- 14 - 6060 - Electrical Drawings - CATDokument32 Seiten14 - 6060 - Electrical Drawings - CAThectorNoch keine Bewertungen

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Essay For BluetoothDokument3 SeitenEssay For BluetoothVenkatesh SNoch keine Bewertungen

- FNA Edge Network Appliance: Operations GuideDokument22 SeitenFNA Edge Network Appliance: Operations GuideYosvensa SetiawanNoch keine Bewertungen