Beruflich Dokumente

Kultur Dokumente

13 Jpe 10073

Hochgeladen von

ankit407Originalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

13 Jpe 10073

Hochgeladen von

ankit407Copyright:

Verfügbare Formate

428

Journal of Power Electronics, Vol. 10, No. 4, July 2010

JPE 10-4-13

Reduction of Input Current Harmonics for Three Phase PWM Converter Systems under a Distorted Utility Voltage

Nae-Chun Park , Hyung-Soo Mok , and Sang-Hoon Kim

Dept.

of Electrical and Electronics Eng., Kangwon National University, Chuncheon, Korea Dept. of Electrical Eng., Konkuk University, Seoul, Korea

Abstract This paper proposes a harmonics reduction technique for the input currents of three phase PWM converters. The quality of the phase angle information on the utility voltage connected to the PWM converters affects their control performance. Under a distorted utility voltage, the extracted phase angle based on the synchronous reference frame PLL method is distorted. This causes large harmonics in the input currents of a PWM converter. In this paper, a harmonics reduction method that makes the input currents in the PWM converter sinusoidal even under distorted utility conditions is proposed. By the proposed method, without additional hardware, the THD (Total Harmonic Distortion) of the input currents can be readily limited to below 5% which is the harmonic current requirements of IEEE std. 519. Its validity is veried by simulations and experimental results. Key Words: Distorted utility voltage, Harmonics reduction method, PLL, PWM converter

I. I NTRODUCTION Phase angle information on utility voltage is essential to the operation of ac to dc conversion systems that are coupled with utility lines such as PWM converters and active power lters. This information has to be accurate because the control performance of the conversion systems such as power factor correction, active or reactive power control, and harmonic current compensation are highly dependent on its quality. The angle information is typically obtained by one of the forms of a phase locked loop (PLL)[1]. Among the different forms, the synchronous d, q reference frame PLL system is used the most because it is simple and works well under an ideal utility condition. Recently, a growing part of the load is fed through power electronic equipment drawing a non-sinusoidal current. This results in undesirable harmonics in the utility voltage, whereby the voltage becomes a non-sinusoidal waveform containing distortions. Under such distorted utility conditions, the extracted phase angle based on the synchronous reference frame PLL also contains harmonics. This distorted phase angle causes harmonics in the current references for the control of a PWM converter. As a result, the real input currents in the PWM converter will become non-sinusoidal waveforms

Manuscript received Apr. 16, 2010; revised Jun. 3, 2010 Corresponding Author: kshoon@kangwon.ac.kr Tel: +82-33-250-6293, Fax: +82 -33-241-3775, Kangwon National Univ. Dept. of Electrical and Electronics Eng., Kangwon National University, Korea Dept. of Electrical Eng., Konkuk University, Korea

containing harmonics. A few PLL systems that take into consideration distorted utility voltage conditions have been studied. These studies focused mainly on obtaining non-distorted phase angles. In order to do this, a low-pass lter (LPF) was used in a synchronous reference frame PLL system[1],[2]. Therefore, these methods have a disadvantage in that the bandwidth of their control system is limited to the cut-off frequency of the LPF. When operating PWM converters under distorted utility voltage conditions, the fundamental problem is the distortion of the real input currents as a result of this distortion rather than the phase angle itself. Therefore, this paper proposes a harmonics reduction method which makes the input currents in a PWM converter almost sinusoidal even under a distorted utility voltage. The proposed method extracts the distorted component from the detected phase angle by a synchronous reference frame PLL system under a distorted utility voltage, and then corrects the d- and q- axis current references to obtain sinusoidal real input currents. Through simulations and experiments, it has been conrmed that the proposed method can readily limit the THD of input currents to below 5%, which is the harmonic current requirement of IEEE Std. 519, even under a source voltage with 12.6% THD. II. SYNCHRONOUS REFERENCE FRAME PLL METHOD The synchronous d, q reference frame PLL system works in a rotating frame of reference synchronized to the utility

Reduction of Input Current Harmonics for Three Phase PWM Converter Systems under

429

Fig. 1.

Control diagram of synchronous reference frame PLL system.

Fig. 3.

Input currents in case of using the distorted phase angle.

e references ie d , iq in the synchronous frame are transformed s into the current references is d , iq in the stationary frame as following

(a) Distorted utility voltages.

is cos d s = iq sin

sin cos

ie d e iq ie d ie q

cos( + ) sin( + ) sin( + ) cos( + )

(1)

(b) Phase angle. Fig. 2. Phase angle in case of distorted utility voltage.

where, is the error between the undistorted utility angle and the PLL output (= + ). When a synchronous frame current regulator is used, the e reference currents ie are given as dc currents in the d , iq e steady state. If these current references ie d , iq are transformed s s into the references id , iq in the stationary frame using the undistorted phase angle under ideal utility conditions, they will become pure sine waves without any distortion. In contrast, if e ie d , iq are transformed using a distorted phase angle, they will not become sinusoidal but will contain distortions. Therefore, the input currents will inevitably be distorted as shown in Fig. 3. III. HARMONICS REDUCTION TECHNIQUE OF INPUT CURRENTS To avoid distortion of the stationary frame current references due to a distorted phase angle, this paper proposes a current references correction method. In the proposed method, the current references in the synchronous frame are corrected so that the currents in the stationary frame can be sinusoidal even if they are transformed by a distorted phase angle. If the phase angle is not distorted, the stationary reference s frame current references is d , iq become sinusoidal and are given by:

is cos d s = iq sin

voltage frequency to detect the phase angle. In the synchronous reference frame, the d and q axis voltages appear as a dc quantity. Thus, the phase angle can be easily obtained by regulating the d-axis voltage ee d to zero using a PI regulator as shown in Fig. 1. If the utility voltage has harmonics, the phase angle which is the output of the synchronous reference frame PLL will include similar harmonics. Fig. 2 shows that the utility voltage distortion produces a distortion on the phase angle extracted by the synchronous reference frame PLL system. Such a distortion of the phase angle may deteriorate the control performance for systems. The distortion components in the phase angle bring about undesirable harmonics in the d and q axis current references for a PWM converter. As a result, the real input currents will not be sinusoidal. These distorted components can be eliminated by using a LPF with a low cutoff-frequency on the voltages[2]. However, using a LPF reduces the bandwidth to make the dynamic response of the PLL system sluggish. To review the impact of the distorted phase angle on the waveforms of the input currents, the d and q axis current

sin cos

ie d e . iq

(2)

However, in the case of a distorted phase angle, these references may include distortion components as shown in (1). e The new corrected synchronous current references ie d , iq can be found by solving (3) so that the stationary currents become sinusoidal currents as in (2) even if they are transformed by a distorted phase angle.

430

Journal of Power Electronics, Vol. 10, No. 4, July 2010

is cos( + ) sin( + ) d s = iq sin( + ) cos( + )

ie d e iq

cos sin

sin cos

ie d e . iq

(3)

e By using the original current references ie d , iq and the distortion components of the phase angle, the corrected current e can be obtained by (4). references ie d , iq ie cos( + ) sin( + ) d e = iq sin( + ) cos( + ) 1 is d s iq

cos( + ) = sin( + ) = = cos( + ) sin( + ) cos sin

sin( + ) cos( + ) sin( + ) cos( + )

ie d . ie q

is d s iq

Fig. 4.

Phase angle of Synchronous frame PLL using LPF.

cos sin

sin cos

ie d e iq

sin cos

(4)

The distortion components sin and cos necessary for calculating (4) can be obtained by (5). [R()] = cos( + ) cos sin = sin( + ) sin cos cos( + ) sin( + )

cos cos( + ) + sin sin( + ) sin cos( + ) + cos sin( + )

Fig. 5. Dynamic response characteristics of two PLLs.

cos = . sin

(5)

To extract such distortion components, the phase angles and + should be known. In order to get these, two synchronous reference frame PLL systems are used in the proposed method. One is for the phase angle + with distortion components and the other is for the phase angle without distortion components. When obtaining the phase angle , a LPF with a low cut-off frequency is used in the synchronous reference frame PLL system. However, in the proposed system, this phase angle is not used to control the system due to its low bandwidth, but to obtain the distortion components sin and cos . The simulation results in Fig. 4 and 5 show that even if an undistorted utility angle can be obtained using a LPF with a low cut-off frequency like 5 Hz, the dynamic response becomes sluggish. Therefore, the phase angle is not used for system control, but exclusively for extracting the distortion components. It is the phase angle + that is used to control the system. Fig. 6 shows a block diagram of the proposed current correction method. The whole system consists of a current corrector and two PLL systems to detect the phase angles + and . Details for the current corrector are shown in Fig 7. Fig. 8 shows the current references before and after the correction. The output currents of a synchronous frame current e regulator, ie d and iq are naturally pure DC values as shown in Fig. 8(a). However, after the correction for obtaining the sinusoidal real input currents, the references become DC currents containing ripple components as shown in Fig. 8(b).

Fig. 6.

Block diagram of proposed method.

Fig. 7.

Detail diagram of current corrector.

IV. SIMULATION RESULTS To show the usefulness of the proposed method which eliminates the distortion of input currents, simulations were executed for a 3kW PWM converter system. Utility ac voltage of 120V (phase, rms) has 10% and 7% of 5th and 7th harmonics respectively, resulting in a 12.6% THD. The interface

Reduction of Input Current Harmonics for Three Phase PWM Converter Systems under

431

(a) Before correction.

(a) Synchronous frame PLL.

(b) After correction. Fig. 8. Current references in the synchronous frame. (b) Synchronous frame PLL using LPF.

inductance at the input terminal is 0.8 mH and the DC link capacitor is 2700 uF. The DC link voltage is regulated at 250V with a load resistance of 30. Simulations were performed with three methods of synchronous reference frame PLL: the synchronous reference frame PLL method, the synchronous reference frame PLL method using a LPF with a 5 Hz cut-off frequency and the proposed method. The simulation results in Fig. 9 show a-phase voltage and input current in the PWM converter. When using the synchronous reference frame PLL method shown in Fig. 9(a), the harmonic components and the THD of the input current are almost the same as those of utility voltage. In this case, the THD of the current is 10.9%. In the case of the synchronous reference frame PLL method with a LPF shown in Fig. 9(b), the current has a 10.6% THD. Although the distortion of the phase angle can be eliminated by using a LPF, it can be seen that the THD is not improved. From the simulation results in Fig. 9(a) and 9(b), it can be concluded that in the two cases above, the harmonics of the input current can be directly inuenced by the distortion of the utility voltage. In the case of a synchronous reference frame PLL with the proposed correction method, even though the phase angle is distorted, the THD of the currents is reduced to 3.2% as shown in Fig. 9(c).

(c) Proposed method. Fig. 9. A-phase voltage and input current in PWM rectier.

V. EXPERIMENT RESULTS To verify the validity of the proposed method, experiments were executed on a PWM IGBT converter system with a digital controller based on a TMS320VC33 DSP as shown in Fig. 10. The switching frequency is 10kHz and the control time interval of the PLL system is 50us. The experiments for the conventional and proposed methods were performed under the same conditions as the simulations. However, the input inductance was changed from 0.5 to 3.12mH in order to investigate its effect on the current THD.

432

Journal of Power Electronics, Vol. 10, No. 4, July 2010

Fig. 10.

Conguration of experimental sets. (a) Synchronous frame PLL (THD=11.8[%]).

Fig. 11 shows the phase voltage, the phase current and the THD for the three methods in the case of using a 0.8mH input inductance. It is conrmed that experiment results similar to the simulation results can be obtained. Fig. 12 shows a comparison of the phase current THD using the three methods for several input inductances. It is natural that the more the input inductance increases, the more the THD reduces. In the case of the synchronous reference frame PLL method with a LPF, it can be seen that the interface inductance has a larger impact on the current THD than the other methods. It is clear that the proposed method needs a smaller inductance than the other methods to meet the THD requirements of the current: below 5% according to IEEE Std. 519. If the synchronous reference frame PLL method with a LPF has a large inductance, such as 3.12mH, a lower current THD can be achieved than with the proposed method. However, slow dynamics in this PLL system are inevitable due to the LPF with a low bandwidth. VI. CONCLUSIONS This paper proposed a new current harmonic reduction method which enables the input currents in PWM converters to be almost sinusoidal even under distorted utility conditions. The proposed method, based on a synchronous reference frame PLL, does not deteriorate the system dynamics as the PLL method with a LPF does. Through simulations and experiments, it was veried that under a utility ac voltage with a 12.6% THD, the THD of the input currents of the proposed method can be readily limited below the 5% harmonic current requirements of IEEE std. 519. The proposed method is useful in ac to dc conversion systems connected to an ac utility line, such as a PWM converter and an active power lter, because the proposed algorithm can be simply implemented by software and requires a smaller interface inductance than the other PLL methods to achieve the same harmonic requirements. ACKNOWLEDGMENT This work is the outcome of a Manpower Development Program for Energy & Resources supported by the Ministry of Knowledge and Economy (MKE).

(b) Synchronous frame PLL using LPF (THD=9.5[%]).

(c) Proposed method (THD=3.4[%]). Fig. 11. A-phase voltage and current at input inductance 0.8mH.

Reduction of Input Current Harmonics for Three Phase PWM Converter Systems under

433

[6] J. W. Dixon and B. T. Ooi, Indirect current control of a unity power factor sinusoidal boost type 3-phase rectier, IEEE Trans. on Ind. Elec., Vol. 35, pp. 508-515, Nov. 1988. [7] Neam, Mahmoud M., El-Sousy, Fayez F. M., Ghazy, Moharned A., Abo-Adma, and Maqed A., Intelligent control for DC-bus voltage of three-phase AC/DC PWM converters, Power Engineering, Energy and Electrical Drives, Powereng 2007 International Conference, pp.444-449, 2007. Nae-Chun Park was born in Wonju, Korea, in 1982. He received his B.S. and M.S. in Electrical and Electronics Engineering from Kangwon National University, Chuncheon, Korea, in 2006 and 2008, respectively. He is currently working toward his Ph.D. at Kangwon National University. His current research interests include high-performance electric machine drives and PWM converters. Fig. 12. Phase current THD as a function of a input inductance. Hyung-Soo Mok received his B.S., M.S., and Ph.D. in Electrical Engineering from Seoul National University, Korea, in 1986, 1988, and 1992, respectively. He was with the Department of Control and Instrumentation Engineering at the Seoul National Polytechnic University from 1993 to 1997. Since 1997, he has been with the Department of Electrical Engineering at Konkuk University. His current teaching and research interests include electric machines, electric machine drive systems, and power electronic control for industrial and power systems. Sang-Hoon Kim received his B.S., M.S., and Ph.D. in Electrical Engineering from Seoul National University, Seoul, Korea, in 1987, 1989, and 1994, respectively. From 1994 to 1996, he was with Daewoo Heavy Industries Ltd., Korea, where he was involved in the development of propulsion systems for rolling stock. Since 1997, he has been with the Department of Electrical and Electronics Engineering, Kangwon National University, Chuncheon, Korea. His current research interests include high-performance electric machine drives and PWM converters.

R EFERENCES

[1] Vikaram Kaura and Vladimir Blasko, Operation of a phase locked loop system under distorted utility conditions, IEEE Trans. on Ind. App., Vol. 33, No.1 pp. 58-63, 1997. [2] Sang-Joon Lee, Jun-Koo Kang, and Seung-Ki Sul, A new phase detecting method for power conversion systems considering distorted conditions in power system, in Conf. Rec. IEEE- IAS Annu. Meeting, Vol. 4, pp. 21672171, 1999. [3] H. S. Song and K. Nam, Dual current controller PWM converter under unbalanced input voltage conditions, IEEE Trans. on Ind. Elec., Vol. 46, No.5, pp. 953-959, 1999. [4] Takaharu Takeshita and Nobuyuki Mastsui, Current waveform control of PWM converter system for harmonic suppression on distribution system, IEEE Trans. on Ind. Elec., Vol. 50, No. 6, pp. 1134-1139, Dec. 2003. [5] H.S. Mok, S.H. Kim, and Y.H. Cho, Reduction of PMSM torque ripple caused by resolver position error, IEE Electron Letters, Vol. 43, No. 11, pp. 646-647, May 2007.

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Jeep WJ 2004 Grand Cherokee MOPAR Parts CatalogDokument432 SeitenJeep WJ 2004 Grand Cherokee MOPAR Parts CatalogravenpisuergaNoch keine Bewertungen

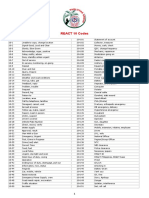

- React 10 Codes PDFDokument2 SeitenReact 10 Codes PDFPaul Anselmo Dela Cruz100% (3)

- Giuliani Etude TabDokument1 SeiteGiuliani Etude TabjohnmeryNoch keine Bewertungen

- EXample of GADokument20 SeitenEXample of GAankit407Noch keine Bewertungen

- 8 Mission MappingDokument21 Seiten8 Mission Mappingankit407Noch keine Bewertungen

- 06jpf06de13 PDFDokument50 Seiten06jpf06de13 PDFviji_pondicherryNoch keine Bewertungen

- 1 Hybrid Evolutionary Algorithms: Methodologies, Architectures, and ReviewsDokument17 Seiten1 Hybrid Evolutionary Algorithms: Methodologies, Architectures, and Reviewsankit407Noch keine Bewertungen

- Stepper Motor OperationDokument6 SeitenStepper Motor OperationPavan KumarNoch keine Bewertungen

- Automated Diagnosis and ImageDokument4 SeitenAutomated Diagnosis and Imageankit407Noch keine Bewertungen

- Ann ChapterDokument8 SeitenAnn ChapterkpanklibNoch keine Bewertungen

- 14 Examples of Evolutionary AlgorithmsDokument23 Seiten14 Examples of Evolutionary AlgorithmsA. S.Noch keine Bewertungen

- GADokument30 SeitenGAankit407Noch keine Bewertungen

- Image Processing ApplicationsDokument27 SeitenImage Processing ApplicationsAbhinand AniganiNoch keine Bewertungen

- 10 Chapter1Dokument23 Seiten10 Chapter1ankit407Noch keine Bewertungen

- Iterated Graph Cuts For Image SegmentationDokument10 SeitenIterated Graph Cuts For Image Segmentationankit407Noch keine Bewertungen

- Chapter-3 Soft Computing TechniquesDokument18 SeitenChapter-3 Soft Computing TechniquesYashi CNoch keine Bewertungen

- FP5003 V06-LF1Dokument21 SeitenFP5003 V06-LF1ankit407Noch keine Bewertungen

- Digital Image Acquisition and Processing in Medical X-Ray ImagingDokument18 SeitenDigital Image Acquisition and Processing in Medical X-Ray Imagingankit407Noch keine Bewertungen

- CPR T 120002010Dokument8 SeitenCPR T 120002010ankit407Noch keine Bewertungen

- AIKED32Dokument4 SeitenAIKED32ankit_elect27Noch keine Bewertungen

- Lundmark Sonja PHDDokument123 SeitenLundmark Sonja PHDZahra ShiraviNoch keine Bewertungen

- Simple Fuzzy PID Controllers For DC-DC Converters: K.-W. Seo and Han Ho ChoiDokument6 SeitenSimple Fuzzy PID Controllers For DC-DC Converters: K.-W. Seo and Han Ho Choiankit407Noch keine Bewertungen

- DC-DC Converter Control Using Fuzzy LogicDokument6 SeitenDC-DC Converter Control Using Fuzzy Logicankit407Noch keine Bewertungen

- Design PID Controller PLCDokument8 SeitenDesign PID Controller PLCankit407Noch keine Bewertungen

- Digital Image Acquisition and Processing in Medical X-Ray ImagingDokument18 SeitenDigital Image Acquisition and Processing in Medical X-Ray Imagingankit407Noch keine Bewertungen

- Topic: Choppers: Class: 5 Sem. (EE)Dokument89 SeitenTopic: Choppers: Class: 5 Sem. (EE)ankit407Noch keine Bewertungen

- PMDC Motor Chopper Control by MATLABDokument10 SeitenPMDC Motor Chopper Control by MATLABAllwayLLGNoch keine Bewertungen

- A Current-Source Active Power Filter With A New DC Filter StructureDokument8 SeitenA Current-Source Active Power Filter With A New DC Filter Structureankit407Noch keine Bewertungen

- Design PID Controller PLCDokument8 SeitenDesign PID Controller PLCankit407Noch keine Bewertungen

- A Current-Source Active Power Filter With A New DC Filter StructureDokument8 SeitenA Current-Source Active Power Filter With A New DC Filter Structureankit407Noch keine Bewertungen

- 021Dokument6 Seiten021ankit407Noch keine Bewertungen

- 32i7 Ijaet0703745 Harmonic Reduction in CascadedDokument11 Seiten32i7 Ijaet0703745 Harmonic Reduction in Cascadedsyed24mayNoch keine Bewertungen

- 37 ADokument11 Seiten37 Amlaura2Noch keine Bewertungen

- Cts 9009plusDokument6 SeitenCts 9009plusNila AkterNoch keine Bewertungen

- ILS Critical AreaDokument6 SeitenILS Critical AreamateivictorNoch keine Bewertungen

- Memory and Tonality in Debussy's Prelude À L'après-Midi D'un Faune /cahiers DebussyDokument17 SeitenMemory and Tonality in Debussy's Prelude À L'après-Midi D'un Faune /cahiers Debussymahler2010100% (1)

- CertsDokument8 SeitenCertsJomar Mapue PormentoNoch keine Bewertungen

- Vixen by Jillian LarkinDokument19 SeitenVixen by Jillian LarkinRandom House Teens0% (1)

- ProLaser III Users Manual 2006-05-08 PDFDokument47 SeitenProLaser III Users Manual 2006-05-08 PDFPeter Shearer100% (1)

- Dance of The Sugar Plum FairyDokument3 SeitenDance of The Sugar Plum FairyAngelica Portia Forbes Regencia100% (1)

- Cyrille Aimée & The Surreal Band - A Dream Is A Wish (In Eb)Dokument4 SeitenCyrille Aimée & The Surreal Band - A Dream Is A Wish (In Eb)zeuta1Noch keine Bewertungen

- Interfacing GPS With Graphic LCD Using 8051 MicrocontrollerDokument49 SeitenInterfacing GPS With Graphic LCD Using 8051 MicrocontrollerManoj KavediaNoch keine Bewertungen

- (Clarinet - Institute) Klose - Complete Method For The Clarinet PDFDokument194 Seiten(Clarinet - Institute) Klose - Complete Method For The Clarinet PDFAndres Jimenez Garcia100% (1)

- Masters Music Theory and Composition With ScoringDokument1 SeiteMasters Music Theory and Composition With ScoringSebastián MoralesNoch keine Bewertungen

- Mobile Number PortabilityDokument19 SeitenMobile Number PortabilityAkshay MeenaNoch keine Bewertungen

- Academy Travel Tour Program January To December 2020Dokument100 SeitenAcademy Travel Tour Program January To December 2020dieschnelleNoch keine Bewertungen

- Vinitsky Estudio in A Blues Form GPDokument2 SeitenVinitsky Estudio in A Blues Form GPLUIS ALVAREZ RODRIGUEZ100% (1)

- Euphoria 106 The Next Episode 2019Dokument67 SeitenEuphoria 106 The Next Episode 2019Ahmed SamehNoch keine Bewertungen

- Using Mis 5th Edition Kroenke Solutions ManuaDwnload Full Using Mis 5th Edition Kroenke Solutions Manual PDFDokument35 SeitenUsing Mis 5th Edition Kroenke Solutions ManuaDwnload Full Using Mis 5th Edition Kroenke Solutions Manual PDFmicrondeafen.4dw0p100% (9)

- Artistry, Creativity, and Inquiry (LHUM-100-2F)Dokument2 SeitenArtistry, Creativity, and Inquiry (LHUM-100-2F)Calvin Yehezkiel LimuelNoch keine Bewertungen

- LTE PRACH Preamble FormatDokument12 SeitenLTE PRACH Preamble FormatBiswajit MohantyNoch keine Bewertungen

- Two Basic Types of Scale in Japanese MusicDokument10 SeitenTwo Basic Types of Scale in Japanese MusicAlita Leal Leguro-Delos SantosNoch keine Bewertungen

- Radio Frequency Identification (RFID) Opportunities For Mobile Telecommunication ServicesDokument18 SeitenRadio Frequency Identification (RFID) Opportunities For Mobile Telecommunication ServicesAmit NaikNoch keine Bewertungen

- LR Phono PreampsDokument44 SeitenLR Phono PreampsMartin FernandezNoch keine Bewertungen

- Cello gut string guideDokument1 SeiteCello gut string guideDominic BertucciNoch keine Bewertungen

- A Former WaiterDokument6 SeitenA Former WaiterfildogecryptoNoch keine Bewertungen

- Xd1 G e Generator Differential Protection RelayDokument20 SeitenXd1 G e Generator Differential Protection RelayRaj KrishNoch keine Bewertungen

- Can Drums Be Used at MassDokument5 SeitenCan Drums Be Used at Masstodos_esperanNoch keine Bewertungen

- Grade - 8 - Maths - Worksheet - Term 3Dokument50 SeitenGrade - 8 - Maths - Worksheet - Term 3dheeraj yadavNoch keine Bewertungen

- Ancient dance history and benefits of movementDokument3 SeitenAncient dance history and benefits of movementKrystal JungNoch keine Bewertungen