Beruflich Dokumente

Kultur Dokumente

MM74HC14 Hex Inverting Schmitt Trigger: Features General Description

Hochgeladen von

d_richard_dOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

MM74HC14 Hex Inverting Schmitt Trigger: Features General Description

Hochgeladen von

d_richard_dCopyright:

Verfügbare Formate

MM74HC14 Hex Inverting Schmitt Trigger

February 2008

MM74HC14 Hex Inverting Schmitt Trigger

Features

Typical propagation delay: 13ns Wide power supply range: 2V6V Low quiescent current: 20A maximum (74HC Series) Low input current: 1A maximum Fanout of 10 LS-TTL loads Typical hysteresis voltage: 0.9V at VCC = 4.5V

General Description

The MM74HC14 utilizes advanced silicon-gate CMOS technology to achieve the low power dissipation and high noise immunity of standard CMOS, as well as the capability to drive 10 LS-TTL loads. The 74HC logic family is functionally and pinout compatible with the standard 74LS logic family. All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.

Ordering Information

Order Number

MM74HC14M MM74HC14SJ MM74HC14MTC MM74HC14N

Package Number

M14A M14D MTC14 N14A

Package Description

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Device also available in Tape and Reel. Specify by appending suffix letter X to the ordering number. All packages are lead free per JEDEC: J-STD-020B standard.

Connection Diagram

Pin Assignments for DIP, SOIC, SOP and TSSOP

Logic Diagram

Top View

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com

MM74HC14 Hex Inverting Schmitt Trigger

Absolute Maximum Ratings(1)

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

Symbol

VCC VIN VOUT IIK, IOK IOUT ICC TSTG PD Supply Voltage DC Input Voltage DC Output Voltage Clamp Diode Current DC Output Current, per pin

Parameter

Rating

0.5 to +7.0V 1.5 to VCC+1.5V 0.5 to VCC+0.5V 20mA 25mA 50mA 65C to +150C 600mW 500mW 260C

DC VCC or GND Current, per pin Storage Temperature Range Power Dissipation Note 2 S.O. Package only Lead Temperature (Soldering 10 seconds)

TL

Notes: 1. Unless otherwise specified all voltages are referenced to ground. 2. Power Dissipation temperature derating plastic N package: 12mW/C from 65C to 85C.

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

Symbol

VCC VIN, VOUT TA Supply Voltage DC Input or Output Voltage

Parameter

Min.

2 0 55

Max.

6 VCC +125

Units

V V C

Operating Temperature Range

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 2

MM74HC14 Hex Inverting Schmitt Trigger

DC Electrical Characteristics(3)

TA = 25C Symbol

VT+

TA = 40C to 85C

1.0 2.0 3.0 1.5 3.15 4.2 0.3 0.9 1.2 1.0 2.2 3.0 0.2 0.4 0.5 1.0 1.4 1.5 1.9 4.4 5.9 3.84 5.34 0.1 0.1 0.1 0.33 0.33 1.0 20

TA = 55C to 125C Units

V 1.0 2.0 3.0 1.5 3.15 4.2 0.3 0.9 1.2 1.0 2.2 3.0 0.2 0.4 0.5 1.0 1.4 1.5 1.9 4.4 5.9 3.7 5.2 0.1 0.1 0.1 0.4 0.4 1.0 40 A A V V V V

Parameter

Positive Going Threshold Voltage

VCC (V)

2.0 4.5 6.0 2.0 4.5 6.0

Conditions

Minimum

Typ.

1.2 2.7 3.2 1.0 2.0 3.0 1.5 3.15 4.2 0.3 0.9 1.2 1.0 2.2 3.0 0.2 0.4 0.5 1.0 1.4 1.5 1.9 4.4 5.9 3.98 5.48 0.1 0.1 0.1 0.26 0.26 0.1 2.0

Guaranteed Limits

Maximum

1.2 2.7 3.2

VT

Negative Going Threshold Voltage

2.0 4.5 6.0 2.0 4.5 6.0

Minimum

0.7 1.8 2.2

Maximum

0.7 1.8 2.2

VH

Hysteresis Voltage

2.0 4.5 6.0 2.0 4.5 6.0

Minimum

0.5 0.9 1.0

Maximum

0.5 0.9 1.0

VOH

Minimum HIGH Level Output Voltage

2.0 4.5 6.0 4.5 6.0

VIN = VIL, |IOUT| = 20A VIN = VIL, |IOUT| = 4.0mA VIN = VIL, |IOUT| = 5.2mA VIN = VIH, |IOUT| = 20A VIN = VIH, |IOUT| = 4.0mA VIN = VIH, |IOUT| = 5.2mA VIN = VCC or GND VIN = VCC or GND, IOUT = 0A

2.0 4.5 6.0 4.2 5.7 0 0 0 0.2 0.2

VOL

Maximum LOW Level Output Voltage

2.0 4.5 6.0 4.5 6.0

IIN ICC

Maximum Input Current Maximum Quiescent Supply Current

6.0 6.0

Note: 3. For a power supply of 5V 10% the worst case output voltages (VOH, and VOL) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case VIH and VIL occur at VCC = 5.5V and 4.5V respectively. (The VIH value at 5.5V is 3.85V.) The worst case leakage current (IIN, ICC, and IOZ) occur for CMOS at the higher voltage and so the 6.0V values should be used.

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0 www.fairchildsemi.com 3

MM74HC14 Hex Inverting Schmitt Trigger

AC Electrical Characteristics

VCC = 5V, TA = 25C, CL = 15pF, tr = tf = 6ns

Symbol

tPHL, tPLH

Parameter

Maximum Propagation Delay

Conditions

Typ.

12

Guaranteed Limit

22

Units

ns

AC Electrical Characteristics

VCC = 2.0V to 6.0V, CL = 50pF, tr = tf = 6ns (unless otherwise specified)

TA = 25C Symbol

tPHL, tPLH

TA = 40C to 85C

156 31 26 95 19 16

TA = 55C to 125C Units

ns 188 38 32 110 22 19 pF ns

Parameter

Maximum Propagation Delay

VCC (V)

2.0 4.5 6.0 2.0 4.5 6.0

Conditions

Typ.

60 13 11 30 8 7 125 25 21 75 15 13

Guaranteed Limits

tTLH, tTHL

Maximum Output Rise and Fall Time

CPD CIN

Power Dissipation Capacitance(4) Maximum Input Capacitance

(per gate)

27 5 10 10 10

pF

Note: 4. CPD determines the no load dynamic power consumption, PD = CPD VCC2 f + ICC VCC, and the no load dynamic current consumption, IS = CPD VCC f + ICC .

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 4

MM74HC14 Hex Inverting Schmitt Trigger

Typical Performance Characteristics

Input Threshold, VT+, VT, vs Power Supply Voltage Propagation Delay vs. Power Supply

Typical Applications

Low Power Oscillator

Note: The equations assume t1+ t2 >> tpd0 + tpd1

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 5

MM74HC14 Hex Inverting Schmitt Trigger

Physical Dimensions

8.75 8.50 7.62

14 8 B A

0.65

5.60 6.00 4.00 3.80 1.70

C B A

PIN ONE INDICATOR

1.27 (0.33)

0.51 0.35

0.25

M

1.27

LAND PATTERN RECOMMENDATION

1.75 MAX 1.50 1.25

SEE DETAIL A

0.25 0.10

C 0.10 C NOTES: UNLESS OTHERWISE SPECIFIED

0.25 0.19

R0.10 R0.10

8 0

0.50 X 45 0.25

A) THIS PACKAGE CONFORMS TO JEDEC MS-012, VARIATION AB, ISSUE C, B) ALL DIMENSIONS ARE IN MILLIMETERS. C) DIMENSIONS DO NOT INCLUDE MOLD GAGE PLANE FLASH OR BURRS. D) LANDPATTERN STANDARD: SOIC127P600X145-14M 0.36 E) DRAWING CONFORMS TO ASME Y14.5M-1994 F) DRAWING FILE NAME: M14AREV13

0.90 0.50 (1.04)

DETAIL A

SCALE: 20:1

SEATING PLANE

Figure 1. 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions, specically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductors online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 6

MM74HC14 Hex Inverting Schmitt Trigger

Physical Dimensions (Continued)

Figure 2. 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions, specically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductors online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 7

MM74HC14 Hex Inverting Schmitt Trigger

Physical Dimensions (Continued)

0.43 TYP

0.65

1.65

0.45

6.10

12.00 TOP R0.09 min

& BOTTOM

A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION AB, REF NOTE 6 B. DIMENSIONS ARE IN MILLIMETERS C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS D. DIMENSIONING AND TOLERANCES PER ANSI Y14.5M, 1982 E. LANDPATTERN STANDARD: SOP65P640X110-14M F. DRAWING FILE NAME: MTC14REV6

1.00

R0.09min

Figure 3. 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions, specically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductors online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 8

MM74HC14 Hex Inverting Schmitt Trigger

Physical Dimensions (Continued)

19.56 18.80

14

8 6.60 6.09

(1.74) 3.56 3.30

1.77 1.14 5.33 MAX 0.38 MIN

8.12 7.62 0.35 0.20

3.81 3.17

0.58 0.35

2.54

8.82

NOTES: UNLESS OTHERWISE SPECIFIED THIS PACKAGE CONFORMS TO A) JEDEC MS-001 VARIATION BA B) ALL DIMENSIONS ARE IN MILLIMETERS. DIMENSIONS ARE EXCLUSIVE OF BURRS, C) MOLD FLASH, AND TIE BAR EXTRUSIONS. D) DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994 E) DRAWING FILE NAME: MKT-N14AREV7

Figure 4. 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions, specically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductors online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 9

MM74HC14 Hex Inverting Schmitt Trigger

TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks. ACEx Build it Now CorePLUS CROSSVOLT CTL Current Transfer Logic EcoSPARK EZSWITCH *

Fairchild Fairchild Semiconductor FACT Quiet Series FACT FAST FastvCore FlashWriter *

FPS FRFET Global Power ResourceSM Green FPS Green FPSe-Series GTO i-Lo IntelliMAX ISOPLANAR MegaBuck MICROCOUPLER MicroFET MicroPak MillerDrive Motion-SPM OPTOLOGIC OPTOPLANAR

PDP-SPM Power220 POWEREDGE Power-SPM PowerTrench Programmable Active Droop QFET QS QT Optoelectronics Quiet Series RapidConfigure SMART START SPM STEALTH SuperFET SuperSOT -3 SuperSOT -6 SuperSOT -8

SupreMOS SyncFET

The Power Franchise

TinyBoost TinyBuck TinyLogic TINYOPTO TinyPower TinyPWM TinyWire SerDes UHC Ultra FRFET UniFET VCX

* EZSWITCH and FlashWriter are trademarks of System General Corporation, used under license by Fairchild Semiconductor. DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILDS WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Advance Information Product Status Formative or In Design Definition This datasheet contains the design specifications for product development. Specifications may change in any manner without notice. This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design. This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.

Rev. I33

2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Preliminary

First Production

No Identification Needed

Full Production

Obsolete

Not In Production

1983 Fairchild Semiconductor Corporation MM74HC14 Rev. 1.4.0

www.fairchildsemi.com 10

Das könnte Ihnen auch gefallen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- 74VHC14 Hex Schmitt Inverter: Features General DescriptionDokument8 Seiten74VHC14 Hex Schmitt Inverter: Features General DescriptionAriel NavarreteNoch keine Bewertungen

- 74HC14 PDFDokument8 Seiten74HC14 PDFNielsy R. Aparicio QuirogaNoch keine Bewertungen

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDokument6 SeitenCD40106BC Hex Schmitt Trigger: General Description Featuresgosa46Noch keine Bewertungen

- Datasheet 74HC32Dokument8 SeitenDatasheet 74HC32Lưu Chung KiênNoch keine Bewertungen

- 74HC04Dokument7 Seiten74HC04Brian DoyleNoch keine Bewertungen

- CD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesDokument8 SeitenCD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesbanoluNoch keine Bewertungen

- CD4093 PDFDokument8 SeitenCD4093 PDFIván IvanovNoch keine Bewertungen

- 023M01 (Triple NAND Gate)Dokument7 Seiten023M01 (Triple NAND Gate)el_george0079491Noch keine Bewertungen

- DatasheetDokument5 SeitenDatasheetIonut SimaNoch keine Bewertungen

- Datasheet 74HCT14Dokument7 SeitenDatasheet 74HCT14Humberto AcostaNoch keine Bewertungen

- 74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesDokument8 Seiten74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesAini NierisNoch keine Bewertungen

- HCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingDokument9 SeitenHCTS245MS: Radiation Hardened Octal Bus Transceiver, Three-State, Non-InvertingDeepa DevarajNoch keine Bewertungen

- Datasheet mc14584Dokument8 SeitenDatasheet mc14584Heriberto Flores AmpieNoch keine Bewertungen

- 4073Dokument7 Seiten4073S Eko AnangNoch keine Bewertungen

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDokument8 SeitenMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuNoch keine Bewertungen

- 74AC02 - 74ACT02 Quad 2-Input NOR Gate: General Description FeaturesDokument7 Seiten74AC02 - 74ACT02 Quad 2-Input NOR Gate: General Description FeaturesAlexandre S. CorrêaNoch keine Bewertungen

- 74HC7014 CNV PDFDokument9 Seiten74HC7014 CNV PDFCesar VilledaNoch keine Bewertungen

- 74AC08, 74ACT08 Quad 2-Input AND Gate: Features General DescriptionDokument10 Seiten74AC08, 74ACT08 Quad 2-Input AND Gate: Features General DescriptioniknowwhatudidNoch keine Bewertungen

- 4096 Circuito IntegradoDokument7 Seiten4096 Circuito IntegradoalexmanriqueNoch keine Bewertungen

- CD4010C Hex Buffers (Non-Inverting) : General Description FeaturesDokument5 SeitenCD4010C Hex Buffers (Non-Inverting) : General Description FeaturesRafael Alexandre CarvalhoNoch keine Bewertungen

- Description: LVPECL, LVDS Crystal Oscillator Data SheetDokument7 SeitenDescription: LVPECL, LVDS Crystal Oscillator Data Sheetbhuppi0802Noch keine Bewertungen

- Quad 2-Input AND Gate: KK74HC08ADokument5 SeitenQuad 2-Input AND Gate: KK74HC08Acatsoithahuong84Noch keine Bewertungen

- 74HC08Dokument7 Seiten74HC08Brian DoyleNoch keine Bewertungen

- CD 4069Dokument6 SeitenCD 4069shaniimranNoch keine Bewertungen

- National Semiconductor CD40106BCN DatasheetDokument7 SeitenNational Semiconductor CD40106BCN DatasheetAlan CienfuegosNoch keine Bewertungen

- mc14518bcp en PDFDokument8 Seitenmc14518bcp en PDFdellcoNoch keine Bewertungen

- 74HC240Dokument8 Seiten74HC240rajesha_sNoch keine Bewertungen

- MC 3488Dokument8 SeitenMC 3488d_richard_dNoch keine Bewertungen

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDokument7 SeitenMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeNoch keine Bewertungen

- 7Z08Dokument7 Seiten7Z08André Frota PaivaNoch keine Bewertungen

- C.I 74HC175Dokument7 SeitenC.I 74HC175DOMINGOS ALADIRNoch keine Bewertungen

- CD40106BE DatasheetDokument10 SeitenCD40106BE DatasheetOscar GonzalesNoch keine Bewertungen

- CD54/74HC688, CD54/74HCT688: Features DescriptionDokument6 SeitenCD54/74HC688, CD54/74HCT688: Features Descriptionbhavsar_vaibhavNoch keine Bewertungen

- CD 74 HCT 164 MDokument16 SeitenCD 74 HCT 164 MfabriziocasNoch keine Bewertungen

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADokument6 SeitenOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100Noch keine Bewertungen

- HCC4073B/81B/82B HCF4073B/81B/82B: and GatesDokument10 SeitenHCC4073B/81B/82B HCF4073B/81B/82B: and GatessttepencambiandoNoch keine Bewertungen

- CD4023Dokument6 SeitenCD4023Jules Le GrandNoch keine Bewertungen

- Ds Sgsthompson 4069 Hex NotDokument12 SeitenDs Sgsthompson 4069 Hex NotMohammed ElhadiNoch keine Bewertungen

- CD4028BC BCD-to-Decimal Decoder: General Description FeaturesDokument6 SeitenCD4028BC BCD-to-Decimal Decoder: General Description Featuresmalirezazadeh5549Noch keine Bewertungen

- CD4011BCDokument10 SeitenCD4011BCKike DavilaNoch keine Bewertungen

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDokument6 SeitenCD40106BC Hex Schmitt Trigger: General Description FeaturesRoozbeh BahmanyarNoch keine Bewertungen

- HCC4007UB HCF4007UB: Dual Complementary Pair Plus InverterDokument14 SeitenHCC4007UB HCF4007UB: Dual Complementary Pair Plus InverterRendy WandarosanzaNoch keine Bewertungen

- MC 14521Dokument12 SeitenMC 14521rrebollarNoch keine Bewertungen

- ICL8069 - Low Voltage Reference - Intersil CorporationDokument6 SeitenICL8069 - Low Voltage Reference - Intersil Corporationwlen2012Noch keine Bewertungen

- 4N37 Opto Salida TransistorDokument7 Seiten4N37 Opto Salida TransistorZoy HavelNoch keine Bewertungen

- FAN8082 (KA3082N) : Bi-Directional DC Motor DriverDokument13 SeitenFAN8082 (KA3082N) : Bi-Directional DC Motor DriverFrancisco Hernandez MartinezNoch keine Bewertungen

- Device Datasheet For CD4021Dokument7 SeitenDevice Datasheet For CD4021bdfbNoch keine Bewertungen

- MM74C00 - MM74C02 - MM74C04 Quad 2-Input NAND Gate - Quad 2-Input NOR Gate - Hex InverterDokument6 SeitenMM74C00 - MM74C02 - MM74C04 Quad 2-Input NAND Gate - Quad 2-Input NOR Gate - Hex InverterPragnesh Hasmukhbhai GajjarNoch keine Bewertungen

- 74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and OutputsDokument13 Seiten74LCX125 Low Voltage Quad Buffer With 5V Tolerant Inputs and Outputsfenixtec1Noch keine Bewertungen

- CD4047Dokument9 SeitenCD4047Haryadi VjNoch keine Bewertungen

- Ua723cn PDFDokument18 SeitenUa723cn PDFOsman KoçakNoch keine Bewertungen

- Ua 723Dokument21 SeitenUa 723roozbehxox0% (1)

- 2N7002L Small Signal MOSFET: 60 V, 115 Ma, N Channel SOT 23Dokument5 Seiten2N7002L Small Signal MOSFET: 60 V, 115 Ma, N Channel SOT 23Guillermo FrancisNoch keine Bewertungen

- 110 Waveform Generator Projects for the Home ConstructorVon Everand110 Waveform Generator Projects for the Home ConstructorBewertung: 4 von 5 Sternen4/5 (1)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsVon EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsBewertung: 3.5 von 5 Sternen3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Pseudovector - Wikipedia, The Free EncyclopediaDokument6 SeitenPseudovector - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Planck Constant - Wikipedia, The Free EncyclopediaDokument15 SeitenPlanck Constant - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- X86 Opcode and Instruction ReferenceDokument16 SeitenX86 Opcode and Instruction Referencebeta2009Noch keine Bewertungen

- Photon - Wikipedia, The Free EncyclopediaDokument22 SeitenPhoton - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Partial Differential Equation - Wikipedia, The Free EncyclopediaDokument17 SeitenPartial Differential Equation - Wikipedia, The Free Encyclopediabeta2009Noch keine Bewertungen

- Magnetic Potential - Wikipedia, The Free EncyclopediaDokument6 SeitenMagnetic Potential - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Multivariable Calculus - Wikipedia, The Free EncyclopediaDokument4 SeitenMultivariable Calculus - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Solaris (Operating System) - Wikipedia, The Free EncyclopediaDokument9 SeitenSolaris (Operating System) - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Lorentz Force - Wikipedia, The Free EncyclopediaDokument14 SeitenLorentz Force - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- James Clerk Maxwell - Wikipedia, The Free EncyclopediaDokument17 SeitenJames Clerk Maxwell - Wikipedia, The Free Encyclopediabeta2009Noch keine Bewertungen

- Current Density - Wikipedia, The Free EncyclopediaDokument6 SeitenCurrent Density - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Ampère's Circuital Law - Wikipedia, The Free EncyclopediaDokument9 SeitenAmpère's Circuital Law - Wikipedia, The Free Encyclopediabeta2009Noch keine Bewertungen

- Dbase - Wikipedia, The Free EncyclopediaDokument7 SeitenDbase - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Clipper (Programming Language) - Wikipedia, The Free EncyclopediaDokument3 SeitenClipper (Programming Language) - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Debian - Wikipedia, The Free EncyclopediaDokument17 SeitenDebian - Wikipedia, The Free Encyclopediad_richard_dNoch keine Bewertungen

- Adesto - Technologies AT25SF041 SSHD T DatasheetDokument45 SeitenAdesto - Technologies AT25SF041 SSHD T DatasheetNuno CarriçoNoch keine Bewertungen

- Mount and Solder Electronic Components: Information Sheet 1.3.1 Learning Outcome No. 3Dokument22 SeitenMount and Solder Electronic Components: Information Sheet 1.3.1 Learning Outcome No. 3Shaira Claire CorreNoch keine Bewertungen

- Three-Wire Serial EEPROM: 1. FeaturesDokument17 SeitenThree-Wire Serial EEPROM: 1. FeatureskppsadiNoch keine Bewertungen

- Sn74ls08n and 2entradasDokument23 SeitenSn74ls08n and 2entradasAndres PeñalozaNoch keine Bewertungen

- CD74HC238Dokument7 SeitenCD74HC238roozbehxoxNoch keine Bewertungen

- Fast Cmos Octal Registered Transceivers: IDT29FCT52AT/BT/CT/DT IDT29FCT2052AT/BT/CT IDT29FCT53AT/BT/CTDokument8 SeitenFast Cmos Octal Registered Transceivers: IDT29FCT52AT/BT/CT/DT IDT29FCT2052AT/BT/CT IDT29FCT53AT/BT/CTStuxnetNoch keine Bewertungen

- Vag Com WenasDokument4 SeitenVag Com Wenasundok1Noch keine Bewertungen

- Datasheet - 74LS283 - Somador Binário Completo de 4 BitsDokument7 SeitenDatasheet - 74LS283 - Somador Binário Completo de 4 BitsLucas CarvalhoNoch keine Bewertungen

- An826 - Sold Pads Vishay RecommendationDokument40 SeitenAn826 - Sold Pads Vishay Recommendationbetodias30Noch keine Bewertungen

- 64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BDokument21 Seiten64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BRoberto Kaled Silva ValdiviaNoch keine Bewertungen

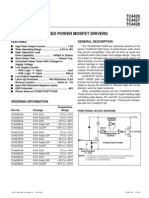

- TC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversDokument9 SeitenTC4426 TC4427 TC4428 1.5A Dual High-Speed Power Mosfet DriversroozbehxoxNoch keine Bewertungen

- PCB Land Pattern DesignsDokument10 SeitenPCB Land Pattern DesignsGabriel SmolnyckiNoch keine Bewertungen

- OZ IC DataDokument31 SeitenOZ IC DataMahi Q Mahi Q100% (1)

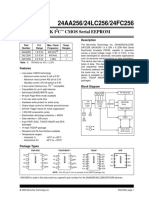

- EEPROM 24LC256 - Microchip PDFDokument28 SeitenEEPROM 24LC256 - Microchip PDFValdir DerlannNoch keine Bewertungen

- 25AA640A/25LC640A: 64K SPI Bus Serial EEPROMDokument36 Seiten25AA640A/25LC640A: 64K SPI Bus Serial EEPROMmarino246Noch keine Bewertungen

- CD54/74HC240, CD54/74HCT240, CD74HC241, CD54/74HCT241, CD54/74HC244, CD54/74HCT244Dokument12 SeitenCD54/74HC240, CD54/74HCT240, CD74HC241, CD54/74HCT241, CD54/74HC244, CD54/74HCT244Born Lion MateNoch keine Bewertungen

- PCB Part B (3rd Sem)Dokument22 SeitenPCB Part B (3rd Sem)jayant kumarNoch keine Bewertungen

- TL084 DatasheetDokument43 SeitenTL084 DatasheetciarmelNoch keine Bewertungen

- Np-R70a004 SegDokument10 SeitenNp-R70a004 SeglrohneNoch keine Bewertungen

- 93c46 DatasheetDokument12 Seiten93c46 Datasheetsimon_someone217Noch keine Bewertungen

- CCFL Inverter IC OZ960Dokument12 SeitenCCFL Inverter IC OZ960davesworkshopNoch keine Bewertungen

- MM74HC139 Dual 2-To-4 Line Decoder: General DescriptionDokument7 SeitenMM74HC139 Dual 2-To-4 Line Decoder: General DescriptionnizarfebNoch keine Bewertungen

- Dataman Mempro SpecificationDokument2 SeitenDataman Mempro SpecificationabcNoch keine Bewertungen

- 25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Dokument31 Seiten25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Ken AlonsoNoch keine Bewertungen

- The CAD Library of The FutureDokument35 SeitenThe CAD Library of The FutureChandragupta MowaveNoch keine Bewertungen

- Samsung CLP-650 Parts ListDokument28 SeitenSamsung CLP-650 Parts Listingmar_sNoch keine Bewertungen

- Datasheet 74hct40103Dokument17 SeitenDatasheet 74hct40103Yettie OgunduboyeNoch keine Bewertungen

- Datasheet - CI 7432Dokument5 SeitenDatasheet - CI 7432Alexandre NettoNoch keine Bewertungen

- Dec50143 - Cmos Integrated Circuit Design & FabricationDokument54 SeitenDec50143 - Cmos Integrated Circuit Design & FabricationKohilan VenugopalNoch keine Bewertungen

- CD405xB CMOS Single 8-Channel Analog Multiplexer/Demultiplexer With Logic-Level ConversionDokument43 SeitenCD405xB CMOS Single 8-Channel Analog Multiplexer/Demultiplexer With Logic-Level Conversionjohny cokecheNoch keine Bewertungen