Beruflich Dokumente

Kultur Dokumente

Módulo 5 Comunicacion Serial Asincrona

Hochgeladen von

Mishell Sanchez GuevaraCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Módulo 5 Comunicacion Serial Asincrona

Hochgeladen von

Mishell Sanchez GuevaraCopyright:

Verfügbare Formate

CURSO DE MICROCONTROLADORES PIC16F877A

USART

Mdulo 5: COMUNICACIN SERIE ASINCRONA

Entre las herramientas que disponen los PIC16F877A se encuentra el USART, llamado SCI (Serial Comunications Interface), puede funcionar como un sistema de comunicacin bidireccional, adaptndose a multitud de perifricos y dispositivos que transfieren informacin de forma serial, tales como un ordenador. Tambin puede trabajar en modo unidireccional para soportar perifricos como memorias, conversores, etc. El USART (Transmisor/Receptor Sncrono/Asncrono Serie) puede trabajar de dos formas: Asncrono (Bidireccional) Sncrono (Unidireccional)

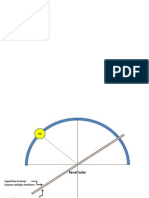

En el modo asncrono, la comunicacin serie del USART en los PIC16F877A esta soportada por las lneas RC6/TX/CK y RC7/RX/DT por las que se mueven los bits a la frecuencia interna de reloj. En el modo sncrono, los bits de informacin circulan en ambos sentidos por la lnea DT a la frecuencia de los impulsos que genere el maestro por la lnea CK. En el presente mdulo vamos a enfocar el estudio del modo asncrono. En esta forma de comunicacin serie, se usa la norma RS-232C, donde cada palabra de informacin o dato se enva independientemente de los dems. Suele constatar de 8 o 9 bits y van precedidos por un bit de START (inicio) y detrs de ellos se coloca un bit de STOP (parada), de acuerdo con las normas del formato estndar NRZ (Non Return-toZero) Los bits se transfieren a una frecuencia fija y normalizada. La USART transmite y recibe primero el bit menos significativo. La USART en modo asncrono contiene los siguientes elementos: - Generador de Baudios - Circuito de Muestreo - Transmisor Asncrono - Receptor Asncrono Generador de Baudios Para el protocolo asncrono RS-232C, la frecuencia en baudios (bits por segundo) a la que se realiza la transferencia se debe efectuar a un valor normalizado: 330, 600, 1200, 2400, 4800, 9600, 19200, 38400, etc. Para generar esta frecuencia, el USART dispone de un generador de frecuencia en Baudios, BRG, cuyo valor es controlado por el contenido grabado en el registro SPBRG. Aparte del valor X cargado en el registro SPBRG, la frecuencia en baudios del generador depende del bit BRGH del registro TXSTA <2>. En el caso de que BRGH = 0 se trabaja en baja velocidad y si BRGH = 1 se trabaja en alta velocidad. Segn este bit se obtendr el valor de una constante K necesaria en la determinacin de la frecuencia de funcionamiento.

Donde: X Es el valor cargado al registro SPBRG BRG Si BRG = 0, baja velocidad y K = 64 Si BRG = 1, baja velocidad y K = 16

Profesor: Mishell Sanchez

Pgina 1

CURSO DE MICROCONTROLADORES PIC16F877A

Frecuencias en baudios para el Modo Asncrono (BRGH=0)

USART

Profesor: Mishell Sanchez

Pgina 2

CURSO DE MICROCONTROLADORES PIC16F877A

USART

Frecuencias en baudios para el Modo Asncrono (BRGH=1)

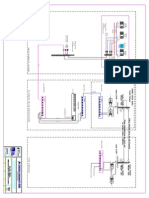

Trasmisor Asncrono La figura muestra el diagrama por bloques de la seccin de transmisin del USART en modo asncrono.

El dato que se desea transmitir por el USART se deposita en el registro TXREG y a continuacin se traspasa al registro de desplazamiento TSR, que va sacando los bits secuencialmente y a la frecuencia establecida. Adems, antes de los bits del dato de informacin incluye un bit de inicio y despus de sacar todos los bits aade un bit de parada. El USART receptor recibe, uno a uno, los bits, elimina los de control y los de informacin una vez que han llenado el registro de desplazamiento RSR los traslada automticamente al registro RCREG, donde quedan disponibles para su posterior procesamiento.

Profesor: Mishell Sanchez

Pgina 3

CURSO DE MICROCONTROLADORES PIC16F877A

USART

Si observamos el diagrama de bloques de la seccin transmisora del USART. El ncleo est constituido por el registro de desplazamiento TSR, que obtiene el dato desde el registro TXREG y luego lo va desplazando y sacando bit a bit, en serie, por la lnea RC6/TX/CK. El primer bit que sale es el de menos peso. El dato a transferir se carga por software en TXREG y se transfiere al TSR en cuanto se haya transmitido el bit de parada del dato anterior. LA transferencia entre los dos registros se realiza en un ciclo y entonces el sealizador TXIF se pone a 1, para advertir que el registro de transmisin se ha vaciado. Tambin en este momento puede producirse una interrupcin si se ha posibilitado el uso de interrupciones. Cuando se escribe otro dato sobre TXREG, l sealizador TXIF se pone a 0. El bit TRMT sirve para indicar el estado del registro TSR y vale 1 cuando est vaco. La secuencia de pasos a seguir para una transmisin en el USART es la como sigue: 1. 2. 3. 4. 5. 6. 7. Configurar las lneas RC6/TX/CK como salida y RC7/RX/DT como entrada. Asignar SYNC=0 y SPEN=1 para activar el USART como asncrono. Si se va a trabajar con interrupcin, asignar TXIE=1, adems de habilitar las interrupciones. Si el dato consta de 9 bits, en lugar de los 8 tpicos, asignar el bit TX9=1. El noveno bit se colocar en TX9D (TXSTA) Se carga el valor adecuado en el registro SPBRG, para producir la frecuencia de trabajo deseada. Hay que controlar el bit BRGH (alta y baja velocidad) Activar la transmisin con TXEN = 1. El bit TXIF tendr valor 1; ya que TXREG se encuentra vacio. Cargar en TXREG el dato a transmitir. Comienza la transmisin.

TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

bit 7

bit 6

bit 5

bit 4

bit 3 bit 2

bit 1

bit 0

CSRC: bit de seleccin de reloj Modo asncrono: no incluye Modo sncrono 1 = Modo maestro (reloj generado internamente desde BRG) 0 = Modo esclavo (reloj generado por una fuente externa) TX9 : Habilita el bit 9 de transmisin 1 = Selecciona transmisin de 9 bits 0 = Selecciona transmisin de 8 bits TXEN: Activa la transmisin 1 = Transmisin activada 0 = Transmisin desactivada Nota: SREN/CREN anula TXEN en modo sncrono. SYNC: Bit de seleccin del modo del USART 1 = Modo sncrono 0 = Modo asncrono Bit no implementado. Ledo como '0' BRGH: Bit de seleccin de la velocidad de baudios Modo asncrono: 1 = Alta velocidad 0 = Baja velocidad Modo Sncrono: No se usa en este modo TRMT: Bit de estado del registro de desplazamiento de transmisin 1= TSR vaco 0 = TSR no vaco TX9D: Bit 9 del dato a transmitir (puede ser el bit de paridad)

Profesor: Mishell Sanchez

Pgina 4

CURSO DE MICROCONTROLADORES PIC16F877A

Receptor Asncrono

USART

La figura muestra el diagrama de bloques de la seccin receptora del USART

Los datos se reciben en serie, bit a bit, por la linea RC7/RX/DT y se van introduciendo secuencialmente en el registro de desplazamiento RSR que funciona a una frecuencia 16 veces ms rpida que la de trabajo (baud rate). Cuando el dato consta de 9 bits hay que programar el bit RX9 = 1 y el noveno bit de informacin se colocar en el bit RX9D del registro RCSTA.

Una vez que el modo asncrono ha sido seleccionado, la recepcin es habilitada colocando a 1-lgico el bit CREN (RCSTA<4>). El corazn de la recepcin serial es el registro de corrimiento de recepcin (RSR). Despus de detectar el bit de parada la data presente en RSR es transferida al registro RCREG (si es que est vaco). Si la transferencia ha sido completada con xito el RCIF (PIR1<5>) es puesto a 1-lgico. Si lo deseamos podemos usar esta caracterstica para trabajar interrupciones. Para ello deberemos habilitar

Profesor: Mishell Sanchez

Pgina 5

CURSO DE MICROCONTROLADORES PIC16F877A

USART

el bit CIE (PIE1<5>). El bit RCIF solo es de lectura y colocado a 0-lgico por hardware; es decir cuando el registro RCREG est vaco. Al parecer el registro RCREG es un solo registro pero no es asi; el registro RCREG es una suerte de pila de dos posiciones. Por tanto es capaz de almacenar 2 datos (bytes) y mantener un tercer dato en RSR. Si la pila est llena y se llena el RSR (tercer dato) es decir llega el bit de stop de ese tercer dato el microcontrolador procede a colocar a 1-lgico el bit OERR (over run error bit) y el valor presente en RSR se pierde. De darse esta situacin lo que debemos hacer es rescatar los dos datos que estn en la pila de RCREG. Luego resetear el OERR, para eso es necesario resetear el bit CREN (ponerlo a 0-lgico y luego a 1-lgico). Cuando se activa el bit OERR las transferencias de RSR a RCREG son deshabilitadas por lo tanto debemos cumplir con hacer el reset del bit CREN para normalizar la recepcin. Hay otro bit que tambin es importante sealar y es el bit FERR (RCSTA<2>) error de frame o trama o marco. El bit FERR se coloca a 1-lgico si detecta un 0-lgico como bit de parada. Por lo tanto antes de leer lo que contiene el registro RCREG es necesario revisar el valor de los bits FERR y OERR. La siguiente es la secuencia de pasos a realizar para configurar la recepcin asncrona: 1. 2. 3. 4. 5. 6. 7. 8. 8. 9. Inicializar el registro SPBRG con el valor apropiado que genere los baudios necesarios. No olvide colocar un valor al bit BRGH en funcin a si va o no a transmitir en alta velocidad. Habilite la puerta serial asncrona colocando a 0-lgico el bit SYNC y a 1-lgico el bit SPEN. Si se va a trabajar con interrupcin, asignar RCIE=1, adems de habilitar las interrupciones. Habilite la recepcin colocando a 1-lgico el bit CREN. El bit RCIF se colocar a 1-lgico cuando un dato llegue completo al microcontrolador y una interrupcin se generar si es que se ha seteado el bit RCIE. Lea el registro RCSTA para obtener el valor del noveno bit (si es que est trabajando con 9 bits de datos) y determine si hubo error en la comunicacin (revise los bits OERR y FERR). Si no hubo error lea los 8 bits de datos del registro RCREG. Si no hubo algn error resetee el bit CREN.

bit 7 serial) bit 6

SPEN: Habilitacin del puerto serie 1 = Puerto serie habilitado (configura los pines RC7/RX/DT y RC6/TX/CK como pines del puerto 0 = Puerto serie deshabilitado RX9: Habilita el bit 9 de recepcin 1 = Selecciona recepcin de 9 bits 0 = Selecciona recepcin de 8 bits SREN: Configura la recepcin sencilla Modo asncrono no incluye Modo sncrono maestro 1 = Habilita recepcin sencilla 0 = Deshabilita recepcin sencilla Modo sncrono esclavo no se utiliza CREN: Configura la recepcin continua Modo asncrono: 1 = Habilita modo de recepcin continua 0 = Deshabilita recepcin continua Modo sncrono: 1 = Habilita recepcin continua hasta que el bit CREN es borrado 0 = Deshabilita recepcin continua

bit 5

bit 4

Profesor: Mishell Sanchez

Pgina 6

CURSO DE MICROCONTROLADORES PIC16F877A

bit 3

USART

bit 2

bit 1

bit 0

ADDEN: Deteccin de direccin Modo asncrono con 9 bits (RX9 = 1): 1 =Activa la deteccin de direccin, activa la interrupcin y descarga el buffer de recepcin al activarse RSR<8> 0 =Desactiva la deteccin de direccin, todos los bits son recibidos y el bit 9 puede ser utilizado como bit de paridad FERR: Bit de error de trama 1 = Error de trama (puede ser actualizado leyendo el registro RCREG y recibir el siguiente dato vlido 0 = No hay error de trama OERR: Bit de error de sobrepasamiento 1 = Error de sobrepasamiento (puede ser borrado escribiendo un 0 en el bit CREN) 0 = No hay error de sobrepasamiento RX9D: Bit 9 del dato recibido (Puede ser el bit de paridad)

Hasta aqu hemos descrito a nivel de hardware la transmisin/recepcin Serial, a continuacin presentaremos las rutinas necesarias para la configuracin, transmisin y recepcin serial en ASM: ;******************** Configura al PIC para transmitir datos *************************** inicio_TX bsf STATUS,RP0 ; Ir al Banco 1 bcf TRISC,6 ; RC6 como salida movlw .129 movwf SPBRG ; 9600 bps XTAL: 20MHz movlw B'00100100' movwf TXSTA ; Modo asincrono / Tx Enable / 8 bits / BRGH = 1 bcf STATUS,RP0 ; Ir al Banco 0 bsf RCSTA,7 ; Habilita Puerto Serial bcf PIR1,TXIF ; Limpia el Indicador de Interrupcin por fin de transmisin return ;********************** Configura al PIC para recibir datos *************************** inicio_RX bsf STATUS,RP0 ; Ir al Banco 1 movlw .129 movwf SPBRG ; 9600 bps XTAL: 20MHz bsf TRISC,7 ; RC7 como entrada bsf TXSTA,BRGH ; BRGH='1' bcf STATUS,RP0 ; Ir al Banco 0 movlw B'10010000' movwf RCSTA ; Modo asncrono / Rx Enable / 8 bits bcf PIR1,RCIF ; Limpia el Indicador de Interrupcin por Recepcin de dato return ;*********************** Transmite el dato que est en W **************************** TX_DATO movwf TXREG ; TXREG <= WREG bsf STATUS,RP0 ; Ir al banco 1 btfss TXSTA,TRMT ; Espera que el perifrico est listo para transmitir otro dato goto $-1 bcf STATUS,RP0 ; Ir al banco 0 return ;******************* Espera por un dato y lo carga en W ************************* WAIT_RX btfss PIR1,RCIF ; Verifica hasta que haya un dato listo, si lo hay saltara goto $-1 bcf PIR1,RCIF ; Limpiamos el indicador de interrupcin por recepcin movf RCREG,W ; WREG <= RCREG return

Profesor: Mishell Sanchez

Pgina 7

CURSO DE MICROCONTROLADORES PIC16F877A

USART

Ejercicio1: Transmitir la palabra HOLA ENTER - MUNDO del PIC hasta la computadora y visualizar el dato por el hyper terminal de Windows. La Velocidad a la que se transmitir ser de 9600bps. Usar un cristal de 4MHz Para este problema usaremos las rutinas descritas anteriormente, sin embargo vemos que por condicon del problema el cristal ahora es de 4MHz, esto significa que tendremos que calcular otros valor para SPBRG.

Donde: X Es el valor cargado al registro SPBRG BRG Si BRG = 0, baja velocidad y K = 64 Si BRG = 1, baja velocidad y K = 16

Para BRG = 1, entonces K=16:

El nuevo valor que usaremos para SPBRG =25, con esto tendremos 9600bps con un cristal de 4MHz.

El Programa en ASM para este ejercicio es: __config _CP_OFF & _PWRTE_ON & _WDT_OFF & _WDT_OFF & _XT_OSC list P=16F877a include<p16f877a.inc> ORG HOLA movlw call movlw call movlw call movlw call ENTER movlw call movlw call MUNDO movlw call movlw call movlw call 'M' TX_DATO 'U' TX_DATO 'N' TX_DATO 0x0a TX_DATO 0x0d TX_DATO ; Estos valores en hexadecimal ; producen el salto ENTER. ; Se debe transmitir ambos ; valores. 'H' TX_DATO 'O' TX_DATO 'L' TX_DATO 'A' TX_DATO ; El valor en ASCII va entre comillas ; Transmitimos el dato 0x000 call

inicio_TX

; configuracion para comunicacin serial

Profesor: Mishell Sanchez

Pgina 8

CURSO DE MICROCONTROLADORES PIC16F877A

movlw call movlw call sleep 'D' TX_DATO 'O' TX_DATO ; Dormimos al PIC

USART

;*********************************************************** inicio_TX bsf STATUS,RP0 bcf TRISC,6 movlw .25 movwf SPBRG movlw B'00100100' movwf TXSTA bcf STATUS,RP0 bsf RCSTA,7 bcf PIR1,TXIF return TX_DATO movwf TXREG bsf STATUS,RP0 btfss TXSTA,TRMT goto $-1 bcf STATUS,RP0 return END

Profesor: Mishell Sanchez

Pgina 9

CURSO DE MICROCONTROLADORES PIC16F877A

USART

Ejercicio2: Recibir datos por el puerto serial del PIC y mostrarlos en el PORTD. La Velocidad a la que se recibir los datos ser de 115200 bps. Usar un cristal de 20MHz. Al igual que en el problema anterior hallaremos el nuevo valor para SPBRG para la velocidad de 115200bps usando un cristal de 20MHz:

Despejando X:

Para BRG = 0, entonces K=16:

El nuevo valor que usaremos para SPBRG =10, con esto tendremos 9600bps con un cristal de 4MHz. El Programa en ASM sera:

Profesor: Mishell Sanchez

Pgina 10

CURSO DE MICROCONTROLADORES PIC16F877A

USART

Profesor: Mishell Sanchez

Pgina 11

Das könnte Ihnen auch gefallen

- UART PIC18F4550Dokument7 SeitenUART PIC18F4550victor hugo matos guerreroNoch keine Bewertungen

- Comunicación Serial RS232 PIC16F877ADokument6 SeitenComunicación Serial RS232 PIC16F877AEduardohrdz HernandezNoch keine Bewertungen

- Modulo UsartDokument37 SeitenModulo UsartEduardo GarciaNoch keine Bewertungen

- Informe LCD y PicDokument5 SeitenInforme LCD y PicWASHINGTON AMORESNoch keine Bewertungen

- Reloj y Calendario en Arduino Con Los RTC DS1307 y DS3231Dokument20 SeitenReloj y Calendario en Arduino Con Los RTC DS1307 y DS3231artemio hernandez gallegosNoch keine Bewertungen

- Gprs Comandos at PicDokument95 SeitenGprs Comandos at PicDiegoMartinezDiaz100% (1)

- Generando Una Funcion de Onda DeseadaDokument6 SeitenGenerando Una Funcion de Onda DeseadaSteven Alexander Buritica MartinezNoch keine Bewertungen

- Arquitectura Interna Del MicrocontroladorDokument9 SeitenArquitectura Interna Del MicrocontroladorUriel SolisNoch keine Bewertungen

- Configurar El BlueTooh HC-05Dokument29 SeitenConfigurar El BlueTooh HC-05Sara Lucia Rueda JaramilloNoch keine Bewertungen

- Contador DijitalDokument10 SeitenContador Dijitaltomkito100% (1)

- Práctica 9Dokument13 SeitenPráctica 9Rodrigo Varona GarciaNoch keine Bewertungen

- Proyecto Matriz de Leds SencillaDokument8 SeitenProyecto Matriz de Leds SencillaAlexander Aguiño ViverosNoch keine Bewertungen

- Turnero digital de dos dígitos con PIC16F84 y displays de LEDDokument4 SeitenTurnero digital de dos dígitos con PIC16F84 y displays de LEDGonzalo Bazoalto OlmosNoch keine Bewertungen

- Contador 4518-4511Dokument2 SeitenContador 4518-4511joacolandyaNoch keine Bewertungen

- Onda Senoidal Con ArduinoDokument5 SeitenOnda Senoidal Con ArduinoDuván Ricardo GuzmánNoch keine Bewertungen

- Experimento de Electrónica Con Componente 74HC595Dokument11 SeitenExperimento de Electrónica Con Componente 74HC595Josemaría VilledaNoch keine Bewertungen

- Marcador_BasketDokument16 SeitenMarcador_Basketcorpses88Noch keine Bewertungen

- Informe de Reloj DigitalDokument22 SeitenInforme de Reloj DigitalWilliams Molina EspirituNoch keine Bewertungen

- PIC16F886 Investigación CI MicrocontroladorDokument11 SeitenPIC16F886 Investigación CI MicrocontroladorIsaias RiveraNoch keine Bewertungen

- Descripción Del Kit Stm32 f4 DiscoveryDokument4 SeitenDescripción Del Kit Stm32 f4 DiscoveryJonathan Betop LhuzonNoch keine Bewertungen

- Proyecto c1 181Dokument3 SeitenProyecto c1 181Emily LopezNoch keine Bewertungen

- 2 - Ucpic18f2550 2017Dokument37 Seiten2 - Ucpic18f2550 2017hipolitoNoch keine Bewertungen

- SemaforoDokument5 SeitenSemaforoRomany DanielNoch keine Bewertungen

- Acoplamiento de ContadoresDokument9 SeitenAcoplamiento de ContadoresAnonymous jv3i8NANoch keine Bewertungen

- Contador 7 segmentos PICDokument7 SeitenContador 7 segmentos PICMian Chauca ApazaNoch keine Bewertungen

- Informe Final 4 - Ci 74ls194Dokument8 SeitenInforme Final 4 - Ci 74ls194edsonygisellaNoch keine Bewertungen

- Timers AVRDokument70 SeitenTimers AVRmarkus_x86100% (1)

- Ejemplos y Practicas 7 y 8 Timer 1Dokument8 SeitenEjemplos y Practicas 7 y 8 Timer 1lfba_16Noch keine Bewertungen

- Puertos Io Pic16f628aDokument1 SeitePuertos Io Pic16f628aRoger Reynaldo Guachalla NarvaezNoch keine Bewertungen

- Control de Potencia en AC Con Triac y Microcontrolador PIC 16F628ADokument8 SeitenControl de Potencia en AC Con Triac y Microcontrolador PIC 16F628ALuis Alejandro Ramos RojasNoch keine Bewertungen

- CD4094, registro de desplazamiento para displays 7 segmentosDokument3 SeitenCD4094, registro de desplazamiento para displays 7 segmentosJuan Luis100% (1)

- CronoCronometro Digital Controlado Por Bluetooth en Una Aplicación Androidmetro Digital Controlado Por Bluetooth en Una Aplicación AndroidDokument10 SeitenCronoCronometro Digital Controlado Por Bluetooth en Una Aplicación Androidmetro Digital Controlado Por Bluetooth en Una Aplicación AndroidHarold Stiven Amaya VillamilNoch keine Bewertungen

- El Módulo Adc de Los Avr PDFDokument27 SeitenEl Módulo Adc de Los Avr PDFmi_papiNoch keine Bewertungen

- RTC DS1302 reloj tiempo real ArduinoDokument4 SeitenRTC DS1302 reloj tiempo real Arduinobuitrago sanchez johan sebastianNoch keine Bewertungen

- Contador VHDLDokument6 SeitenContador VHDLAntonio PérezNoch keine Bewertungen

- Introducción a los Microcontroladores PIC16F8XX: Aplicaciones, Periféricos y Programación BásicaDokument31 SeitenIntroducción a los Microcontroladores PIC16F8XX: Aplicaciones, Periféricos y Programación BásicacarlosbuitronNoch keine Bewertungen

- Módulo NRF24L01Dokument11 SeitenMódulo NRF24L01Cindy MoralesNoch keine Bewertungen

- INTCON registroDokument1 SeiteINTCON registroJorge AlviarezNoch keine Bewertungen

- Capitulo 1Dokument42 SeitenCapitulo 1Max AlvarezNoch keine Bewertungen

- Funcionamiento Técnico de Un Reproductor DVDDokument4 SeitenFuncionamiento Técnico de Un Reproductor DVDJorge Ivan Ospina Mejia50% (4)

- Curso de Programación de PIC en PICBasic Pro - Página 4Dokument93 SeitenCurso de Programación de PIC en PICBasic Pro - Página 4Rene Gonzales VasquezNoch keine Bewertungen

- Curso MikrobasicDokument9 SeitenCurso MikrobasicEdson RodasNoch keine Bewertungen

- Termómetro DigitalDokument7 SeitenTermómetro DigitalChristianMRDNoch keine Bewertungen

- 2 Contador de 0-99 7segDokument6 Seiten2 Contador de 0-99 7segJalapa Lug GuatemalaNoch keine Bewertungen

- Registros PORT ArduinoDokument4 SeitenRegistros PORT ArduinoIvan Andres MuñozNoch keine Bewertungen

- Proyecto Básico Con PICDokument3 SeitenProyecto Básico Con PICOscar Ramos VeraNoch keine Bewertungen

- Manejo de Lcd-128x64 Con Pic18f4550Dokument8 SeitenManejo de Lcd-128x64 Con Pic18f4550Juan David OrtizNoch keine Bewertungen

- Introducción Al Sistema de Computación PersonalDokument23 SeitenIntroducción Al Sistema de Computación PersonalSergio RamosNoch keine Bewertungen

- P3 Satuquinga Evelin ContadoresDokument15 SeitenP3 Satuquinga Evelin ContadoresEvelin SatuquingaNoch keine Bewertungen

- Entrenador Pic 16f84a - 16f628aDokument10 SeitenEntrenador Pic 16f84a - 16f628aGabriela ONoch keine Bewertungen

- Clase 13 I2cDokument80 SeitenClase 13 I2cDavid Alejandro Espejo GarciaNoch keine Bewertungen

- Tema 6 Teclado Digital DecimalDokument4 SeitenTema 6 Teclado Digital Decimal2mercedesNoch keine Bewertungen

- Amplificador de AudioDokument12 SeitenAmplificador de Audiousi moscosoNoch keine Bewertungen

- Sistemas Embebidos Basados en MicrocontroladoresDokument7 SeitenSistemas Embebidos Basados en MicrocontroladoresAntony Salcedo OrtizNoch keine Bewertungen

- MANUAL DE PRÁCTICAS DE SISTEMAS DIGITALES II-aDokument79 SeitenMANUAL DE PRÁCTICAS DE SISTEMAS DIGITALES II-aElizabeth Manzano ZavalaNoch keine Bewertungen

- El Puerto Serial RS232 2022ADokument16 SeitenEl Puerto Serial RS232 2022AMonse MorenoNoch keine Bewertungen

- Comunicacion Serial UsartDokument2 SeitenComunicacion Serial UsartAlvio Valencia GonzaliaNoch keine Bewertungen

- Use RS232Dokument6 SeitenUse RS232Gräce Mäggüiie PicöNoch keine Bewertungen

- Ejemplo de Comunicacion Entre PicsDokument12 SeitenEjemplo de Comunicacion Entre PicsDanielNoch keine Bewertungen

- USART (Universal Synchronous Asynchronous Receiver Transmitter)Dokument22 SeitenUSART (Universal Synchronous Asynchronous Receiver Transmitter)Edson AguirreNoch keine Bewertungen

- SYLLABUS Capacitación SEDAPALDokument2 SeitenSYLLABUS Capacitación SEDAPALMishell Sanchez GuevaraNoch keine Bewertungen

- Tarea 3 Controlador y Observador Sistema MIMODokument22 SeitenTarea 3 Controlador y Observador Sistema MIMOMishell Sanchez Guevara0% (1)

- Entrenadores Siemens 2014 (LOGO y S7-1200)Dokument61 SeitenEntrenadores Siemens 2014 (LOGO y S7-1200)Mishell Sanchez Guevara50% (2)

- Estudio Enlaces 7GHZDokument3 SeitenEstudio Enlaces 7GHZMishell Sanchez GuevaraNoch keine Bewertungen

- CONTROL AVANZADODokument4 SeitenCONTROL AVANZADOMishell Sanchez GuevaraNoch keine Bewertungen

- Ie-11.Planos Comunicaciones MayoDokument1 SeiteIe-11.Planos Comunicaciones MayoMishell Sanchez GuevaraNoch keine Bewertungen

- Borrador Ejercicio Lógica DifusaDokument4 SeitenBorrador Ejercicio Lógica DifusaMishell Sanchez GuevaraNoch keine Bewertungen

- Clase1 IntroduccionDokument17 SeitenClase1 IntroduccionMishell Sanchez GuevaraNoch keine Bewertungen

- Tutor PathlossDokument14 SeitenTutor PathlossMishell Sanchez GuevaraNoch keine Bewertungen

- El Problema EconómicoDokument18 SeitenEl Problema EconómicoMishell Sanchez GuevaraNoch keine Bewertungen

- Control voltaje paneles solaresDokument6 SeitenControl voltaje paneles solaresMishell Sanchez GuevaraNoch keine Bewertungen

- Control 2012Dokument31 SeitenControl 2012Mishell Sanchez Guevara100% (1)

- Documentacion Sistema de MedicionDokument3 SeitenDocumentacion Sistema de MedicionMishell Sanchez GuevaraNoch keine Bewertungen

- T Rec G.703 200111 I!!pdf SDokument62 SeitenT Rec G.703 200111 I!!pdf SjustrichiNoch keine Bewertungen

- Sistemas de control avanzado digitales: conceptos básicosDokument126 SeitenSistemas de control avanzado digitales: conceptos básicosMishell Sanchez Guevara100% (1)

- Como Conectar Un Mosfet de Potencia A Un MicrocontroladorDokument6 SeitenComo Conectar Un Mosfet de Potencia A Un MicrocontroladorMishell Sanchez GuevaraNoch keine Bewertungen

- T Rec G.772 198811 S!!PDF SDokument8 SeitenT Rec G.772 198811 S!!PDF SMishell Sanchez GuevaraNoch keine Bewertungen

- Pic40 28 GuiaDokument8 SeitenPic40 28 GuiaMishell Sanchez GuevaraNoch keine Bewertungen

- El Amor Encontro El CaminoDokument31 SeitenEl Amor Encontro El CaminoMishell Sanchez GuevaraNoch keine Bewertungen

- Examen Final Domiciliario de PIC en CDokument4 SeitenExamen Final Domiciliario de PIC en CMishell Sanchez GuevaraNoch keine Bewertungen

- Angulos de Tait-Bryan y SensoresDokument10 SeitenAngulos de Tait-Bryan y SensoresMishell Sanchez GuevaraNoch keine Bewertungen

- Clase 1 Compilador CCS CDokument31 SeitenClase 1 Compilador CCS CMishell Sanchez GuevaraNoch keine Bewertungen

- Examen Final de Pic en CDokument2 SeitenExamen Final de Pic en CMishell Sanchez GuevaraNoch keine Bewertungen

- Clase 1 Compilador CCS CDokument31 SeitenClase 1 Compilador CCS CMishell Sanchez GuevaraNoch keine Bewertungen

- Clase 2 Gestión de Los Puertos Digitales CDokument12 SeitenClase 2 Gestión de Los Puertos Digitales CMishell Sanchez GuevaraNoch keine Bewertungen

- Módulo 2 Manejo de TimersDokument20 SeitenMódulo 2 Manejo de TimersMishell Sanchez GuevaraNoch keine Bewertungen

- General I Dad EsDokument11 SeitenGeneral I Dad EsMishell Sanchez GuevaraNoch keine Bewertungen

- Módulo 1 - Manejo de Puertos DigitalesDokument22 SeitenMódulo 1 - Manejo de Puertos DigitalesMishell Sanchez GuevaraNoch keine Bewertungen

- Módulo 6 Conversor ADDokument14 SeitenMódulo 6 Conversor ADMishell Sanchez GuevaraNoch keine Bewertungen

- Clase 6 TDA PILAS Y COLASDokument26 SeitenClase 6 TDA PILAS Y COLASChrystal CastleNoch keine Bewertungen

- Exámenes Ingeniería de Computadores IDokument124 SeitenExámenes Ingeniería de Computadores Iantonio perezNoch keine Bewertungen

- Array ListDokument4 SeitenArray ListTavo SierraNoch keine Bewertungen

- 2021 SeptiembreDokument2 Seiten2021 SeptiembreismsNoch keine Bewertungen

- Componentes de Un Aplicación AndroidDokument8 SeitenComponentes de Un Aplicación AndroidCarlos Omar YacilaNoch keine Bewertungen

- Características y uso de microcontroladores PICDokument53 SeitenCaracterísticas y uso de microcontroladores PICAldryOsvely SandreaNoch keine Bewertungen

- Recursividad Conceptos BásicosDokument7 SeitenRecursividad Conceptos BásicosjsedanomNoch keine Bewertungen

- Actividad - Semana - 2 Resuelto EnsambladorDokument6 SeitenActividad - Semana - 2 Resuelto EnsambladorKira Shivan Cubukus100% (1)

- Instrucciones PUSH y POP para manejo de pila en ensambladorDokument7 SeitenInstrucciones PUSH y POP para manejo de pila en ensambladorKrloz ChokzNoch keine Bewertungen

- SpinDokument24 SeitenSpinNews Today100% (2)

- CLASE 4 - Microprocesadores, EMU 8086Dokument8 SeitenCLASE 4 - Microprocesadores, EMU 8086MiltonNoch keine Bewertungen

- Controlador Disco RAM MINIXDokument8 SeitenControlador Disco RAM MINIXJose Lenin Martinez Murillo0% (1)

- Unidad 2 Ensamblador - TemaDokument22 SeitenUnidad 2 Ensamblador - Temadarien riveraNoch keine Bewertungen

- 316 - MicroprocesadoresDokument103 Seiten316 - MicroprocesadoresRafael CalderaNoch keine Bewertungen

- Programacion C++ t12 ColasDokument14 SeitenProgramacion C++ t12 ColasNachoBrotoBlascoNoch keine Bewertungen

- Angelica Bello - EntregableDokument4 SeitenAngelica Bello - EntregableAngelica PerezNoch keine Bewertungen

- Cuestionario de Teoria de La ProgramaciónDokument6 SeitenCuestionario de Teoria de La ProgramaciónDiegoNoch keine Bewertungen

- Richard Reese-Understanding and Using C Pointers-Oreilly Media (2013)Dokument226 SeitenRichard Reese-Understanding and Using C Pointers-Oreilly Media (2013)Olga Angelica Barreros RodriguezNoch keine Bewertungen

- Unidad 3. Modularización PDFDokument4 SeitenUnidad 3. Modularización PDFVictor Alfonso MontalvoNoch keine Bewertungen

- Sílabo Por CompetenciasDokument10 SeitenSílabo Por CompetenciasGUILLEN ROMANI CARLOS ALBERTONoch keine Bewertungen

- Simulador de 8085Dokument63 SeitenSimulador de 8085Sergio Puente100% (1)

- Memorias y Periféricos - Visualizar y Modificar RegistrosDokument2 SeitenMemorias y Periféricos - Visualizar y Modificar RegistrosLaura MarquezNoch keine Bewertungen

- Pilas en C++Dokument7 SeitenPilas en C++rikudouriisNoch keine Bewertungen

- Funciones Principales OpenglDokument11 SeitenFunciones Principales OpenglMarco Antonio Alpaca Ch.Noch keine Bewertungen

- Prog hp48Dokument62 SeitenProg hp48Andres Caro100% (1)

- Unidad 3 Sistemas Basados en Microprocesadores SBM UAMDokument28 SeitenUnidad 3 Sistemas Basados en Microprocesadores SBM UAMLex CalNoch keine Bewertungen

- Direccionamiento de MemoriaDokument10 SeitenDireccionamiento de MemoriaGustavo Joaquín Bustamante JaureNoch keine Bewertungen

- Cap 6 - Lya Tarea Control de LecturaDokument2 SeitenCap 6 - Lya Tarea Control de LecturaTom BahenaNoch keine Bewertungen

- Tics UnlamDokument55 SeitenTics UnlamEmaNoch keine Bewertungen

- Clase 1Dokument24 SeitenClase 1Fera SiulNoch keine Bewertungen