Beruflich Dokumente

Kultur Dokumente

EXP5

Hochgeladen von

fatih_ealOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

EXP5

Hochgeladen von

fatih_ealCopyright:

Verfügbare Formate

METU-EEE

EE 314-Digital Electronics Laboratory

5. ELEMENTARY GATE NETWORKS

I. INTRODUCTION 1. Objectives In this experiment, some of commonly used gate networks, such as multiplexers, comparators, and code converters are investigated using discrete components and XILINX software. 2. Background a. Multiplexers Digital multiplexers are combinational (non-memory) devices controlled by a selector which routes one of many input signals to the output. They can be considered as electronic equivalents of multiposition switches. Figure 5-1 gives the block diagram of an m-input, n-bit multiplexer. INPUT SIGNALS I11 I12

. .

I1n

I 2 1 I2 2

. .

I2n

Im1 Im2 Imn

. .

SELECT SIGNALS

S1 S2

. .

SELECTOR NETWORK

Sk

. .

Z1

Z2 OUTPUTS

Zm

Figure 5-1. The block diagram of an m-input, n-bit multiplexer. M groups of signals, where each group consists of n signals, can be multiplexed by a sufficient number of select inputs. In an ideal case, k select inputs can control n=2k signals per group.

3-input 2-bit multiplexer

In this multiplexer, S is the select input, Ia(Ia1Ia2), Ib(Ib1Ib2), Ic(Ic1Ic2) are the input groups, and Za, Zb, Zc are the outputs. E is an enable (active low) signal. That is, when E=1, Za=Zb=Zc=0 independent of the input signals. When E=0, depending on the value of the select input S, Zi will be either Ii1 or Ii2 where i=a, b, c. Figure 4-2 gives the schematic view of 3-input 2-bit multiplexer.

Experiment 5

METU-EEE

EE 314-Digital Electronics Laboratory

Ia1 E

Ia2

Ib1

Ib2

Ic1

Ic2

S1

Za Zb Zc Figure 5-2. The schematic view of 3-input 2-bit multiplexer. b. Comparators Comparators are used to compare two n-bit numbers and give an output signal indicating that the first number is greater than, equal to, or less than the second number. Table 5-1 gives the truth table of a 2-bit comparator. Table 5-1. The truth table of a 2-bit comparator

A A1

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B A0

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

A<B B0

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

A=B Z2

1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

A>B Z3

0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0

B1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

Z1

0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0

c. Code converters There are coding systems other than the binary coding such as, excess-3 code, Gray code, etc. The Gray code has the property that any consecutive codes differ only by a single bit. Table 5-2 and Table 5-3 give the truth tables for two bit and four bit Gray codes respectively. Note the mirror image property (except for the most significant bit) of the Gray code.

Experiment 5 2

METU-EEE

EE 314-Digital Electronics Laboratory

Table 5-2. Truth table of 2-bit Gray code.

DECIMAL

0 1 2 3

G1

0 0 1 1

G0

0 1 1 0

Table 5-3. Truth table of 4-bit Gray code

BINARY DECIMAL

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

GRAY B0

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

B3

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B2

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

B1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

G3

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

G2

0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0

G1

0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0

G0

0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

II. PRELIMINARY WORK 1. Read sections 4.7 and 4.10 from Digital Design, by Mano. 2. Read the experiments 1, 3 & 4 to refresh your mind about the design entry, simulation and design downloading in XILINX program. Bring the manuals for these experiments. 3. It is known that the following circuit is an 8-bit multiplexer. What is F(Q1,Q2,S2)? Select signal: S2S1S0 Input: A7...A0

Experiment 5

METU-EEE

EE 314-Digital Electronics Laboratory

4. Design a 16 to 1 multiplexer with the minimum number of select signals, using only 4-input, 3-input, 2-input NAND gates and INVERTERS, keeping the usage of hierarchical design in mind. (to be implemented in XILINX) 5. Design a 16 to 1 multiplexer with the minimum number of select signals, using 74151 IC s and NAND gates. (to be implemented on protoboard) 6. By using the truth table of the comparator given in Table 1, design a minimized comparator circuit to compare two 4-bit numbers, i.e., it has two 4-bit inputs and 3 outputs. Note that at any time only one of the outputs can be at logic level 1. This design will be implemented in XILINX and you are not allowed to use any complex gates from the libraries. You can only use NAND, NOR, XOR, and Inverter gates in your design. 7. Design a binary to gray converter and a gray to binary converter, using the truth table given in Table 3. This design will be implemented on protoboard. You are allowed to use NAND, XOR, and INVERTERS only. III. EXPERIMENTAL WORK 1. Construct the circuit you designed in Part 5 of the preliminary work on protoboard and test it. 2. Read the IMPORTANT NOTE below before proceeding. Draw the circuit you designed in part 4 of the preliminary work in XILINX. Perform the simulation to show that the circuit operates as a 16 to 1 multiplexer. As a final step, download your design into the XILINX FPGA box and test it using the box to verify that it also works as in the simulations. 3. Draw the circuit you designed in part 6 of the preliminary work in XILINX. Perform the simulation to show that the circuit operates as a comparator. As a final step, download your design into the XILINX FPGA box and test it using the box to verify that it also works as in the simulations. 4. Construct the circuits you designed in part 7 of the preliminary work on protoboard. Test the circuits to show that they operate as Binary to Gray and Gray to Binary converters respectively.

IMPORTANT NOTE :

i. A 16 to 1 MUX needs 4 select inputs and 16 data inputs. Thus we need 20 switches. Fortunately we have 4x8=32 switches installed on the box. You should assign 4 of them to select signals and 16 of them to 16 data inputs. Since 16-bit MUX requires many gates and routings between them, it will be wise to design a 4-bit MUX firstly, and then design 16-bits MUX hierarchically. Wire naming is a very useful method for large designs. The idea is the following; every wire with the same name is just connected to each other. See the example below:

ii.

iii.

Experiment 5

METU-EEE

EE 314-Digital Electronics Laboratory

Figure 5-3 Wire naming All wires with the same name are connected to each other. In more detail, the output of the IBUF of input A is connected to the D0 input of M2_1 since those wires have the same name, A_BUF. Similarly, the wires with the names B_BUF are also connected to each other, and so on. Although wire naming is useful for large circuits, the designer should be careful about the fact that, any wire with the same name will be connected. In order to give a name to a wire, right click on the wire and rename it.

Experiment 5

METU-EEE

EE 314-Digital Electronics Laboratory

IC LIST FOR EXPERIMENT 5 74151 7410 7400 7404 7486 Two 8 to 1 multiplexers with active low enable (Figure 5-3) Three 3-input NAND gates Four 2-input NAND gates Five inverter gates Four 2-input XOR gates

ENABLE

7 E 4 3 2 1 D0 D1 D2 D3 D4 D5 D6 D7 9 A

16 VCC

8 GND

Data Inputs

15 14 13 12

7 4 L S 1 5 1

~Y

B 10

C 11

Select Inputs

~Y resembling the inverse of Y.

ENABLE E 1 0 0 0 0 0 0 0 0 SELECT A X 0 0 0 0 1 1 1 1 SELECT B X 0 0 1 1 0 0 1 1 SELECT C X 0 1 0 1 0 1 0 1 OUTPUT Y 0 D0 D1 D2 D3 D4 D5 D6 D7

Figure 5-4. The pin diagram and function table of IC type 74151 8 x 1 multiplexer

Experiment 5 6

METU-EEE

EE 314-Digital Electronics Laboratory

Figure 5-5. Digital Gates in IC Packages with Identification Numbers and Pin Assignments

Experiment 5

Das könnte Ihnen auch gefallen

- Barrier FunctionDokument8 SeitenBarrier Functionfatih_ealNoch keine Bewertungen

- Ai TheDokument4 SeitenAi Thefatih_ealNoch keine Bewertungen

- EE586 Syllabus Fall2015Dokument4 SeitenEE586 Syllabus Fall2015fatih_ealNoch keine Bewertungen

- Lecture 23Dokument16 SeitenLecture 23fatih_ealNoch keine Bewertungen

- EXP6Dokument10 SeitenEXP6fatih_ealNoch keine Bewertungen

- Basys 2 Reference ManualDokument12 SeitenBasys 2 Reference ManualAnonymous lidok7lDiNoch keine Bewertungen

- Mechlabreport1 120522114907 Phpapp01Dokument8 SeitenMechlabreport1 120522114907 Phpapp01fatih_ealNoch keine Bewertungen

- Using The TMS320C2000 DMC To Build Control Systems: Wiki ArticleDokument2 SeitenUsing The TMS320C2000 DMC To Build Control Systems: Wiki Articlefatih_ealNoch keine Bewertungen

- Space Invader: VHDL: Yuebing Jiang Andrea WrightDokument38 SeitenSpace Invader: VHDL: Yuebing Jiang Andrea WrightGafitas MoralesNoch keine Bewertungen

- MITRES 6 007S11 hw26 SolDokument12 SeitenMITRES 6 007S11 hw26 Solfatih_ealNoch keine Bewertungen

- Ee212 mt2 2008Dokument9 SeitenEe212 mt2 2008fatih_ealNoch keine Bewertungen

- bảng công thức toán họcDokument35 Seitenbảng công thức toán họcNguyen Tuan DanhNoch keine Bewertungen

- Exp 2Dokument22 SeitenExp 2fatih_ealNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5783)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Department of Information Science and Engineering Analog and Digital Electronics Lab Subject Code: 17Csl37 Lab ManualDokument73 SeitenDepartment of Information Science and Engineering Analog and Digital Electronics Lab Subject Code: 17Csl37 Lab ManualrmaffanNoch keine Bewertungen

- Schematic Checklist LAN8740 QFN Rev ADokument23 SeitenSchematic Checklist LAN8740 QFN Rev ABillGNoch keine Bewertungen

- Experiment 11: NPN BJT Common Emitter CharacteristicsDokument7 SeitenExperiment 11: NPN BJT Common Emitter CharacteristicsMalikAlrahabiNoch keine Bewertungen

- L-4rr-l/EEE Date: 25/09/2022Dokument50 SeitenL-4rr-l/EEE Date: 25/09/2022Nure Alam DipuNoch keine Bewertungen

- ECE Faculty Research Areas for Final Year ProjectsDokument2 SeitenECE Faculty Research Areas for Final Year ProjectsAbhayNoch keine Bewertungen

- Implementation of KHN Biquad Filter Using Differential Voltage Current Controlled ConveyorDokument4 SeitenImplementation of KHN Biquad Filter Using Differential Voltage Current Controlled ConveyorijsretNoch keine Bewertungen

- Dual Transistor Multivariate Circuit.Dokument3 SeitenDual Transistor Multivariate Circuit.sbpatel123Noch keine Bewertungen

- JNTUK VLSI Lab Manual for R16 ECE StudentsDokument86 SeitenJNTUK VLSI Lab Manual for R16 ECE StudentsparrotpanduNoch keine Bewertungen

- Prerequisite: Marks Teachers Signature With DateDokument3 SeitenPrerequisite: Marks Teachers Signature With DateYash BhangaleNoch keine Bewertungen

- Expression 1640XL PDFDokument13 SeitenExpression 1640XL PDFfefotroncitoNoch keine Bewertungen

- OP AMPS HughesDokument8 SeitenOP AMPS Hughesmarkos_mylonas4152Noch keine Bewertungen

- DatasheetDokument160 SeitenDatasheetsamsularief03Noch keine Bewertungen

- Precision Curvature-Compensated CMOS Bandgap ReferenceDokument10 SeitenPrecision Curvature-Compensated CMOS Bandgap ReferenceAnonymous TPVfFif6TONoch keine Bewertungen

- Digital Circuits - Shift Registers: Serial in Serial Out (SISO) Shift RegisterDokument7 SeitenDigital Circuits - Shift Registers: Serial in Serial Out (SISO) Shift RegisterTanmay HazraNoch keine Bewertungen

- Tutorial 4 PHY 340Dokument3 SeitenTutorial 4 PHY 340ammirulhafiz03Noch keine Bewertungen

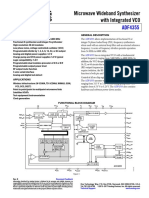

- Microwave Wideband Synthesizer With Integrated VCO: Data SheetDokument35 SeitenMicrowave Wideband Synthesizer With Integrated VCO: Data SheetBilles GatesNoch keine Bewertungen

- 4500W High Power Class-D Amplifier D4K5 - Electronic CircuitDokument4 Seiten4500W High Power Class-D Amplifier D4K5 - Electronic CircuitK Raja Sekar71% (7)

- Schematic Diagram: 7-1. Circuit DescriptionsDokument6 SeitenSchematic Diagram: 7-1. Circuit Descriptionsivo rodriguesNoch keine Bewertungen

- Power Amplifiers Chap22Dokument29 SeitenPower Amplifiers Chap22chandu3072002Noch keine Bewertungen

- Dpco Lab ManualDokument53 SeitenDpco Lab ManualBELMER GLADSON Asst. Prof. (CSE)Noch keine Bewertungen

- Aec 25 QuestionDokument3 SeitenAec 25 QuestionAvniNoch keine Bewertungen

- xl4016 DatasheetDokument10 Seitenxl4016 DatasheetEduardo Jose Torres HernandezNoch keine Bewertungen

- Two Port Networks - UploadDokument16 SeitenTwo Port Networks - UploadkarthikhrajvNoch keine Bewertungen

- Chapter 4 Combinational LogicDokument35 SeitenChapter 4 Combinational LogicHuda NaeemNoch keine Bewertungen

- Versatile In-Amp Signal Processing AmplifierDokument8 SeitenVersatile In-Amp Signal Processing AmplifierNima MoeenNoch keine Bewertungen

- Operational AmplifierDokument7 SeitenOperational Amplifiermothaffar ahmadNoch keine Bewertungen

- BCT Lecture5 6 Node AnalysisDokument36 SeitenBCT Lecture5 6 Node AnalysisShaleva SinghNoch keine Bewertungen

- A Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseDokument22 SeitenA Practical Clock Control Circuit Design & Example Tessent ATPG Test CaseSiva Sreeramdas100% (1)

- Com Par at orDokument7 SeitenCom Par at orసదాశివ మద్దిగిరిNoch keine Bewertungen

- Datasheet MC14013BCP (Dual Type D Flip Flop)Dokument9 SeitenDatasheet MC14013BCP (Dual Type D Flip Flop)vanmarteNoch keine Bewertungen