Beruflich Dokumente

Kultur Dokumente

74HC HCT597 CNV PDF

Hochgeladen von

Cesar VilledaOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

74HC HCT597 CNV PDF

Hochgeladen von

Cesar VilledaCopyright:

Verfügbare Formate

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications The IC06 74HC/HCT/HCU/HCMOS Logic Package Information The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT597 8-bit shift register with input flip-flops

Product specication File under Integrated Circuits, IC06 December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

FEATURES 8-bit parallel storage register inputs Shift register has direct overriding load and clear Output capability: standard ICC category: MSI GENERAL DESCRIPTION

74HC/HCT597

The 74HC/HCT597 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT597 consist each of an 8-bit storage register feeding a parallel-in, serial-out 8-bit shift register. Both the storage register and the shift register have positive edge-triggered clocks. The shift register also has direct load (from storage) and clear inputs.

QUICK REFERENCE DATA GND = 0 V; Tamb = 25 C; tr = tf = 6 ns TYPICAL SYMBOL tPHL/ tPLH PARAMETER propagation delay SHCP to Q STCP to Q PL to Q fmax CI CPD Notes 1. CPD is used to determine the dynamic power dissipation (PD in W): PD = CPD VCC2 fi + (CL VCC2 fo) where: fi = input frequency in MHz fo = output frequency in MHz (CL VCC2 fo) = sum of outputs CL = output load capacitance in pF VCC = supply voltage in V 2. For HC the condition is VI = GND to VCC For HCT the condition is VI = GND to VCC 1.5 V ORDERING INFORMATION See 74HC/HCT/HCU/HCMOS Logic Package Information. maximum clock frequency SHCP input capacitance power dissipation capacitance per package notes 1 and 2 CONDITIONS HC CL = 15 pF; VCC = 5 V 17 25 21 96 3.5 29 20 29 26 83 3.5 32 ns ns ns MHz pF pF HCT UNIT

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

PIN DESCRIPTION PIN NO. 8 9 10 11 12 13 14 15, 1, 2, 3, 4, 5, 6, 7 16 SYMBOL GND Q MR SHCP STCP PL DS D0 to D7 VCC NAME AND FUNCTION ground (0 V) serial data output asynchronous reset input (active LOW)

74HC/HCT597

shift clock input (LOW-to-HIGH, edge-triggered) storage clock input (LOW-to-HIGH, edge-triggered) parallel load input (active LOW) serial data input parallel data inputs positive supply voltage

Fig.1 Pin configuration.

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

74HC/HCT597

Fig.4 Functional diagram.

FUNCTION TABLE STCP no clock edge X X X Notes 1. H L X = HIGH voltage level = LOW voltage level = dont care = LOW-to-HIGH CP transition SHCP X X X X X PL X L L L H H MR X H H L L H FUNCTION data loaded to input latches data loaded from inputs to shift register data transferred from input ip-ops to shift register invalid logic, state of shift register indeterminate when signals removed shift register cleared shift register clocked Qn = Qn1, Q0 = DS

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

74HC/HCT597

Fig.5 Logic diagram.

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

74HC/HCT597

Fig.6 Timing diagram.

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

DC CHARACTERISTICS FOR 74HC For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications. Output capability: standard ICC category: MSI AC CHARACTERISTICS FOR 74HC GND = 0 V; tr = tf = 6 ns; CL = 50 pF Tamb (C) 74HC SYMBOL PARAMETER +25 40 to +85 40 to +125 max. 265 53 45 265 53 45 375 75 64 325 65 55 110 22 19 120 24 20 120 24 20 120 24 20 120 24 20 90 18 15 90 18 15 ns

74HC/HCT597

TEST CONDITIONS UNIT V WAVEFORMS CC (V) 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 Fig.7

min. typ. max. min. max. min. tPHL/ tPLH propagation delay SHCP to Q propagation delay MR to Q propagation delay STCP to Q propagation delay PL to Q output transition time 55 20 16 58 21 17 80 29 23 69 25 20 19 7 6 80 16 14 80 16 14 80 16 14 80 16 14 60 12 10 60 12 10 11 4 3 14 5 4 22 8 6 22 8 6 3 1 1 8 3 2 175 35 30 175 35 30 250 50 43 215 43 37 75 15 13 100 20 17 100 20 17 100 20 17 100 20 17 75 15 13 75 15 13 220 44 37 220 44 37 315 63 54 270 54 46 95 19 16

tPHL

ns

Fig.8

tPHL/ tPLH

ns

Fig.7

tPHL/ tPLH

ns

Fig.9

tTHL/ tTLH

ns

Fig.9

tW

STCP pulse width HIGH or LOW SHCP pulse width HIGH or LOW MR pulse width LOW PL pulse width LOW removal time MR to SHCP set-up time Dn to STCP

ns

Fig.7

tW

ns

Fig.7

tW

ns

Fig.8

tW

ns

Fig.9

trem

ns

Fig.10

tsu

ns

Fig.11

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

Tamb (C) 74HC SYMBOL PARAMETER +25 40 to +85 40 to +125 max. ns

74HC/HCT597

TEST CONDITIONS WAVEFORMS UNIT V CC (V) 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 2.0 4.5 6.0 Fig.11

min. typ. max. min. max. min. tsu set-up time DS to SHCP set-up time PL to SHCP hold time Dn to STCP hold time PL, DS to SHCP maximum pulse frequency SHCP 60 12 10 60 12 10 5 5 5 5 5 5 6.0 30 35 11 4 3 11 4 3 3 1 1 6 2 2 29 87 104 75 15 13 75 15 13 5 5 5 5 5 5 4.8 24 28 90 18 15 90 18 15 5 5 5 5 5 5 4.0 20 24

tsu

ns

Fig.12

th

ns

Fig.11

th

ns

Fig.11

fmax

MHz

Fig.7

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

DC CHARACTERISTICS FOR 74HCT For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications. Output capability: standard ICC category: MSI Note to HCT types

74HC/HCT597

The value of additional quiescent supply current (ICC) for a unit load of 1 is given in the family specifications. To determine ICC per input, multiply this value by the unit load coefficient shown in the table below.

INPUT DS Dn PL, MR STCP, SHCP

UNIT LOAD COEFFICIENT 0.25 0.30 1.50 1.50

December 1990

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

AC WAVEFORMS FOR 74HCT GND = 0 V; tr = tf = 6 ns; CL = 50 pF Tamb (C) 74HCT SYMBOL PARAMETER +25 40 to +85 40 to +125 max. 60 74 86 78 22 24 24 38 30 18 18 18 18 5 5 20 ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns

74HC/HCT597

TEST CONDITIONS UNIT V CC WAVEFORMS (V) 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 4.5 Fig.7 Fig.8 Fig.7 Fig.9 Fig.9 Fig.7 Fig.7 Fig.8 Fig.9 Fig.10 Fig.11 Fig.11 Fig.12 Fig.11 Fig.11 Fig.7

min. typ. max. min. max. min. tPHL/ tPLH tPHL tPHL/ tPLH tPHL/ tPLH tTHL/ tTLH tW tW tW tW trem tsu tsu tsu th th fmax propagation delay SHCP to Q propagation delay MR to Q propagation delay STCP to Q propagation delay PL to Q output transition time SHCP pulse width HIGH or LOW STCP pulse width HIGH or LOW MR pulse width LOW PL pulse width LOW removal time MR to SHCP set-up time Dn to STCP set-up time DS to SHCP set-up time PL to SHCP hold time Dn to STCP hold time PL, DS to SHCP maximum pulse frequency SHCP 16 16 25 20 12 12 12 12 5 5 30 23 28 33 30 7 7 6 14 10 2 5 2 4 1 2 75 40 49 57 52 15 20 20 31 25 15 15 15 15 5 5 24 50 61 71 65 19

MHz

December 1990

10

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

AC WAVEFORMS

74HC/HCT597

(1) HC : VM = 50%; VI = GND to VCC. HCT : VM = 1.3 V; VI = GND to 3 V.

(1) HC : VM = 50%; VI = GND to VCC. HCT : VM = 1.3 V; VI = GND to 3 V.

Fig.7

Waveforms showing the SHCP and STCP inputs to Q output propagation delays, the SHCP and STCP pulse widths and maximum clock pulse frequency.

Fig.8

Waveforms showing the MR input to Q output propagation delays and the MR pulse width.

(1) HC : VM = 50%; VI = GND to VCC. HCT : VM = 1.3 V; VI = GND to 3 V.

(1) HC : VM = 50%; VI = GND to VCC. HCT : VM = 1.3 V; VI = GND to 3 V.

Fig.9

Waveforms showing the PL input to Q output propagation delays, PL pulse width and output transition times.

Fig.10 Waveforms showing the MR input to SHCP, STCP removal times.

December 1990

11

Philips Semiconductors

Product specication

8-bit shift register with input ip-ops

74HC/HCT597

(1) HC : VM = 50%; VI = GND to VCC. HCT : VM = 1.3 V; VI = GND to 3 V.

(1) HC : VM = 50%; VI = GND to VCC. HCT : VM = 1.3 V; VI = GND to 3 V.

Fig.11 Waveforms showing hold and set-up times for DS, Dn inputs to SHCP, STCP inputs.

Fig.12 Waveforms showing set-up times for PL input to SHCP input.

PACKAGE OUTLINES See 74HC/HCT/HCU/HCMOS Logic Package Outlines.

December 1990

12

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Bigben01 e A4Dokument0 SeitenBigben01 e A4Marcelo TorresNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Neuschwanstein e A4Dokument9 SeitenNeuschwanstein e A4mariosergio05Noch keine Bewertungen

- Neuschwanstein e A4Dokument9 SeitenNeuschwanstein e A4mariosergio05Noch keine Bewertungen

- XBOX 360 Jtag and Modifying TutorialDokument31 SeitenXBOX 360 Jtag and Modifying TutorialNumair Imran100% (2)

- Bol ModelDokument15 SeitenBol ModelSuresh BabuNoch keine Bewertungen

- Cheap Xbox 360 S Trinity RGH Using An LPT Port and X360Ace - William QuadeDokument28 SeitenCheap Xbox 360 S Trinity RGH Using An LPT Port and X360Ace - William QuadeAnderson BucchianicoNoch keine Bewertungen

- Chemical Dosing I/o ListDokument3 SeitenChemical Dosing I/o Listpriyo_a_sNoch keine Bewertungen

- Oec 9600imaging Workstation Illustrated Parts ManualDokument95 SeitenOec 9600imaging Workstation Illustrated Parts ManualJoe B BestialNoch keine Bewertungen

- Mazak Fusion 640 Series How To Create A Backup Using RS232Dokument5 SeitenMazak Fusion 640 Series How To Create A Backup Using RS232sunhuynh100% (2)

- Microprocessors and Microcontrollers: Sunil Mathur Jeebananda PandaDokument16 SeitenMicroprocessors and Microcontrollers: Sunil Mathur Jeebananda Pandadinesh patnaikNoch keine Bewertungen

- Kubernetes Full INSAT's CourseDokument55 SeitenKubernetes Full INSAT's CourseHAMDI GDHAMINoch keine Bewertungen

- HYNIX DDR5 Module - New Part Number Decoder - r.2.1 - Sep 2021Dokument5 SeitenHYNIX DDR5 Module - New Part Number Decoder - r.2.1 - Sep 2021Aleksandr Nevedrov100% (1)

- Cisco ACI Initial Deployment Cookbook 1Dokument213 SeitenCisco ACI Initial Deployment Cookbook 1scribdmax404Noch keine Bewertungen

- Guide For I2C OLED Display With Arduino - Random Nerd TutorialsDokument99 SeitenGuide For I2C OLED Display With Arduino - Random Nerd TutorialsNick Karaiskos100% (1)

- Pic16f 2 PDFDokument124 SeitenPic16f 2 PDFCesar VilledaNoch keine Bewertungen

- BC548 - Datashet PDFDokument2 SeitenBC548 - Datashet PDFBraian KonzgenNoch keine Bewertungen

- Compuertas Logicas or ChipDokument3 SeitenCompuertas Logicas or ChipCesar VilledaNoch keine Bewertungen

- Led InfrarrojoDokument7 SeitenLed InfrarrojoPatrick SteinerNoch keine Bewertungen

- Ups Apc BR900GIDokument1 SeiteUps Apc BR900GICesar VilledaNoch keine Bewertungen

- PT1302B C2Dokument7 SeitenPT1302B C2G Ivan Torres RNoch keine Bewertungen

- 16 F 716Dokument136 Seiten16 F 716Andreyna Emilia Guevara GalindezNoch keine Bewertungen

- 3D Paper Heart: HEART BOX © Minieco - Co.uk. To Be Used For Non-Commercial Purposes Only. Do Not Link Directly To PDFDokument1 Seite3D Paper Heart: HEART BOX © Minieco - Co.uk. To Be Used For Non-Commercial Purposes Only. Do Not Link Directly To PDFCesar VilledaNoch keine Bewertungen

- Standing PentagramDokument5 SeitenStanding PentagramCesar VilledaNoch keine Bewertungen

- Asymetric Square PyramidDokument5 SeitenAsymetric Square PyramidCesar VilledaNoch keine Bewertungen

- Tecaldo Inalambico 6139Dokument2 SeitenTecaldo Inalambico 6139Cesar VilledaNoch keine Bewertungen

- Lampara de HalloweenDokument1 SeiteLampara de HalloweenCesar VilledaNoch keine Bewertungen

- BC548 - Datashet PDFDokument2 SeitenBC548 - Datashet PDFBraian KonzgenNoch keine Bewertungen

- Paper Star Lantern TemplatesDokument3 SeitenPaper Star Lantern TemplatesGrace ImanuelNoch keine Bewertungen

- Tecaldo Inalambico 6139Dokument2 SeitenTecaldo Inalambico 6139Cesar VilledaNoch keine Bewertungen

- PT1302B C2Dokument7 SeitenPT1302B C2G Ivan Torres RNoch keine Bewertungen

- Arduino RGB LedDokument1 SeiteArduino RGB LedBigHeadLittleFeetNoch keine Bewertungen

- BC548 - Datashet PDFDokument2 SeitenBC548 - Datashet PDFBraian KonzgenNoch keine Bewertungen

- Led InfrarrojoDokument7 SeitenLed InfrarrojoPatrick SteinerNoch keine Bewertungen

- Led InfrarrojoDokument7 SeitenLed InfrarrojoPatrick SteinerNoch keine Bewertungen

- SMP4 RGB PDFDokument5 SeitenSMP4 RGB PDFCesar VilledaNoch keine Bewertungen

- Whitepaper EN c6906 Xperia z1 2 PDFDokument25 SeitenWhitepaper EN c6906 Xperia z1 2 PDFCesar VilledaNoch keine Bewertungen

- BC1602B2 Flyer PDFDokument1 SeiteBC1602B2 Flyer PDFCesar VilledaNoch keine Bewertungen

- Abc Del RGBDokument5 SeitenAbc Del RGBCesar VilledaNoch keine Bewertungen

- Opti RGB PDFDokument6 SeitenOpti RGB PDFCesar VilledaNoch keine Bewertungen

- Disco Duro ST380011ADokument54 SeitenDisco Duro ST380011ARaul Carlos Ramirez AguirreNoch keine Bewertungen

- Atf22v10cqz PDFDokument19 SeitenAtf22v10cqz PDFCesar VilledaNoch keine Bewertungen

- Printers Quotations: HP Laserjet P4015N Price 13500Dokument3 SeitenPrinters Quotations: HP Laserjet P4015N Price 13500Mohsin Warriach0% (1)

- Network OrchestrationDokument2 SeitenNetwork OrchestrationMo ElNoch keine Bewertungen

- In Gaming NBDokument11 SeitenIn Gaming NBKaushik BorahNoch keine Bewertungen

- Chapter 11Dokument43 SeitenChapter 11Anonymous 3BpcKiFBUNoch keine Bewertungen

- Demantra Installation Guide For Release 7314 August21 2012Dokument120 SeitenDemantra Installation Guide For Release 7314 August21 2012infyrajayaarNoch keine Bewertungen

- Setstate Tutorial ReactDokument8 SeitenSetstate Tutorial ReactDhanushNoch keine Bewertungen

- Maasai Mara University: Answer Question ONE and Any Other TWODokument3 SeitenMaasai Mara University: Answer Question ONE and Any Other TWOAlbert OmondiNoch keine Bewertungen

- Microsoft System Center Orchestrator 2012 R2 Essentials - Sample ChapterDokument33 SeitenMicrosoft System Center Orchestrator 2012 R2 Essentials - Sample ChapterPackt PublishingNoch keine Bewertungen

- Unit 2 Clock-Driven Scheduling: 5.1 Notations and AssumptionsDokument18 SeitenUnit 2 Clock-Driven Scheduling: 5.1 Notations and Assumptions一鸿Noch keine Bewertungen

- Lecture 6 (Strings in Java)Dokument33 SeitenLecture 6 (Strings in Java)Deepak DewaniNoch keine Bewertungen

- Understanding Time Delay Relay FunctionsDokument6 SeitenUnderstanding Time Delay Relay FunctionsAndrew BullNoch keine Bewertungen

- FC255Dokument6 SeitenFC255GOKUL GNoch keine Bewertungen

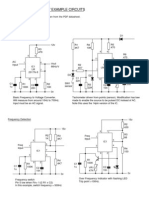

- LM2917 ExamplesDokument1 SeiteLM2917 ExamplesSergio RamosNoch keine Bewertungen

- INF 208 Programming - Java: File ProcessingDokument23 SeitenINF 208 Programming - Java: File ProcessingAshiru kattoNoch keine Bewertungen

- Emc Symmetrix Veritas DMP WP LDV PDFDokument7 SeitenEmc Symmetrix Veritas DMP WP LDV PDFManoj AntonyNoch keine Bewertungen

- Sample Project On Telephone DiaryDokument29 SeitenSample Project On Telephone DiaryVinod GandhiNoch keine Bewertungen

- Introduction To FORTRANDokument30 SeitenIntroduction To FORTRANWisdom OjimahNoch keine Bewertungen

- 03 - Exceptional HandlingDokument41 Seiten03 - Exceptional HandlingRahulNoch keine Bewertungen