Beruflich Dokumente

Kultur Dokumente

Part 1

Hochgeladen von

bmbsnpOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Part 1

Hochgeladen von

bmbsnpCopyright:

Verfügbare Formate

INTRODUCING VHDL

1.1 Introduction

The VHSIC Hardware Description Language is an industry standard language used to describe hardware from the abstract to the concrete level. VHDL resulted from work done in the '70s and early '80s by the U.S. Department of Defense. VHDL usage has risen rapidly since its inception and Is used by literally tens of thousands of engineers around the globe to create sophisticated electronic products, This chapter will start the process of easing the reader into the complexities of VHDL. VHDL is a powerful language with numerous language constructs that are capable of describing, very complex behavior. Learning all the features of VHDL is not a simple task. In 1986, VHDL was proposed as an IEEEstandard. It went through a number of revisions and changes until it was adopted as the IEEE 1076 standard in December 1987, Then VHDL 1076-1993 and the latest VHDL 1076-2002. All the examples have been described in IEEE 1076 VHDL.

1.2 Levels of representation

There are two levels of representation, which are supported by VHDL: 1-Behavioral level: this describes system in terms of what it does (or how it behaves). 2-Structural level: this describes a system as a collection of gates and components Figure 1.1 shows the two levels of representation.

Figure 1.1 Levels of representation

1.3 Structure of a VHDL file

To create a VHDL file the following steps are necessary: 1.3.1 Design Entity Figure 1.2 shows that Entity Declaration is considered as the interface to the outside world, which defines the input and output signals as well as the Architecture contains the description of the entity and is composed of interconnected entities, processes and components.

The code of the entity declaration Syntax: Entity NAME_OF _ENTITY is Port (signal names: mode type; signal names: mode type; . . signal names: mode type); End NAME_OF_ENTITY; Mode: is one of the reserved words to indicate the signal direction (in - out - buffer - inout). Type: a built-in or user-defined signal type. ( bit, bit_vector, Boolean, character, std_logic, integer ... ) The following example explain the declaration of a D flip-flop with set and reset inputs

Entity D_flip is Port (D, CLK, S, R : in std_logic; Q, Qnot : out std_logic); End D_flip; 1.3.2 Architecture Body An entity or circuit can be specified in a variety of ways, such as behavioral, structural, or a combination of both. The architecture body looks as follows: Architecture architecture_name of NAME_OF_ENTITY is -- Declarations -- Components declarations -- Signal declarations -- Constant declarations -- Type declarations . . Begin -- Statements . . End architecture_name; 1.3.3 Library & Packages A library can be considered as a place where the compiler stores information about a design project, and a VHDL package is a file or module that contains declarations of commonly used objects, data type, component declarations, signal, procedures and functions. To specify the library and package, use the "library" and the "Use" keywords. For example to include the std_logic_1164 package that exists in the library IEEE library IEEE; Use IEEE.std_logic_1164.all; The .all extension indicates to use the entire ieee.std_logic_1164 package.

Das könnte Ihnen auch gefallen

- Banking AwarenessDokument41 SeitenBanking AwarenessApeksha Rajoriya100% (1)

- Static G.K. Tornado AVIKDokument45 SeitenStatic G.K. Tornado AVIKdassreerenjiniNoch keine Bewertungen

- One WordDokument15 SeitenOne WordVamshi KrishnaNoch keine Bewertungen

- Introduction To Accounting: ContentsDokument251 SeitenIntroduction To Accounting: ContentsJaya Bala ChandranNoch keine Bewertungen

- Bank Not of UK, Telangana Charitra, Telangana Coins, Telangana Language, Indian Banknote, Musham Damodhar, Banknotes Auction, Ancient Coins Auction, Bank of Bengal Half Notes AuctionDokument16 SeitenBank Not of UK, Telangana Charitra, Telangana Coins, Telangana Language, Indian Banknote, Musham Damodhar, Banknotes Auction, Ancient Coins Auction, Bank of Bengal Half Notes Auctionmusham9Noch keine Bewertungen

- Platinum Points For IBPS clerk-IV PDFDokument22 SeitenPlatinum Points For IBPS clerk-IV PDFAniruddha SahasrabuddheNoch keine Bewertungen

- Sbi Assistant Clerk Notification 2014Dokument5 SeitenSbi Assistant Clerk Notification 2014Telugu VaahiniNoch keine Bewertungen

- Bank NotesDokument68 SeitenBank NotesbmbsnpNoch keine Bewertungen

- Banking TerminologyDokument8 SeitenBanking TerminologybmbsnpNoch keine Bewertungen

- Sbi ADokument5 SeitenSbi AJeshiNoch keine Bewertungen

- Interview TipsDokument11 SeitenInterview TipsIkshvaku KansaraNoch keine Bewertungen

- Cenpeid Leaflet 1Dokument4 SeitenCenpeid Leaflet 1bmbsnpNoch keine Bewertungen

- Sbi Assistant Clerk Notification 2014Dokument5 SeitenSbi Assistant Clerk Notification 2014Telugu VaahiniNoch keine Bewertungen

- 1.4.1.2 Concurrent StatementsDokument3 Seiten1.4.1.2 Concurrent StatementsbmbsnpNoch keine Bewertungen

- Introduction To Electrical Drives: Figure 1 Conventional Variable Speed Electrical Drive SystemDokument19 SeitenIntroduction To Electrical Drives: Figure 1 Conventional Variable Speed Electrical Drive SystemChakradhara TheppavariNoch keine Bewertungen

- Syllabus CWCDokument5 SeitenSyllabus CWCDowlath BashaNoch keine Bewertungen

- Part 6Dokument5 SeitenPart 6bmbsnpNoch keine Bewertungen

- III. Fast Fourier Transform: Digital Signal Processing - 3Dokument17 SeitenIII. Fast Fourier Transform: Digital Signal Processing - 3Sathish BalaNoch keine Bewertungen

- JK Lecture Notes On Electric Power SystemsDokument80 SeitenJK Lecture Notes On Electric Power Systemstabibujuha84100% (6)

- VHDL NotesDokument14 SeitenVHDL Notesumang_1010100% (2)

- Part 2Dokument4 SeitenPart 2bmbsnpNoch keine Bewertungen

- Binomial Formulas: Definition of Factorial NumbersDokument2 SeitenBinomial Formulas: Definition of Factorial NumbersbmbsnpNoch keine Bewertungen

- 2.1 Combinational Circuit Desion ExampleDokument2 Seiten2.1 Combinational Circuit Desion ExamplebmbsnpNoch keine Bewertungen

- Part 4Dokument5 SeitenPart 4bmbsnpNoch keine Bewertungen

- Coordinate GeometryDokument78 SeitenCoordinate Geometrybmbsnp100% (1)

- Wall MartDokument22 SeitenWall MartbmbsnpNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- VHDL Bram BromDokument9 SeitenVHDL Bram BromGmit MandyaNoch keine Bewertungen

- Good VLSI Design Test Power TutorialDokument1.515 SeitenGood VLSI Design Test Power TutorialprakashthamankarNoch keine Bewertungen

- Experiment No 3Dokument20 SeitenExperiment No 3Ako C SeanNoch keine Bewertungen

- Christian Dufour 2008Dokument7 SeitenChristian Dufour 2008oualid zouggarNoch keine Bewertungen

- VLSI &embedded SystemsDokument38 SeitenVLSI &embedded SystemsOLLURI ROHITNoch keine Bewertungen

- Midterm PDFDokument2 SeitenMidterm PDFObada Ar-ruzziNoch keine Bewertungen

- P2a EntityDokument19 SeitenP2a EntitykslmohanNoch keine Bewertungen

- pg119 C AccumDokument24 Seitenpg119 C Accumfarrokh razaviNoch keine Bewertungen

- Simple Image Processing in VHDLDokument5 SeitenSimple Image Processing in VHDLGaihre KrishnaNoch keine Bewertungen

- Project Report VHDLDokument68 SeitenProject Report VHDLricha_shukla_40Noch keine Bewertungen

- 8.1 Mux 1Dokument6 Seiten8.1 Mux 1Maddy Trichy50% (2)

- To Be Replaced by Standard Cover : DMA Controller For AMBA Bus IP CoreDokument32 SeitenTo Be Replaced by Standard Cover : DMA Controller For AMBA Bus IP CorePronadeep BoraNoch keine Bewertungen

- Lab Session 3 DescriptionDokument6 SeitenLab Session 3 DescriptionUmer huzaifaNoch keine Bewertungen

- Design and Implementation of Ofdm Transmitter and Receiver On Fpga HardwareDokument153 SeitenDesign and Implementation of Ofdm Transmitter and Receiver On Fpga Hardwaredhan_7100% (11)

- Multiplexers in VHDL: Four-Bit Wide 2 To 1 MultiplexerDokument4 SeitenMultiplexers in VHDL: Four-Bit Wide 2 To 1 Multiplexeranon_818776315Noch keine Bewertungen

- מדריך modelsim למתחיליםDokument22 Seitenמדריך modelsim למתחיליםRonNoch keine Bewertungen

- VLSI BookDokument6 SeitenVLSI BookVinod JagdaleNoch keine Bewertungen

- VHDL For Programmable Logic Aug95 PDFDokument404 SeitenVHDL For Programmable Logic Aug95 PDFkurukuruddinpuruNoch keine Bewertungen

- 1.logic Gates: OR GateDokument70 Seiten1.logic Gates: OR GateDinesh SharmaNoch keine Bewertungen

- Alu 32 BitDokument6 SeitenAlu 32 Bitsachin_bhingareNoch keine Bewertungen

- Ise Tutorial Using Xilinx Chipscope Pro Ila Core With Project Navigator To Debug Fpga ApplicationsDokument34 SeitenIse Tutorial Using Xilinx Chipscope Pro Ila Core With Project Navigator To Debug Fpga ApplicationsMarcos Guerra MedinaNoch keine Bewertungen

- ITCE362: Computer Architecture Experiment No. 2 Register File DesignDokument9 SeitenITCE362: Computer Architecture Experiment No. 2 Register File DesignHALIMANoch keine Bewertungen

- Vlsi Lab Manual-Microwind PDFDokument54 SeitenVlsi Lab Manual-Microwind PDFyayavaramNoch keine Bewertungen

- Beginning FPGA Programming - Partie58Dokument5 SeitenBeginning FPGA Programming - Partie58ali alilouNoch keine Bewertungen

- Debussy 0407Dokument117 SeitenDebussy 0407ravikumar@sssNoch keine Bewertungen

- Tutorial Active HDLDokument19 SeitenTutorial Active HDLMEBM80Noch keine Bewertungen

- VHDL Code For A 74LS194 Universal Shift RegisterDokument3 SeitenVHDL Code For A 74LS194 Universal Shift RegisterMario Andres0% (1)

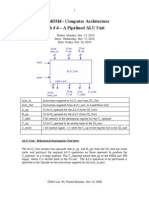

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitDokument8 SeitenECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilNoch keine Bewertungen

- FSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017Dokument25 SeitenFSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017antoniocljNoch keine Bewertungen

- DFT AcronymsDokument4 SeitenDFT Acronymspravallika vysyarajuNoch keine Bewertungen