Beruflich Dokumente

Kultur Dokumente

MSP430 Microcontroller Basics Chapter 8.1

Hochgeladen von

Jag JagCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

MSP430 Microcontroller Basics Chapter 8.1

Hochgeladen von

Jag JagCopyright:

Verfügbare Formate

276

Chapter 8

modulation. Against this, it lacks a feature of sampling inputs in Timer_A that is useful in communication. The simplest way to generating a delay is to use a software loop as in the section Automatic Control Flashing Light by Software Delay on page 91. This should be avoided wherever possible in favor of one of the hardware timers because the timers are more precise and leave the CPU free for more productive activities. Alternatively, the device can be put into a low-power mode if there is nothing else to be done. We already saw that the MSP430 spends much of its time asleep in many applications and is awakened periodically by a timer.

8.1

Watchdog Timer

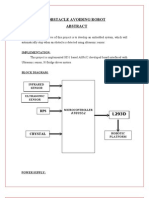

The main purpose of the watchdog timer is to protect the system against failure of the software, such as the program becoming trapped in an unintended, innite loop. Left to itself, the watchdog counts up and resets the MSP430 when it reaches its limit. The code must therefore keep clearing the counter before the limit is reached to prevent a reset. The operation of the watchdog is controlled by the 16-bit register WDTCTL. It is guarded against accidental writes by requiring the password WDTPW = 0x5A in the upper byte. A reset will occur if a value with an incorrect password is written to WDTCTL. This can be done deliberately if you need to reset the chip from software. Reading WDTCTL returns 0x69 in the upper byte, so reading WDTCTL and writing the value back violates the password and causes a reset. The lower byte of WDTCTL contains the bits that control the operation of the watchdog timer, shown in Figure 8.1. The RST/NMI pin is also congured using this register, which you must not forget when servicing the watchdogwe see why shortly. This pin is described in the section Nonmaskable Interrupts on page 195. Most bits are reset to 0 after a power-on reset (POR) but are unaffected by a power-up clear (PUC). This distinction is important in handling resets caused by the watchdog. The exception is the

7 WDTHOLD rw(0)

6 WDTNMIES rw(0)

5 WDTNMI rw(0)

4 WDTTMSEL rw(0)

3 WDTCNTCL r0(w)

2 WDTSSEL rw(0)

1 WDTISx rw(0)

rw(0)

Figure 8.1: The lower byte of the watchdog timer control register WDTCTL.

www.newnespress.com

Timers

277

WDTCNTCL bit, labeled r0(w). This means that the bit always reads as 0 but a 1 can be written to stimulate some action, clearing the counter in this case. The watchdog counter is a 16-bit register WDTCNT, which is not visible to the user. It is clocked from either SMCLK (default) or ACLK, according to the WDTSSEL bit. The reset output can be selected from bits 6, 9, 13, or 15 of the counter. Thus the period is 26 = 64, 512, 8192, or 32,768 (default) times the period of the clock. This is controlled by the WDTISx bits in WDTCTL. The intervals are roughly 2, 16, 250, and 1000 ms if the watchdog runs from ACLK at 32 KHz. The watchdog is always active after the MSP430 has been reset. By default the clock is SMCLK, which is in turn derived from the DCO at about 1 MHz. The default period of the watchdog is the maximum value of 32,768 counts, which is therefore around 32 ms. You must clear, stop, or recongure the watchdog before this time has elapsed. In almost all programs in this book, I take the simplest approach of stopping the watchdog, which means setting the WDTHOLD bit. This goes back to the rst program to light LEDs, Listing 4.2. If the watchdog is left running, the counter must be repeatedly cleared to prevent it counting up as far as its limit. This is done by setting the WDTCNTCL bit in WDTCTL. The task is often called petting, feeding, or kicking the dog, depending on your attitude toward canines. The bit automatically clears again after WDTCNT has been reset. The MSP430 is reset if the watchdog counter reaches its limit. Recall from the section Resets on page 157 that there are two levels of reset. The watchdog causes a power-up clear, which is the less drastic form. Most registers are reset to default values but some retain their contents, which is vital so that the source of the reset can be determined. The watchdog timer sets the WDTIFG ag in the special function register IFG1. This is cleared by a power-on reset but its value is preserved during a PUC. Thus a program can check this bit to nd out whether a reset arose from the watchdog. Listing 8.1 shows a trivial program to demonstrate the watchdog. I selected the clock from ACLK (WDTSSEL = 1) and the longest period (WDTISx = 00), which gives 1s with a 32 KHz crystal for ACLK. It is wise to restart any timer whenever its conguration is changed so I also cleared the counter by setting the WDTCNTCL bit. LED1 shows the state of button B1 and LED2 shows WDTIFG. The watchdog is serviced by rewriting the conguration value in a loop while button B1 is held down. If the button is left up for more than 1s the watchdog times out, raises the ag WDTIFG, and resets the device with a PUC. This is shown by LED2 lighting.

www.newnespress.com

278

Chapter 8

Listing 8.1: Program wdtest1.c to demonstrate the watchdog timer.

// wdtest1 . c - trival program to demonstrate watchdog timer // Olimex 1121 STK board , 32 KHz ACLK // J H Davies , 2007 -05 -10; IAR Kickstart version 3.42 A // - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - # include < io430x11x1 .h > // Specific device // - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - // Pins for LEDs and button # define LED1 P2OUT_bit . P2OUT_3 # define LED2 P2OUT_bit . P2OUT_4 # define B1 P2IN_bit . P2IN_1 // Watchdog config : active , ACLK /32768 -> 1 s interval ; clear counter # define WDTCONFIG ( WDTCNTCL | WDTSSEL ) // Include settings for _RST / NMI pin here as well // - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - void main ( void ) { WDTCTL = WDTPW | WDTCONFIG ; // Configure and clear watchdog P2DIR = BIT3 | BIT4 ; // Set pins with LEDs to output P2OUT = BIT3 | BIT4 ; // LEDs off ( active low ) for (;;) { // Loop forever LED2 = IFG1_bit . WDTIFG ; // LED2 shows state of WDTIFG if ( B1 == 1) { // Button up LED1 = 1; // LED1 off } else { // Button down WDTCTL = WDTPW | WDTCONFIG ; // Feed / pet / kick / clear watchdog LED1 = 0; // LED1 on } } }

I have to admit with embarrassment that this program gave me a little trouble. In my rst version I serviced the watchdog with the following line of C. The obvious idea was to clear the counter and leave everything else as it was:

WDTCTL = WDTPW | WDTCNTCL ; // Feed / pet / kick / clear watchdog

In my defense, this is given as an example in the family users guide. Distressingly, the MSP430 seemed to reset as soon as the button was released, even if this was less than 1s after the power was applied. The reason is that this line overwrites the complete register and clears all the bits other than WDTCNTCL. In particular, the clock reverts to SMCLK, which reduces the period to 32 ms instead of 1s. It also wipes out the settings for the RST/NMI pin if I changed them. The correct approach is to rewrite the complete conguration to WDTCTL as in the listing. Do not try to set only the WDTCNTCL bit either, as follows:

WDTCTL_bit . WDTCNTCL = 1; // Crashes

www.newnespress.com

Timers

279

This causes a reset because it violates the password protection. Maybe the watchdog is not quite so simple after all. Example 8.1 Experiment with Listing 8.1, which you may need to adapt to your hardware. You might wish to try some of the stupid mistakes tooit is a good way of remembering them. You should nd that LED2 remains lit permanently after a PUC because the WDTIFG bit needs to be cleared in software and I deliberately omitted this. It is cleared only after a POR, which can be requested by the Reset command in the debugger. Listing 8.2 shows a traditional example of how the watchdog is used to protect a program built around a paced loop. The general idea was explained in the section Returning from a Low-Power Mode to the Main Function on page 203. A timer is congured to generate interrupts every 10 ms. Its interrupt service routine restores active mode, which causes the program to resume the main loop. This services the watchdog before carrying out its tasks. Both the watchdog and the other timer run from ACLK and therefore continue to operate in low-power mode 3. Listing 8.2: Outline of a traditional paced loop protected by the watchdog.

// Configure a timer for interrupts every 10 ms and return to active mode // Configure watchdog for 16 ms period from 32\ , KHz ACLK # define WDTCONFIG ( WDTCNTCL | WDTSSEL | WDTIS1 ) WDTCTL = WDTPW | WDTCONFIG ; // Configure and clear watchdog for (;;) { _ _ l o w _ p o w e r _ m o d e _ 3 (); // Enter low power mode LPM3 // Wait here , pace loop until timer expires and ISR restores Active Mode WDTCTL = WDTPW | WDTCONFIG ; // Service watchdog // Tasks of paced loop }

What should we choose for the period of the watchdog? Clearly it should be greater than 10 ms. I chose the next period up, 16 ms, which is given by selecting ACLK with a period of 512 and setting WDTISx = 10. This may be a bit short. It does not matter too much if one pass through the paced loop is slower than 10 ms provided that the next is shorter, so that the program never lags by more than 10 ms and misses an interrupt. Unfortunately the next interval up is 250 ms, which is too long. It is important that the watchdog is serviced from the highest level of the program. This should never be done in an interrupt service routine. In this example it would be tempting to reset the watchdog in the ISR for the timer but this would lose a great deal of protection.

www.newnespress.com

280

Chapter 8

Suppose that the program became stuck in one of the tasks of the paced loop. Interrupts would still be generated periodically and the watchdog would continue to be serviced correctly if this were done in the ISR. On the other hand, the watchdog would expire and cause a reset with the structure in Listing 8.2. It is possible that the watchdog may time out during the initialization of a program, which is carried out by the startup code before the users main() function is called. This would happen if it took longer than 32 ms to initialize the RAM, which is possible if a large number of global or static variables are used. In EW430 you can supply a function _ _low_level_init(), which is called before the RAM is initialized. The watchdog can be stopped or recongured here. Watchdogs vary considerably from one type of microcontroller to another. Some have a set of passwords that must be used in a prescribed order, rather than a single value; a reset occurs if a password is used out of sequence. Windowed watchdogs must be serviced only during a particular part of their period, such as the last quarter; clearing the watchdog earlier than this causes a reset. Some have their own built-in oscillator, which protects them from failure of the main clocks. Many watchdogs are controlled by write-once registers, which means that their conguration cannot be changed after an initial value has been written. This would be a problem in the MSP430, where the watchdog may need to be recongured for low-power modes. The reset caused by the watchdog can be a nuisance during development because a PUC destroys much of the evidence that could help you to detect a problem that caused the watchdog to time out. A solution might be to generate an interrupt rather than a reset by using the watchdog as an interval timer, which is described shortly. The interrupt service routine could copy critical data to somewhere safe, signal a problem by lighting an LED, or simply cause execution to stop on a breakpoint. Nagy [4] has further suggestions.

8.1.1

Failsafe Clock Source for Watchdog Timer+

Newer devices, including the MSP430F2xx family and recent members of the MSP430x4xx, have the enhanced watchdog timer+ (WDT+). This includes fail-safe logic to preserve the watchdogs clock. Suppose that the watchdog is congured to use ACLK and the program enters low-power mode 4 to wait for an external interrupt, as in Listing 7.1. The old watchdog (WDT) stops during LPM4 and resumes counting when the device is awakened. In contrast, WDT+ does not let the device enter LPM4 because that would disable its clock. Therefore it is not possible to use LPM4 with WDT+ active; the

www.newnespress.com

Timers

281

watchdog must rst be stopped by setting WDTHOLD. Similarly, it is not possible to use LPM3 if WDT+ is active and gets its clock from SMCLK. If its clock fails, WDT+ switches from ACLK or SMCLK to MCLK and takes this from the DCO if an external crystal fails. The watchdog interval may change dramatically but there must be serious problems elsewhere if this happens.

8.1.2

Watchdog as an Interval Timer

The watchdog can be used as an interval timer if its protective function is not desired. Set the WDTTMSEL bit in WDTCTL for interval timer mode. The periods are the same as before and again WDTIFG is set when the timer reaches its limit, but no reset occurs. The counter rolls over and restarts from 0. An interrupt is requested if the WDTIE bit in the special function register IE1 is set. This interrupt is maskable and as usual takes effect only if GIE is also set. The watchdog timer has its own interrupt vector, which is fairly high in priority but not at the top. It is not the same as the reset vector, which is taken if the counter times out in watchdog mode. The WDTIFG ag is automatically cleared when the interrupt is serviced. It can be polled if interrupts are not used. Many applications need a periodic tick, for which the watchdog timer could be used in interval mode. The disadvantage is the limited selection of periods, but 1s is convenient for a clock. Some of the previous examples that used Timer_A could be rewritten for the watchdog instead and its use is illustrated in the standard sets of code examples from TI. Example 8.2 Rewrite the simple clock in Listing 7.4 to use the watchdog as a 1s interval timer instead of Timer_A.

ChecklistHave You . . .

Stopped the watchdog or ensured that it is serviced frequently enough? Set the WDTIE bit in the special function register IE1 if you want interrupts? (It is easy to forget this because it is not in WDTCTL.)

8.2

Basic Timer1

Basic Timer1 is present in all MSP430xF4xx devices and is perhaps the most straightforward module in the MSP430, as you might guess from its name. It provides the clock

www.newnespress.com

Das könnte Ihnen auch gefallen

- Volvo A30e2 PDFDokument28 SeitenVolvo A30e2 PDFsafdey100% (1)

- Mandt Certificate 2019Dokument1 SeiteMandt Certificate 2019api-283422107Noch keine Bewertungen

- Embedded SW Development With ECosDokument35 SeitenEmbedded SW Development With ECosRakesh MenonNoch keine Bewertungen

- Obstacle RobotDokument58 SeitenObstacle Robotvenu_10462834100% (1)

- Mathcad ReferenceDokument2 SeitenMathcad Referencejerezg25Noch keine Bewertungen

- Foundation Course for Advanced Computer StudiesVon EverandFoundation Course for Advanced Computer StudiesNoch keine Bewertungen

- Intel Recommended Reading List 1H14 0Dokument10 SeitenIntel Recommended Reading List 1H14 0Mahmoud EladawiNoch keine Bewertungen

- Somatic Psychology Linda Hartley Review PDFDokument8 SeitenSomatic Psychology Linda Hartley Review PDFAndres SanabriaNoch keine Bewertungen

- Fitness RX For Women - April 2014Dokument116 SeitenFitness RX For Women - April 2014Ricardo Soares100% (2)

- CCCCCC CDokument60 SeitenCCCCCC CSanthan ManneNoch keine Bewertungen

- Embedded Systems Tools & PeripheralsDokument4 SeitenEmbedded Systems Tools & PeripheralsShoriful Islam TarekNoch keine Bewertungen

- Formation Damage ExamplesDokument89 SeitenFormation Damage ExamplesLaurensius Raymond SanjayaNoch keine Bewertungen

- AstigmatismDokument1 SeiteAstigmatismAmmellya PutriNoch keine Bewertungen

- Embedded Systems Course IntroductionDokument75 SeitenEmbedded Systems Course IntroductionpandiNoch keine Bewertungen

- Embedded SystemsDokument178 SeitenEmbedded SystemsPranjal Verma100% (1)

- Embedded SystemsDokument41 SeitenEmbedded SystemsMina Nabil100% (2)

- Complete PCB Design Using NI Multisim, NI Ultiboard, LPKF CircuitCAM and BoardMasterDokument50 SeitenComplete PCB Design Using NI Multisim, NI Ultiboard, LPKF CircuitCAM and BoardMasterRonell SolijonNoch keine Bewertungen

- Fingerprint Door Lock SystemDokument84 SeitenFingerprint Door Lock Systemsrikanth reddyNoch keine Bewertungen

- Spraying TechniquesDokument12 SeitenSpraying TechniquesX800XLNoch keine Bewertungen

- Embedded Systems Interview QuestionsDokument13 SeitenEmbedded Systems Interview QuestionsAnonymous JPbUTto8tqNoch keine Bewertungen

- Entrepreneurship in Nigeria Report 2021 Fate FoundationDokument68 SeitenEntrepreneurship in Nigeria Report 2021 Fate FoundationTaofeeq YekinniNoch keine Bewertungen

- Analysis of Heart Sound and Murmurs For Cardiac DisorderDokument13 SeitenAnalysis of Heart Sound and Murmurs For Cardiac DisorderAnjali NagarNoch keine Bewertungen

- Real-Time Operating SystemsDokument39 SeitenReal-Time Operating SystemsAman JainNoch keine Bewertungen

- Object Oriented Analysis & Design Course OverviewDokument85 SeitenObject Oriented Analysis & Design Course OverviewIrfan Memon100% (1)

- The Unified Modeling Language Reference Manual, Second EditionDokument742 SeitenThe Unified Modeling Language Reference Manual, Second EditionDiego LópezNoch keine Bewertungen

- Embedded SystemsDokument11 SeitenEmbedded Systemsapi-3827000Noch keine Bewertungen

- Microcontroller Based Heartbeat Monitoring With Display LCDDokument90 SeitenMicrocontroller Based Heartbeat Monitoring With Display LCDRama Krishna M64% (14)

- (2014) Colour and Technology in Historic Decorated Glazes and Glasses PDFDokument117 Seiten(2014) Colour and Technology in Historic Decorated Glazes and Glasses PDFtariq.toffa4760Noch keine Bewertungen

- First Periodical Mapeh 9Dokument5 SeitenFirst Periodical Mapeh 9Juvy Singian100% (1)

- Mixed Signal TestDokument14 SeitenMixed Signal TestperiodoNoch keine Bewertungen

- Sree Vidyanikethan College of Engineering: Technical Paper PresentationDokument9 SeitenSree Vidyanikethan College of Engineering: Technical Paper Presentationceaser4274Noch keine Bewertungen

- Development Process of Embedded SystemsDokument7 SeitenDevelopment Process of Embedded SystemsSruthi Reddy100% (1)

- The Ten Commandments of Digital ControlDokument14 SeitenThe Ten Commandments of Digital ControlHüseyin Murat PolaterNoch keine Bewertungen

- Frequency Locked Loop For DC MotorsDokument102 SeitenFrequency Locked Loop For DC MotorsBhagya Sri100% (2)

- Embedded Systems Design and DevelopmentDokument45 SeitenEmbedded Systems Design and DevelopmentPrashant Parashar100% (1)

- QUBE-Servo MyRIO Quick Start GuideDokument4 SeitenQUBE-Servo MyRIO Quick Start GuidealfredokpuNoch keine Bewertungen

- LPC1768 - UART ProgrammingDokument11 SeitenLPC1768 - UART ProgrammingAnonymous Dl13tZi2Noch keine Bewertungen

- Entrepreneurship FG Edited FINALDokument122 SeitenEntrepreneurship FG Edited FINALAthumani100% (1)

- RTOS Marketstudy-V3Dokument33 SeitenRTOS Marketstudy-V3IRFAN RAWAIL KHANNoch keine Bewertungen

- The MSP430 Microcontroller SystemDokument7 SeitenThe MSP430 Microcontroller SystemArthu hNoch keine Bewertungen

- ET7102-Microcontroller Based System DesignDokument19 SeitenET7102-Microcontroller Based System DesignbalaNoch keine Bewertungen

- MSP430-1 MSP430 OverviewDokument99 SeitenMSP430-1 MSP430 OverviewBrian YehNoch keine Bewertungen

- OMADADokument13 SeitenOMADAXBASCOM BANDUNGNoch keine Bewertungen

- Exam Questions 2018Dokument3 SeitenExam Questions 2018naveen g cNoch keine Bewertungen

- Valeo QsDokument7 SeitenValeo QsNoha MustafaNoch keine Bewertungen

- Financial Inclusion Opportunities For Micro Health Insurance in Nepal: An Exploratory Analysis of Health Incidence, Costs and Willingness To Pay in Dhading and Banke Districts of NepalDokument150 SeitenFinancial Inclusion Opportunities For Micro Health Insurance in Nepal: An Exploratory Analysis of Health Incidence, Costs and Willingness To Pay in Dhading and Banke Districts of NepalJason WolfeNoch keine Bewertungen

- 6Dokument35 Seiten6Ankit Sethia100% (3)

- Elements of GUIDokument3 SeitenElements of GUIBanhiNoch keine Bewertungen

- Dynamic Cmos LogicDokument3 SeitenDynamic Cmos Logicasheesh12febNoch keine Bewertungen

- Pont Eres1 2014Dokument399 SeitenPont Eres1 2014Chamuko CanijoNoch keine Bewertungen

- Remotely Controlled Android Based Electronic Notice BoardDokument27 SeitenRemotely Controlled Android Based Electronic Notice BoardyasirNoch keine Bewertungen

- VHDLDokument97 SeitenVHDLapi-3864016100% (1)

- Bitwise OperatorsDokument4 SeitenBitwise OperatorsslspaNoch keine Bewertungen

- Micro Servo RobotDokument40 SeitenMicro Servo Robotlokesh mahor0% (1)

- Introduction To 8085 MicroprocessorDokument35 SeitenIntroduction To 8085 MicroprocessorCave BosNoch keine Bewertungen

- 05190505Dokument5 Seiten05190505deepak.stoicNoch keine Bewertungen

- Embedded Hypervisor The Ultimate Step-By-Step GuideVon EverandEmbedded Hypervisor The Ultimate Step-By-Step GuideNoch keine Bewertungen

- Introduction to Embedded Systems Definition and ComponentsDokument28 SeitenIntroduction to Embedded Systems Definition and ComponentsCheril Mehta0% (1)

- Chapter 1: Introduction To Psoc: From The Free Online Book "Architecture and Programming of Psoc Microcontrollers"Dokument34 SeitenChapter 1: Introduction To Psoc: From The Free Online Book "Architecture and Programming of Psoc Microcontrollers"Joel George MathewNoch keine Bewertungen

- Fundamentals in Digital IC DesignDokument16 SeitenFundamentals in Digital IC DesignSiddharth PanditNoch keine Bewertungen

- 1.2language Processing ActivitiesDokument15 Seiten1.2language Processing ActivitiesMailk Kumar KNoch keine Bewertungen

- TMS320F2812 Dsp/biosDokument26 SeitenTMS320F2812 Dsp/biosPantech ProLabs India Pvt LtdNoch keine Bewertungen

- RtosDokument42 SeitenRtospipul36Noch keine Bewertungen

- USB Field Firmware Updates On MSP430 MCUsDokument24 SeitenUSB Field Firmware Updates On MSP430 MCUsDaniel Gustavo Martinez MartinezNoch keine Bewertungen

- Chapter 4 Assembly Language and ProgrammingDokument85 SeitenChapter 4 Assembly Language and ProgrammingPetra Kalasa100% (1)

- Unit 1Dokument124 SeitenUnit 1RaviNoch keine Bewertungen

- C++ Program For PalindromeDokument1 SeiteC++ Program For Palindromejokerbuddy01Noch keine Bewertungen

- C++ Program - Factorial Using FunctionDokument1 SeiteC++ Program - Factorial Using FunctionJag JagNoch keine Bewertungen

- Chap 3Lesson15EmsysNewDokument14 SeitenChap 3Lesson15EmsysNewDominic NorrisNoch keine Bewertungen

- Case Study 3 DDokument4 SeitenCase Study 3 DJag JagNoch keine Bewertungen

- Ansys - MEMS Lab IntroductionDokument9 SeitenAnsys - MEMS Lab IntroductionJag JagNoch keine Bewertungen

- Mitsubishi: Technical Service BulletinDokument11 SeitenMitsubishi: Technical Service BulletinKonstantinNoch keine Bewertungen

- Weeder SynopsisDokument8 SeitenWeeder SynopsisParas ChauhanNoch keine Bewertungen

- Moral vs Non-Moral Standards ExplainedDokument2 SeitenMoral vs Non-Moral Standards ExplainedLee PascuaNoch keine Bewertungen

- Columbus United Methodist Church: in This IssueDokument11 SeitenColumbus United Methodist Church: in This IssueColumbusUMCNoch keine Bewertungen

- Assignment On Computer HardwareDokument9 SeitenAssignment On Computer HardwareMuktadirhasan100% (1)

- AR213 PostWar AjKanokwan HandoutDokument28 SeitenAR213 PostWar AjKanokwan Handoutpranutchaya.bamNoch keine Bewertungen

- PDF If I Break 15 Portia Moore CompressDokument61 SeitenPDF If I Break 15 Portia Moore CompressAlbenis RodríguezNoch keine Bewertungen

- Godrej Group Is An Indian Conglomerate Headquartered in MumbaiDokument4 SeitenGodrej Group Is An Indian Conglomerate Headquartered in MumbairahulbastyNoch keine Bewertungen

- Cash Valve Product OverviewDokument16 SeitenCash Valve Product OverviewestebanNoch keine Bewertungen

- Chapte4 ZamznDokument24 SeitenChapte4 ZamznAHMED DARAJNoch keine Bewertungen

- Ask Astrologer Report - Specific Answer To Major Concern of LifeDokument8 SeitenAsk Astrologer Report - Specific Answer To Major Concern of LifecyberastroNoch keine Bewertungen

- Ficha Técnica Electroválvula JJ08Dokument1 SeiteFicha Técnica Electroválvula JJ08Jorge JuanNoch keine Bewertungen

- Single Point Earthing and Equipotential Planes for Sensitive Electronic EquipmentDokument30 SeitenSingle Point Earthing and Equipotential Planes for Sensitive Electronic EquipmentDeepak GuptaNoch keine Bewertungen

- RFP Master PlanDokument9 SeitenRFP Master PlanakhilchibberNoch keine Bewertungen

- Deka Batteries PDFDokument6 SeitenDeka Batteries PDFLuis Alonso Osorio MolinaNoch keine Bewertungen

- Chapter 4Dokument9 SeitenChapter 4Aung KhantNoch keine Bewertungen

- Automated Home Rainwater Harvesting Earns MoneyDokument4 SeitenAutomated Home Rainwater Harvesting Earns MoneysaravananNoch keine Bewertungen

- BCH102 Unit - III: Physiology Topic: BloodDokument18 SeitenBCH102 Unit - III: Physiology Topic: Blooddivya vajpayeeNoch keine Bewertungen

- Safety Data Sheet: SECTION 1: Identification of The Substance/mixture and of The Company/ UndertakingDokument10 SeitenSafety Data Sheet: SECTION 1: Identification of The Substance/mixture and of The Company/ UndertakingBradyNoch keine Bewertungen

- Belecobeauty Company ProfileDokument19 SeitenBelecobeauty Company ProfileBisma BrawijayaNoch keine Bewertungen

- Chapter 14: Understanding Clutches and Their Operating PrinciplesDokument39 SeitenChapter 14: Understanding Clutches and Their Operating PrinciplespapipapiiNoch keine Bewertungen